Super B IFR outline of the IFR DAQ

Super. B IFR: outline of the IFR DAQ electronics X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 1

Summary • prototype detector and electronics for a proof of principle • updated IFR detector data bandwidth and event size estimates X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 2

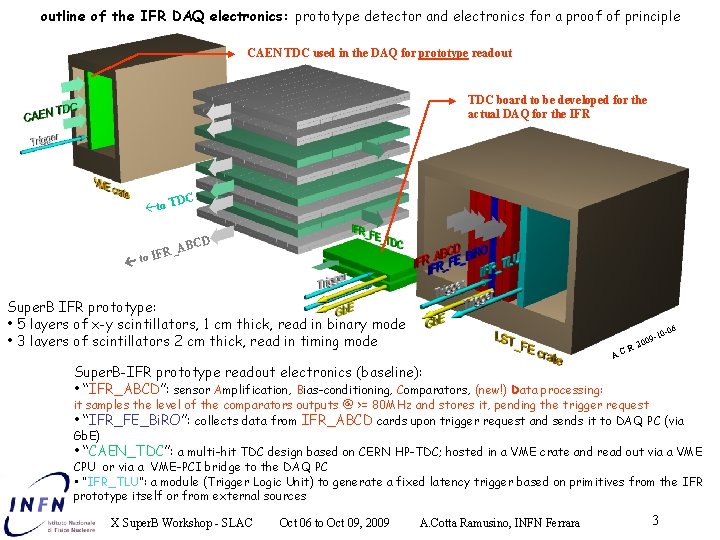

outline of the IFR DAQ electronics: prototype detector and electronics for a proof of principle CAEN TDC used in the DAQ for prototype readout TDC board to be developed for the actual DAQ for the IFR DC ßto T D ABC R_ to IF Super. B IFR prototype: • 5 layers of x-y scintillators, 1 cm thick, read in binary mode • 3 layers of scintillators 2 cm thick, read in timing mode 06 10 - 009 R. 2 . A. C Super. B-IFR prototype readout electronics (baseline): • “IFR_ABCD”: sensor Amplification, Bias-conditioning, Comparators, (new!) Data processing: it samples the level of the comparators outputs @ >= 80 MHz and stores it, pending the trigger request • “IFR_FE_Bi. RO”: collects data from IFR_ABCD cards upon trigger request and sends it to DAQ PC (via Gb. E) • “CAEN_TDC”: a multi-hit TDC design based on CERN HP-TDC; hosted in a VME crate and read out via a VME CPU or via a VME-PCI bridge to the DAQ PC • “IFR_TLU”: a module (Trigger Logic Unit) to generate a fixed latency trigger based on primitives from the IFR prototype itself or from external sources X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 3

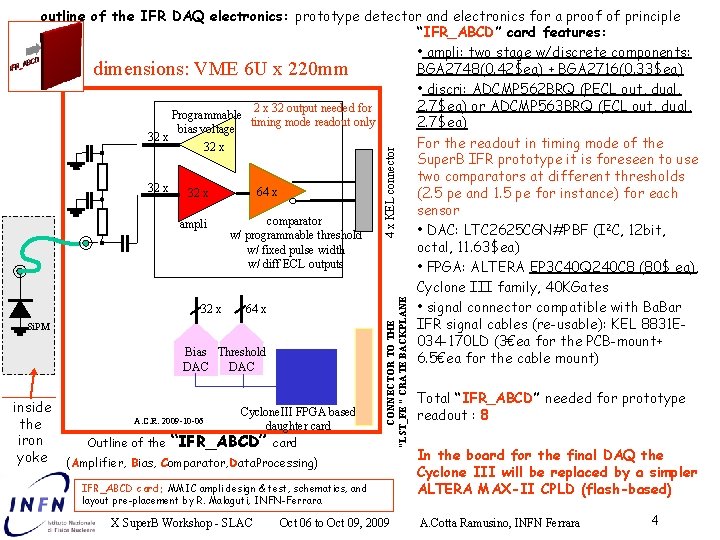

DAC inside the iron yoke DAC Cyclone. III FPGA based A. C. R. 2009 -10 -06 daughter card Outline of the “IFR_ABCD” card CONNECTOR TO THE “LST_FE “ CRATE BACKPLANE 4 x KEL connector outline of the IFR DAQ electronics: prototype detector and electronics for a proof of principle “IFR_ABCD” card features: • ampli: two stage w/discrete components: BGA 2748(0. 42$ea) + BGA 2716(0. 33$ea) dimensions: VME 6 U x 220 mm • discri: ADCMP 562 BRQ (PECL out, dual, 2. 7$ea) or ADCMP 563 BRQ (ECL out, dual, 2 x 32 output needed for Programmable timing mode readout only 2. 7$ea) bias voltage 32 x For the readout in timing mode of the 32 x Super. B IFR prototype it is foreseen to use two comparators at different thresholds 32 x 64 x 32 x (2. 5 pe and 1. 5 pe for instance) for each sensor comparator ampli • DAC: LTC 2625 CGN#PBF (I 2 C, 12 bit, w/ programmable threshold octal, 11. 63$ea) w/ fixed pulse width w/ diff ECL outputs • FPGA: ALTERA EP 3 C 40 Q 240 C 8 (80$ ea), Cyclone III family, 40 KGates • signal connector compatible with Ba. Bar 32 x 64 x IFR signal cables (re-usable): KEL 8831 ESi. PM 034 -170 LD (3€ea for the PCB-mount+ Bias Threshold 6. 5€ea for the cable mount) (Amplifier, Bias, Comparator, Data. Processing) IFR_ABCD card: MMIC ampli design & test, schematics, and layout pre-placement by R. Malaguti, INFN-Ferrara X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 Total “IFR_ABCD” needed for prototype readout : 8 In the board for the final DAQ the Cyclone III will be replaced by a simpler ALTERA MAX-II CPLD (flash-based) A. Cotta Ramusino, INFN Ferrara 4

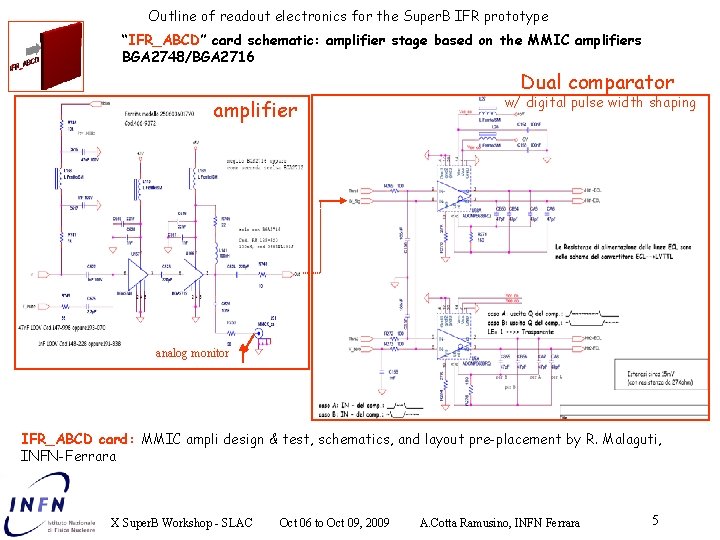

Outline of readout electronics for the Super. B IFR prototype “IFR_ABCD” card schematic: amplifier stage based on the MMIC amplifiers BGA 2748/BGA 2716 Dual comparator amplifier w/ digital pulse width shaping analog monitor IFR_ABCD card: MMIC ampli design & test, schematics, and layout pre-placement by R. Malaguti, INFN-Ferrara X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 5

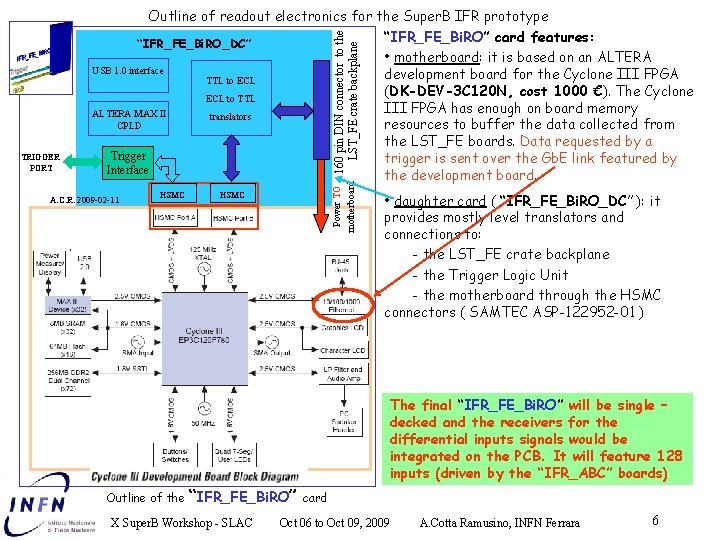

160 pin DIN connector to the LST_FE crate backplane A. C. R. 2009 -02 -11 HSMC Power TO motherboard TRIGGER PORT Outline of readout electronics for the Super. B IFR prototype “IFR_FE_Bi. RO” card features: “IFR_FE_Bi. RO_DC” • motherboard: it is based on an ALTERA USB 1. 0 interface development board for the Cyclone III FPGA TTL to ECL (DK-DEV-3 C 120 N, cost 1000 €). The Cyclone ECL to TTL III FPGA has enough on board memory ALTERA MAX II translators CPLD resources to buffer the data collected from the LST_FE boards. Data requested by a Trigger trigger is sent over the Gb. E link featured by Interface the development board. HSMC • daughter card ( “IFR_FE_Bi. RO_DC” ): it provides mostly level translators and connections to: - the LST_FE crate backplane - the Trigger Logic Unit - the motherboard through the HSMC connectors ( SAMTEC ASP-122952 -01 ) The final “IFR_FE_Bi. RO” will be single – decked and the receivers for the differential inputs signals would be integrated on the PCB. It will feature 128 inputs (driven by the “IFR_ABC” boards) Outline of the “IFR_FE_Bi. RO” card X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 6

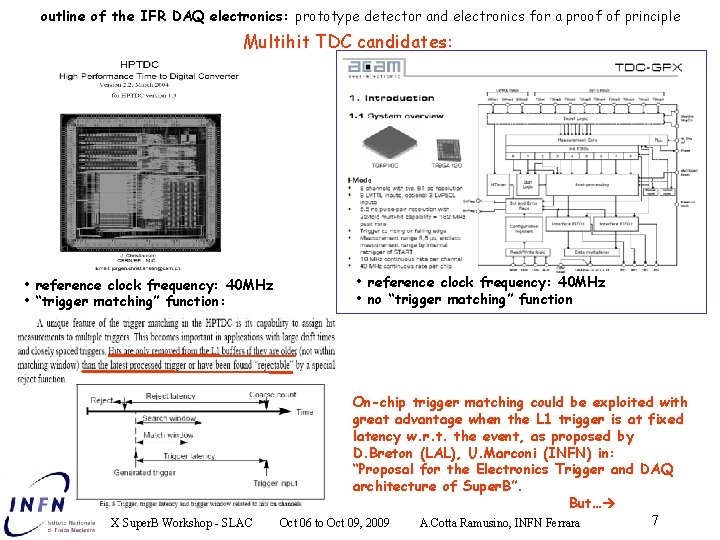

outline of the IFR DAQ electronics: prototype detector and electronics for a proof of principle Multihit TDC candidates: • reference clock frequency: 40 MHz • “trigger matching” function: X Super. B Workshop - SLAC • reference clock frequency: 40 MHz • no “trigger matching” function On-chip trigger matching could be exploited with great advantage when the L 1 trigger is at fixed latency w. r. t. the event, as proposed by D. Breton (LAL), U. Marconi (INFN) in: “Proposal for the Electronics Trigger and DAQ architecture of Super. B”. But… 7 Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara

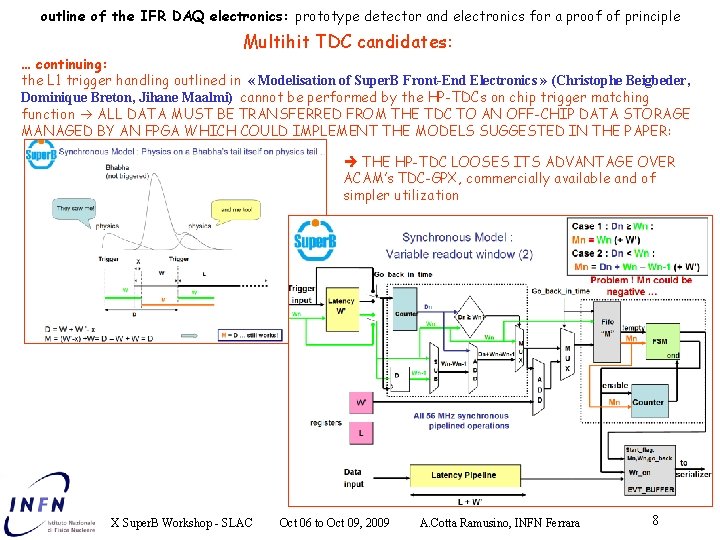

outline of the IFR DAQ electronics: prototype detector and electronics for a proof of principle Multihit TDC candidates: … continuing: the L 1 trigger handling outlined in « Modelisation of Super. B Front-End Electronics » (Christophe Beigbeder, Dominique Breton, Jihane Maalmi) cannot be performed by the HP-TDCs on chip trigger matching function ALL DATA MUST BE TRANSFERRED FROM THE TDC TO AN OFF-CHIP DATA STORAGE MANAGED BY AN FPGA WHICH COULD IMPLEMENT THE MODELS SUGGESTED IN THE PAPER: THE HP-TDC LOOSES ITS ADVANTAGE OVER ACAM’s TDC-GPX, commercially available and of simpler utilization X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 8

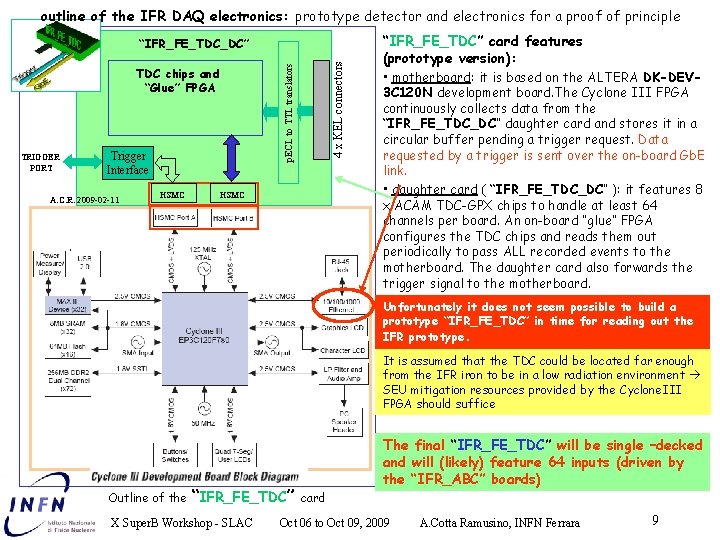

outline of the IFR DAQ electronics: prototype detector and electronics for a proof of principle TDC chips and “Glue” FPGA TRIGGER PORT Trigger Interface A. C. R. 2009 -02 -11 HSMC 4 x KEL connectors p. ECL to TTL translators “IFR_FE_TDC_DC” “IFR_FE_TDC” card features (prototype version): • motherboard: it is based on the ALTERA DK-DEV- 3 C 120 N development board. The Cyclone III FPGA continuously collects data from the “IFR_FE_TDC_DC” daughter card and stores it in a circular buffer pending a trigger request. Data requested by a trigger is sent over the on-board Gb. E link. • daughter card ( “IFR_FE_TDC_DC” ): it features 8 x ACAM TDC-GPX chips to handle at least 64 channels per board. An on-board “glue” FPGA configures the TDC chips and reads them out periodically to pass ALL recorded events to the motherboard. The daughter card also forwards the trigger signal to the motherboard. Unfortunately it does not seem possible to build a prototype “IFR_FE_TDC” in time for reading out the IFR prototype. It is assumed that the TDC could be located far enough from the IFR iron to be in a low radiation environment SEU mitigation resources provided by the Cyclone. III FPGA should suffice Outline of the “IFR_FE_TDC” card X Super. B Workshop - SLAC The final “IFR_FE_TDC” will be single –decked and will (likely) feature 64 inputs (driven by the “IFR_ABC” boards) Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 9

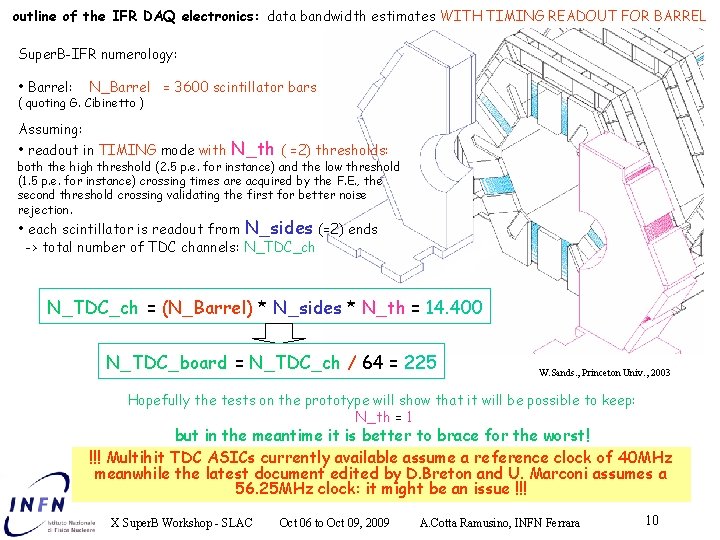

outline of the IFR DAQ electronics: data bandwidth estimates WITH TIMING READOUT FOR BARREL Super. B-IFR numerology: • Barrel: N_Barrel = 3600 scintillator bars ( quoting G. Cibinetto ) Assuming: • readout in TIMING mode with N_th ( =2) thresholds: both the high threshold (2. 5 p. e. for instance) and the low threshold (1. 5 p. e. for instance) crossing times are acquired by the F. E. , the second threshold crossing validating the first for better noise rejection. • each scintillator is readout from N_sides (=2) ends -> total number of TDC channels: N_TDC_ch = (N_Barrel) * N_sides * N_th = 14. 400 N_TDC_board = N_TDC_ch / 64 = 225 W. Sands. , Princeton Univ. , 2003 Hopefully the tests on the prototype will show that it will be possible to keep: N_th = 1 but in the meantime it is better to brace for the worst! !!! Multihit TDC ASICs currently available assume a reference clock of 40 MHz meanwhile the latest document edited by D. Breton and U. Marconi assumes a 56. 25 MHz clock: it might be an issue !!! X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 10

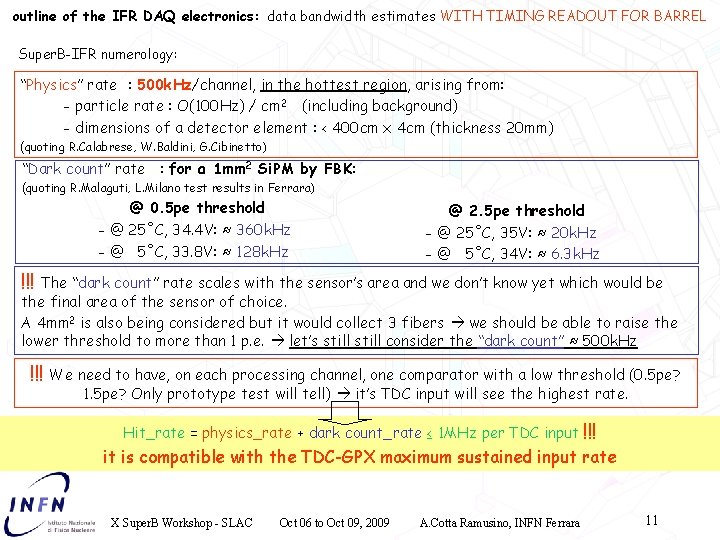

outline of the IFR DAQ electronics: data bandwidth estimates WITH TIMING READOUT FOR BARREL Super. B-IFR numerology: “Physics” rate : 500 k. Hz/channel, in the hottest region, arising from: - particle rate : O(100 Hz) / cm 2 (including background) - dimensions of a detector element : < 400 cm x 4 cm (thickness 20 mm) (quoting R. Calabrese, W. Baldini, G. Cibinetto ) “Dark count” rate : for a 1 mm 2 Si. PM by FBK: (quoting R. Malaguti, L. Milano test results in Ferrara ) @ 0. 5 pe threshold - @ 25˚C, 34. 4 V: ≈ 360 k. Hz - @ 5˚C, 33. 8 V: ≈ 128 k. Hz @ 2. 5 pe threshold - @ 25˚C, 35 V: ≈ 20 k. Hz - @ 5˚C, 34 V: ≈ 6. 3 k. Hz !!! The “dark count” rate scales with the sensor’s area and we don’t know yet which would be the final area of the sensor of choice. A 4 mm 2 is also being considered but it would collect 3 fibers we should be able to raise the lower threshold to more than 1 p. e. let’s still consider the “dark count” ≈ 500 k. Hz !!! We need to have, on each processing channel, one comparator with a low threshold (0. 5 pe? 1. 5 pe? Only prototype test will tell) it’s TDC input will see the highest rate. Hit_rate = physics_rate + dark count_rate ≤ 1 MHz per TDC input !!! it is compatible with the TDC-GPX maximum sustained input rate X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 11

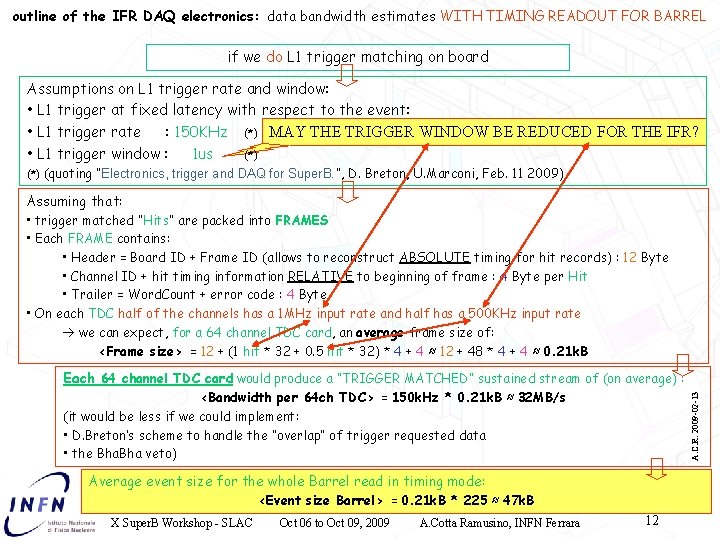

outline of the IFR DAQ electronics: data bandwidth estimates WITH TIMING READOUT FOR BARREL if we do L 1 trigger matching on board Assumptions on L 1 trigger rate and window: • L 1 trigger at fixed latency with respect to the event: • L 1 trigger rate : 150 KHz (*) MAY THE TRIGGER WINDOW BE REDUCED FOR THE IFR? • L 1 trigger window : 1 us (*) (quoting “Electronics, trigger and DAQ for Super. B. ”, D. Breton, U. Marconi, Feb. 11 2009) Assuming that: • trigger matched “Hits” are packed into FRAMES • Each FRAME contains: • Header = Board ID + Frame ID (allows to reconstruct ABSOLUTE timing for hit records) : 12 Byte • Channel ID + hit timing information RELATIVE to beginning of frame : 4 Byte per Hit • Trailer = Word. Count + error code : 4 Byte • On each TDC half of the channels has a 1 MHz input rate and half has a 500 KHz input rate we can expect, for a 64 channel TDC card, an average frame size of: <Frame size> = 12 + (1 hit * 32 + 0. 5 hit * 32) * 4 + 4 ≈ 12 + 48 * 4 + 4 ≈ 0. 21 k. B Each 64 channel TDC card would produce a “TRIGGER MATCHED” sustained stream of (on average) : A. C. R. 2009 -02 -13 <Bandwidth per 64 ch TDC> = 150 k. Hz * 0. 21 k. B ≈ 32 MB/s (it would be less if we could implement: • D. Breton’s scheme to handle the “overlap” of trigger requested data • the Bha veto) Average event size for the whole Barrel read in timing mode : <Event size Barrel> = 0. 21 k. B * 225 ≈ 47 k. B X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 12

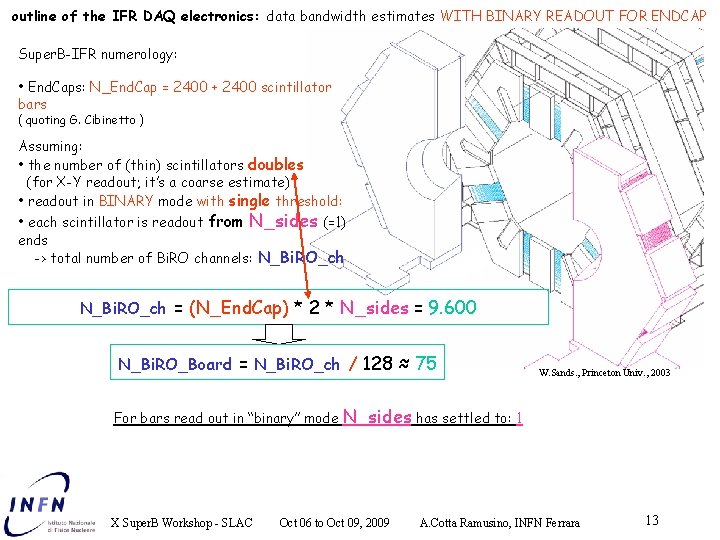

outline of the IFR DAQ electronics: data bandwidth estimates WITH BINARY READOUT FOR ENDCAP Super. B-IFR numerology: • End. Caps: N_End. Cap = 2400 + 2400 scintillator bars ( quoting G. Cibinetto ) Assuming: • the number of (thin) scintillators doubles (for X-Y readout; it’s a coarse estimate) • readout in BINARY mode with single threshold: • each scintillator is readout from N_sides (=1) ends -> total number of Bi. RO channels: N_Bi. RO_ch = (N_End. Cap) * 2 * N_sides = 9. 600 N_Bi. RO_Board = N_Bi. RO_ch / 128 ≈ 75 For bars read out in “binary” mode X Super. B Workshop - SLAC W. Sands. , Princeton Univ. , 2003 N_sides has settled to: 1 Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 13

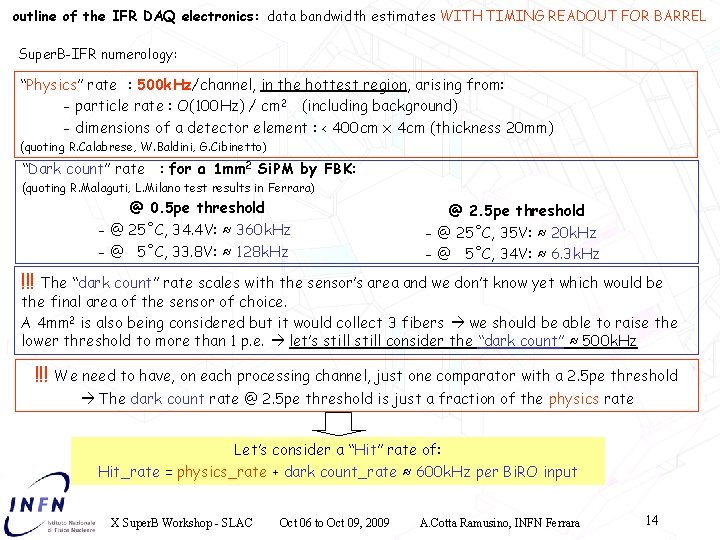

outline of the IFR DAQ electronics: data bandwidth estimates WITH TIMING READOUT FOR BARREL Super. B-IFR numerology: “Physics” rate : 500 k. Hz/channel, in the hottest region, arising from: - particle rate : O(100 Hz) / cm 2 (including background) - dimensions of a detector element : < 400 cm x 4 cm (thickness 20 mm) (quoting R. Calabrese, W. Baldini, G. Cibinetto ) “Dark count” rate : for a 1 mm 2 Si. PM by FBK: (quoting R. Malaguti, L. Milano test results in Ferrara ) @ 0. 5 pe threshold - @ 25˚C, 34. 4 V: ≈ 360 k. Hz - @ 5˚C, 33. 8 V: ≈ 128 k. Hz @ 2. 5 pe threshold - @ 25˚C, 35 V: ≈ 20 k. Hz - @ 5˚C, 34 V: ≈ 6. 3 k. Hz !!! The “dark count” rate scales with the sensor’s area and we don’t know yet which would be the final area of the sensor of choice. A 4 mm 2 is also being considered but it would collect 3 fibers we should be able to raise the lower threshold to more than 1 p. e. let’s still consider the “dark count” ≈ 500 k. Hz !!! We need to have, on each processing channel, just one comparator with a 2. 5 pe threshold The dark count rate @ 2. 5 pe threshold is just a fraction of the physics rate Let’s consider a “Hit” rate of: Hit_rate = physics_rate + dark count_rate ≈ 600 k. Hz per Bi. RO input X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 14

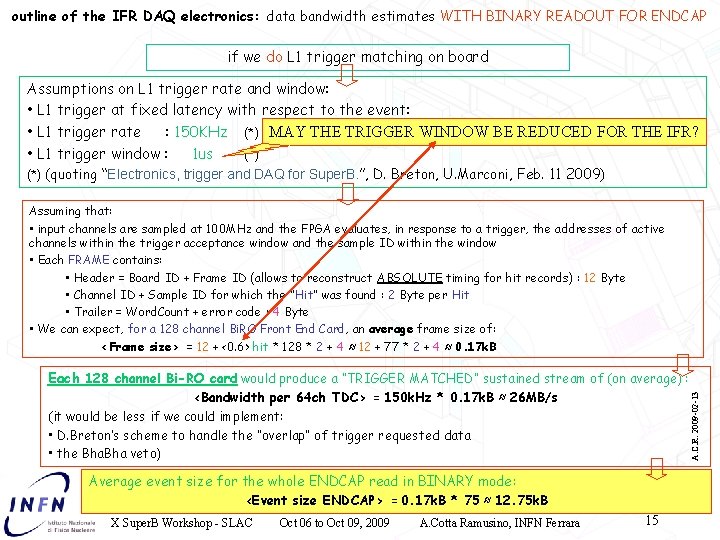

outline of the IFR DAQ electronics: data bandwidth estimates WITH BINARY READOUT FOR ENDCAP if we do L 1 trigger matching on board Assumptions on L 1 trigger rate and window: • L 1 trigger at fixed latency with respect to the event: • L 1 trigger rate : 150 KHz (*) MAY THE TRIGGER WINDOW BE REDUCED FOR THE IFR? • L 1 trigger window : 1 us (*) (quoting “Electronics, trigger and DAQ for Super. B. ”, D. Breton, U. Marconi, Feb. 11 2009) Assuming that: • input channels are sampled at 100 MHz and the FPGA evaluates, in response to a trigger, the addresses of active channels within the trigger acceptance window and the sample ID within the window • Each FRAME contains: • Header = Board ID + Frame ID (allows to reconstruct ABSOLUTE timing for hit records) : 12 Byte • Channel ID + Sample ID for which the “Hit” was found : 2 Byte per Hit • Trailer = Word. Count + error code : 4 Byte • We can expect, for a 128 channel Bi. RO Front End Card, an average frame size of: <Frame size> = 12 + <0. 6> hit * 128 * 2 + 4 ≈ 12 + 77 * 2 + 4 ≈ 0. 17 k. B Each 128 channel Bi-RO card would produce a “TRIGGER MATCHED” sustained stream of (on average) : A. C. R. 2009 -02 -13 <Bandwidth per 64 ch TDC> = 150 k. Hz * 0. 17 k. B ≈ 26 MB/s (it would be less if we could implement: • D. Breton’s scheme to handle the “overlap” of trigger requested data • the Bha veto) Average event size for the whole ENDCAP read in BINARY mode : <Event size ENDCAP> = 0. 17 k. B * 75 ≈ 12. 75 k. B X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 15

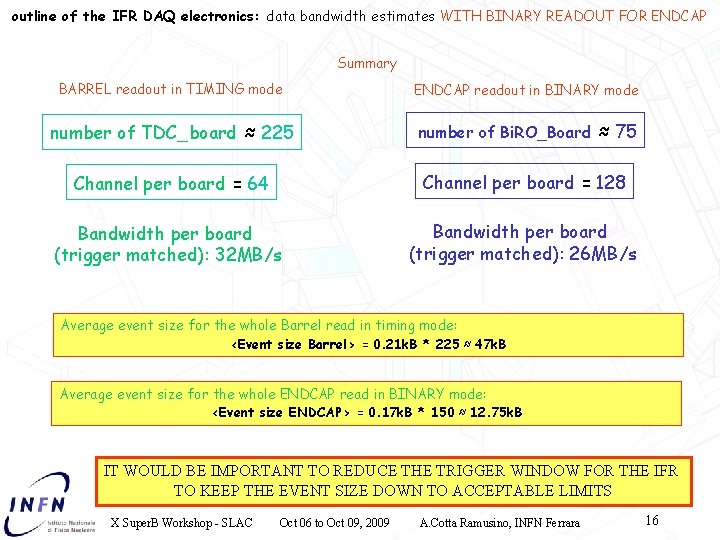

outline of the IFR DAQ electronics: data bandwidth estimates WITH BINARY READOUT FOR ENDCAP Summary BARREL readout in TIMING mode ENDCAP readout in BINARY mode number of TDC_board ≈ 225 number of Bi. RO_Board ≈ 75 Channel per board = 64 Channel per board = 128 Bandwidth per board (trigger matched): 32 MB/s Bandwidth per board (trigger matched): 26 MB/s Average event size for the whole Barrel read in timing mode : <Event size Barrel> = 0. 21 k. B * 225 ≈ 47 k. B Average event size for the whole ENDCAP read in BINARY mode : <Event size ENDCAP> = 0. 17 k. B * 150 ≈ 12. 75 k. B IT WOULD BE IMPORTANT TO REDUCE THE TRIGGER WINDOW FOR THE IFR TO KEEP THE EVENT SIZE DOWN TO ACCEPTABLE LIMITS X Super. B Workshop - SLAC Oct 06 to Oct 09, 2009 A. Cotta Ramusino, INFN Ferrara 16

- Slides: 16