Sun HyeSeung Hanbat National University Prof Lee Jaeheung

조합논리회로 모델링 한밭대학교 반도체설계실 Sun, Hye-Seung Hanbat National University Prof. Lee Jaeheung

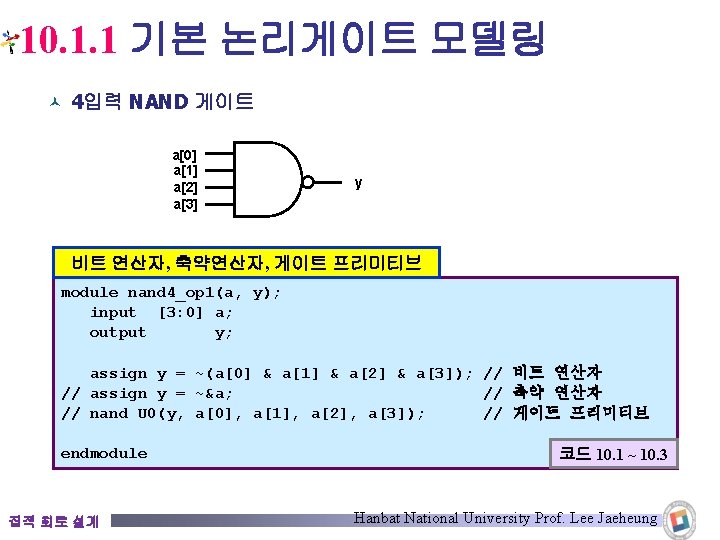

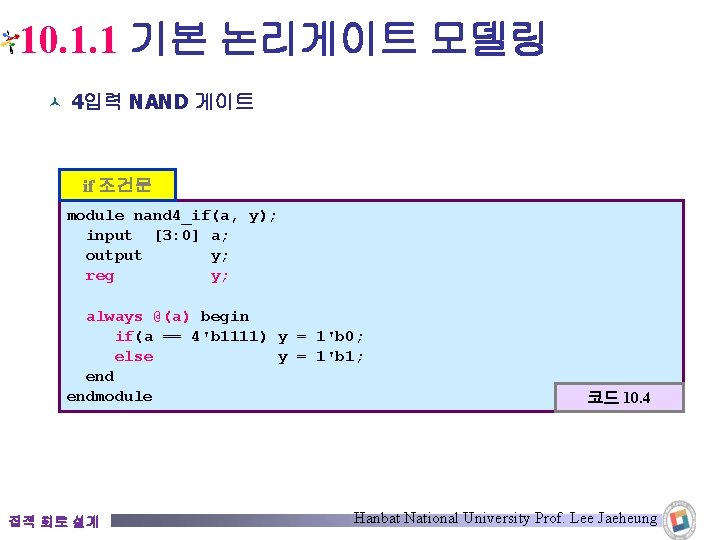

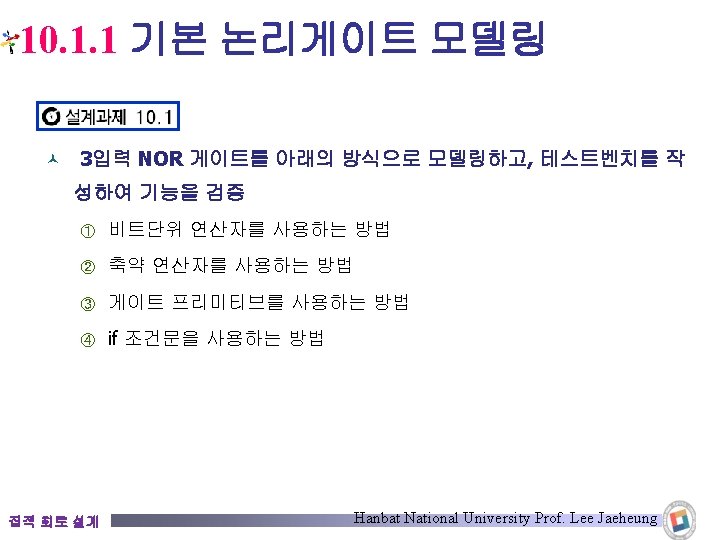

10. 1. 1 기본 논리게이트 모델링 © 4입력 NAND 게이트 if 조건문 module nand 4_if(a, y); input [3: 0] a; output y; reg y; always @(a) begin if(a == 4'b 1111) y = 1'b 0; else y = 1'b 1; endmodule 집적 회로 설계 코드 10. 4 Hanbat National University Prof. Lee Jaeheung

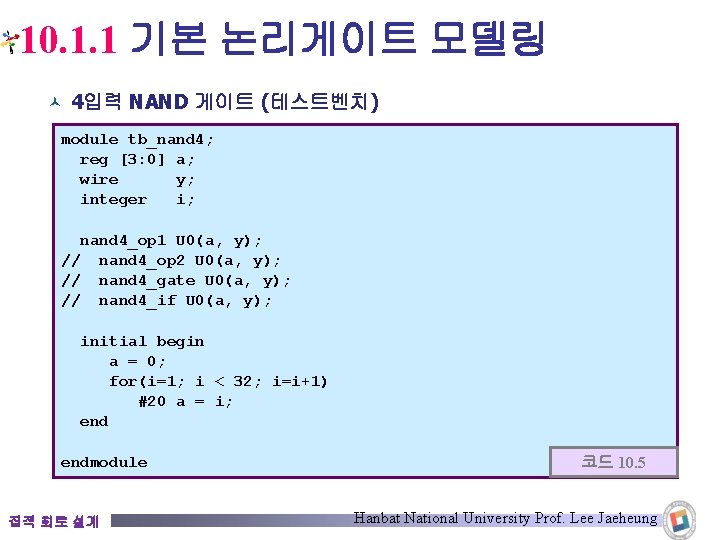

10. 1. 1 기본 논리게이트 모델링 © 4입력 NAND 게이트 (테스트벤치) module tb_nand 4; reg [3: 0] a; wire y; integer i; nand 4_op 1 U 0(a, y); // nand 4_op 2 U 0(a, y); // nand 4_gate U 0(a, y); // nand 4_if U 0(a, y); initial begin a = 0; for(i=1; i < 32; i=i+1) #20 a = i; endmodule 집적 회로 설계 코드 10. 5 Hanbat National University Prof. Lee Jaeheung

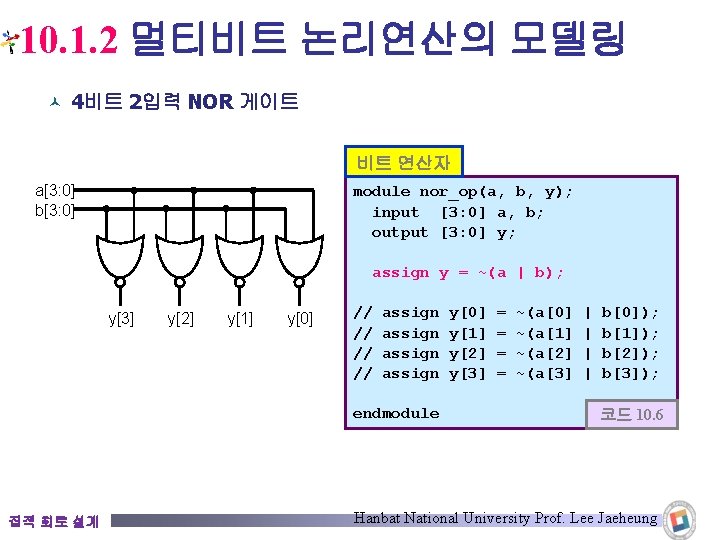

10. 1. 2 멀티비트 논리연산의 모델링 © 4비트 2입력 NOR 게이트 비트 연산자 a[3: 0] b[3: 0] module nor_op(a, b, y); input [3: 0] a, b; output [3: 0] y; assign y = ~(a | b); y[3] y[2] y[1] y[0] // // assign endmodule 집적 회로 설계 y[0] y[1] y[2] y[3] = = ~(a[0] ~(a[1] ~(a[2] ~(a[3] | | b[0]); b[1]); b[2]); b[3]); 코드 10. 6 Hanbat National University Prof. Lee Jaeheung

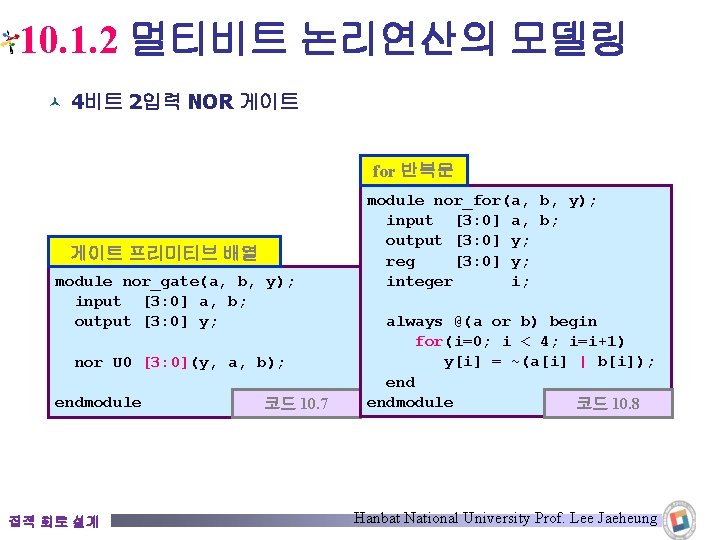

10. 1. 2 멀티비트 논리연산의 모델링 © 4비트 2입력 NOR 게이트 for 반복문 게이트 프리미티브 배열 module nor_gate(a, b, y); input [3: 0] a, b; output [3: 0] y; nor U 0 [3: 0](y, a, b); endmodule 집적 회로 설계 코드 10. 7 module nor_for(a, b, y); input [3: 0] a, b; output [3: 0] y; reg [3: 0] y; integer i; always @(a or b) begin for(i=0; i < 4; i=i+1) y[i] = ~(a[i] | b[i]); endmodule 코드 10. 8 Hanbat National University Prof. Lee Jaeheung

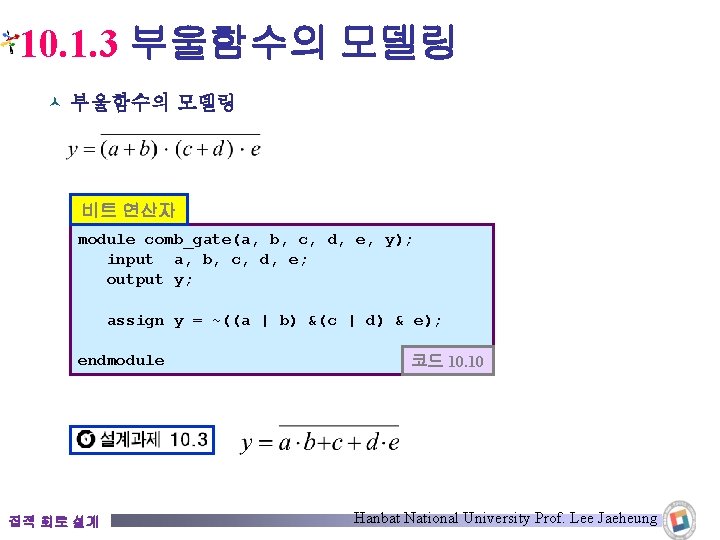

10. 1. 3 부울함수의 모델링 © 부울함수의 모델링 비트 연산자 module comb_gate(a, b, c, d, e, y); input a, b, c, d, e; output y; assign y = ~((a | b) &(c | d) & e); endmodule 집적 회로 설계 코드 10. 10 Hanbat National University Prof. Lee Jaeheung

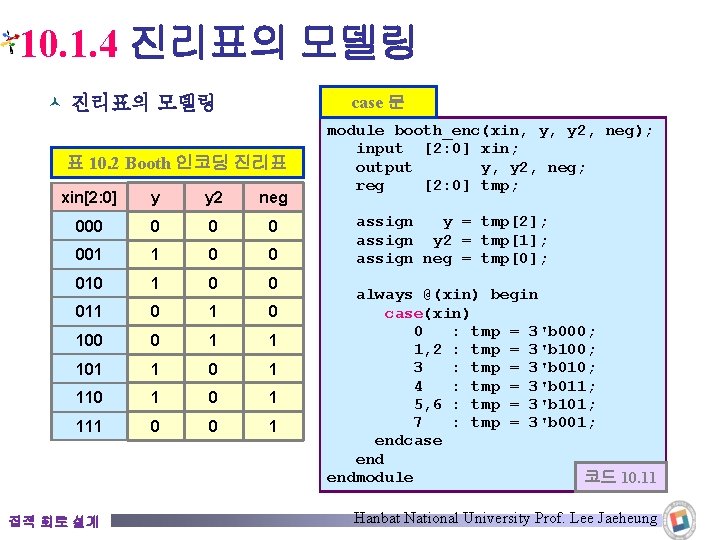

10. 1. 4 진리표의 모델링 © 진리표의 모델링 case 문 표 10. 2 Booth 인코딩 진리표 xin[2: 0] y y 2 neg 000 0 001 1 0 0 010 1 0 0 011 0 100 0 1 1 101 1 0 1 110 1 111 0 0 1 집적 회로 설계 module booth_enc(xin, y, y 2, neg); input [2: 0] xin; output y, y 2, neg; reg [2: 0] tmp; assign y = tmp[2]; assign y 2 = tmp[1]; assign neg = tmp[0]; always @(xin) begin case(xin) 0 : tmp = 3'b 000; 1, 2 : tmp = 3'b 100; 3 : tmp = 3'b 010; 4 : tmp = 3'b 011; 5, 6 : tmp = 3'b 101; 7 : tmp = 3'b 001; endcase endmodule 코드 10. 11 Hanbat National University Prof. Lee Jaeheung

![10. 1. 4 진리표의 모델링 © 진리표의 모델링 테스트벤치 module tb_booth_enc; reg [2: 0] 10. 1. 4 진리표의 모델링 © 진리표의 모델링 테스트벤치 module tb_booth_enc; reg [2: 0]](http://slidetodoc.com/presentation_image/102bf6cc135f767430cc551e1de42dbc/image-14.jpg)

10. 1. 4 진리표의 모델링 © 진리표의 모델링 테스트벤치 module tb_booth_enc; reg [2: 0] xin; wire y, y 2, neg; integer i; booth_enc U 0(xin, y, y 2, neg); initial begin xin = 0; for(i=1; i < 16; i=i+1) #20 xin = i; endmodule 집적 회로 설계 코드 10. 12 Hanbat National University Prof. Lee Jaeheung

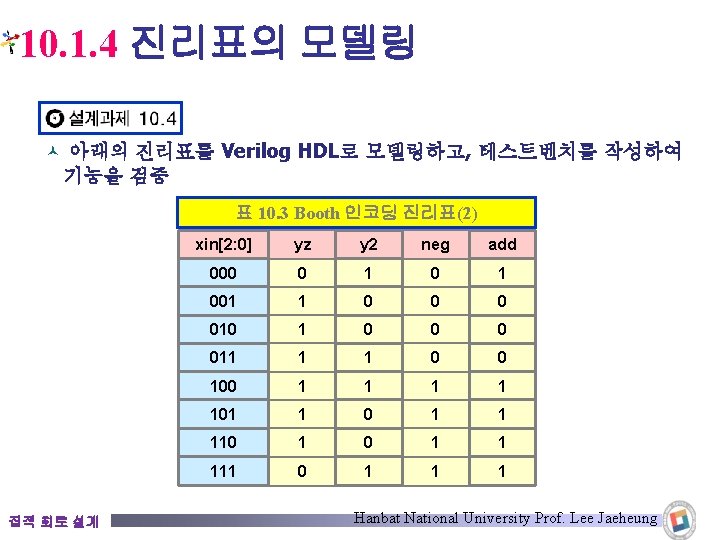

10. 1. 4 진리표의 모델링 © 아래의 진리표를 Verilog HDL로 모델링하고, 테스트벤치를 작성하여 기능을 검증 표 10. 3 Booth 인코딩 진리표(2) 집적 회로 설계 xin[2: 0] yz y 2 neg add 000 0 1 001 1 0 010 1 0 011 1 1 0 0 100 1 1 101 1 0 1 1 110 1 1 111 0 1 1 1 Hanbat National University Prof. Lee Jaeheung

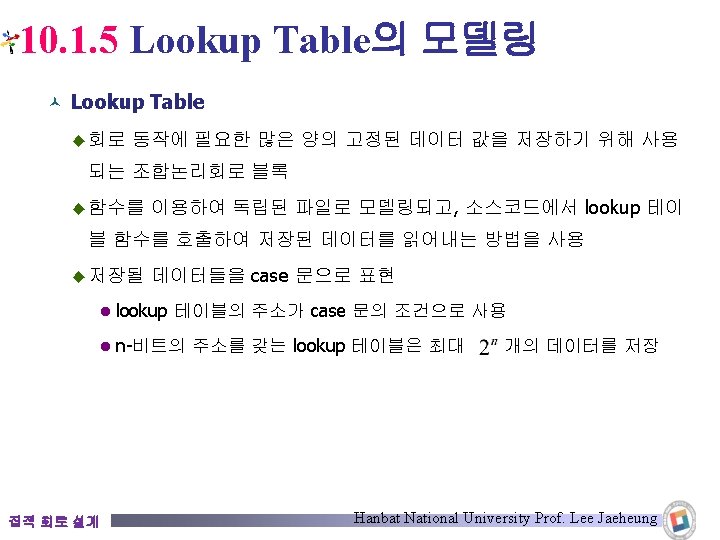

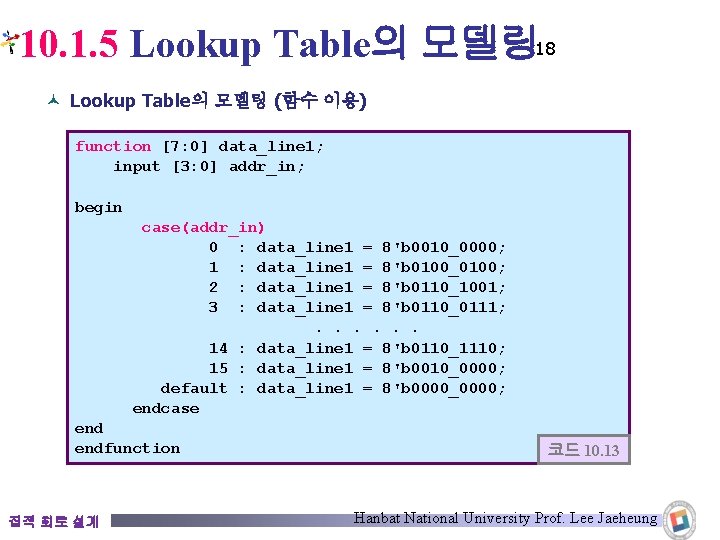

10. 1. 5 Lookup Table의 모델링18 © Lookup Table의 모델링 (함수 이용) function [7: 0] data_line 1; input [3: 0] addr_in; begin case(addr_in) 0 : data_line 1 = 8'b 0010_0000; 1 : data_line 1 = 8'b 0100_0100; 2 : data_line 1 = 8'b 0110_1001; 3 : data_line 1 = 8'b 0110_0111; . . . 14 : data_line 1 = 8'b 0110_1110; 15 : data_line 1 = 8'b 0010_0000; default : data_line 1 = 8'b 0000_0000; endcase endfunction 집적 회로 설계 코드 10. 13 Hanbat National University Prof. Lee Jaeheung

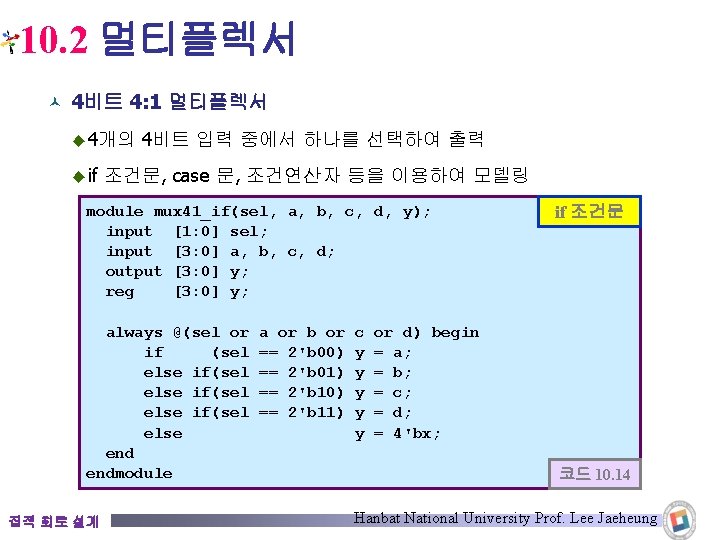

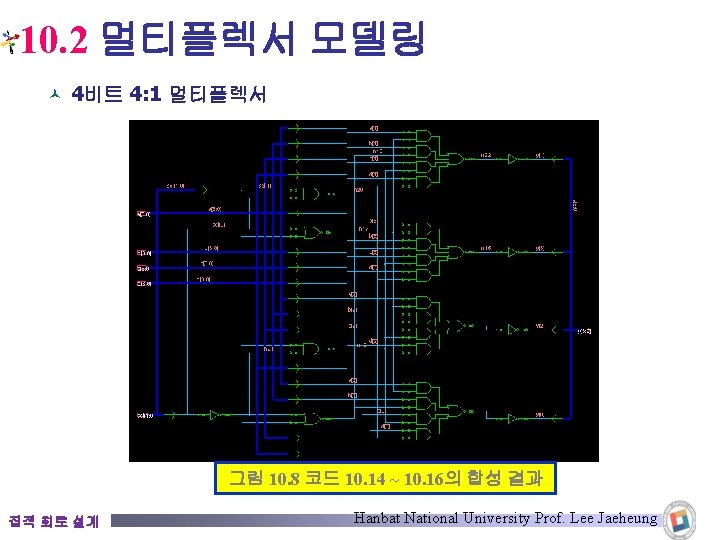

10. 2 멀티플렉서 © 4비트 4: 1 멀티플렉서 ◆ 4개의 ◆ if 4비트 입력 중에서 하나를 선택하여 출력 조건문, case 문, 조건연산자 등을 이용하여 모델링 module mux 41_if(sel, a, b, c, d, y); input [1: 0] sel; input [3: 0] a, b, c, d; output [3: 0] y; reg [3: 0] y; always @(sel or if (sel else if(sel else endmodule 집적 회로 설계 a or b or == 2'b 00) == 2'b 01) == 2'b 10) == 2'b 11) c y y y if 조건문 or d) begin = a; = b; = c; = d; = 4'bx; 코드 10. 14 Hanbat National University Prof. Lee Jaeheung

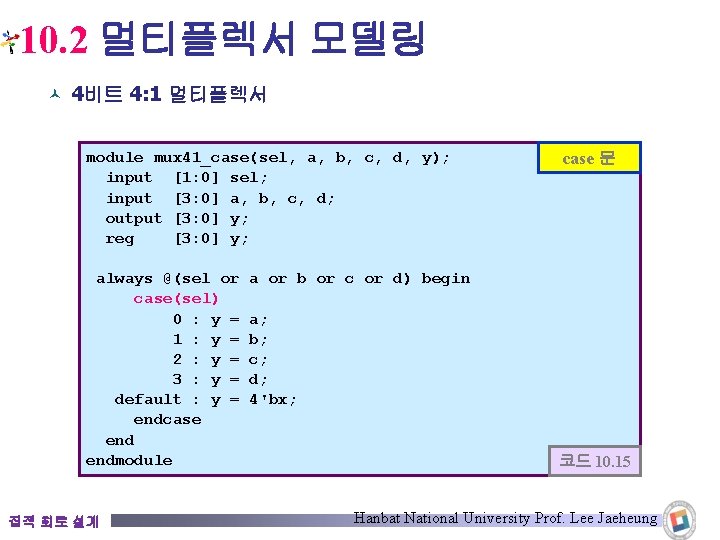

10. 2 멀티플렉서 모델링 © 4비트 4: 1 멀티플렉서 module mux 41_case(sel, a, b, c, d, y); input [1: 0] sel; input [3: 0] a, b, c, d; output [3: 0] y; reg [3: 0] y; always @(sel or case(sel) 0 : y = 1 : y = 2 : y = 3 : y = default : y = endcase endmodule 집적 회로 설계 case 문 a or b or c or d) begin a; b; c; d; 4'bx; 코드 10. 15 Hanbat National University Prof. Lee Jaeheung

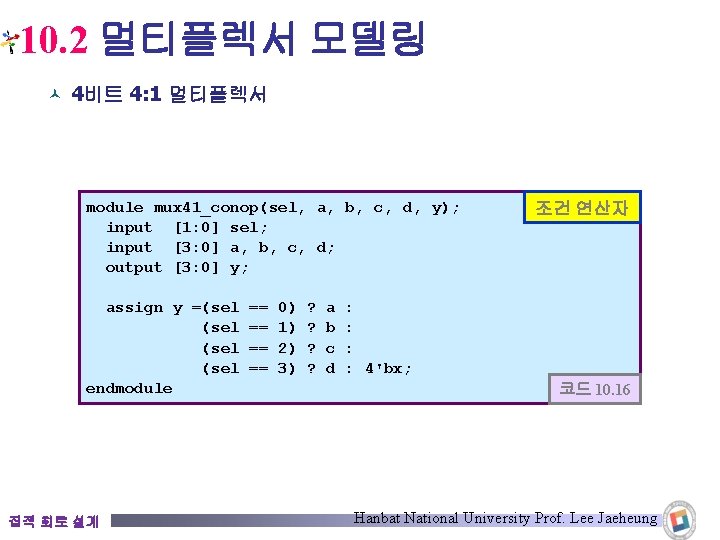

10. 2 멀티플렉서 모델링 © 4비트 4: 1 멀티플렉서 module mux 41_conop(sel, a, b, c, d, y); input [1: 0] sel; input [3: 0] a, b, c, d; output [3: 0] y; assign y =(sel endmodule 집적 회로 설계 == == 0) 1) 2) 3) ? ? a b c d 조건 연산자 : : 4'bx; 코드 10. 16 Hanbat National University Prof. Lee Jaeheung

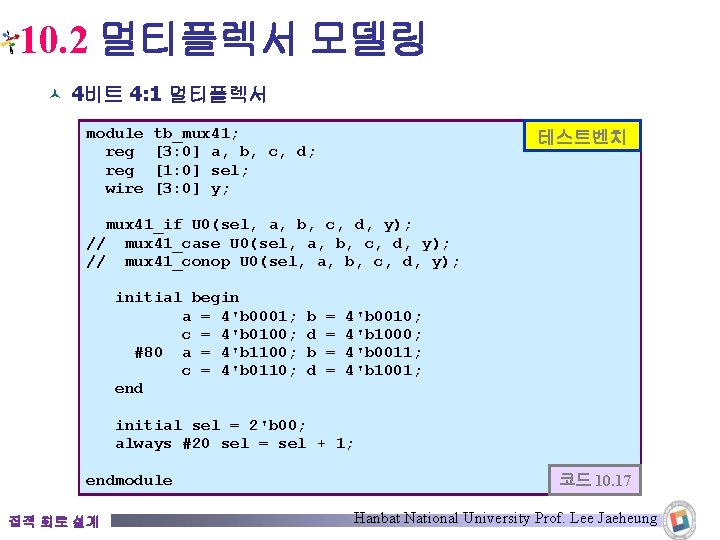

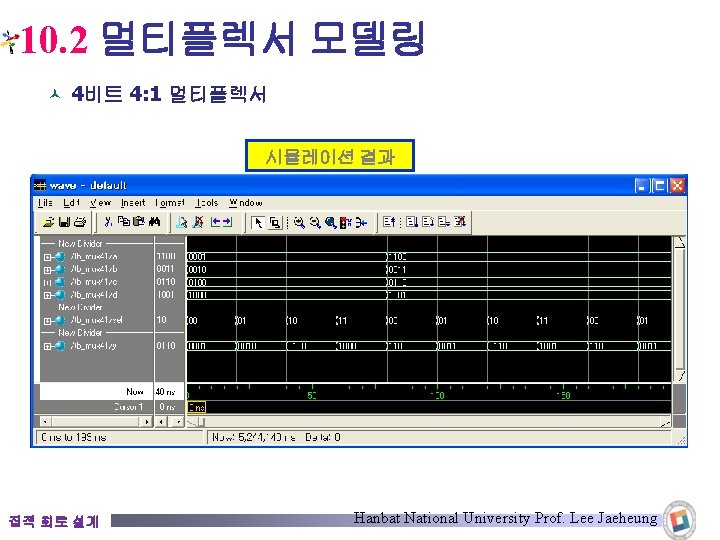

10. 2 멀티플렉서 모델링 © 4비트 4: 1 멀티플렉서 module reg wire tb_mux 41; [3: 0] a, b, c, d; [1: 0] sel; [3: 0] y; 테스트벤치 mux 41_if U 0(sel, a, b, c, d, y); // mux 41_case U 0(sel, a, b, c, d, y); // mux 41_conop U 0(sel, a, b, c, d, y); initial begin a = 4'b 0001; c = 4'b 0100; #80 a = 4'b 1100; c = 4'b 0110; end b d = = 4'b 0010; 4'b 1000; 4'b 0011; 4'b 1001; initial sel = 2'b 00; always #20 sel = sel + 1; endmodule 집적 회로 설계 코드 10. 17 Hanbat National University Prof. Lee Jaeheung

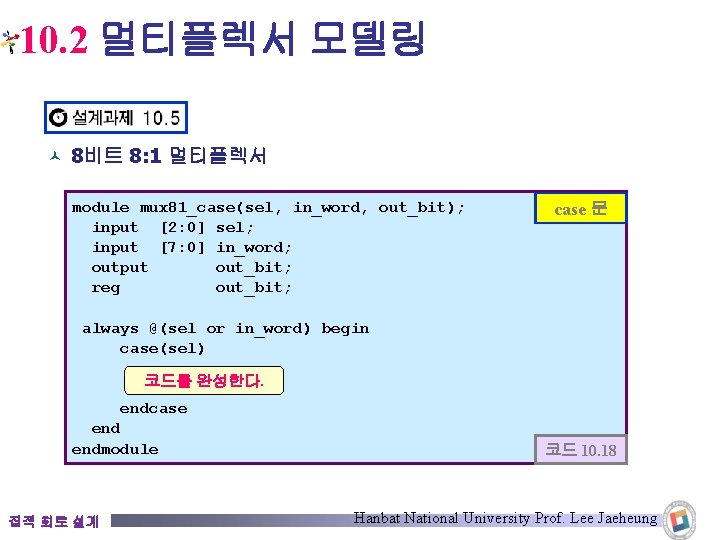

10. 2 멀티플렉서 모델링 © 8비트 8: 1 멀티플렉서 module mux 81_case(sel, in_word, out_bit); input [2: 0] sel; input [7: 0] in_word; output out_bit; reg out_bit; case 문 always @(sel or in_word) begin case(sel) 코드를 완성한다. endcase endmodule 집적 회로 설계 코드 10. 18 Hanbat National University Prof. Lee Jaeheung

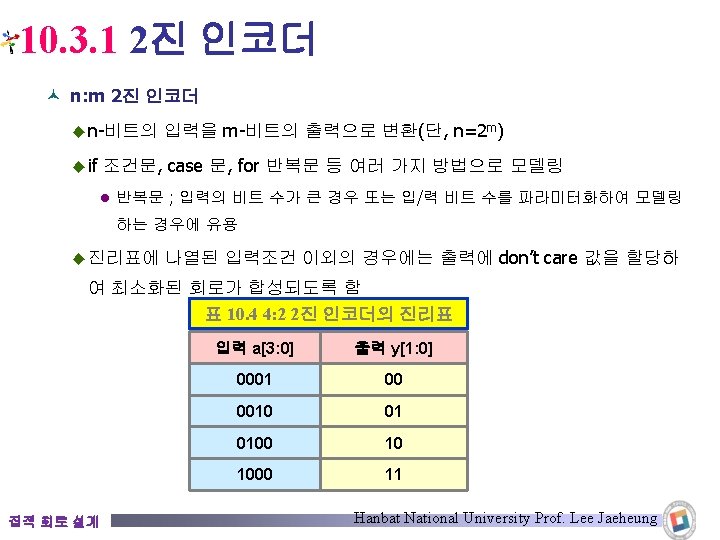

10. 3. 1 2진 인코더 © 4: 2 2진 인코더 case 문 module enc_4 to 2_case(a, y); input [3: 0] a; output [1: 0] y; reg [1: 0] y; always @(a) begin casex(a) 4'b 0001 : y 4'b 0010 : y 4'b 0100 : y 4'b 1000 : y default : y endcase endmodule 집적 회로 설계 = = = 0; 1; 2; 3; 2'bx; 코드 10. 19 if 조건문 module enc_4 to 2_if(a, y); input [3: 0] a; output [1: 0] y; reg [1: 0] y; always @(a) begin if (a == 4'b 0001) else if(a == 4'b 0010) else if(a == 4'b 0100) else if(a == 4'b 1000) else endmodule y y y = = = 0; 1; 2; 3; 2'bx; 코드 10. 20 Hanbat National University Prof. Lee Jaeheung

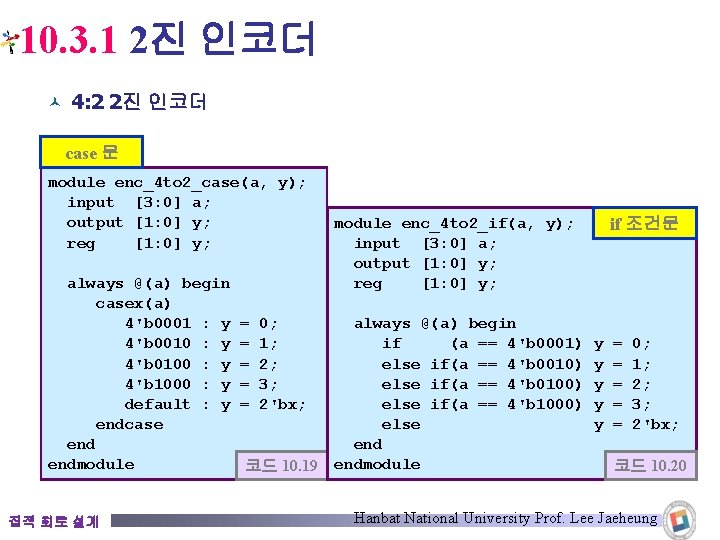

10. 3. 1 2진 인코더 © 4: 2 2진 인코더 for 반복문 module enc_4 to 2_for(a, y); input [3: 0] a; output [1: 0] y; reg [3: 0] temp; integer n; always @(a) begin temp = 4'b 0001; y = 2'bx; for(n = 0; n < 4; n = n + 1) begin if(a == temp) y = n; temp = temp << 1; end endmodule 집적 회로 설계 코드 10. 21 Hanbat National University Prof. Lee Jaeheung

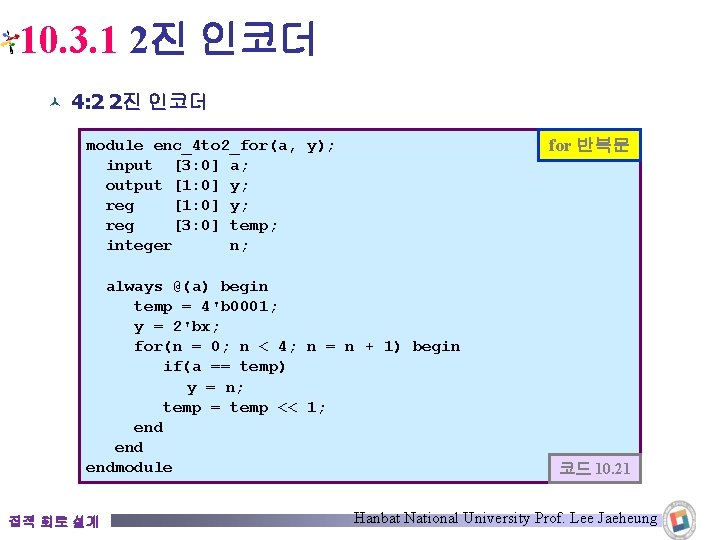

10. 3. 1 2진 인코더 © 4: 2 2진 인코더 module reg wire tb_enc_4 to 2; [3: 0] a; [1: 0] y; 테스트벤치 enc_4 to 2_case U 0(a, y); // enc_4 to 2_if U 0(a, y); // enc_4 to 2_for U 0(a, y); always begin a = 4'b 0001; #20 a = 4'b 0010; #20 a = 4'b 0100; #20 a = 4'b 1000; #20; endmodule 집적 회로 설계 코드 10. 22 Hanbat National University Prof. Lee Jaeheung

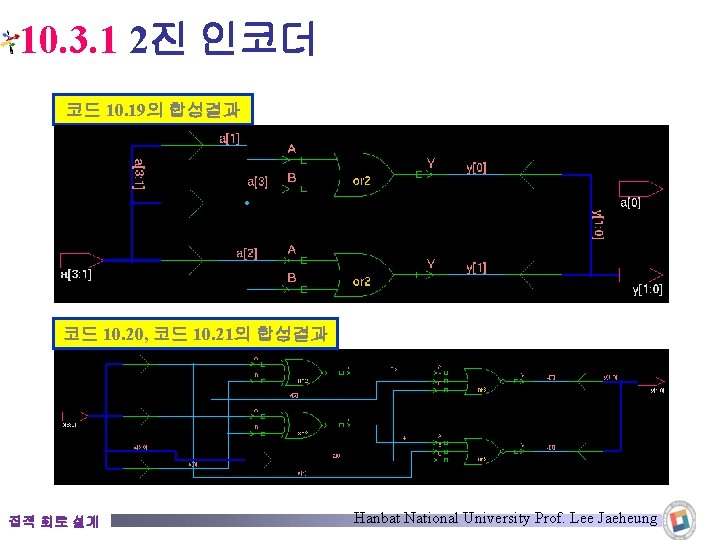

10. 3. 1 2진 인코더 코드 10. 19의 합성결과 코드 10. 20, 코드 10. 21의 합성결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

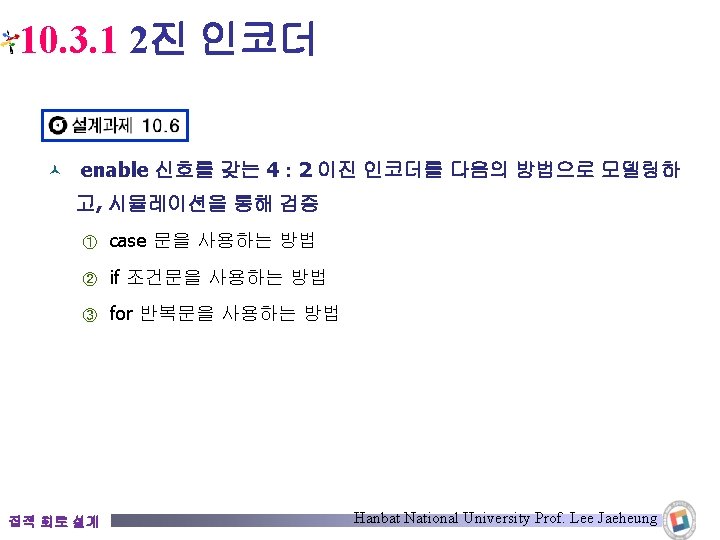

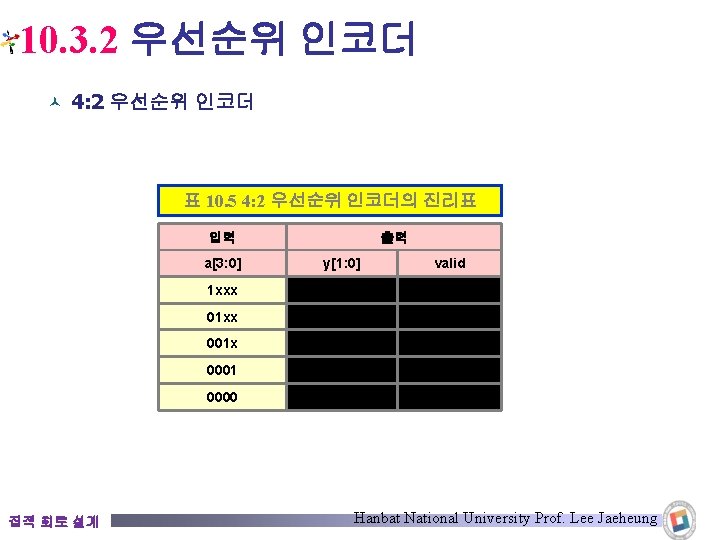

10. 3. 2 우선순위 인코더 © 4: 2 우선순위 인코더 표 10. 5 4: 2 우선순위 인코더의 진리표 입력 집적 회로 설계 출력 a[3: 0] y[1: 0] valid 1 xxx 11 1 01 xx 10 1 001 x 01 1 0001 0000 xx 0 Hanbat National University Prof. Lee Jaeheung

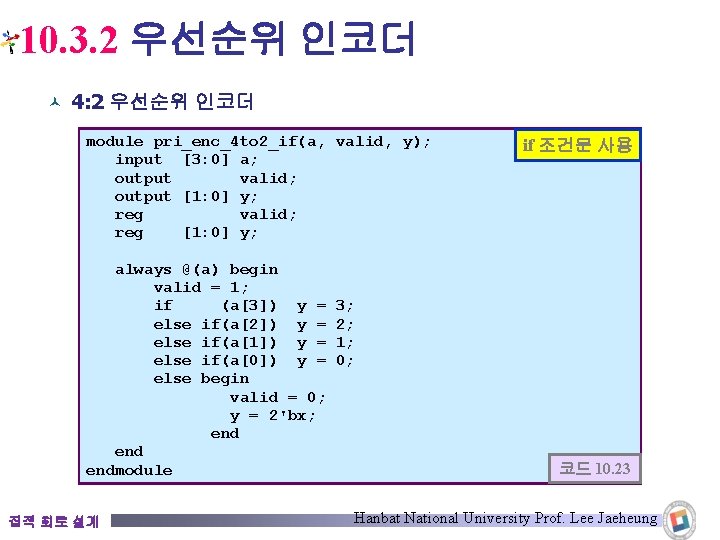

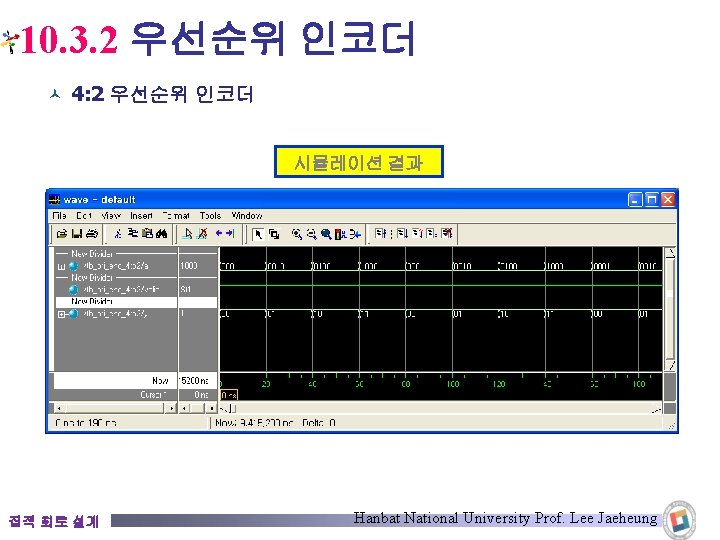

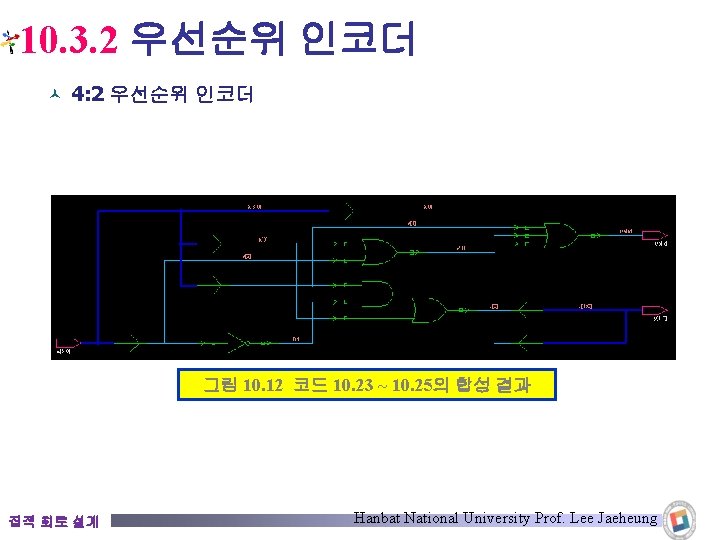

10. 3. 2 우선순위 인코더 © 4: 2 우선순위 인코더 module pri_enc_4 to 2_if(a, valid, y); input [3: 0] a; output valid; output [1: 0] y; reg valid; reg [1: 0] y; always @(a) begin valid = 1; if (a[3]) y = else if(a[2]) y = else if(a[1]) y = else if(a[0]) y = else begin valid = 0; y = 2'bx; end endmodule 집적 회로 설계 if 조건문 사용 3; 2; 1; 0; 코드 10. 23 Hanbat National University Prof. Lee Jaeheung

10. 3. 2 우선순위 인코더 © 4: 2 우선순위 인코더 module pri_enc_4 to 2_case(a, valid, y); input [3: 0] a; output valid; output [1: 0] y; reg valid; reg [1: 0] y; always @(a) begin valid = 1; casex(a) 4'b 1 xxx : y = 3; 4'b 01 xx : y = 2; 4'b 001 x : y = 1; 4'b 0001 : y = 0; default : begin valid = 0; y = 2'bx; endcase endmodule 집적 회로 설계 casex 문 사용 코드 10. 24 Hanbat National University Prof. Lee Jaeheung

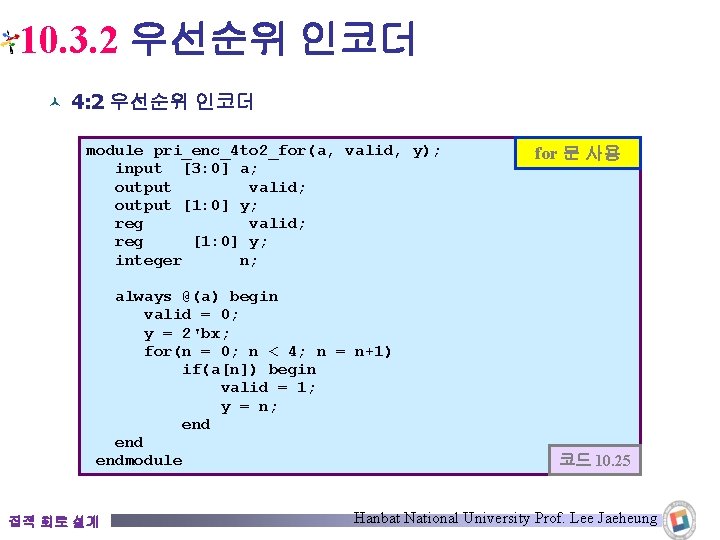

10. 3. 2 우선순위 인코더 © 4: 2 우선순위 인코더 module pri_enc_4 to 2_for(a, valid, y); input [3: 0] a; output valid; output [1: 0] y; reg valid; reg [1: 0] y; integer n; always @(a) begin valid = 0; y = 2'bx; for(n = 0; n < 4; n = n+1) if(a[n]) begin valid = 1; y = n; end endmodule 집적 회로 설계 for 문 사용 코드 10. 25 Hanbat National University Prof. Lee Jaeheung

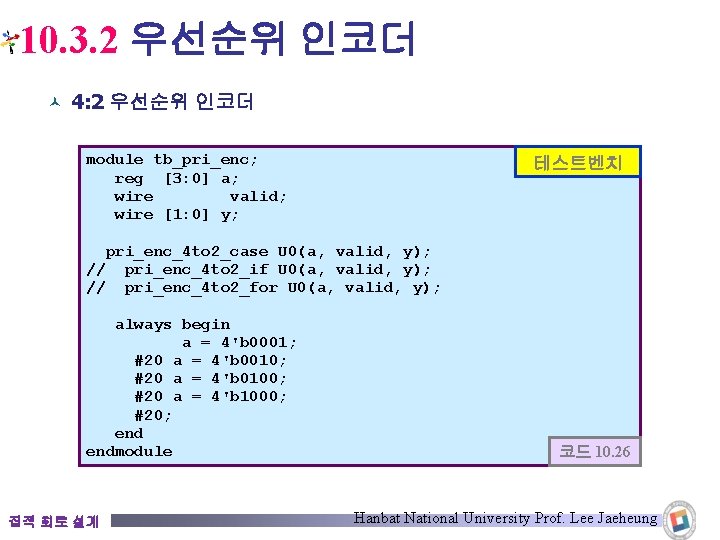

10. 3. 2 우선순위 인코더 © 4: 2 우선순위 인코더 module tb_pri_enc; reg [3: 0] a; wire valid; wire [1: 0] y; 테스트벤치 pri_enc_4 to 2_case U 0(a, valid, y); // pri_enc_4 to 2_if U 0(a, valid, y); // pri_enc_4 to 2_for U 0(a, valid, y); always begin a = 4'b 0001; #20 a = 4'b 0010; #20 a = 4'b 0100; #20 a = 4'b 1000; #20; endmodule 집적 회로 설계 코드 10. 26 Hanbat National University Prof. Lee Jaeheung

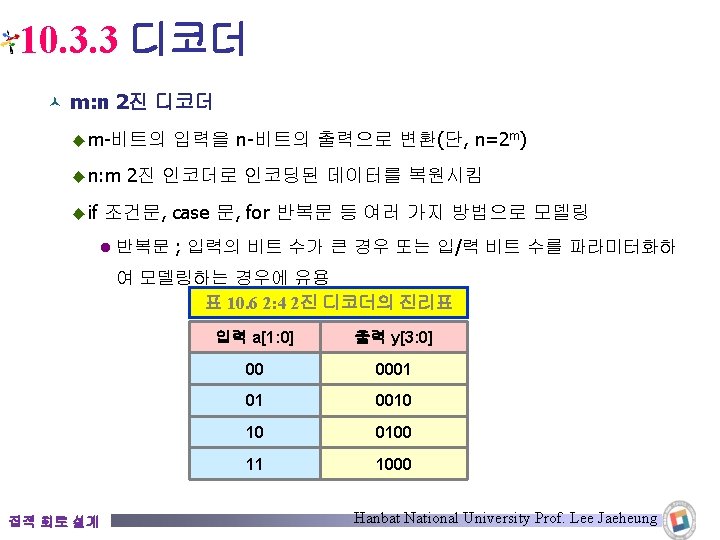

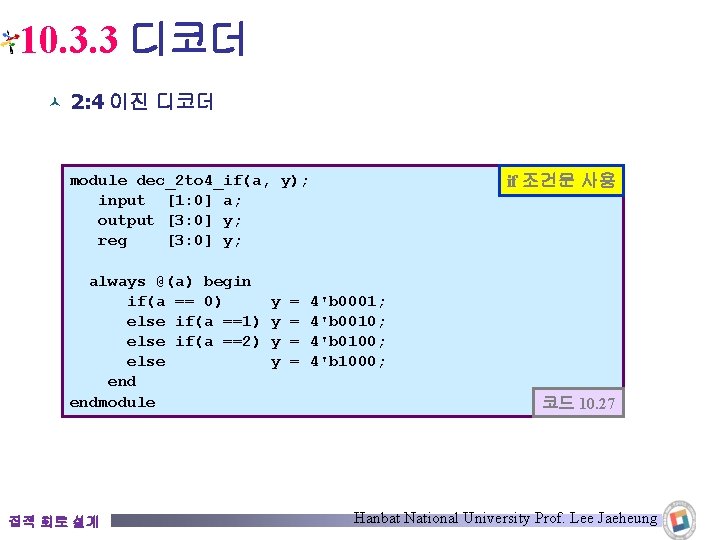

10. 3. 3 디코더 © 2: 4 이진 디코더 if 조건문 사용 module dec_2 to 4_if(a, y); input [1: 0] a; output [3: 0] y; reg [3: 0] y; always @(a) begin if(a == 0) else if(a ==1) else if(a ==2) else endmodule 집적 회로 설계 y y = = 4'b 0001; 4'b 0010; 4'b 0100; 4'b 1000; 코드 10. 27 Hanbat National University Prof. Lee Jaeheung

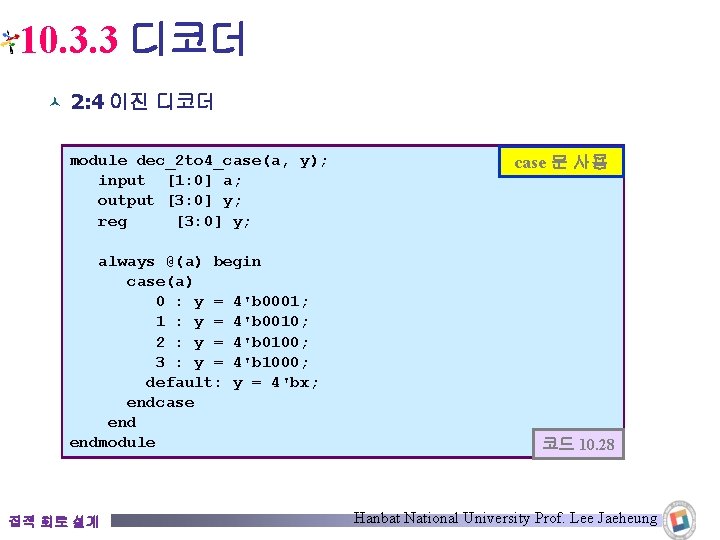

10. 3. 3 디코더 © 2: 4 이진 디코더 module dec_2 to 4_case(a, y); input [1: 0] a; output [3: 0] y; reg [3: 0] y; always @(a) begin case(a) 0 : y = 4'b 0001; 1 : y = 4'b 0010; 2 : y = 4'b 0100; 3 : y = 4'b 1000; default: y = 4'bx; endcase endmodule 집적 회로 설계 case 문 사용 코드 10. 28 Hanbat National University Prof. Lee Jaeheung

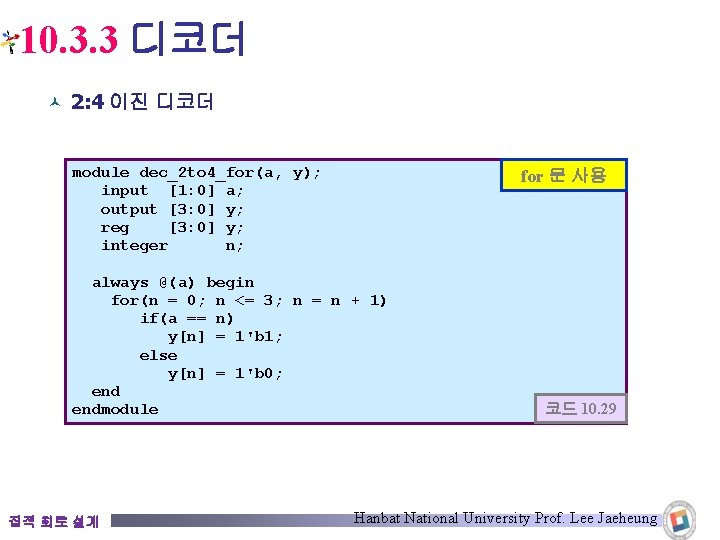

10. 3. 3 디코더 © 2: 4 이진 디코더 module dec_2 to 4_for(a, y); input [1: 0] a; output [3: 0] y; reg [3: 0] y; integer n; for 문 사용 always @(a) begin for(n = 0; n <= 3; n = n + 1) if(a == n) y[n] = 1'b 1; else y[n] = 1'b 0; endmodule 집적 회로 설계 코드 10. 29 Hanbat National University Prof. Lee Jaeheung

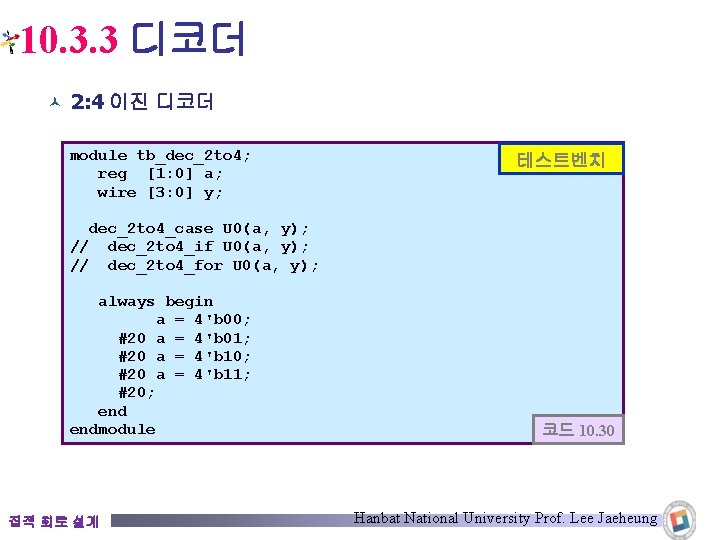

10. 3. 3 디코더 © 2: 4 이진 디코더 module tb_dec_2 to 4; reg [1: 0] a; wire [3: 0] y; 테스트벤치 dec_2 to 4_case U 0(a, y); // dec_2 to 4_if U 0(a, y); // dec_2 to 4_for U 0(a, y); always begin a = 4'b 00; #20 a = 4'b 01; #20 a = 4'b 10; #20 a = 4'b 11; #20; endmodule 집적 회로 설계 코드 10. 30 Hanbat National University Prof. Lee Jaeheung

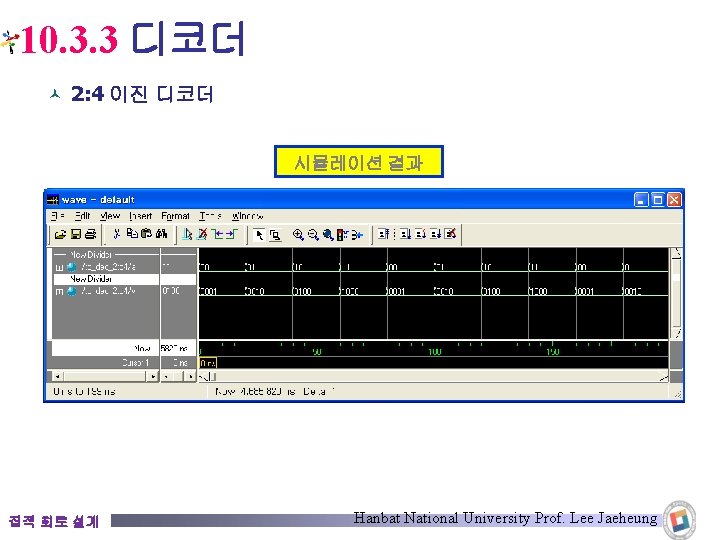

10. 3. 3 디코더 © 2: 4 이진 디코더 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

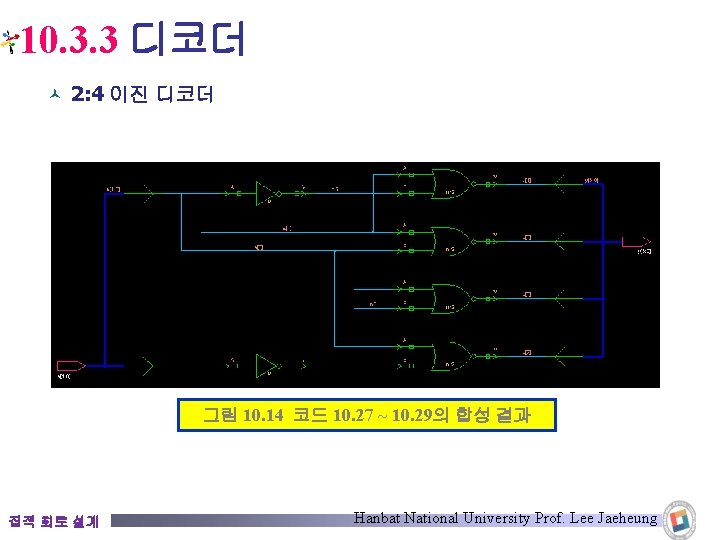

10. 3. 3 디코더 © 2: 4 이진 디코더 그림 10. 14 코드 10. 27 ~ 10. 29의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

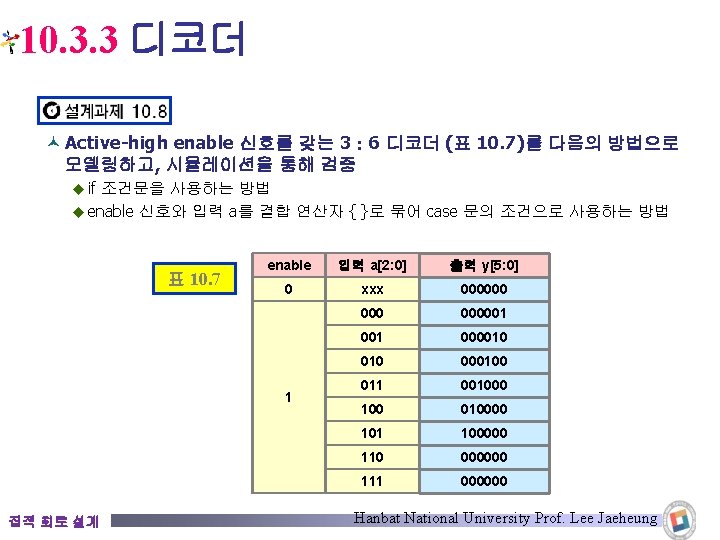

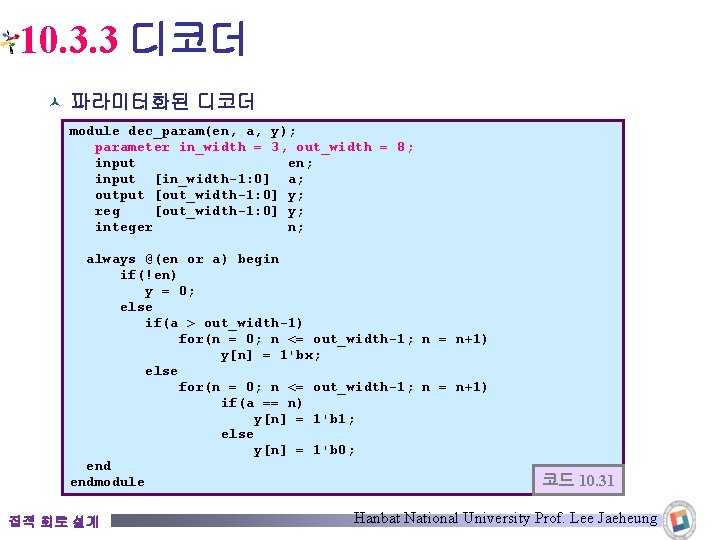

10. 3. 3 디코더 © 파라미터화된 디코더 module dec_param(en, a, y); parameter in_width = 3, out_width = 8; input en; input [in_width-1: 0] a; output [out_width-1: 0] y; reg [out_width-1: 0] y; integer n; always @(en or a) begin if(!en) y = 0; else if(a > out_width-1) for(n = 0; n <= out_width-1; n = n+1) y[n] = 1'bx; else for(n = 0; n <= out_width-1; n = n+1) if(a == n) y[n] = 1'b 1; else y[n] = 1'b 0; endmodule 집적 회로 설계 코드 10. 31 Hanbat National University Prof. Lee Jaeheung

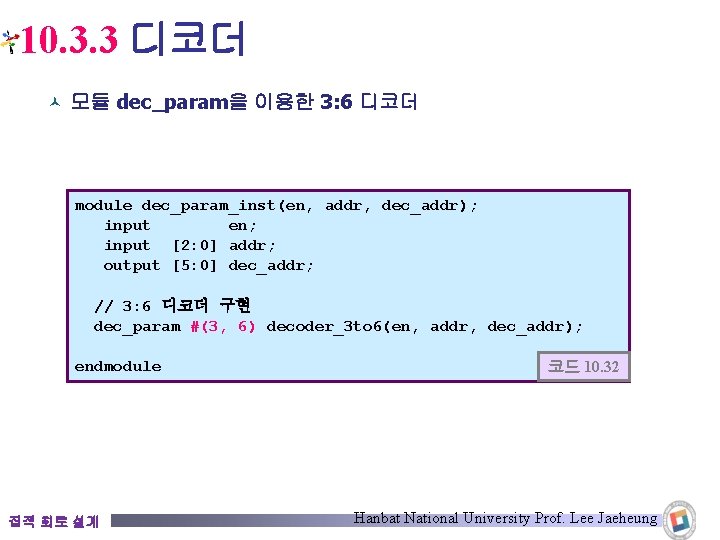

10. 3. 3 디코더 © 모듈 dec_param을 이용한 3: 6 디코더 module dec_param_inst(en, addr, dec_addr); input en; input [2: 0] addr; output [5: 0] dec_addr; // 3: 6 디코더 구현 dec_param #(3, 6) decoder_3 to 6(en, addr, dec_addr); endmodule 집적 회로 설계 코드 10. 32 Hanbat National University Prof. Lee Jaeheung

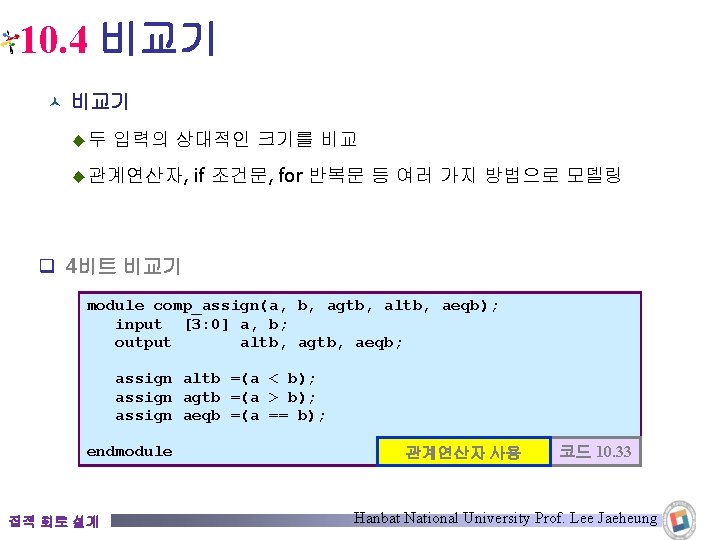

10. 4 비교기 © 비교기 ◆두 입력의 상대적인 크기를 비교 ◆ 관계연산자, if 조건문, for 반복문 등 여러 가지 방법으로 모델링 q 4비트 비교기 module comp_assign(a, b, agtb, altb, aeqb); input [3: 0] a, b; output altb, agtb, aeqb; assign altb =(a < b); assign agtb =(a > b); assign aeqb =(a == b); endmodule 집적 회로 설계 관계연산자 사용 코드 10. 33 Hanbat National University Prof. Lee Jaeheung

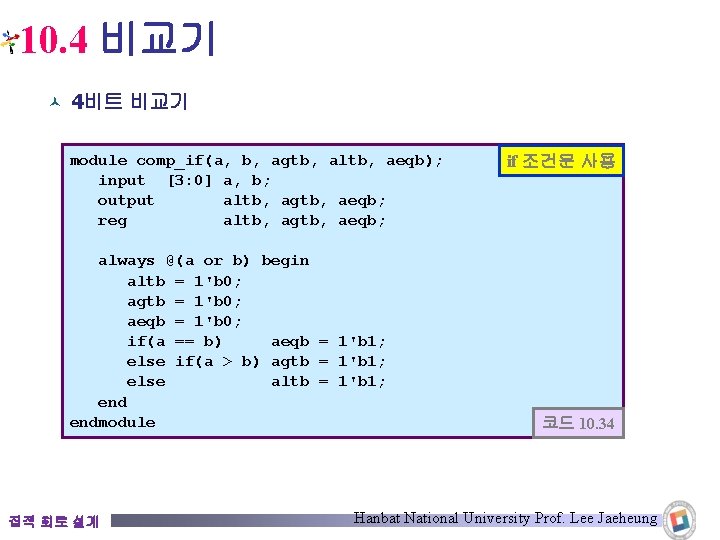

10. 4 비교기 © 4비트 비교기 module comp_if(a, b, agtb, altb, aeqb); input [3: 0] a, b; output altb, agtb, aeqb; reg altb, agtb, aeqb; always @(a or b) begin altb = 1'b 0; agtb = 1'b 0; aeqb = 1'b 0; if(a == b) aeqb = 1'b 1; else if(a > b) agtb = 1'b 1; else altb = 1'b 1; endmodule 집적 회로 설계 if 조건문 사용 코드 10. 34 Hanbat National University Prof. Lee Jaeheung

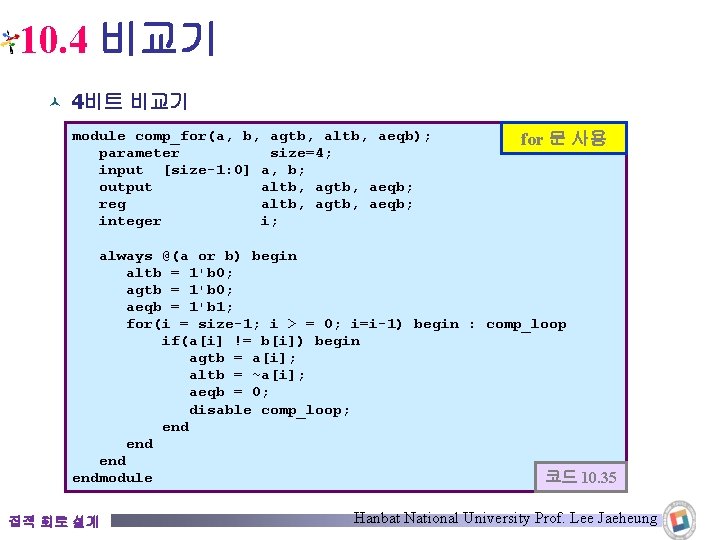

10. 4 비교기 © 4비트 비교기 module comp_for(a, b, agtb, altb, aeqb); parameter size=4; input [size-1: 0] a, b; output altb, agtb, aeqb; reg altb, agtb, aeqb; integer i; for 문 사용 always @(a or b) begin altb = 1'b 0; agtb = 1'b 0; aeqb = 1'b 1; for(i = size-1; i > = 0; i=i-1) begin : comp_loop if(a[i] != b[i]) begin agtb = a[i]; altb = ~a[i]; aeqb = 0; disable comp_loop; end endmodule 코드 10. 35 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

![10. 4 비교기 © 4비트 비교기 module tb_comp; reg [3: 0] a, b; wire 10. 4 비교기 © 4비트 비교기 module tb_comp; reg [3: 0] a, b; wire](http://slidetodoc.com/presentation_image/102bf6cc135f767430cc551e1de42dbc/image-53.jpg)

10. 4 비교기 © 4비트 비교기 module tb_comp; reg [3: 0] a, b; wire agtb, altb, aeqb; // // 테스트벤치 comp_assign Uo(a, b, agtb, altb, aeqb); comp_if Uo(a, b, agtb, altb, aeqb); comp_for Uo(a, b, agtb, altb, aeqb); always begin a = 4'b 0001; b = 4'b 1001; #20 a = 4'b 0010; b = 4'b 0000; #20 a = 4'b 1100; b = 4'b 1101; #20 a = 4'b 1001; b = 4'b 1001; #20 a = 4'b 0111; b = 4'b 0100; #20 a = 4'b 1111; b = 4'b 1111; #20 a = 4'b 1101; b = 4'b 1001; #20 a = 4'b 0000; b = 4'b 0000; #20 a = 4'b 1010; b = 4'b 1010; #20 a = 4'b 0001; b = 4'b 1011; #20; endmodule 집적 회로 설계 코드 10. 36 Hanbat National University Prof. Lee Jaeheung

10. 4 비교기 © 4비트 비교기 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

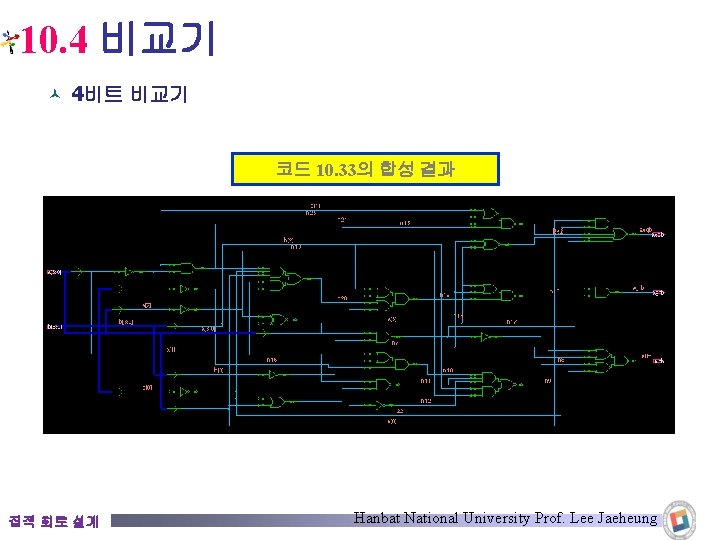

10. 4 비교기 © 4비트 비교기 코드 10. 33의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

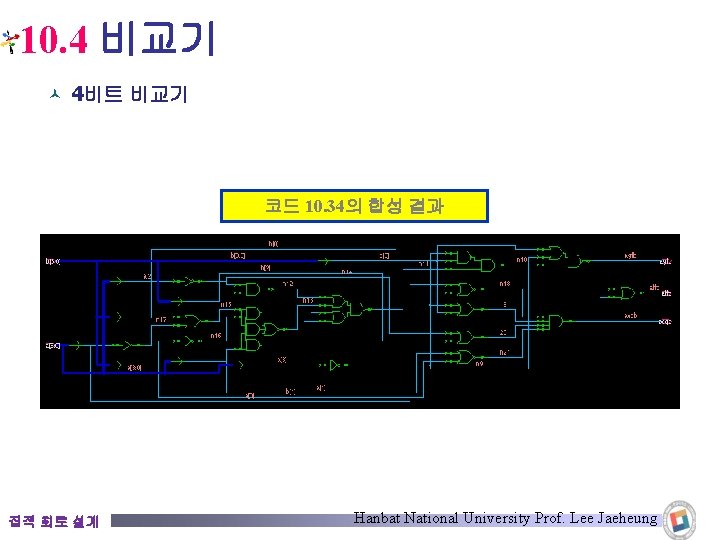

10. 4 비교기 © 4비트 비교기 코드 10. 34의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

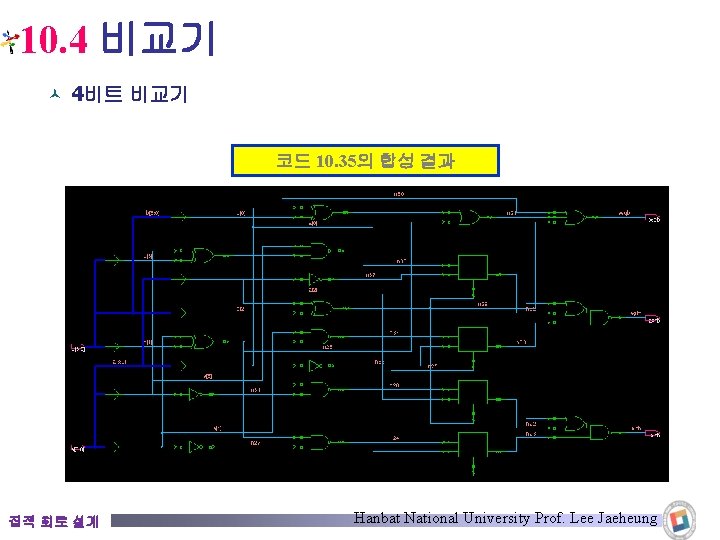

10. 4 비교기 © 4비트 비교기 코드 10. 35의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

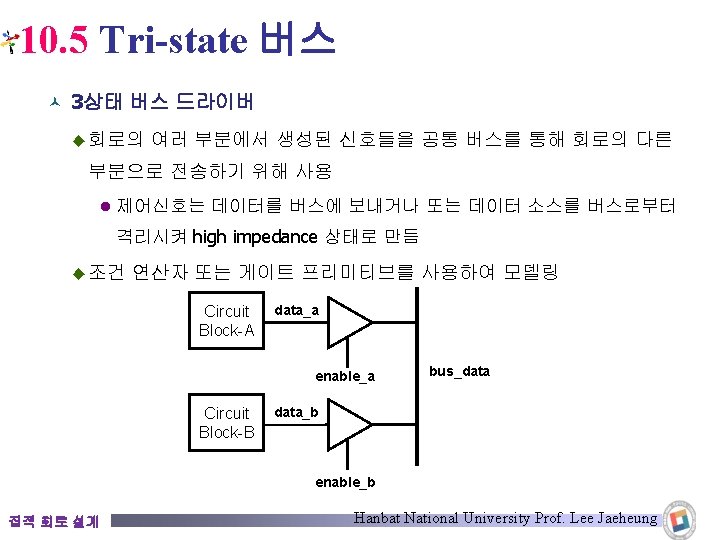

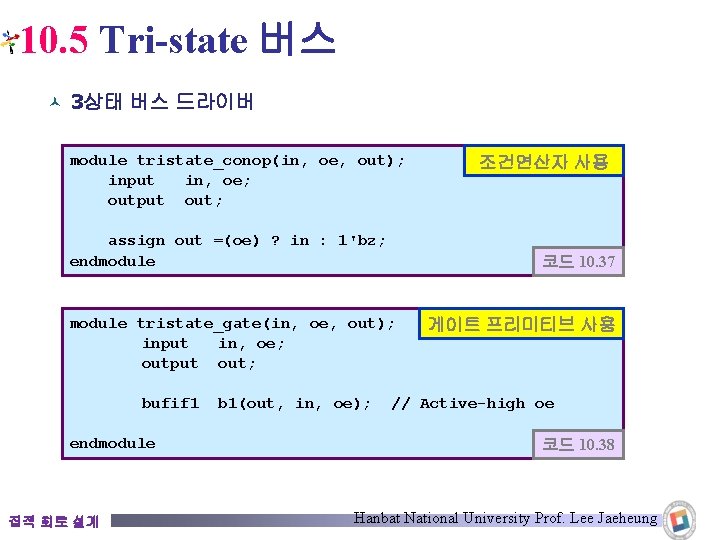

10. 5 Tri-state 버스 © 3상태 버스 드라이버 module tristate_conop(in, oe, out); input in, oe; output out; assign out =(oe) ? in : 1'bz; endmodule 코드 10. 37 module tristate_gate(in, oe, out); input in, oe; output out; bufif 1 endmodule 집적 회로 설계 b 1(out, in, oe); 조건연산자 사용 게이트 프리미티브 사용 // Active-high oe 코드 10. 38 Hanbat National University Prof. Lee Jaeheung

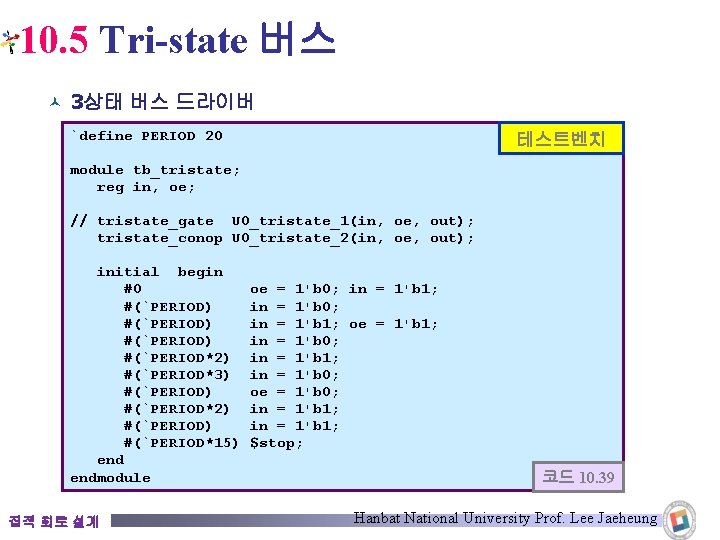

10. 5 Tri-state 버스 © 3상태 버스 드라이버 `define PERIOD 20 테스트벤치 module tb_tristate; reg in, oe; // tristate_gate U 0_tristate_1(in, oe, out); tristate_conop U 0_tristate_2(in, oe, out); initial begin #0 #(`PERIOD) #(`PERIOD*2) #(`PERIOD*3) #(`PERIOD*2) #(`PERIOD*15) endmodule 집적 회로 설계 oe = 1'b 0; in = 1'b 1; in = 1'b 0; in = 1'b 1; oe = 1'b 1; in = 1'b 0; in = 1'b 1; in = 1'b 0; oe = 1'b 0; in = 1'b 1; $stop; 코드 10. 39 Hanbat National University Prof. Lee Jaeheung

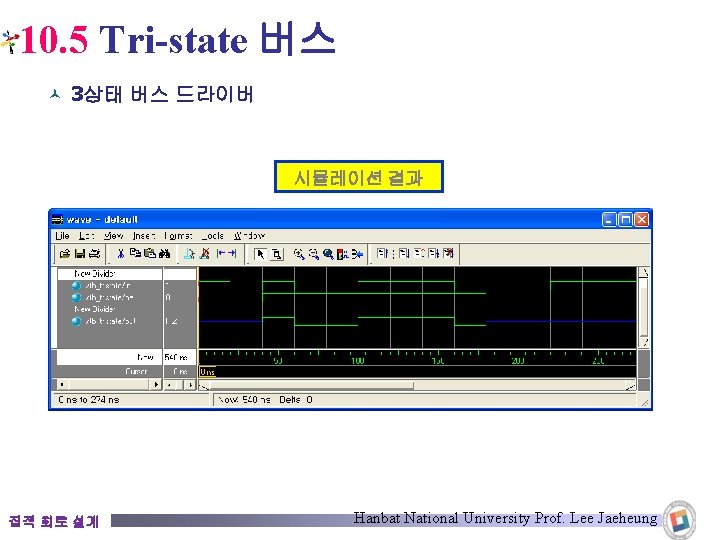

10. 5 Tri-state 버스 © 3상태 버스 드라이버 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

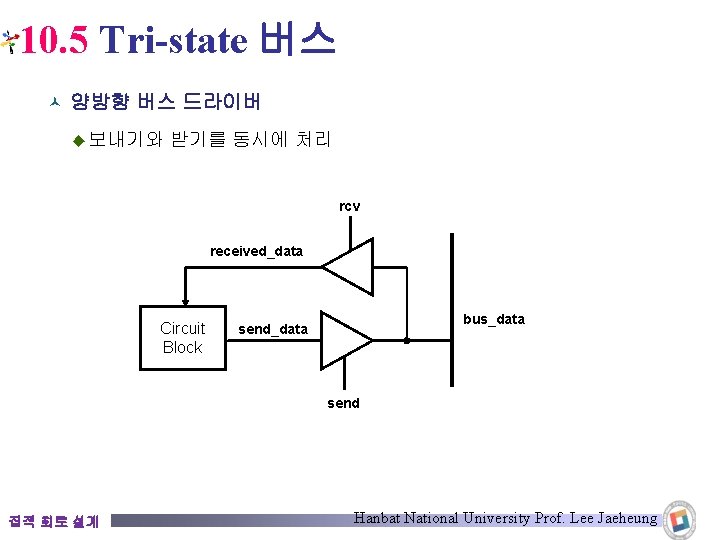

10. 5 Tri-state 버스 © 양방향 버스 드라이버 ◆ 보내기와 받기를 동시에 처리 rcv received_data Circuit Block bus_data send 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

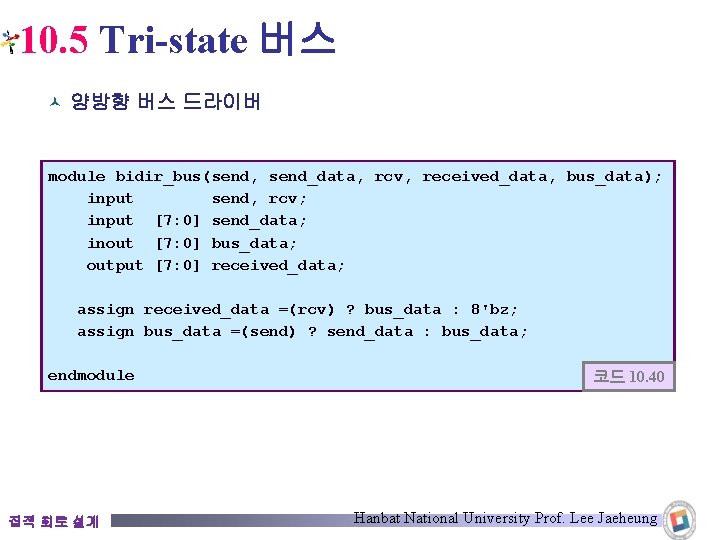

10. 5 Tri-state 버스 © 양방향 버스 드라이버 module bidir_bus(send, send_data, rcv, received_data, bus_data); input send, rcv; input [7: 0] send_data; inout [7: 0] bus_data; output [7: 0] received_data; assign received_data =(rcv) ? bus_data : 8'bz; assign bus_data =(send) ? send_data : bus_data; endmodule 집적 회로 설계 코드 10. 40 Hanbat National University Prof. Lee Jaeheung

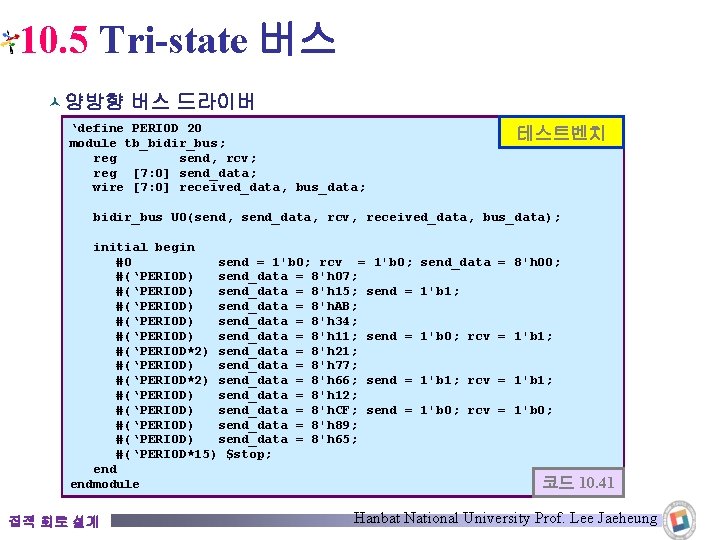

10. 5 Tri-state 버스 © 양방향 버스 드라이버 ‘define PERIOD 20 module tb_bidir_bus; reg send, rcv; reg [7: 0] send_data; wire [7: 0] received_data, bus_data; 테스트벤치 bidir_bus U 0(send, send_data, rcv, received_data, bus_data); initial begin #0 send = 1'b 0; rcv = 1'b 0; #(‘PERIOD) send_data = 8'h 07; #(‘PERIOD) send_data = 8'h 15; send = #(‘PERIOD) send_data = 8'h. AB; #(‘PERIOD) send_data = 8'h 34; #(‘PERIOD) send_data = 8'h 11; send = #(‘PERIOD*2) send_data = 8'h 21; #(‘PERIOD) send_data = 8'h 77; #(‘PERIOD*2) send_data = 8'h 66; send = #(‘PERIOD) send_data = 8'h 12; #(‘PERIOD) send_data = 8'h. CF; send = #(‘PERIOD) send_data = 8'h 89; #(‘PERIOD) send_data = 8'h 65; #(‘PERIOD*15) $stop; endmodule 집적 회로 설계 send_data = 8'h 00; 1'b 1; 1'b 0; rcv = 1'b 1; 1'b 0; rcv = 1'b 0; 코드 10. 41 Hanbat National University Prof. Lee Jaeheung

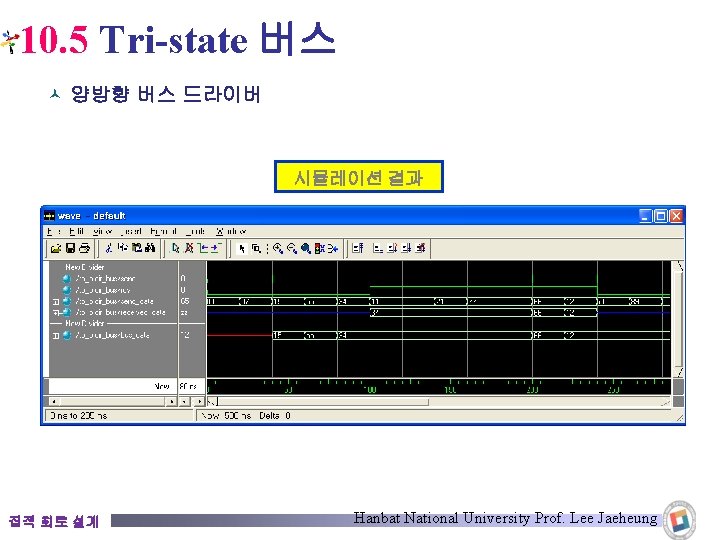

10. 5 Tri-state 버스 © 양방향 버스 드라이버 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

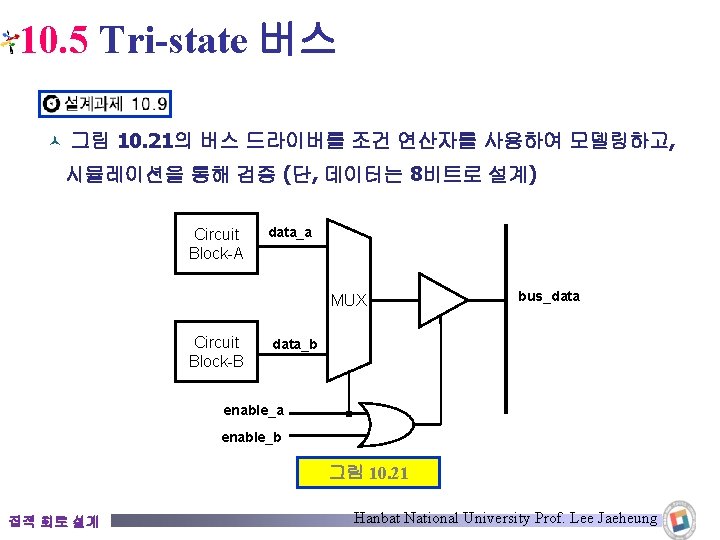

10. 5 Tri-state 버스 © 그림 10. 21의 버스 드라이버를 조건 연산자를 사용하여 모델링하고, 시뮬레이션을 통해 검증 (단, 데이터는 8비트로 설계) Circuit Block-A data_a MUX Circuit Block-B bus_data_b enable_a enable_b 그림 10. 21 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

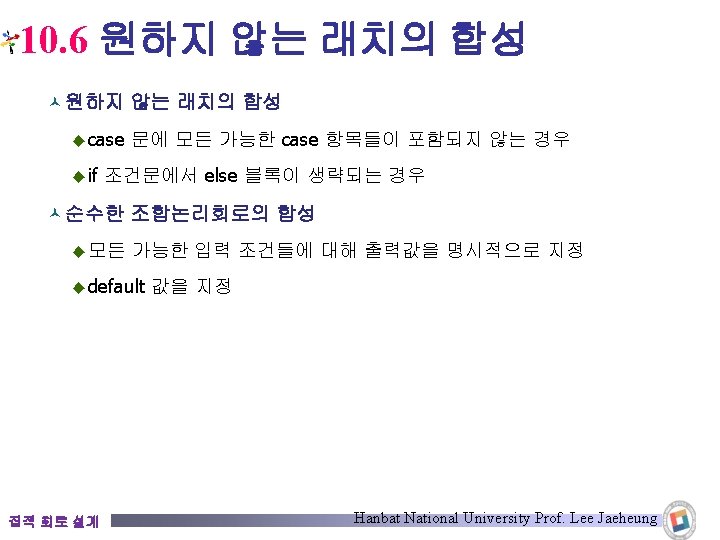

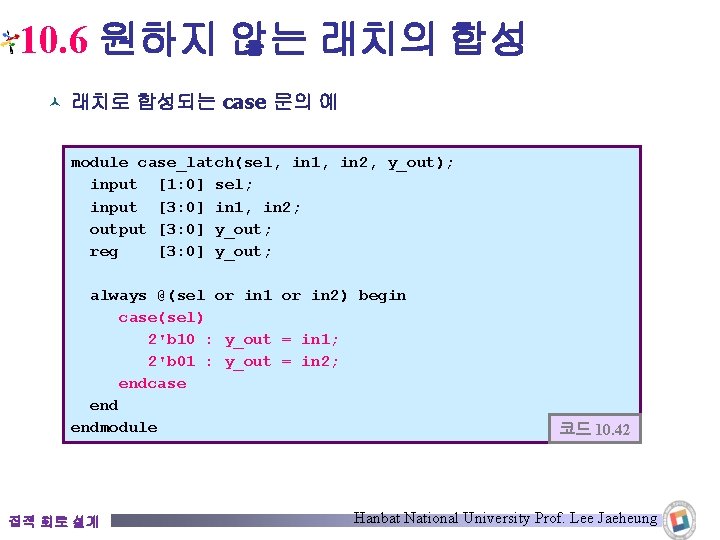

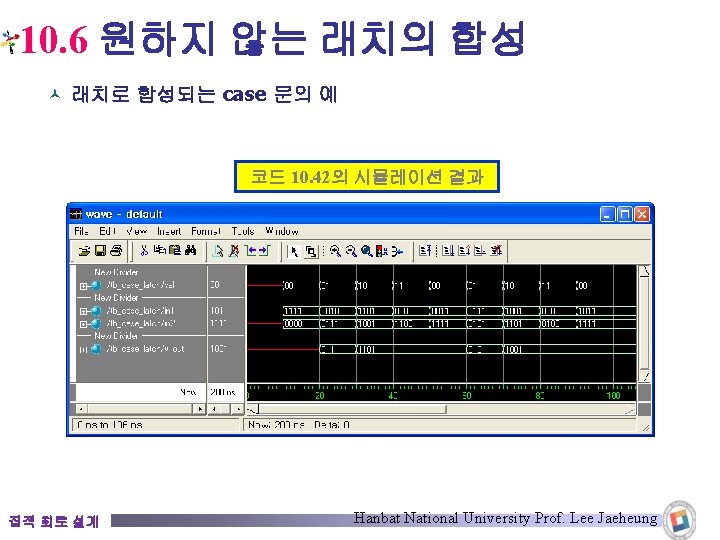

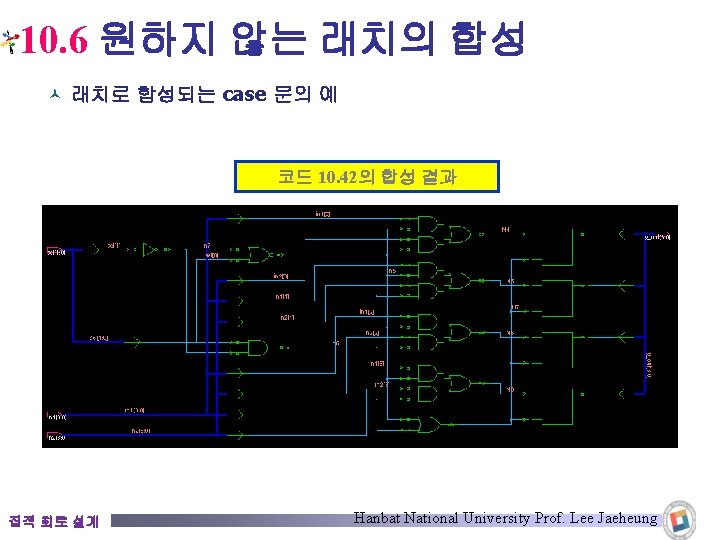

10. 6 원하지 않는 래치의 합성 © 래치로 합성되는 case 문의 예 module case_latch(sel, in 1, in 2, y_out); input [1: 0] sel; input [3: 0] in 1, in 2; output [3: 0] y_out; reg [3: 0] y_out; always @(sel or in 1 or in 2) begin case(sel) 2'b 10 : y_out = in 1; 2'b 01 : y_out = in 2; endcase endmodule 집적 회로 설계 코드 10. 42 Hanbat National University Prof. Lee Jaeheung

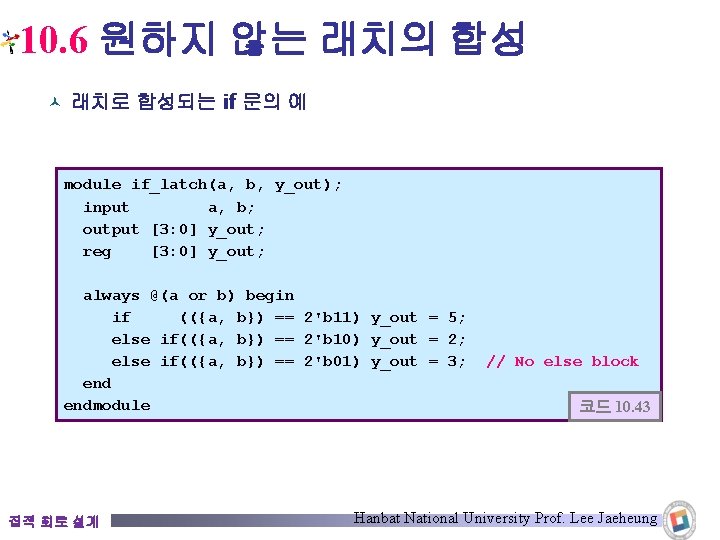

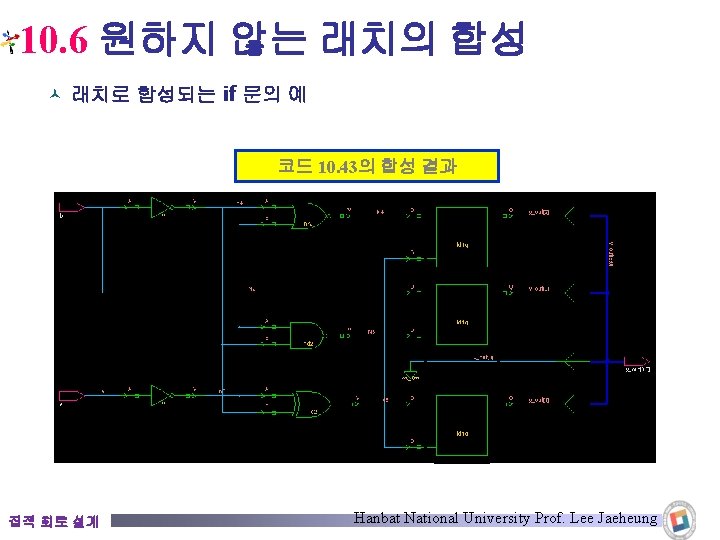

10. 6 원하지 않는 래치의 합성 © 래치로 합성되는 if 문의 예 module if_latch(a, b, y_out); input a, b; output [3: 0] y_out; reg [3: 0] y_out; always @(a or b) begin if (({a, b}) == 2'b 11) y_out = 5; else if(({a, b}) == 2'b 10) y_out = 2; else if(({a, b}) == 2'b 01) y_out = 3; endmodule 집적 회로 설계 // No else block 코드 10. 43 Hanbat National University Prof. Lee Jaeheung

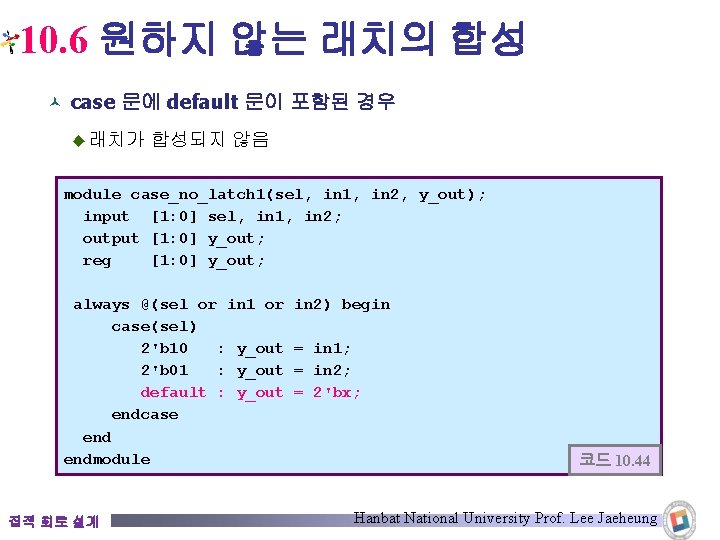

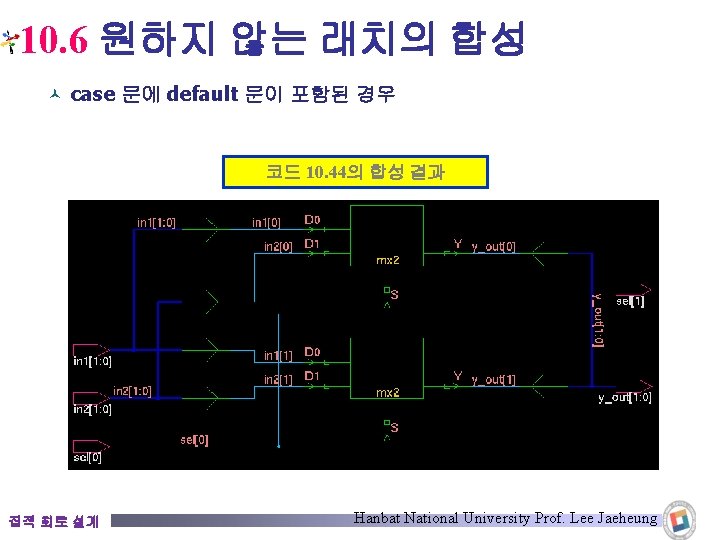

10. 6 원하지 않는 래치의 합성 © case 문에 default 문이 포함된 경우 ◆ 래치가 합성되지 않음 module case_no_latch 1(sel, in 1, in 2, y_out); input [1: 0] sel, in 1, in 2; output [1: 0] y_out; reg [1: 0] y_out; always @(sel or in 1 or case(sel) 2'b 10 : y_out 2'b 01 : y_out default : y_out endcase endmodule 집적 회로 설계 in 2) begin = in 1; = in 2; = 2'bx; 코드 10. 44 Hanbat National University Prof. Lee Jaeheung

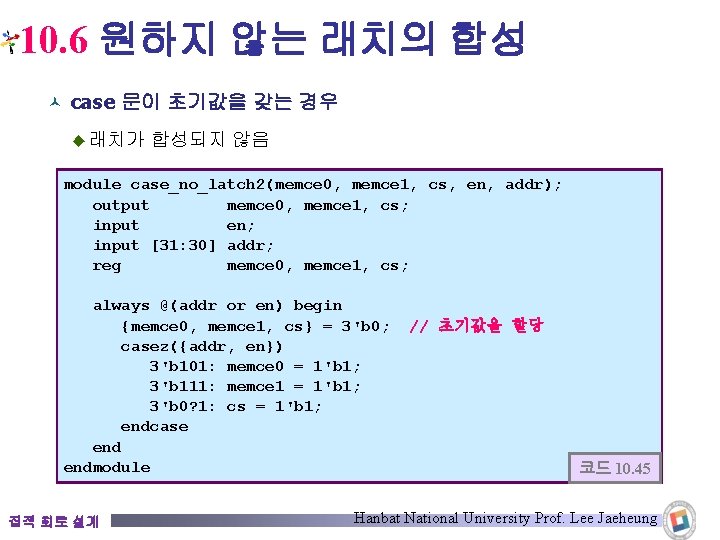

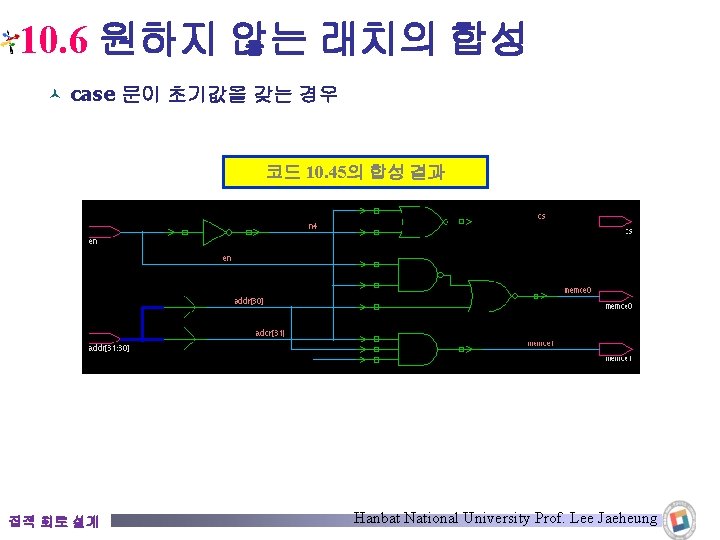

10. 6 원하지 않는 래치의 합성 © case 문이 초기값을 갖는 경우 ◆ 래치가 합성되지 않음 module case_no_latch 2(memce 0, memce 1, cs, en, addr); output memce 0, memce 1, cs; input en; input [31: 30] addr; reg memce 0, memce 1, cs; always @(addr or en) begin {memce 0, memce 1, cs} = 3'b 0; casez({addr, en}) 3'b 101: memce 0 = 1'b 1; 3'b 111: memce 1 = 1'b 1; 3'b 0? 1: cs = 1'b 1; endcase endmodule 집적 회로 설계 // 초기값을 할당 코드 10. 45 Hanbat National University Prof. Lee Jaeheung

- Slides: 76