Sun HyeSeung Hanbat National University Prof Lee Jaeheung

순차회로 모델링 한밭대학교 반도체설계실 Sun, Hye-Seung Hanbat National University Prof. Lee Jaeheung

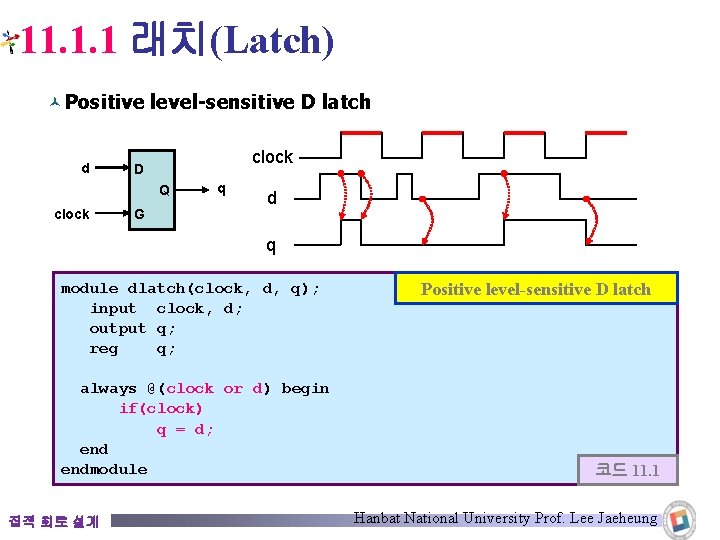

11. 1. 1 래치(Latch) © Positive level-sensitive D latch d clock D Q clock G q d q module dlatch(clock, d, q); input clock, d; output q; reg q; always @(clock or d) begin if(clock) q = d; endmodule 집적 회로 설계 Positive level-sensitive D latch 코드 11. 1 Hanbat National University Prof. Lee Jaeheung

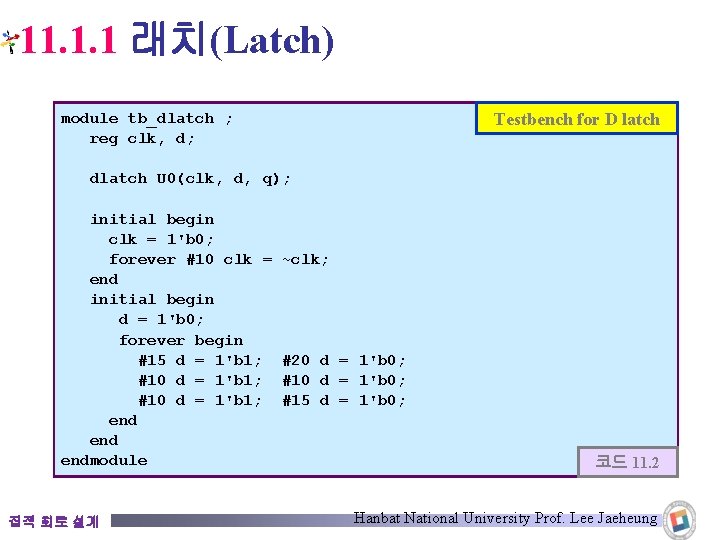

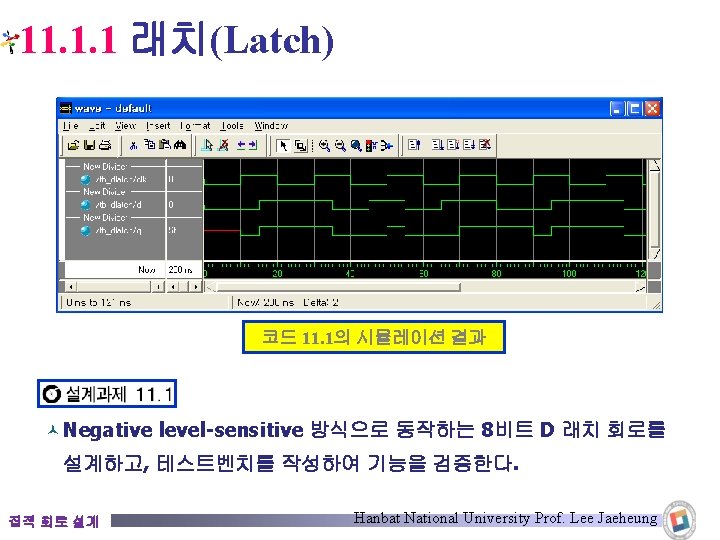

11. 1. 1 래치(Latch) Testbench for D latch module tb_dlatch ; reg clk, d; dlatch U 0(clk, d, q); initial begin clk = 1'b 0; forever #10 clk = end initial begin d = 1'b 0; forever begin #15 d = 1'b 1; #10 d = 1'b 1; end endmodule 집적 회로 설계 ~clk; #20 d = 1'b 0; #15 d = 1'b 0; 코드 11. 2 Hanbat National University Prof. Lee Jaeheung

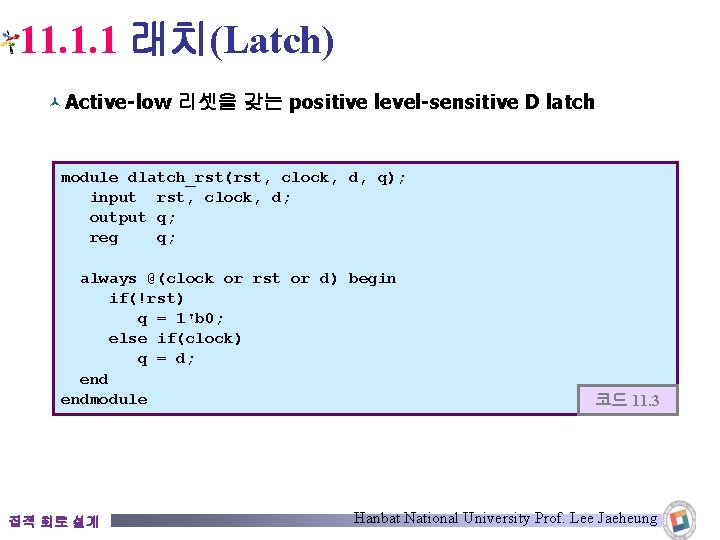

11. 1. 1 래치(Latch) © Active-low 리셋을 갖는 positive level-sensitive D latch module dlatch_rst(rst, clock, d, q); input rst, clock, d; output q; reg q; always @(clock or rst or d) begin if(!rst) q = 1'b 0; else if(clock) q = d; endmodule 집적 회로 설계 코드 11. 3 Hanbat National University Prof. Lee Jaeheung

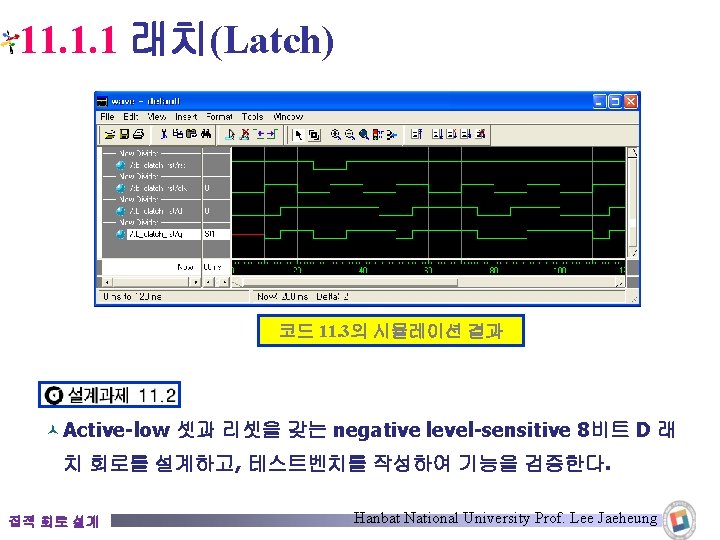

11. 1. 1 래치(Latch) © Latch가 포함된 회로에 blocking 할당문이 사용된 경우 코드 11. 4 module latch_blk(en, a, b, c, y); input en, a, b, c; output y; reg m, y; always @(en or a or b or c) begin if(en) begin m = ~(a | b); y = ~(m & c); end endmodule 합성 결과 Latch 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

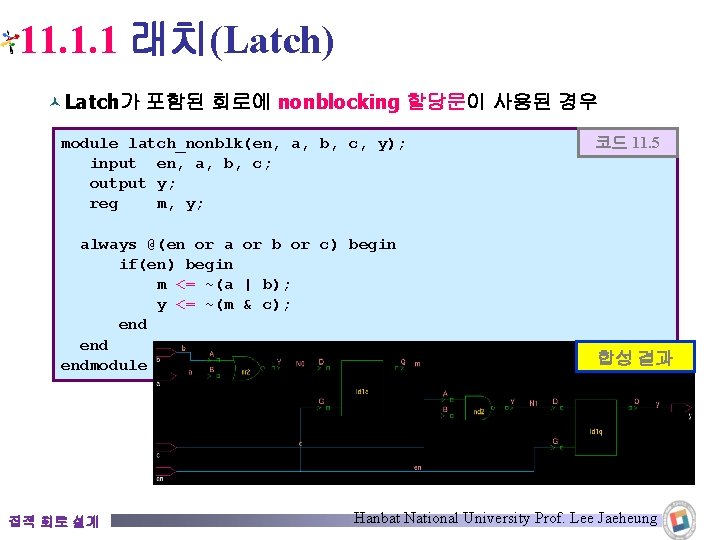

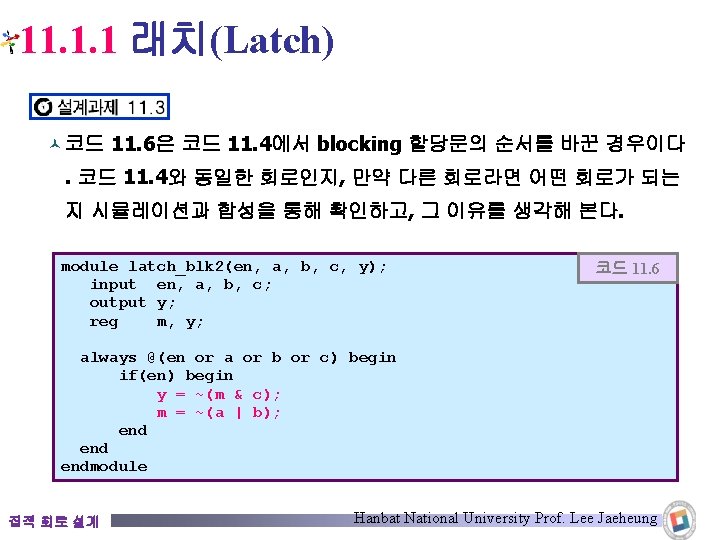

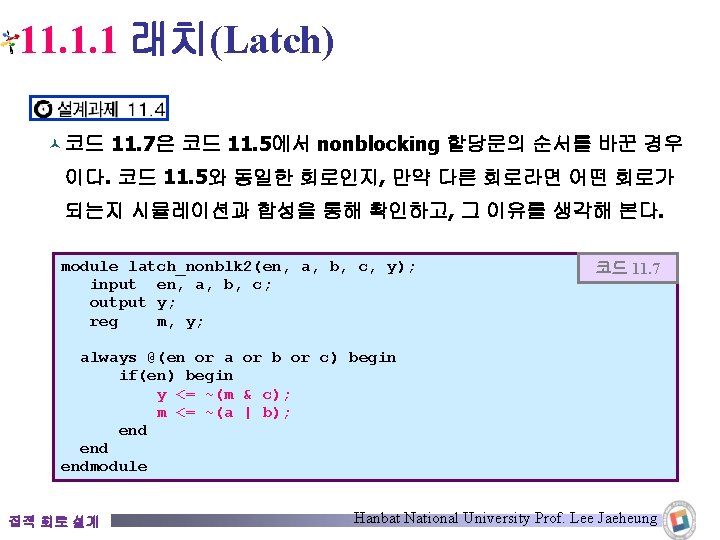

11. 1. 1 래치(Latch) © Latch가 포함된 회로에 nonblocking 할당문이 사용된 경우 module latch_nonblk(en, a, b, c, y); input en, a, b, c; output y; reg m, y; always @(en or a or b or c) begin if(en) begin m <= ~(a | b); y <= ~(m & c); end endmodule Latch 코드 11. 5 합성 결과 Latch 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

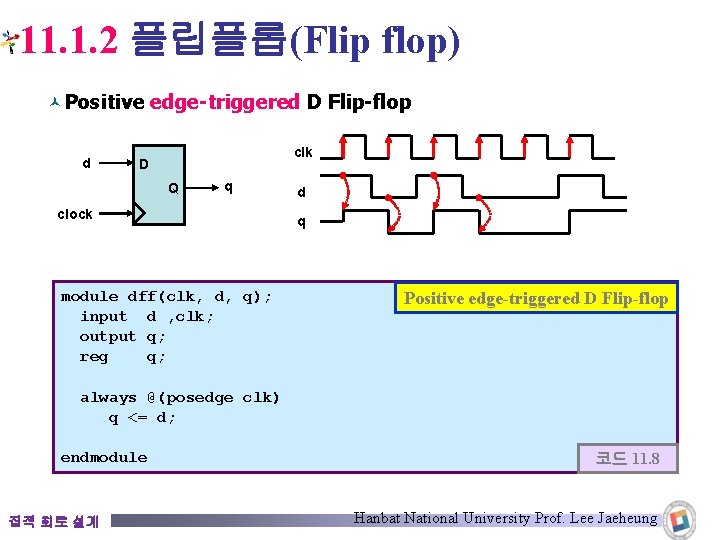

11. 1. 2 플립플롭(Flip flop) © Positive edge-triggered D Flip-flop d clk D Q q clock module dff(clk, d, q); input d , clk; output q; reg q; d q Positive edge-triggered D Flip-flop always @(posedge clk) q <= d; endmodule 집적 회로 설계 코드 11. 8 Hanbat National University Prof. Lee Jaeheung

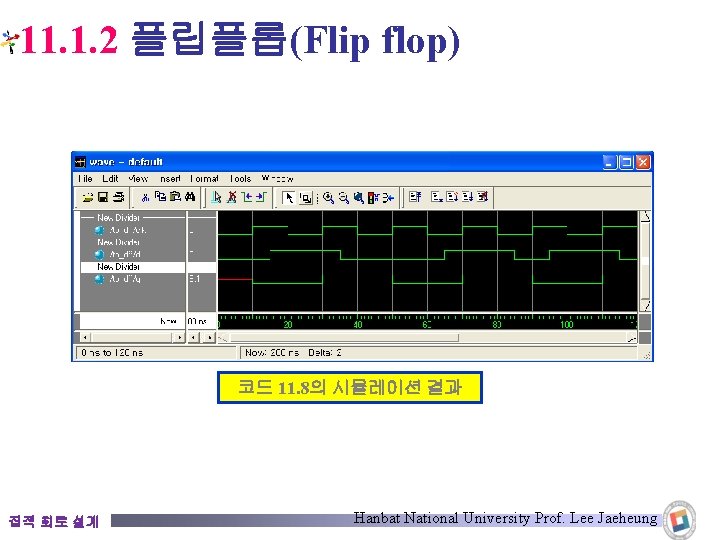

11. 1. 2 플립플롭(Flip flop) 코드 11. 8의 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

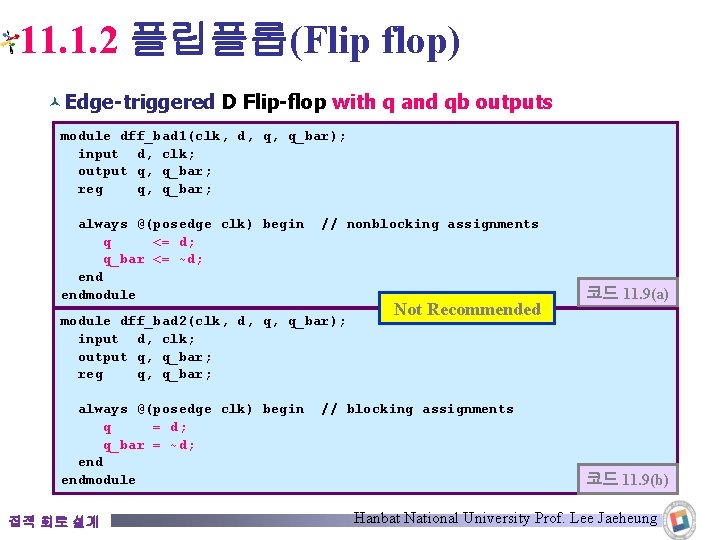

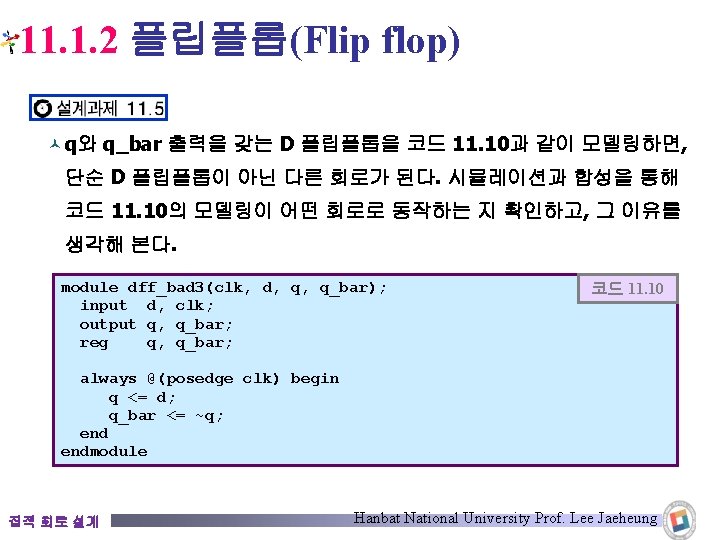

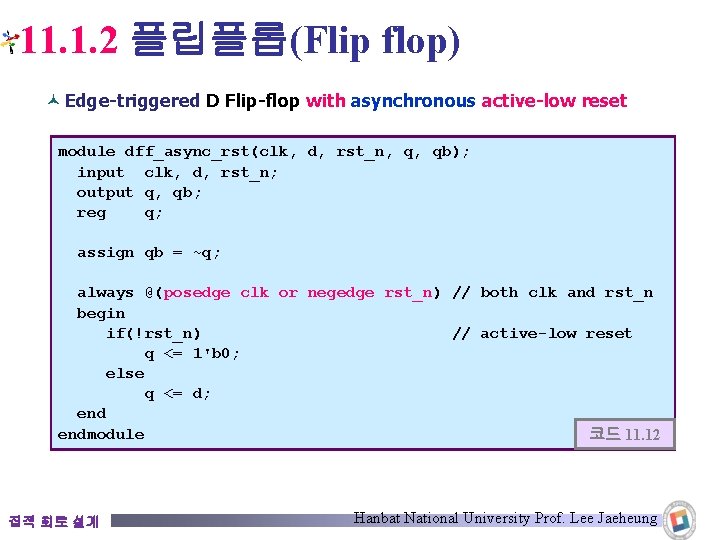

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with q and qb outputs module dff_bad 1(clk, d, q, q_bar); input d, clk; output q, q_bar; reg q, q_bar; always @(posedge clk) begin q <= d; q_bar <= ~d; endmodule // nonblocking assignments module dff_bad 2(clk, d, q, q_bar); input d, clk; output q, q_bar; reg q, q_bar; always @(posedge clk) begin q = d; q_bar = ~d; endmodule 집적 회로 설계 Not Recommended 코드 11. 9(a) // blocking assignments 코드 11. 9(b) Hanbat National University Prof. Lee Jaeheung

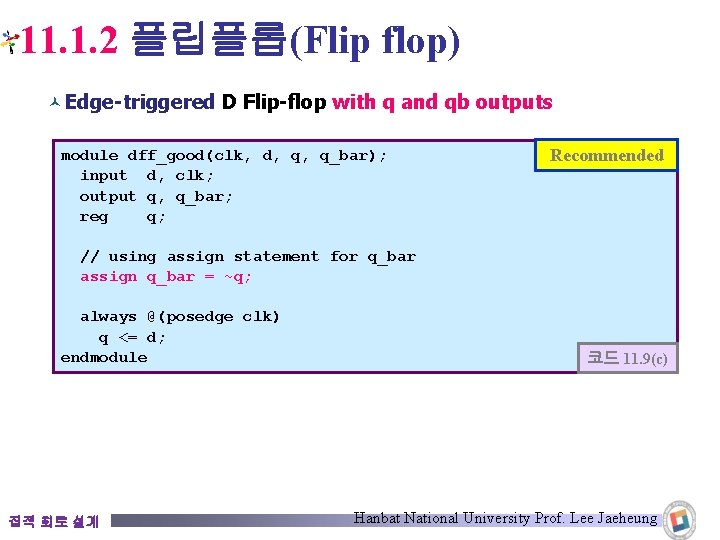

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with q and qb outputs module dff_good(clk, d, q, q_bar); input d, clk; output q, q_bar; reg q; Recommended // using assign statement for q_bar assign q_bar = ~q; always @(posedge clk) q <= d; endmodule 집적 회로 설계 코드 11. 9(c) Hanbat National University Prof. Lee Jaeheung

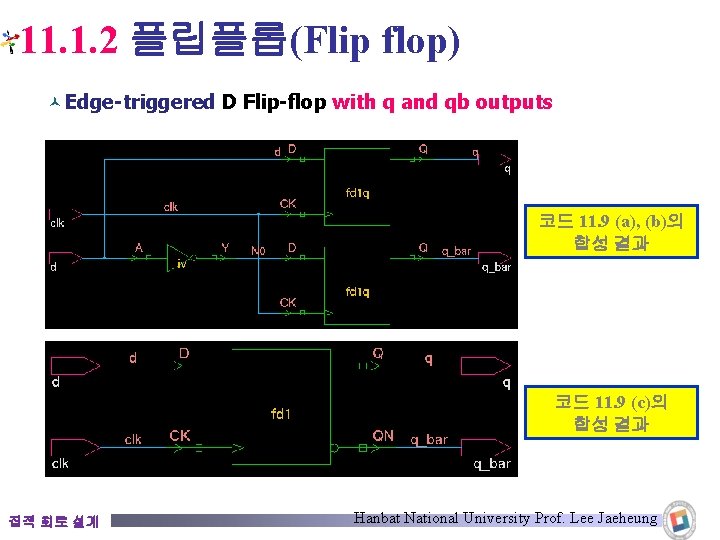

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with q and qb outputs Flip flop 코드 11. 9 (a), (b)의 합성 결과 Flip flop 코드 11. 9 (c)의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

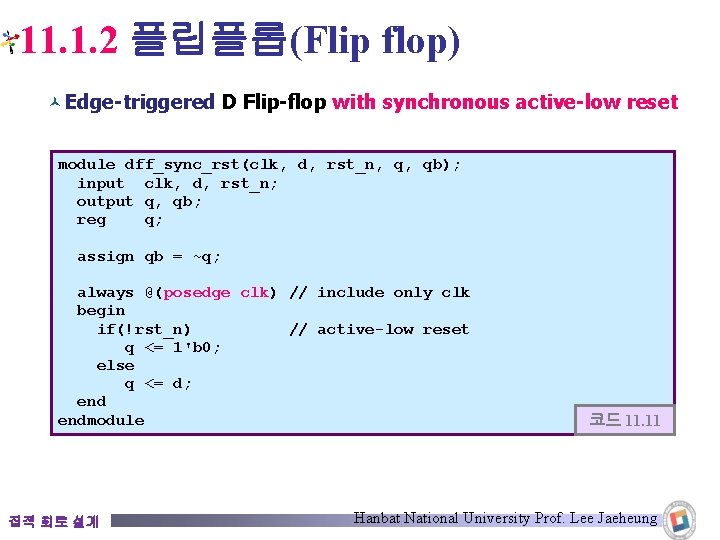

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with synchronous active-low reset module dff_sync_rst(clk, d, rst_n, q, qb); input clk, d, rst_n; output q, qb; reg q; assign qb = ~q; always @(posedge clk) // include only clk begin if(!rst_n) // active-low reset q <= 1'b 0; else q <= d; endmodule 집적 회로 설계 코드 11. 11 Hanbat National University Prof. Lee Jaeheung

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with synchronous active-low reset 코드 11. 11의 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

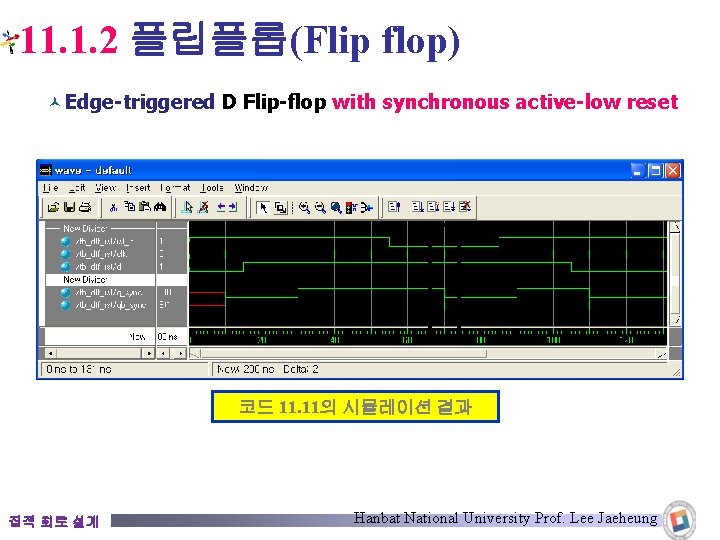

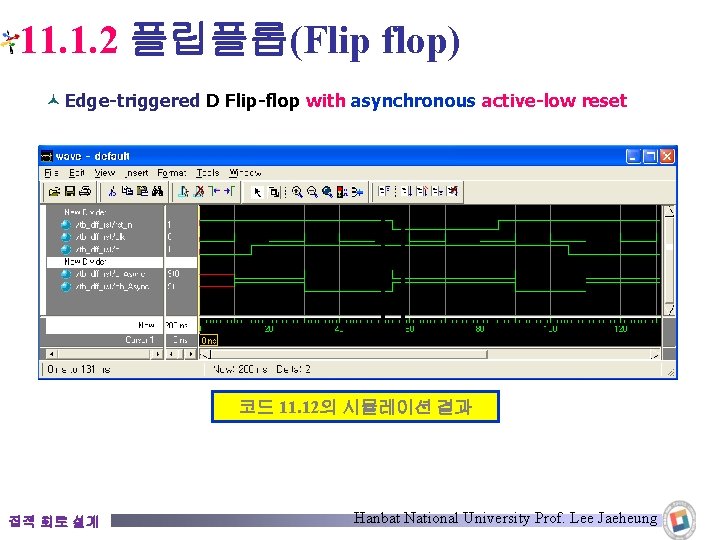

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with asynchronous active-low reset module dff_async_rst(clk, d, rst_n, q, qb); input clk, d, rst_n; output q, qb; reg q; assign qb = ~q; always @(posedge clk or negedge rst_n) // both clk and rst_n begin if(!rst_n) // active-low reset q <= 1'b 0; else q <= d; endmodule 코드 11. 12 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

11. 1. 2 플립플롭(Flip flop) © Edge-triggered D Flip-flop with asynchronous active-low reset 코드 11. 12의 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

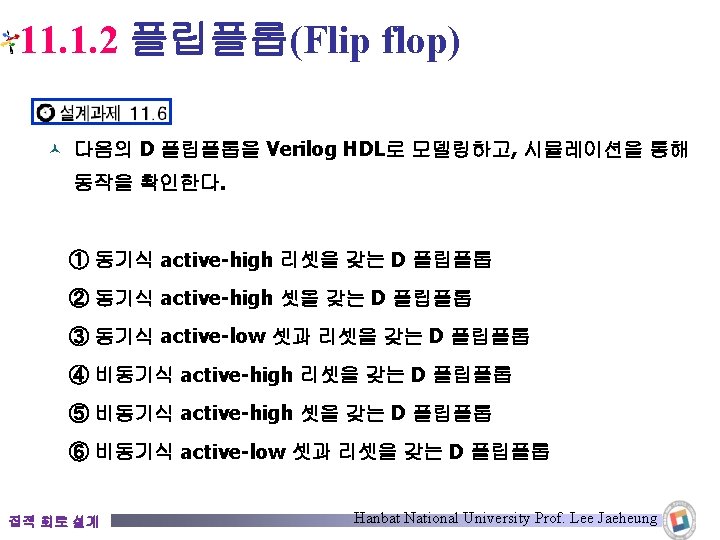

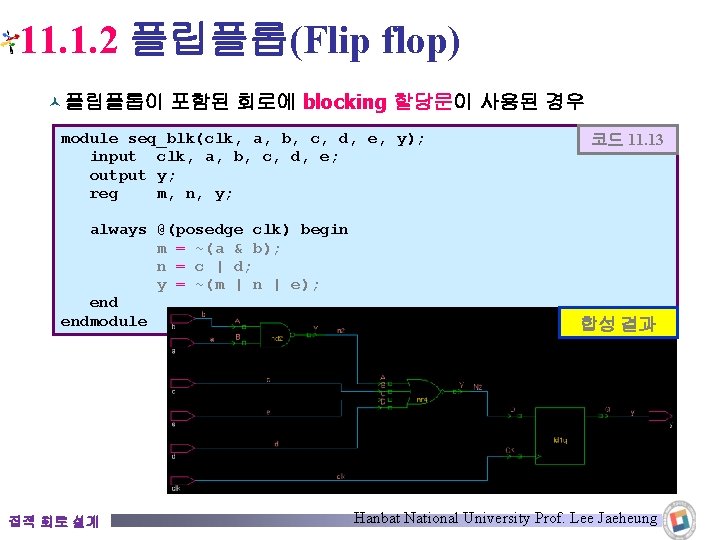

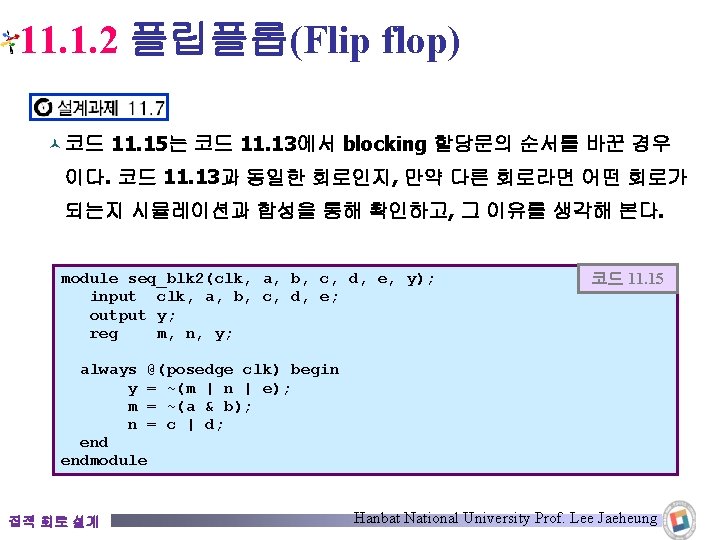

11. 1. 2 플립플롭(Flip flop) © 플립플롭이 포함된 회로에 blocking 할당문이 사용된 경우 module seq_blk(clk, a, b, c, d, e, y); input clk, a, b, c, d, e; output y; reg m, n, y; always @(posedge clk) begin m = ~(a & b); n = c | d; y = ~(m | n | e); endmodule 코드 11. 13 합성 결과 Flip Flop 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

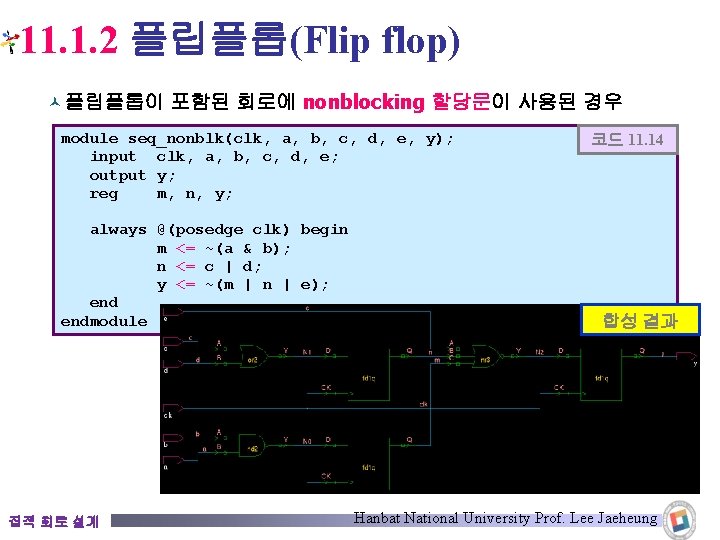

11. 1. 2 플립플롭(Flip flop) © 플립플롭이 포함된 회로에 nonblocking 할당문이 사용된 경우 module seq_nonblk(clk, a, b, c, d, e, y); input clk, a, b, c, d, e; output y; reg m, n, y; always @(posedge clk) begin m <= ~(a & b); n <= c | d; y <= ~(m | n | e); endmodule 코드 11. 14 합성 결과 Flip Flop 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

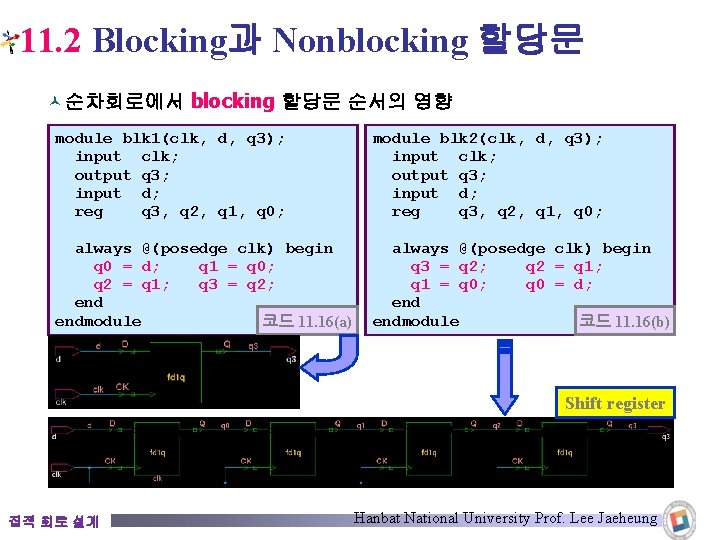

11. 2 Blocking과 Nonblocking 할당문 © 순차회로에서 blocking 할당문 순서의 영향 module blk 1(clk, d, q 3); input clk; output q 3; input d; reg q 3, q 2, q 1, q 0; module blk 2(clk, d, q 3); input clk; output q 3; input d; reg q 3, q 2, q 1, q 0; always @(posedge clk) begin q 0 = d; q 1 = q 0; q 2 = q 1; q 3 = q 2; endmodule 코드 11. 16(a) always @(posedge clk) begin q 3 = q 2; q 2 = q 1; q 1 = q 0; q 0 = d; endmodule 코드 11. 16(b) Flip Flop Shift register Flip Flop 집적 회로 설계 Flip Flop Hanbat National University Prof. Lee Jaeheung

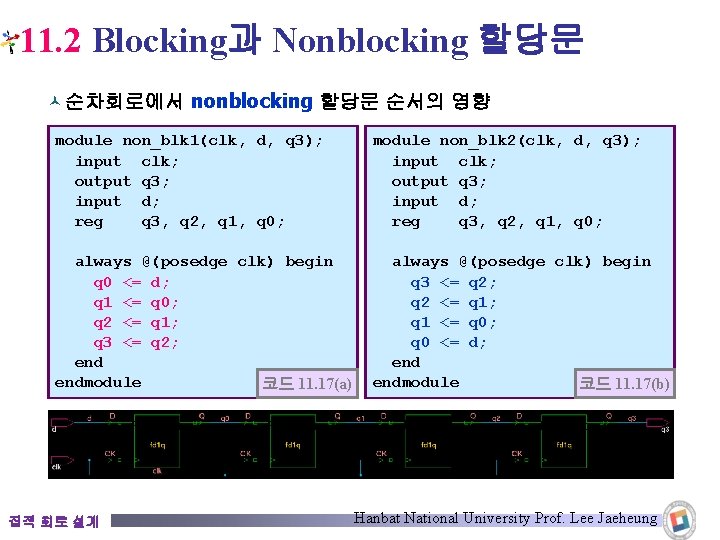

11. 2 Blocking과 Nonblocking 할당문 © 순차회로에서 nonblocking 할당문 순서의 영향 module non_blk 1(clk, d, q 3); input clk; output q 3; input d; reg q 3, q 2, q 1, q 0; module non_blk 2(clk, d, q 3); input clk; output q 3; input d; reg q 3, q 2, q 1, q 0; always @(posedge clk) begin q 0 <= d; q 1 <= q 0; q 2 <= q 1; q 3 <= q 2; endmodule 코드 11. 17(a) always @(posedge clk) begin q 3 <= q 2; q 2 <= q 1; q 1 <= q 0; q 0 <= d; endmodule 코드 11. 17(b) Flip Flop 집적 회로 설계 Flip Flop Hanbat National University Prof. Lee Jaeheung

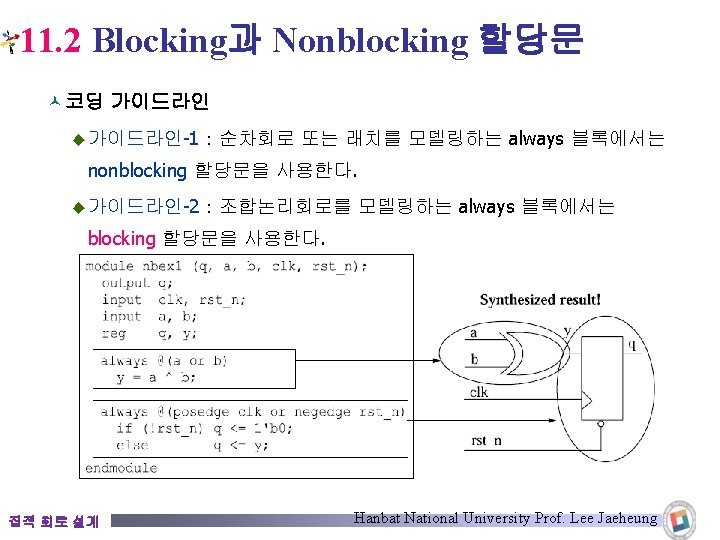

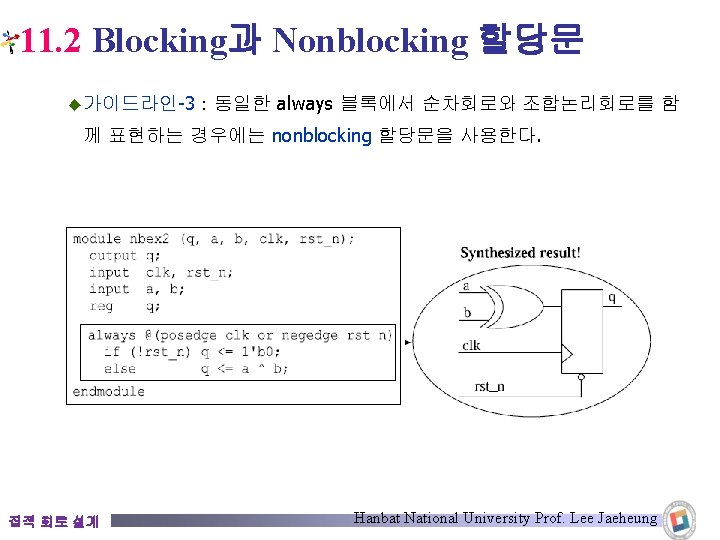

11. 2 Blocking과 Nonblocking 할당문 always 블록 내에서 blocking 할당문과 nonblocking 할당문을 혼합해서 사용하지 않는다. ◆ 가이드라인-4:동일한 module ba_nba 1(q, a, b, clk, rst_n); output q; input a, b, rst_n, clk; reg q, tmp; always @(posedge clk or negedge rst_n) if(!rst_n) q <= 1'b 0; else begin tmp = a & b; q <= tmp; endmodule ba_nba 2(q, a, b, clk, rst_n); output q; input a, b, rst_n, clk; reg q, tmp; always @(posedge clk or negedge rst_n) if(!rst_n) q = 1'b 0; //blocking else begin tmp = a & b; q <= tmp; //nonblocking endmodule 집적 회로 설계 Bad Coding 코드 11. 18(a) 코드 11. 18(b) Hanbat National University Prof. Lee Jaeheung

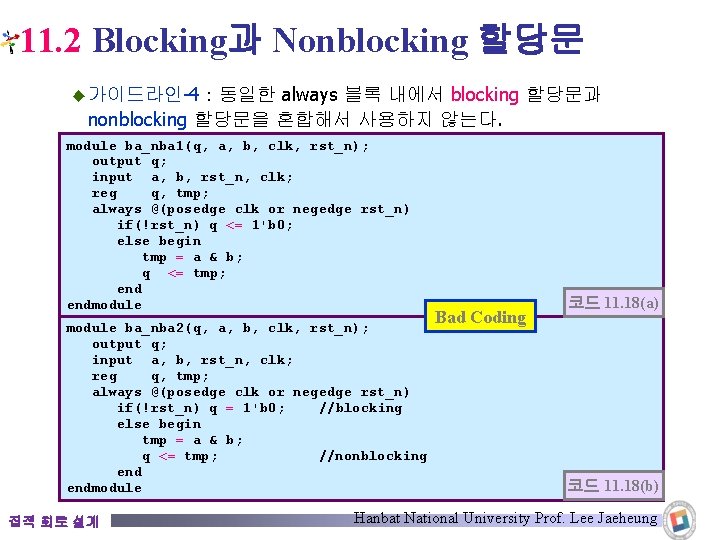

11. 2 Blocking과 Nonblocking 할당문 module ba_nba 3(q, a, b, clk, rst_n); output q; input a, b, rst_n, clk; reg q; always @(posedge clk or negedge rst_n) if(!rst_n) q <= 1'b 0; else q <= a & b; endmodule ba_nba 4(q, a, b, clk, rst_n); output q; input a, b, rst_n, clk; reg q; wire tmp; Good Coding 코드 11. 18(c) assign tmp = a & b; always @(posedge clk or negedge rst_n) if(!rst_n) q <= 1'b 0; else q <= tmp; endmodule 집적 회로 설계 코드 11. 18(d) Hanbat National University Prof. Lee Jaeheung

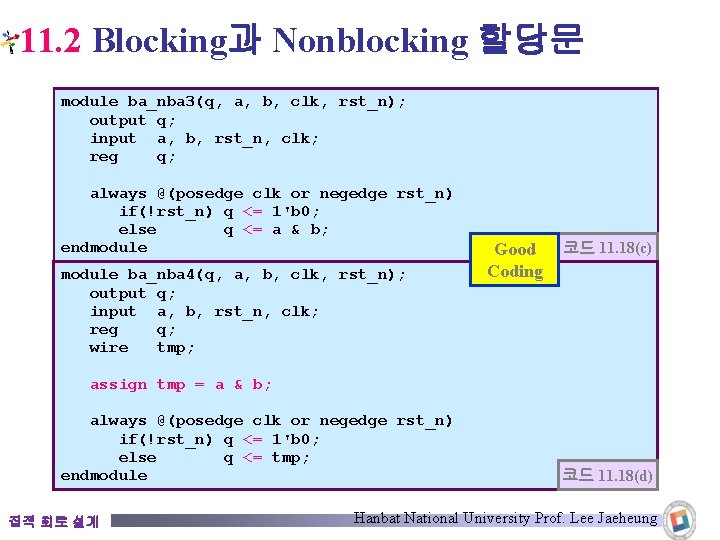

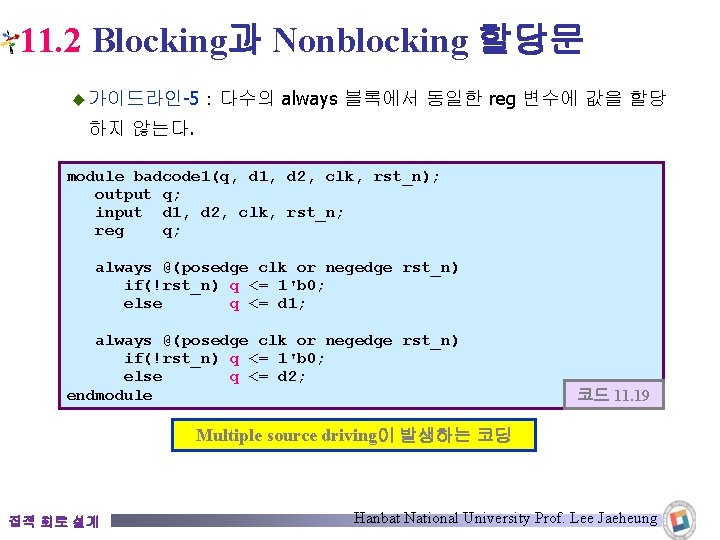

11. 2 Blocking과 Nonblocking 할당문 ◆ 가이드라인-5:다수의 always 블록에서 동일한 reg 변수에 값을 할당 하지 않는다. module badcode 1(q, d 1, d 2, clk, rst_n); output q; input d 1, d 2, clk, rst_n; reg q; always @(posedge clk or negedge rst_n) if(!rst_n) q <= 1'b 0; else q <= d 1; always @(posedge clk or negedge rst_n) if(!rst_n) q <= 1'b 0; else q <= d 2; endmodule 코드 11. 19 Multiple source driving이 발생하는 코딩 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

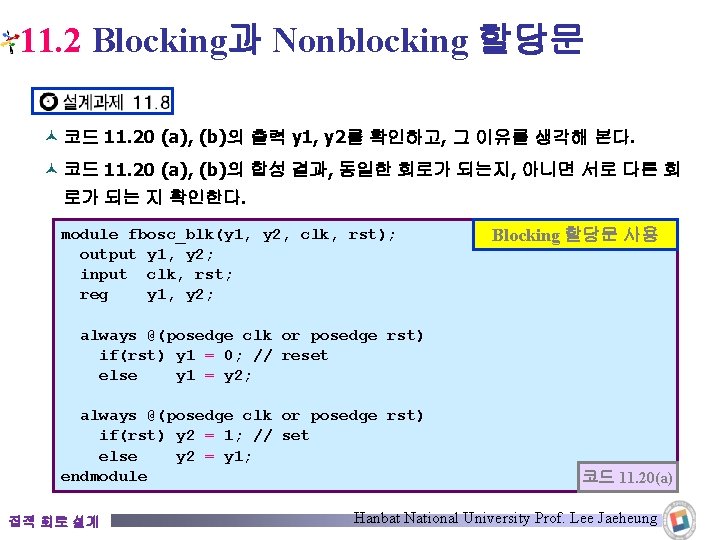

11. 2 Blocking과 Nonblocking 할당문 © 코드 11. 20 (a), (b)의 출력 y 1, y 2를 확인하고, 그 이유를 생각해 본다. © 코드 11. 20 (a), (b)의 합성 결과, 동일한 회로가 되는지, 아니면 서로 다른 회 로가 되는 지 확인한다. module fbosc_blk(y 1, y 2, clk, rst); output y 1, y 2; input clk, rst; reg y 1, y 2; Blocking 할당문 사용 always @(posedge clk or posedge rst) if(rst) y 1 = 0; // reset else y 1 = y 2; always @(posedge clk or posedge rst) if(rst) y 2 = 1; // set else y 2 = y 1; endmodule 집적 회로 설계 코드 11. 20(a) Hanbat National University Prof. Lee Jaeheung

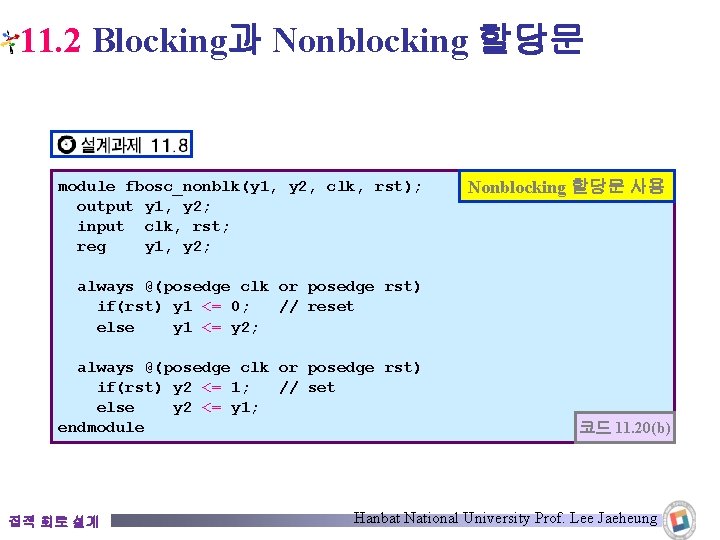

11. 2 Blocking과 Nonblocking 할당문 module fbosc_nonblk(y 1, y 2, clk, rst); output y 1, y 2; input clk, rst; reg y 1, y 2; Nonblocking 할당문 사용 always @(posedge clk or posedge rst) if(rst) y 1 <= 0; // reset else y 1 <= y 2; always @(posedge clk or posedge rst) if(rst) y 2 <= 1; // set else y 2 <= y 1; endmodule 집적 회로 설계 코드 11. 20(b) Hanbat National University Prof. Lee Jaeheung

![11. 3. 1 직렬입력-직렬출력 시프트 레지스터 sout q[7] Q D q[2] DFF Q D 11. 3. 1 직렬입력-직렬출력 시프트 레지스터 sout q[7] Q D q[2] DFF Q D](http://slidetodoc.com/presentation_image_h/e42c314bb08fbb5336e690dbe855bfdd/image-36.jpg)

11. 3. 1 직렬입력-직렬출력 시프트 레지스터 sout q[7] Q D q[2] DFF Q D DFF q[1] Q D q[0] DFF Q D sin DFF clk rst 그림 11. 17 직렬입력-직렬출력 시프트 레지스터 module shift_reg_nblk 1(clk, rst, sin, sout); input clk, rst, sin; output sout; reg [7: 0] q; assign sout = q[7]; always @(posedge clk) begin if(!rst) q <= 8'b 0; else begin 집적 회로 설계 코드 11. 21 q[0] q[1] q[2] q[3] q[4] q[5] q[6] q[7] end endmodule <= <= sin; q[0]; q[1]; q[2]; q[3]; q[4]; q[5]; q[6]; Hanbat National University Prof. Lee Jaeheung

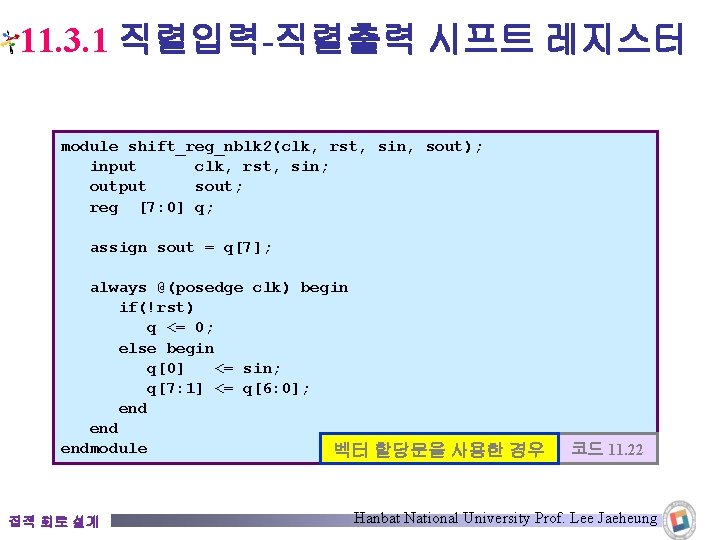

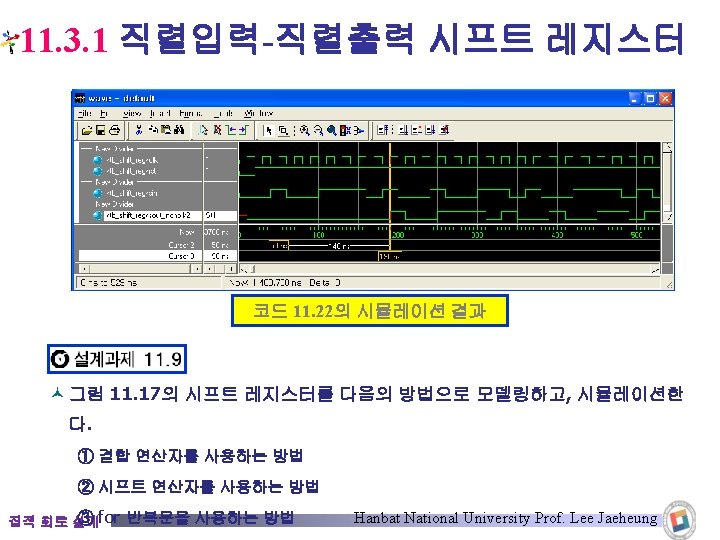

11. 3. 1 직렬입력-직렬출력 시프트 레지스터 module shift_reg_nblk 2(clk, rst, sin, sout); input clk, rst, sin; output sout; reg [7: 0] q; assign sout = q[7]; always @(posedge clk) begin if(!rst) q <= 0; else begin q[0] <= sin; q[7: 1] <= q[6: 0]; end endmodule 벡터 할당문을 사용한 경우 집적 회로 설계 코드 11. 22 Hanbat National University Prof. Lee Jaeheung

![11. 3. 2 병렬입력-병렬출력 시프트 레지스터 © 병렬입력-병렬출력 시프트 레지스터 pout[8] din[8] load Q 11. 3. 2 병렬입력-병렬출력 시프트 레지스터 © 병렬입력-병렬출력 시프트 레지스터 pout[8] din[8] load Q](http://slidetodoc.com/presentation_image_h/e42c314bb08fbb5336e690dbe855bfdd/image-39.jpg)

11. 3. 2 병렬입력-병렬출력 시프트 레지스터 © 병렬입력-병렬출력 시프트 레지스터 pout[8] din[8] load Q MUX D DFF pout[2] din[2] pout[1] load Q MUX D DFF load Q din[0] din[1] pout[0] MUX D DFF Q D DFF clk rst 그림 11. 19 병렬입력-직렬출력 시프트 레지스터 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

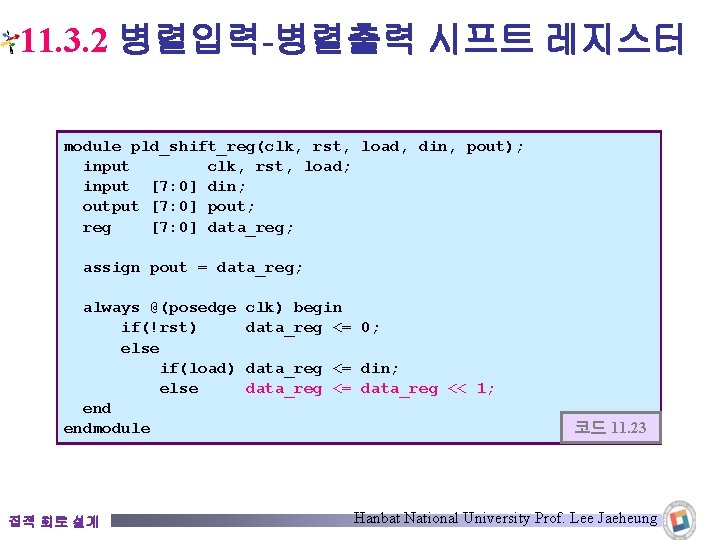

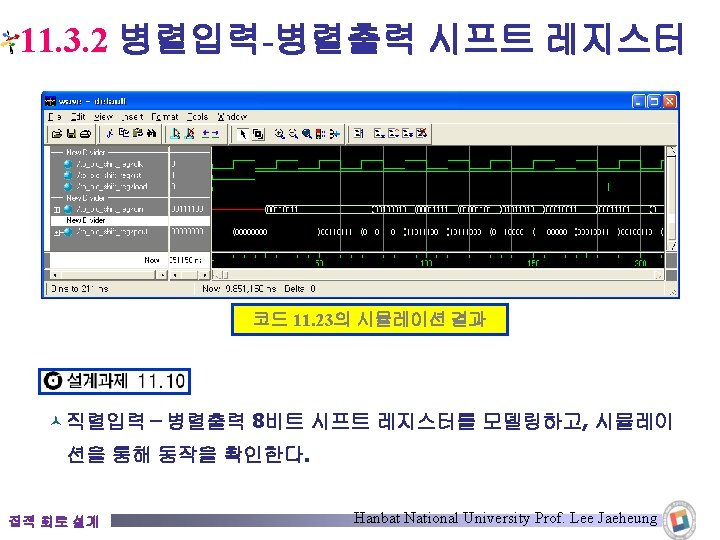

11. 3. 2 병렬입력-병렬출력 시프트 레지스터 module pld_shift_reg(clk, rst, load, din, pout); input clk, rst, load; input [7: 0] din; output [7: 0] pout; reg [7: 0] data_reg; assign pout = data_reg; always @(posedge if(!rst) else if(load) else endmodule 집적 회로 설계 clk) begin data_reg <= 0; data_reg <= din; data_reg <= data_reg << 1; 코드 11. 23 Hanbat National University Prof. Lee Jaeheung

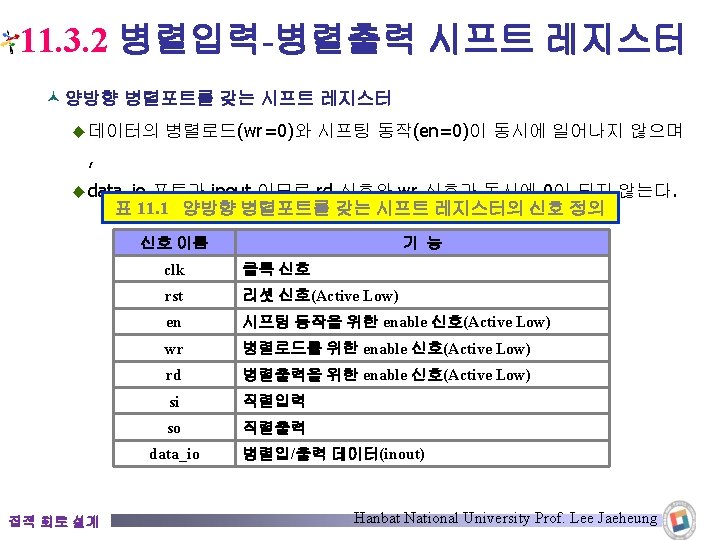

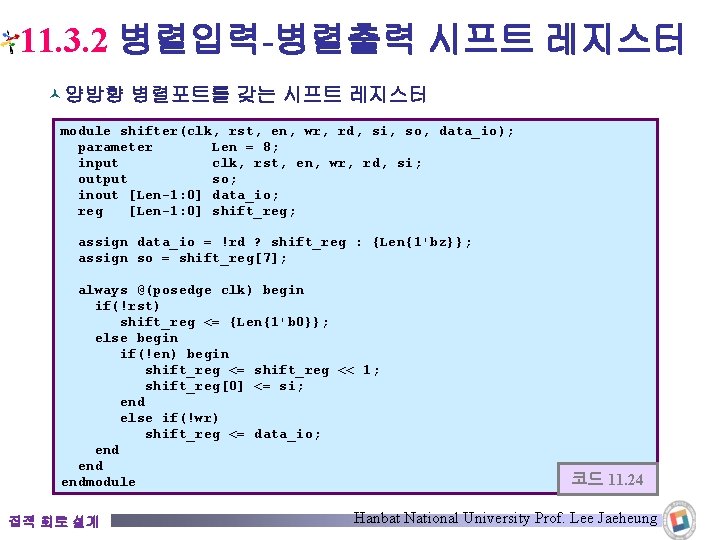

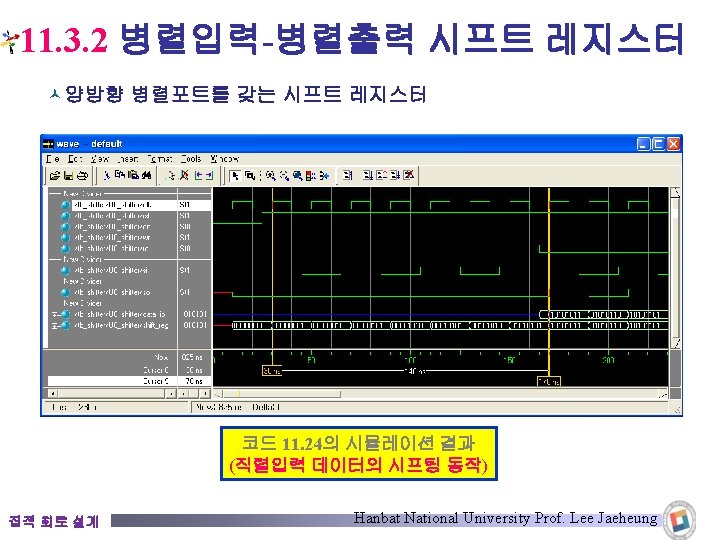

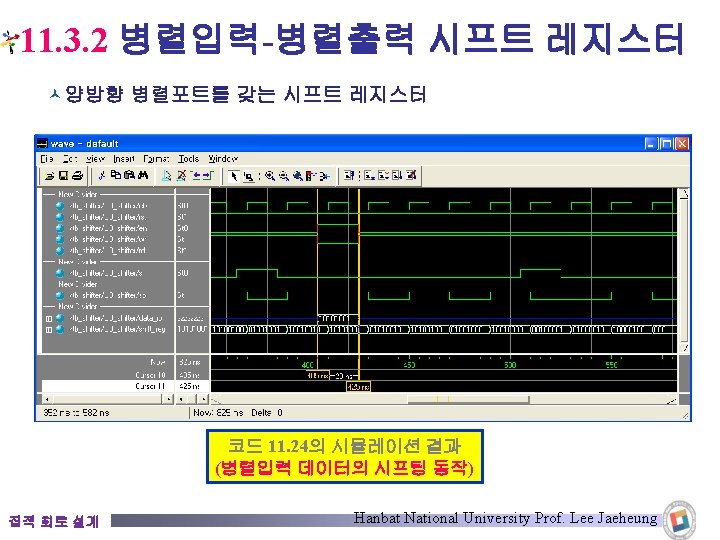

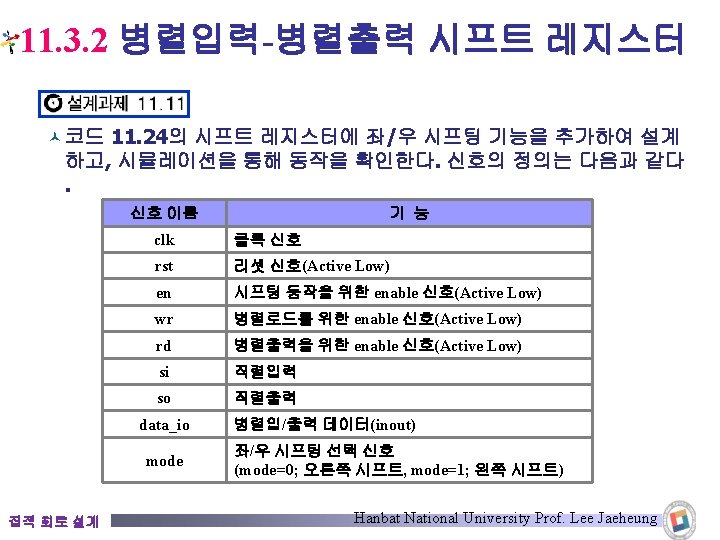

11. 3. 2 병렬입력-병렬출력 시프트 레지스터 © 양방향 병렬포트를 갖는 시프트 레지스터 module shifter(clk, rst, en, wr, rd, si, so, data_io); parameter Len = 8; input clk, rst, en, wr, rd, si; output so; inout [Len-1: 0] data_io; reg [Len-1: 0] shift_reg; assign data_io = !rd ? shift_reg : {Len{1'bz}}; assign so = shift_reg[7]; always @(posedge clk) begin if(!rst) shift_reg <= {Len{1'b 0}}; else begin if(!en) begin shift_reg <= shift_reg << 1; shift_reg[0] <= si; end else if(!wr) shift_reg <= data_io; end endmodule 집적 회로 설계 코드 11. 24 Hanbat National University Prof. Lee Jaeheung

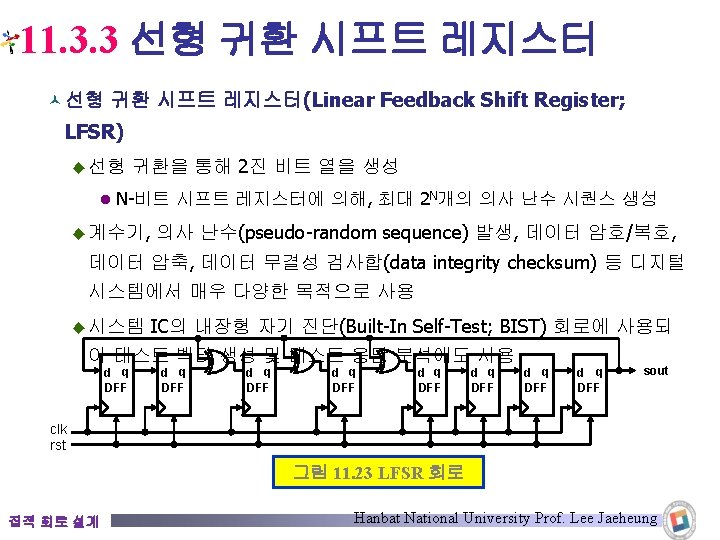

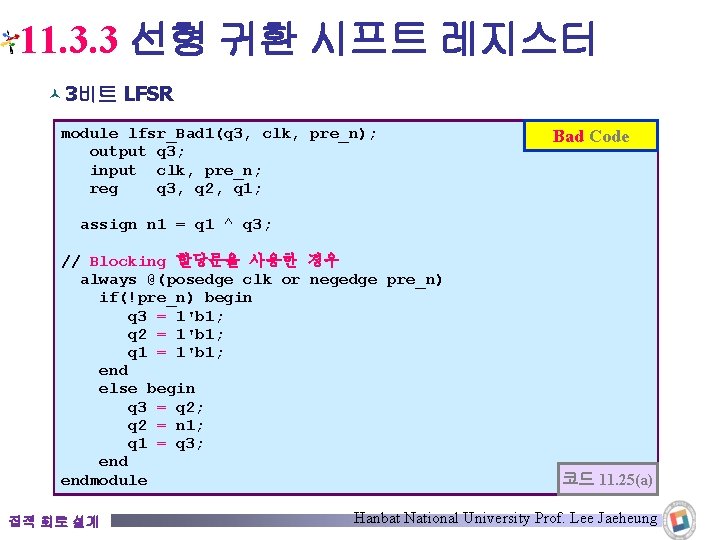

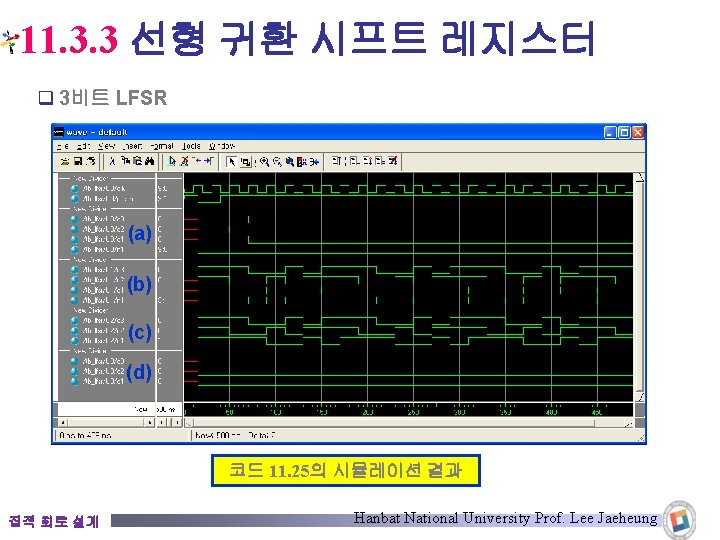

11. 3. 3 선형 귀환 시프트 레지스터 © 3비트 LFSR module lfsr_Bad 1(q 3, clk, pre_n); output q 3; input clk, pre_n; reg q 3, q 2, q 1; Bad Code assign n 1 = q 1 ^ q 3; // Blocking 할당문을 사용한 경우 always @(posedge clk or negedge pre_n) if(!pre_n) begin q 3 = 1'b 1; q 2 = 1'b 1; q 1 = 1'b 1; end else begin q 3 = q 2; q 2 = n 1; q 1 = q 3; endmodule 집적 회로 설계 코드 11. 25(a) Hanbat National University Prof. Lee Jaeheung

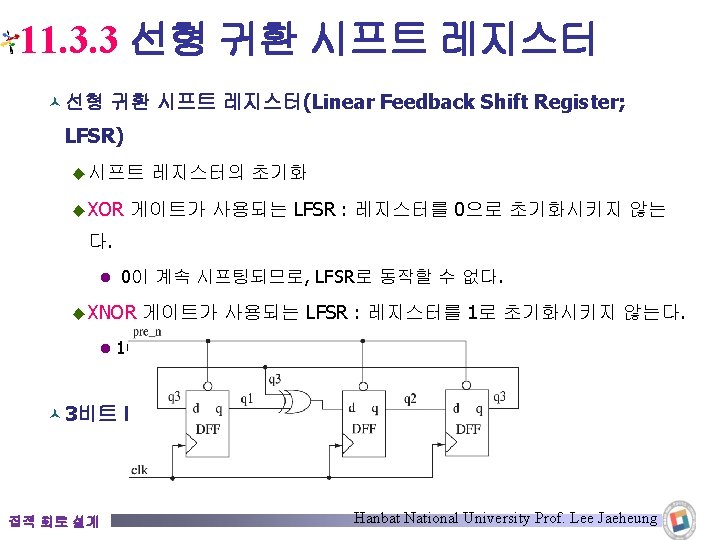

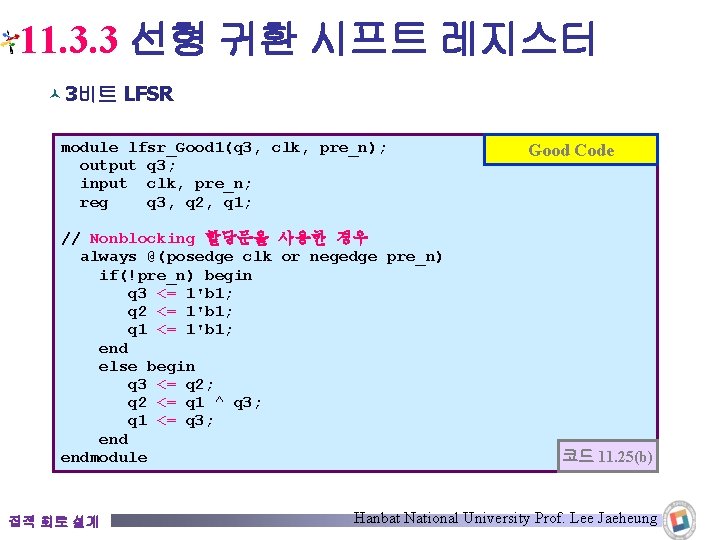

11. 3. 3 선형 귀환 시프트 레지스터 © 3비트 LFSR module lfsr_Good 1(q 3, clk, pre_n); output q 3; input clk, pre_n; reg q 3, q 2, q 1; // Nonblocking 할당문을 사용한 경우 always @(posedge clk or negedge pre_n) if(!pre_n) begin q 3 <= 1'b 1; q 2 <= 1'b 1; q 1 <= 1'b 1; end else begin q 3 <= q 2; q 2 <= q 1 ^ q 3; q 1 <= q 3; endmodule 집적 회로 설계 Good Code 코드 11. 25(b) Hanbat National University Prof. Lee Jaeheung

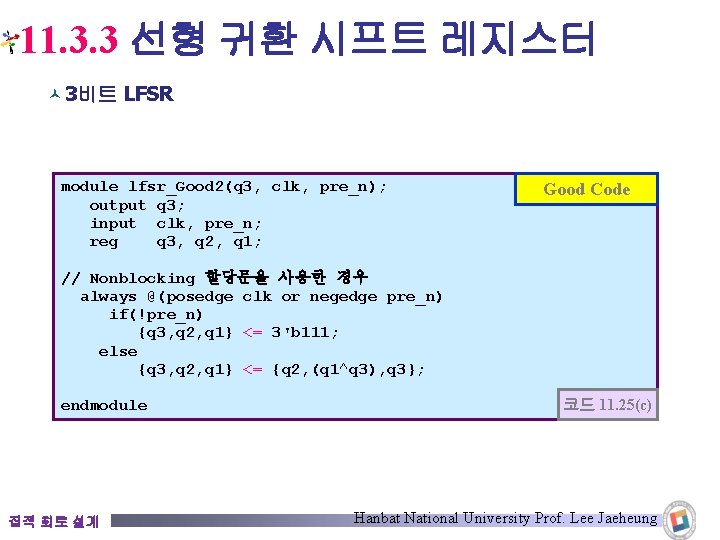

11. 3. 3 선형 귀환 시프트 레지스터 © 3비트 LFSR module lfsr_Good 2(q 3, clk, pre_n); output q 3; input clk, pre_n; reg q 3, q 2, q 1; Good Code // Nonblocking 할당문을 사용한 경우 always @(posedge clk or negedge pre_n) if(!pre_n) {q 3, q 2, q 1} <= 3'b 111; else {q 3, q 2, q 1} <= {q 2, (q 1^q 3), q 3}; endmodule 집적 회로 설계 코드 11. 25(c) Hanbat National University Prof. Lee Jaeheung

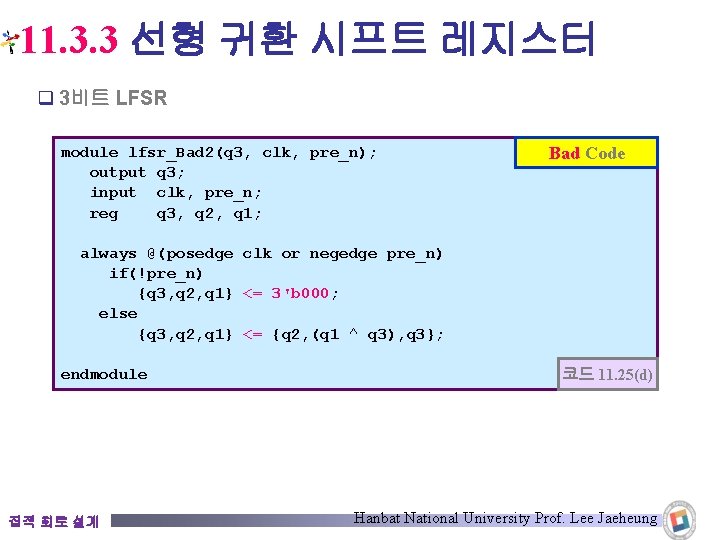

11. 3. 3 선형 귀환 시프트 레지스터 q 3비트 LFSR module lfsr_Bad 2(q 3, clk, pre_n); output q 3; input clk, pre_n; reg q 3, q 2, q 1; Bad Code always @(posedge clk or negedge pre_n) if(!pre_n) {q 3, q 2, q 1} <= 3'b 000; else {q 3, q 2, q 1} <= {q 2, (q 1 ^ q 3), q 3}; endmodule 집적 회로 설계 코드 11. 25(d) Hanbat National University Prof. Lee Jaeheung

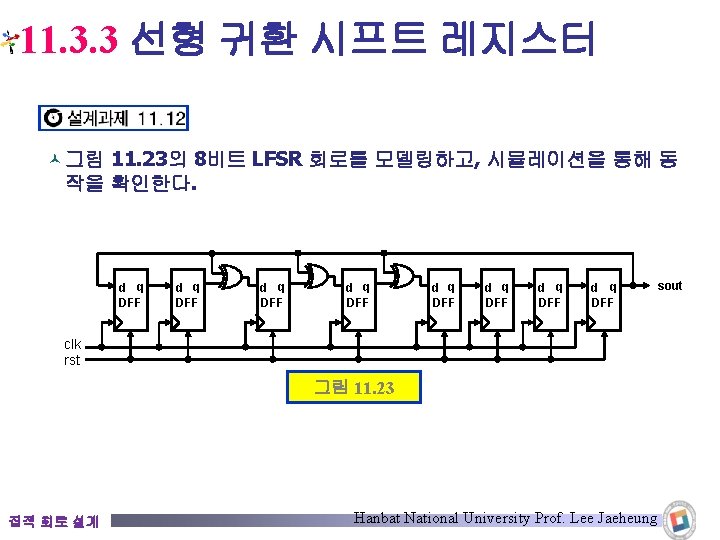

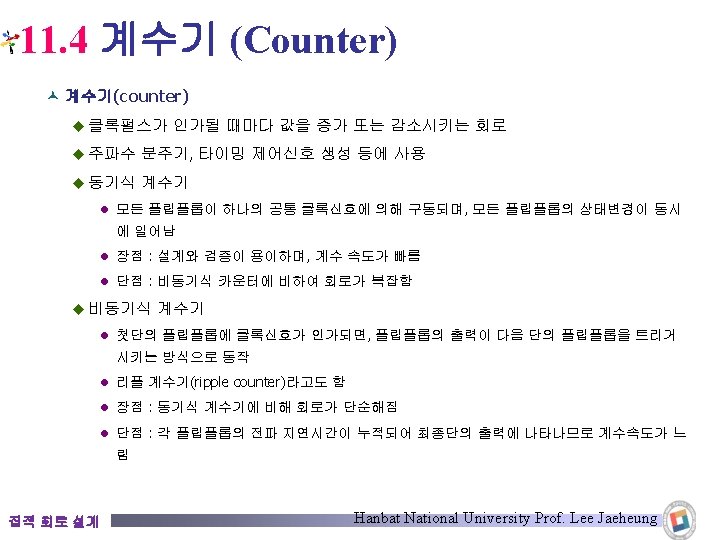

11. 4 계수기 (Counter) © 8비트 증가 계수기 module counter_up(clk, rst, cnt); input clk, rst; output [7: 0] cnt; reg [7: 0] cnt; always @(posedge clk or negedge rst) begin if(!rst) cnt <= 0; else cnt <= cnt + 1; endmodule 집적 회로 설계 코드 11. 26 Hanbat National University Prof. Lee Jaeheung

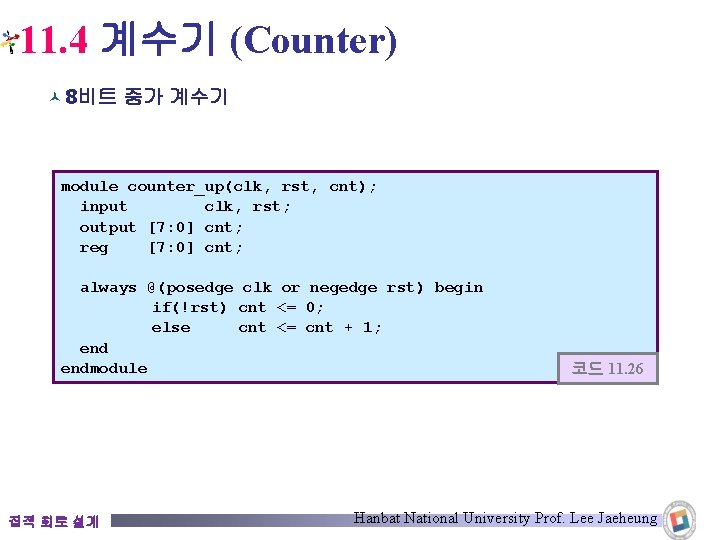

11. 4 계수기 (Counter) © 8비트 증가 계수기 코드 11. 26의 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

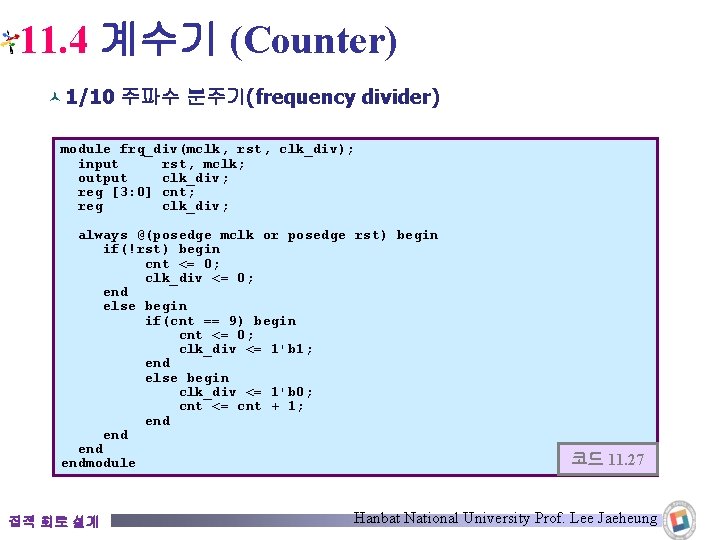

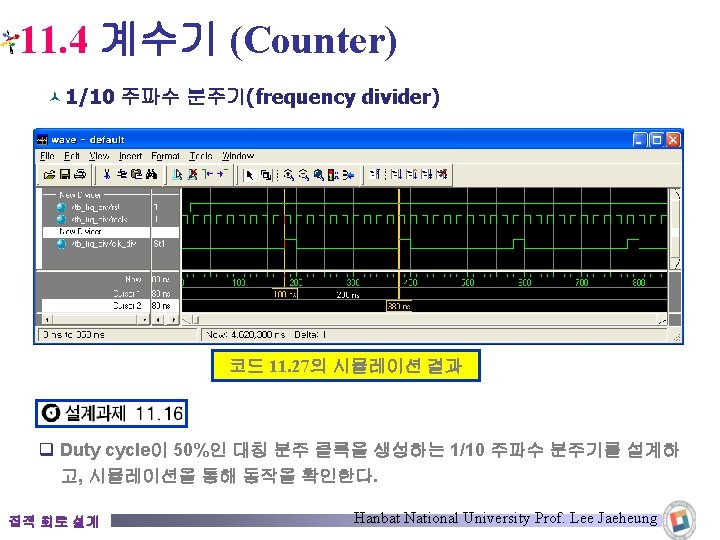

11. 4 계수기 (Counter) © 1/10 주파수 분주기(frequency divider) module frq_div(mclk, rst, clk_div); input rst, mclk; output clk_div; reg [3: 0] cnt; reg clk_div; always @(posedge mclk or posedge rst) begin if(!rst) begin cnt <= 0; clk_div <= 0; end else begin if(cnt == 9) begin cnt <= 0; clk_div <= 1'b 1; end else begin clk_div <= 1'b 0; cnt <= cnt + 1; end endmodule 집적 회로 설계 코드 11. 27 Hanbat National University Prof. Lee Jaeheung

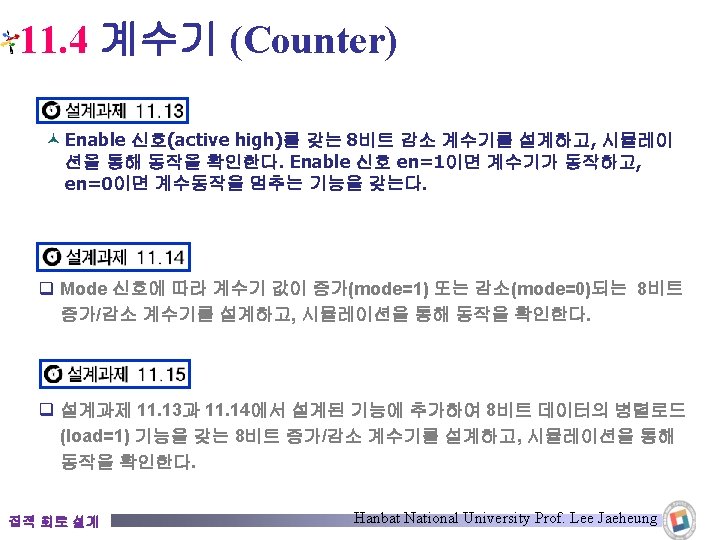

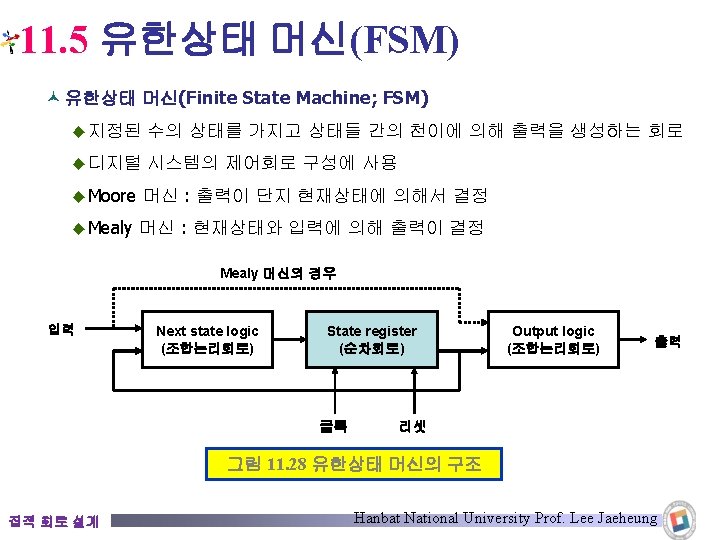

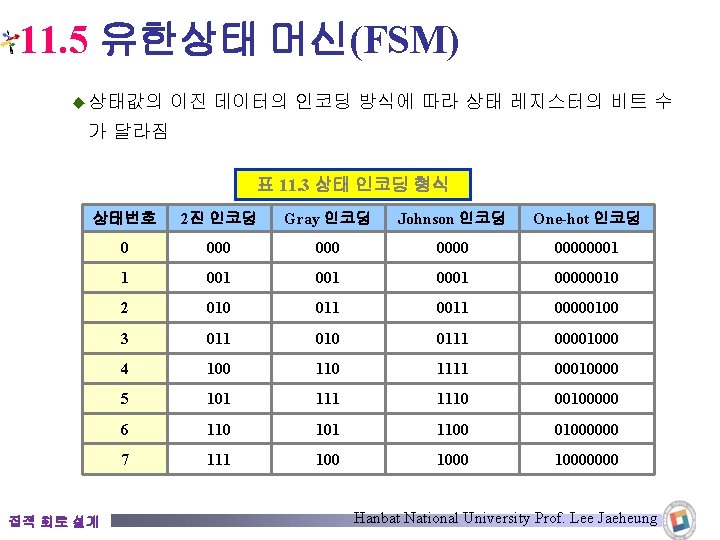

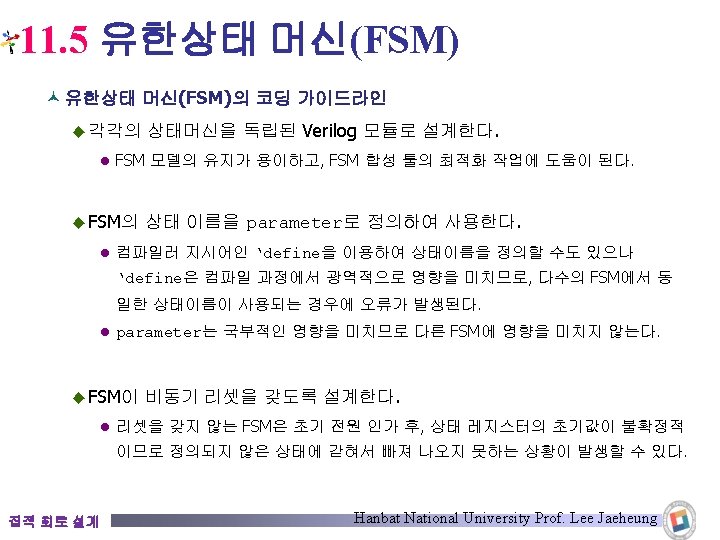

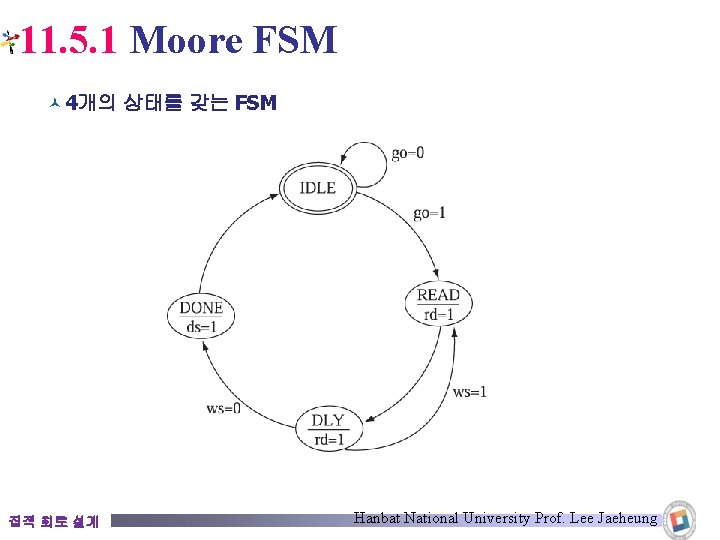

11. 5 유한상태 머신(FSM) ◆ 상태값의 이진 데이터의 인코딩 방식에 따라 상태 레지스터의 비트 수 가 달라짐 표 11. 3 상태 인코딩 형식 상태번호 2진 인코딩 Gray 인코딩 Johnson 인코딩 One-hot 인코딩 0 000 00000001 1 001 00000010 2 010 011 00000100 3 011 010 0111 00001000 4 100 1111 00010000 5 101 1110 00100000 6 110 101 1100 01000000 7 111 10000000 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

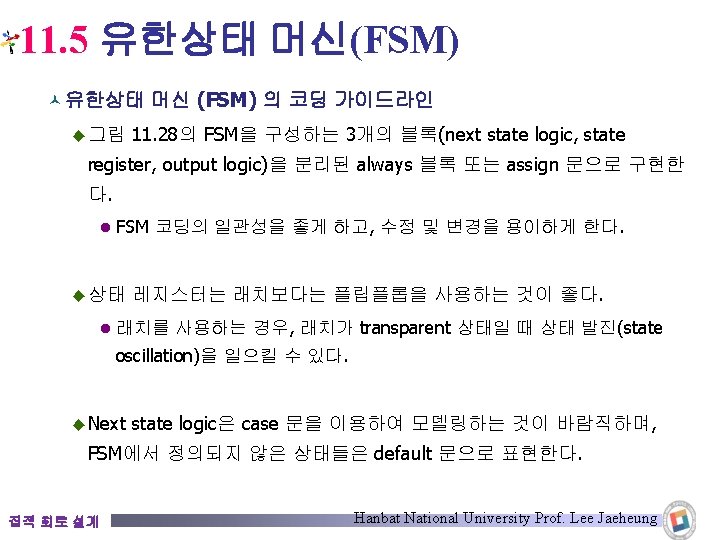

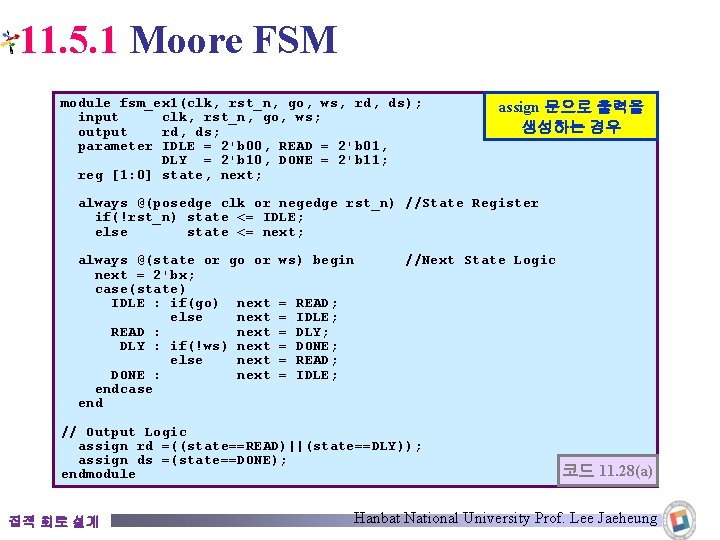

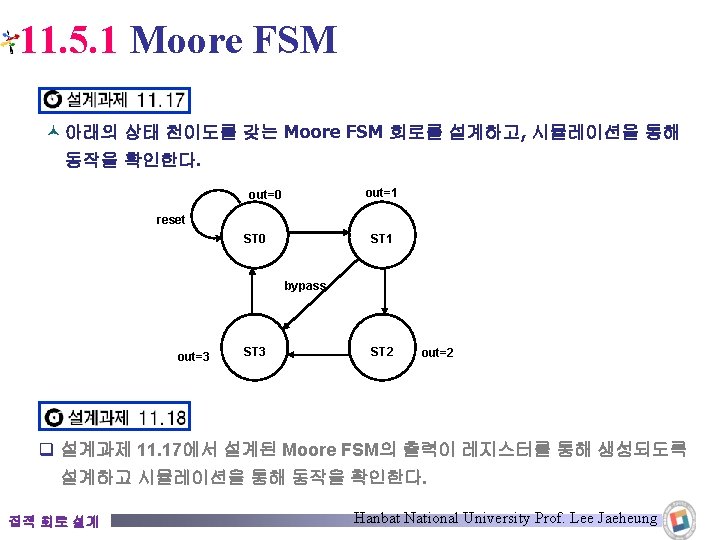

11. 5. 1 Moore FSM © 4개의 상태를 갖는 FSM 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

11. 5. 1 Moore FSM module fsm_ex 1(clk, rst_n, go, ws, rd, ds); input clk, rst_n, go, ws; output rd, ds; parameter IDLE = 2'b 00, READ = 2'b 01, DLY = 2'b 10, DONE = 2'b 11; reg [1: 0] state, next; assign 문으로 출력을 생성하는 경우 always @(posedge clk or negedge rst_n) //State Register if(!rst_n) state <= IDLE; else state <= next; always @(state or go or next = 2'bx; case(state) IDLE : if(go) next else next READ : next DLY : if(!ws) next else next DONE : next endcase end ws) begin = = = //Next State Logic READ; IDLE; DLY; DONE; READ; IDLE; // Output Logic assign rd =((state==READ)||(state==DLY)); assign ds =(state==DONE); endmodule 집적 회로 설계 코드 11. 28(a) Hanbat National University Prof. Lee Jaeheung

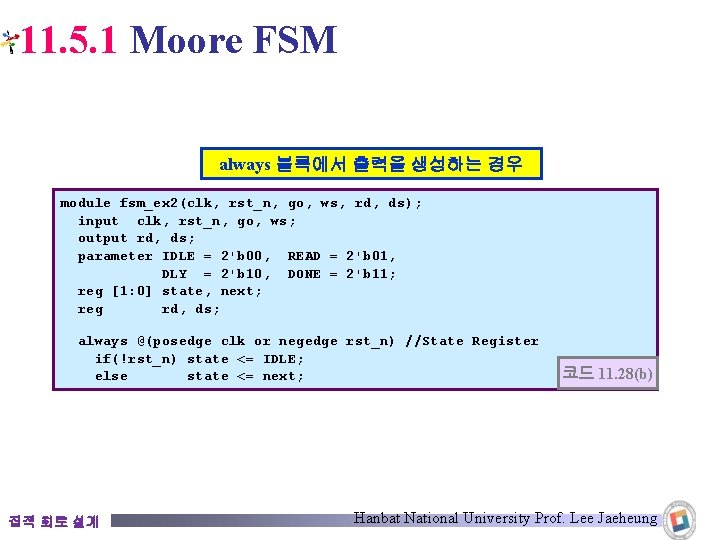

11. 5. 1 Moore FSM always 블록에서 출력을 생성하는 경우 module fsm_ex 2(clk, rst_n, go, ws, rd, ds); input clk, rst_n, go, ws; output rd, ds; parameter IDLE = 2'b 00, READ = 2'b 01, DLY = 2'b 10, DONE = 2'b 11; reg [1: 0] state, next; reg rd, ds; always @(posedge clk or negedge rst_n) //State Register if(!rst_n) state <= IDLE; else state <= next; 집적 회로 설계 코드 11. 28(b) Hanbat National University Prof. Lee Jaeheung

11. 5. 1 Moore FSM //Next State and Output Logic always @(state or go or ws) begin next = 2'bx; rd = 1'b 0; ds = 1'b 0; case(state) IDLE : if(go) next = READ; else next = IDLE; READ : begin rd = 1'b 1; next = DLY; end DLY : begin rd = 1'b 1; if(!ws) next = DONE; else next = READ; end DONE : begin ds = 1'b 1; next = IDLE; endcase endmodule 집적 회로 설계 코드 11. 28(b) Hanbat National University Prof. Lee Jaeheung

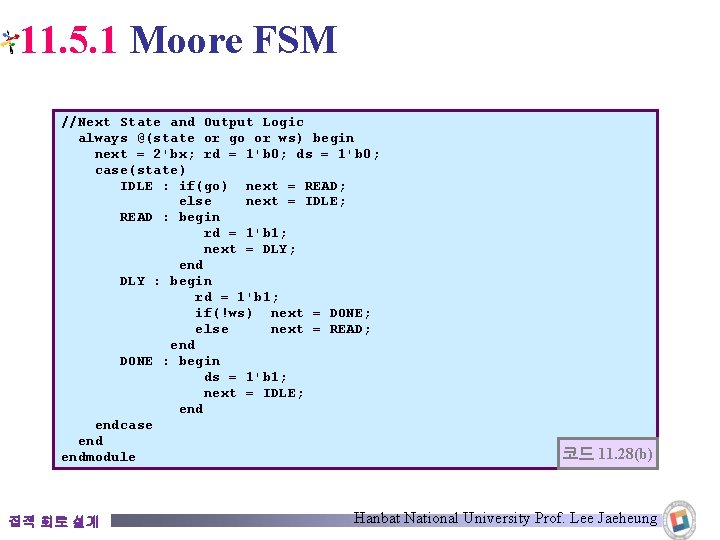

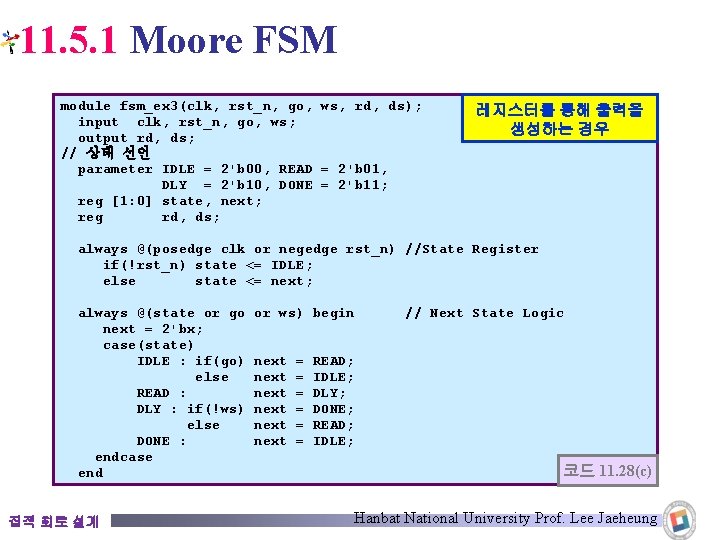

11. 5. 1 Moore FSM module fsm_ex 3(clk, rst_n, go, ws, rd, ds); input clk, rst_n, go, ws; output rd, ds; // 상태 선언 parameter IDLE = 2'b 00, READ = 2'b 01, DLY = 2'b 10, DONE = 2'b 11; reg [1: 0] state, next; reg rd, ds; 레지스터를 통해 출력을 생성하는 경우 always @(posedge clk or negedge rst_n) //State Register if(!rst_n) state <= IDLE; else state <= next; always @(state or go next = 2'bx; case(state) IDLE : if(go) else READ : DLY : if(!ws) else DONE : endcase end 집적 회로 설계 or ws) begin next next = = = // Next State Logic READ; IDLE; DLY; DONE; READ; IDLE; 코드 11. 28(c) Hanbat National University Prof. Lee Jaeheung

11. 5. 1 Moore FSM //Output Logic and output register always @(posedge clk or negedge rst_n) if(!rst_n) begin ds <= 1'b 0; rd <= 1'b 0; end else begin ds <= 1'b 0; rd <= 1'b 0; case(next) READ: rd <= 1'b 1; DLY : rd <= 1'b 1; DONE: ds <= 1'b 1; endcase endmodule 집적 회로 설계 코드 11. 28(c) Hanbat National University Prof. Lee Jaeheung

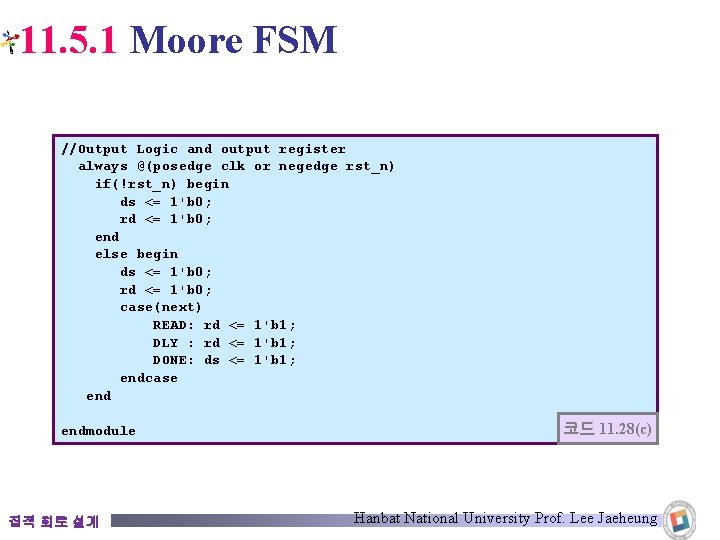

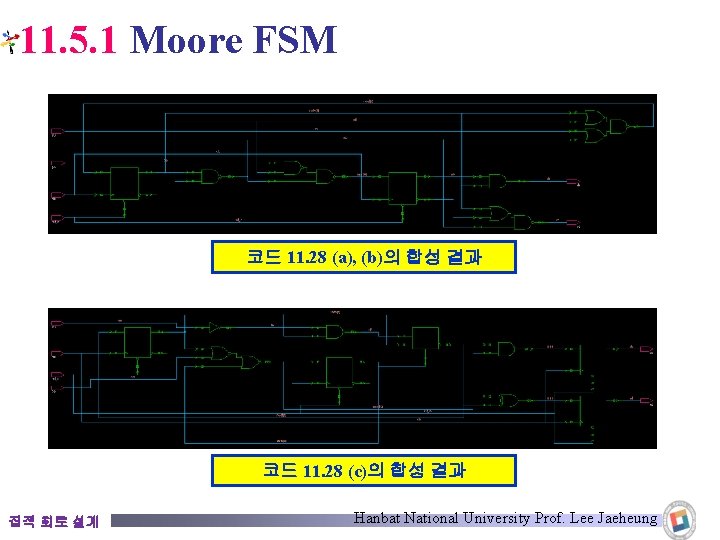

11. 5. 1 Moore FSM 코드 11. 28 (a), (b)의 합성 결과 코드 11. 28 (c)의 합성 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

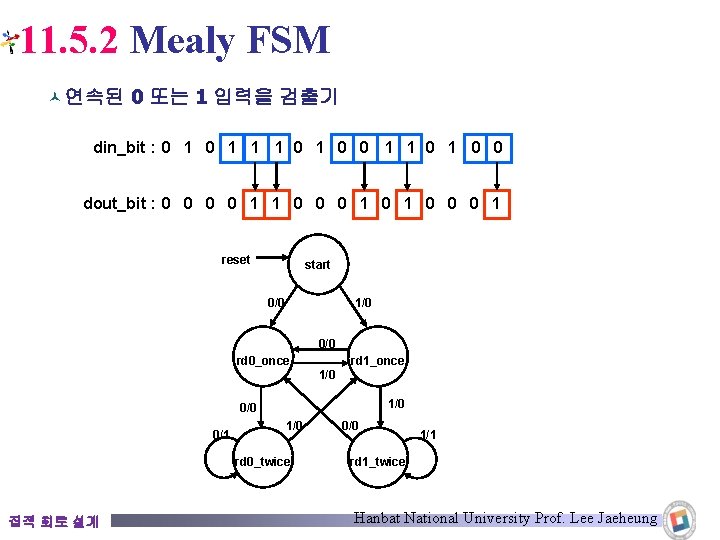

11. 5. 2 Mealy FSM © 연속된 0 또는 1 입력을 검출기 din_bit : 0 1 1 1 0 1 0 0 dout_bit : 0 0 1 1 0 0 0 1 reset start 0/0 1/0 0/0 rd 0_once rd 1_once 1/0 0/0 0/1 1/0 rd 0_twice 집적 회로 설계 0/0 1/1 rd 1_twice Hanbat National University Prof. Lee Jaeheung

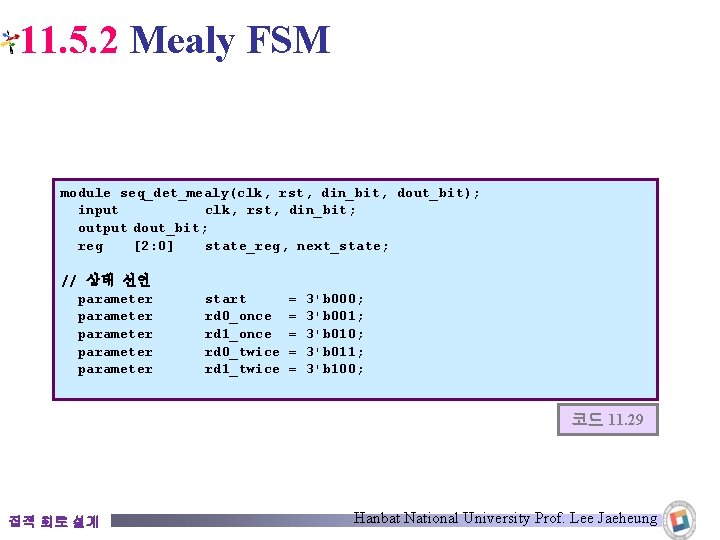

11. 5. 2 Mealy FSM module seq_det_mealy(clk, rst, din_bit, dout_bit); input clk, rst, din_bit; output dout_bit; reg [2: 0] state_reg, next_state; // 상태 선언 parameter parameter start rd 0_once rd 1_once rd 0_twice rd 1_twice = = = 3'b 000; 3'b 001; 3'b 010; 3'b 011; 3'b 100; 코드 11. 29 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

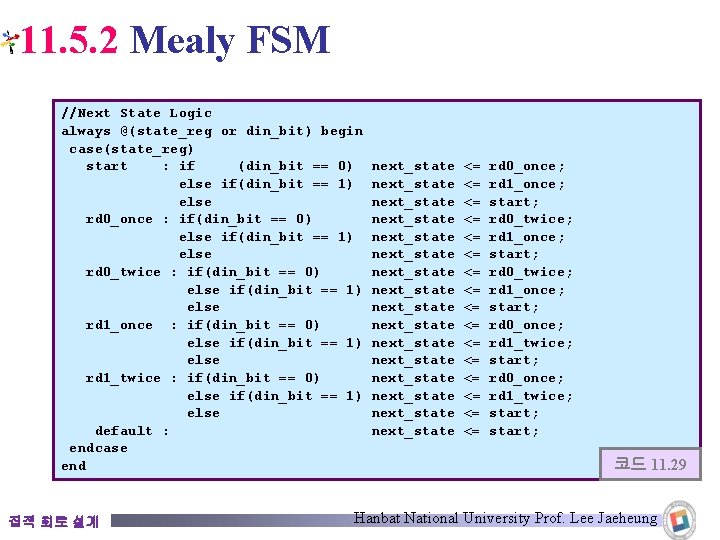

11. 5. 2 Mealy FSM //Next State Logic always @(state_reg or din_bit) begin case(state_reg) start : if (din_bit == 0) else if(din_bit == 1) else rd 0_once : if(din_bit == 0) else if(din_bit == 1) else rd 0_twice : if(din_bit == 0) else if(din_bit == 1) else rd 1_once : if(din_bit == 0) else if(din_bit == 1) else rd 1_twice : if(din_bit == 0) else if(din_bit == 1) else default : endcase end 집적 회로 설계 next_state next_state next_state next_state <= <= <= <= rd 0_once; rd 1_once; start; rd 0_twice; rd 1_once; start; rd 0_once; rd 1_twice; start; 코드 11. 29 Hanbat National University Prof. Lee Jaeheung

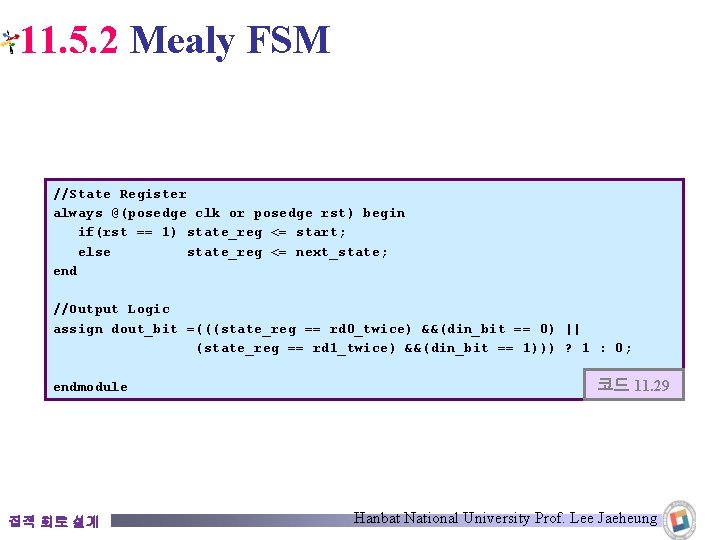

11. 5. 2 Mealy FSM //State Register always @(posedge clk or posedge rst) begin if(rst == 1) state_reg <= start; else state_reg <= next_state; end //Output Logic assign dout_bit =(((state_reg == rd 0_twice) &&(din_bit == 0) || (state_reg == rd 1_twice) &&(din_bit == 1))) ? 1 : 0; endmodule 집적 회로 설계 코드 11. 29 Hanbat National University Prof. Lee Jaeheung

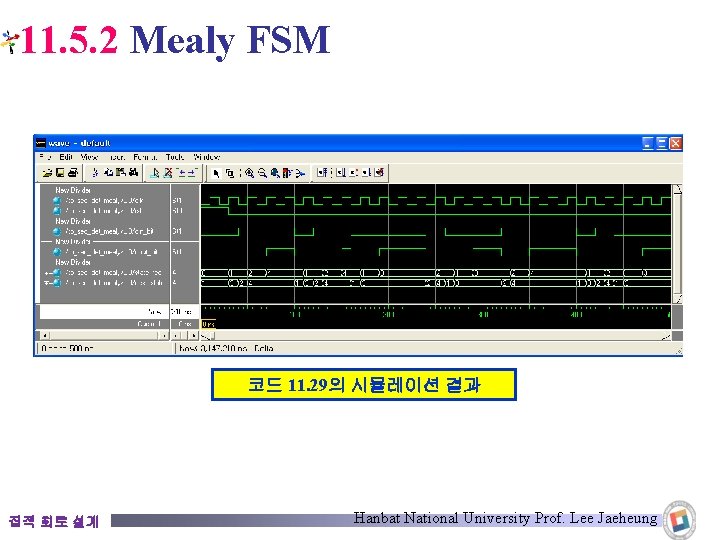

11. 5. 2 Mealy FSM 코드 11. 29의 시뮬레이션 결과 집적 회로 설계 Hanbat National University Prof. Lee Jaeheung

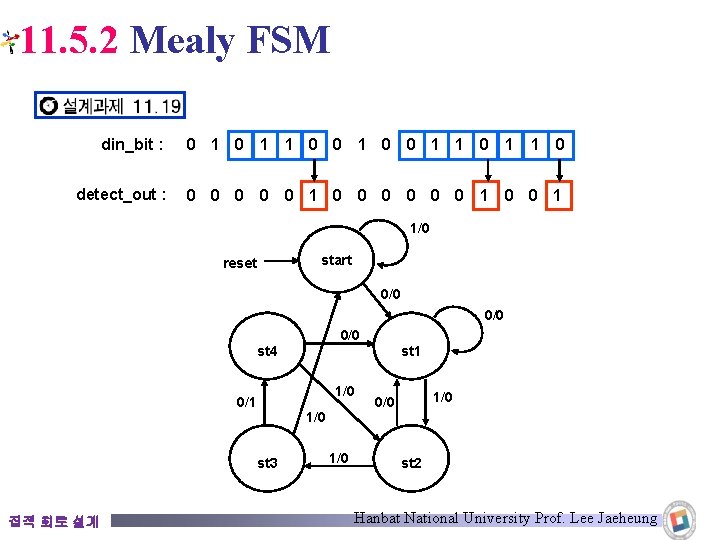

11. 5. 2 Mealy FSM din_bit : detect_out : 0 1 1 0 0 0 0 0 0 1 1/0 start reset 0/0 0/0 st 4 1/0 0/1 1/0 st 3 집적 회로 설계 st 1 1/0 0/0 st 2 Hanbat National University Prof. Lee Jaeheung

- Slides: 78