Subject Name Microelectronics Circuits Subject Code 10 EC

Subject Name: Microelectronics Circuits Subject Code: 10 EC 63 Prepared By: Arshiya Sultana, Sreepriya Kurup Department: ECE Date 9/18/2020

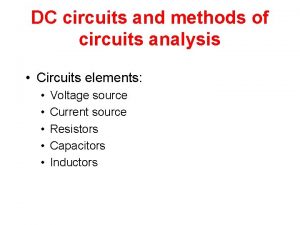

Content • UNIT 7: Digital CMOS circuits. 9/18/2020 : 7 Hrs

UNIT 5 Digital CMOS circuits Syllabus: v v v Overview Design and Performance Analysis of CMOS inverter CMOS Logic gate circuits Pass transistor logic Dynamic logic circuits 9/18/2020

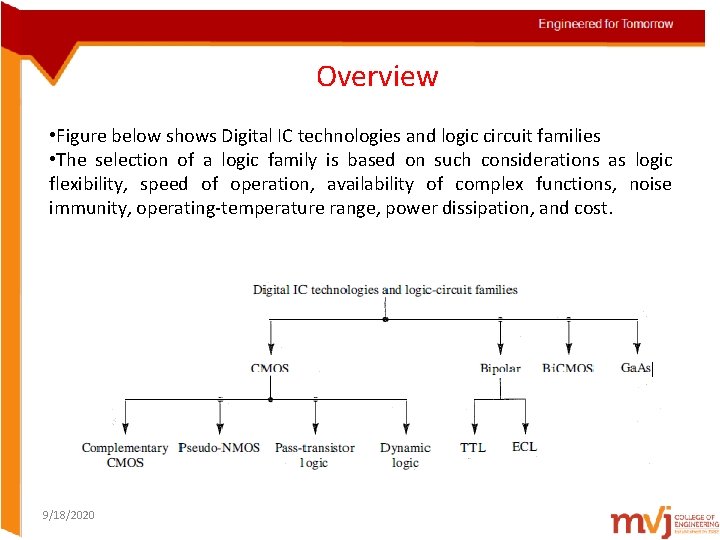

Overview • Figure below shows Digital IC technologies and logic circuit families • The selection of a logic family is based on such considerations as logic flexibility, speed of operation, availability of complex functions, noise immunity, operating-temperature range, power dissipation, and cost. 9/18/2020

Overview CMOS technology is, by a large margin, the most dominant of all the IC technologies available for digital-circuit design. 1. CMOS logic circuits dissipate much less power than bipolar logic circuits and thus one can pack more CMOS circuits on a chip than is possible with bipolar circuits. 2. The high input impedance of the MOS transistor allows the designer to use charge storage as a means for the temporary storage of information in both logic and memory circuits. This technique cannot be used in bipolar circuits. 3. The feature size (i. e. , minimum channel length) of the MOS transistor has decreased dramatically over the years, with some recently reported designs utilizing channel lengths as short as 0. 06 μm. This permits very tight circuit packing and, correspondingly, very high levels of integration. 9/18/2020

Overview Bipolar • Two logic-circuit families based on the bipolar junction transistor are Transistor-transistor logic (TTL or T 2 L) and Emitter Coupled Logic (ECL) • TTL logic was precipitated with the advent of VLSI era • ECL logic provides high speed of operation but has high power dissipation Bi. CMOS • Bi. CMOS combines the high operating speeds possible with BJTs with the low power dissipation and other excellent characteristics of CMOS. • Like CMOS, Bi. CMOS allows for the implementation of both analog and digital circuits on the same chip. • At present, Bi. CMOS is used to great advantage in special applications, including memory chips, where it requires a high-speed and lower power dissipation. Ga. As The high carrier mobility in Ga. As results in very high speeds of operation. This has been demonstrated in a number of digital IC chips utilizing Ga. As technology. 9/18/2020

Overview Logic Circuit Characterization The following parameters are usually used to characterize the operation and performance of a logic-circuit family 1. Noise Margin 2. Propagation delay 3. Power dissipation 4. Delay – Power product 5. Silicon Area 6. Fan in and Fan out 9/18/2020

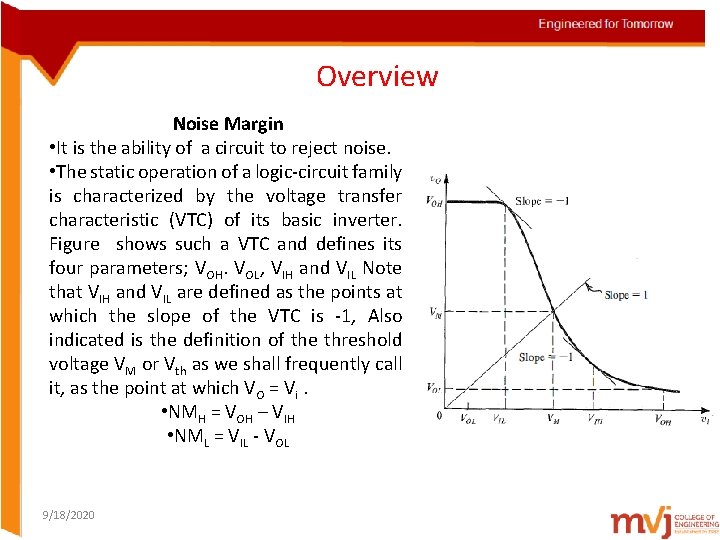

Overview Noise Margin • It is the ability of a circuit to reject noise. • The static operation of a logic-circuit family is characterized by the voltage transfer characteristic (VTC) of its basic inverter. Figure shows such a VTC and defines its four parameters; VOH. VOL, VIH and VIL Note that VIH and VIL are defined as the points at which the slope of the VTC is -1, Also indicated is the definition of the threshold voltage VM or Vth as we shall frequently call it, as the point at which VO = Vi. • NMH = VOH – VIH • NML = VIL - VOL 9/18/2020

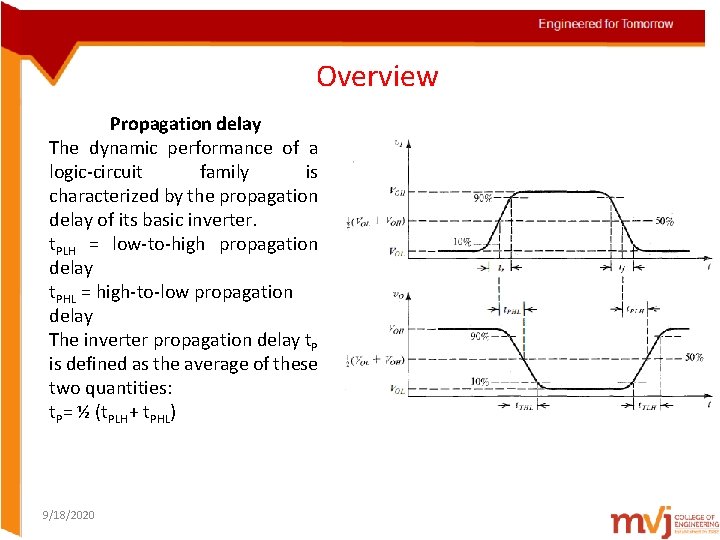

Overview Propagation delay The dynamic performance of a logic-circuit family is characterized by the propagation delay of its basic inverter. t. PLH = low-to-high propagation delay t. PHL = high-to-low propagation delay The inverter propagation delay t. P is defined as the average of these two quantities: t. P= ½ (t. PLH+ t. PHL) 9/18/2020

Overview Power Dissipation • There are two types of power dissipation in a logic gate: static and dynamic. Static power refers to the power that the gate dissipates in the absence of switching action. It results from the presence of a path in the gate circuit between the power supply and ground in one or both of its two states. • Dynamic power, on the other hand, occurs only when the gate is switched: An inverter operated from a power supply VDD and driving a load capacitance C, dissipates dynamic power PD, PD =f CVDD 2 • Where f is the frequency at which the inverter is being switched. 9/18/2020

Overview Delay – Power product • One is usually interested in high-. speed performance (low t. P) combined with low power dissipation. • Unfortunately, these two requirements are often in conflict; when designing a gate, if one attempts to reduce power dissipation by decreasing the supply voltage, or the supply current, or both, the current-driving capability of the gate decreases. This in turn results in longer times to charge and discharge the load and parasitic capacitances, and thus the propagation delay increases. • DP =PD t. P • where PD is the power dissipation of the gate. Note that DP has the units of joules. • The lower the DP figure for a logic family, the more effective it is. 9/18/2020

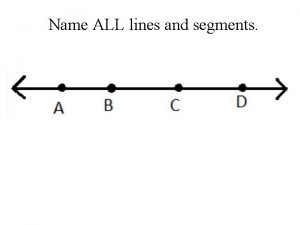

Overview Silicon Area • Objective in the design of digital VLSI circuits is the minimization of silicon area per logic gate. Smaller area requirement enables the fabrication of a larger number of gates per chip, which has economic and space advantages from a system design standpoint. • Area reduction occurs in three different ways: through advances in processing technology, through advances in circuit-design techniques, and through careful chip layout. Fan-In and Fan-Out • The fan-in of a gate is the number of its inputs. • Fan-out is the maximum number of similar gates that a gate can drive while remaining within guaranteed specifications. 9/18/2020

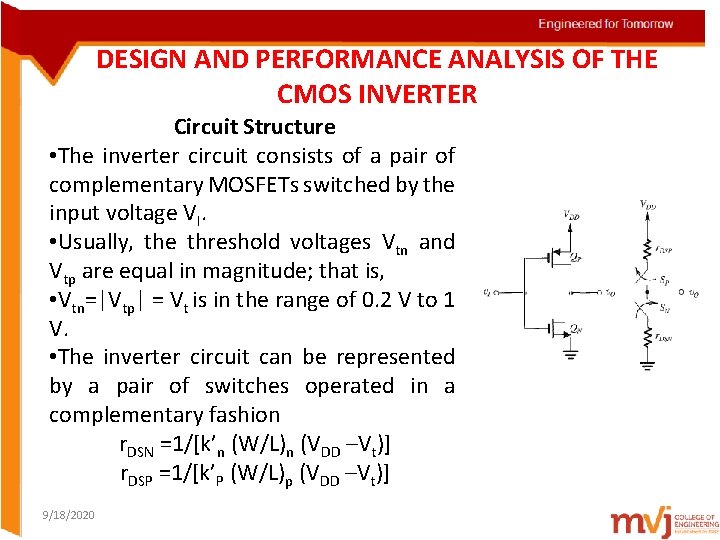

DESIGN AND PERFORMANCE ANALYSIS OF THE CMOS INVERTER Circuit Structure • The inverter circuit consists of a pair of complementary MOSFETs switched by the input voltage VI. • Usually, the threshold voltages Vtn and Vtp are equal in magnitude; that is, • Vtn=|Vtp| = Vt is in the range of 0. 2 V to 1 V. • The inverter circuit can be represented by a pair of switches operated in a complementary fashion r. DSN =1/[k’n (W/L)n (VDD –Vt)] r. DSP =1/[k’P (W/L)p (VDD –Vt)] 9/18/2020

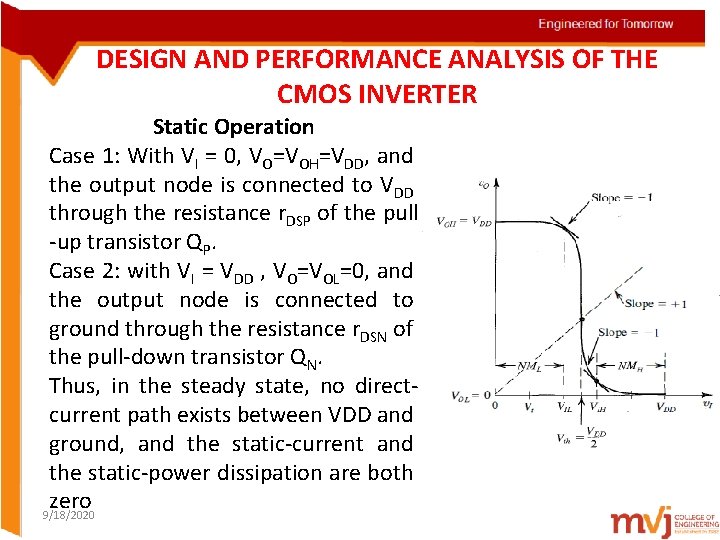

DESIGN AND PERFORMANCE ANALYSIS OF THE CMOS INVERTER Static Operation Case 1: With VI = 0, VO=VOH=VDD, and the output node is connected to VDD through the resistance r. DSP of the pull -up transistor QP. Case 2: with VI = VDD , VO=VOL=0, and the output node is connected to ground through the resistance r. DSN of the pull-down transistor QN. Thus, in the steady state, no directcurrent path exists between VDD and ground, and the static-current and the static-power dissipation are both zero 9/18/2020

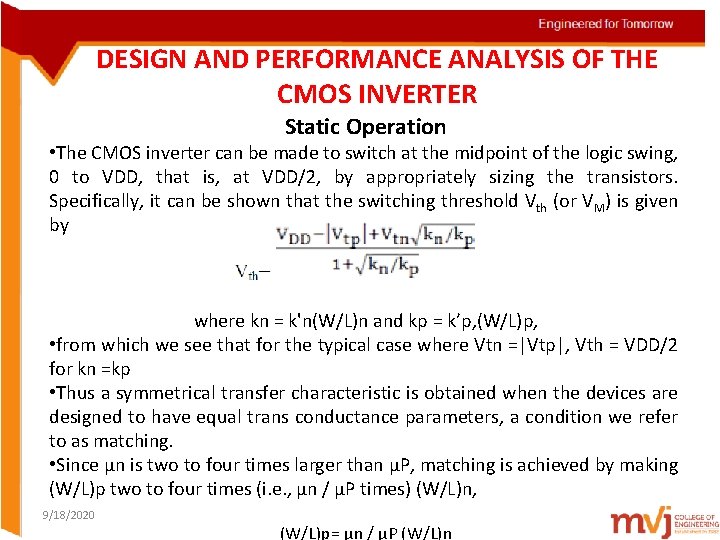

DESIGN AND PERFORMANCE ANALYSIS OF THE CMOS INVERTER Static Operation • The CMOS inverter can be made to switch at the midpoint of the logic swing, 0 to VDD, that is, at VDD/2, by appropriately sizing the transistors. Specifically, it can be shown that the switching threshold Vth (or VM) is given by where kn = k'n(W/L)n and kp = k’p, (W/L)p, • from which we see that for the typical case where Vtn =|Vtp|, Vth = VDD/2 for kn =kp • Thus a symmetrical transfer characteristic is obtained when the devices are designed to have equal trans conductance parameters, a condition we refer to as matching. • Since μn is two to four times larger than μP, matching is achieved by making (W/L)p two to four times (i. e. , μn / μP times) (W/L)n, 9/18/2020 (W/L)p= μn / μP (W/L)n

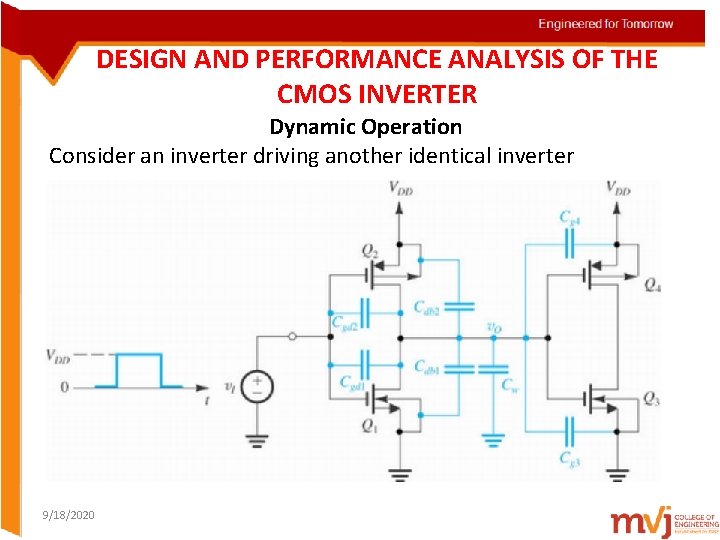

DESIGN AND PERFORMANCE ANALYSIS OF THE CMOS INVERTER Dynamic Operation Consider an inverter driving another identical inverter 9/18/2020

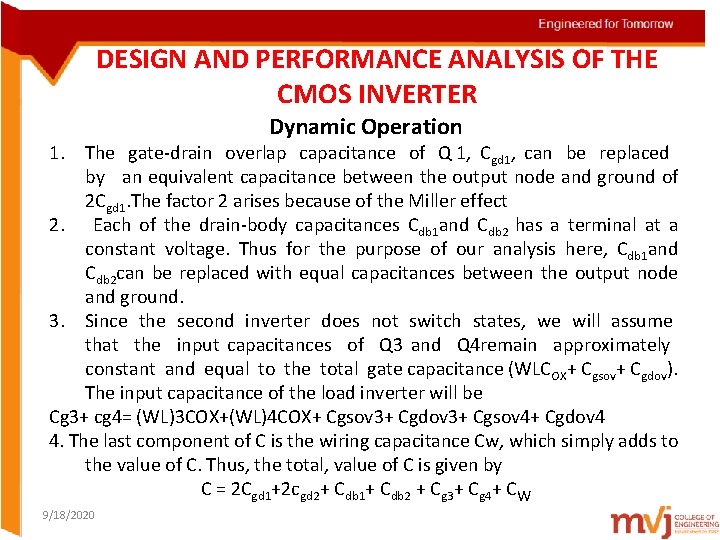

DESIGN AND PERFORMANCE ANALYSIS OF THE CMOS INVERTER Dynamic Operation 1. The gate-drain overlap capacitance of Q 1, Cgd 1, can be replaced by an equivalent capacitance between the output node and ground of 2 Cgd 1. The factor 2 arises because of the Miller effect 2. Each of the drain-body capacitances Cdb 1 and Cdb 2 has a terminal at a constant voltage. Thus for the purpose of our analysis here, Cdb 1 and Cdb 2 can be replaced with equal capacitances between the output node and ground. 3. Since the second inverter does not switch states, we will assume that the input capacitances of Q 3 and Q 4 remain approximately constant and equal to the total gate capacitance (WLCOX+ Cgsov+ Cgdov). The input capacitance of the load inverter will be Cg 3+ cg 4= (WL)3 COX+(WL)4 COX+ Cgsov 3+ Cgdov 3+ Cgsov 4+ Cgdov 4 4. The last component of C is the wiring capacitance Cw, which simply adds to the value of C. Thus, the total, value of C is given by C = 2 Cgd 1+2 cgd 2+ Cdb 1+ Cdb 2 + Cg 3+ Cg 4+ CW 9/18/2020

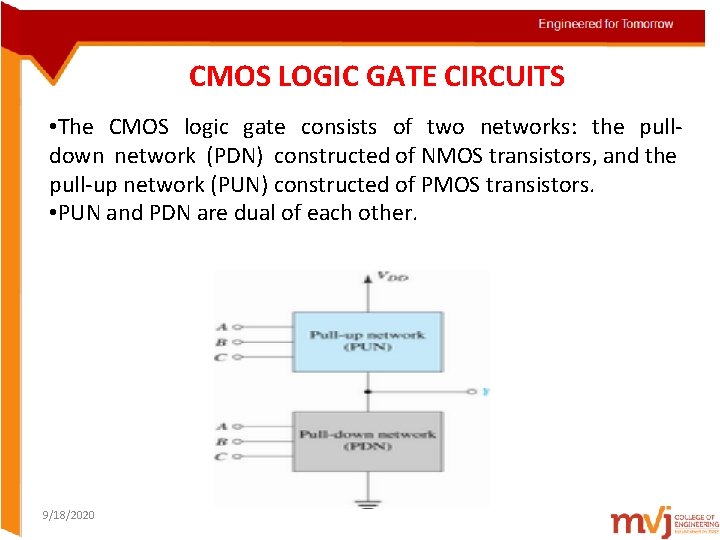

CMOS LOGIC GATE CIRCUITS • The CMOS logic gate consists of two networks: the pulldown network (PDN) constructed of NMOS transistors, and the pull-up network (PUN) constructed of PMOS transistors. • PUN and PDN are dual of each other. 9/18/2020

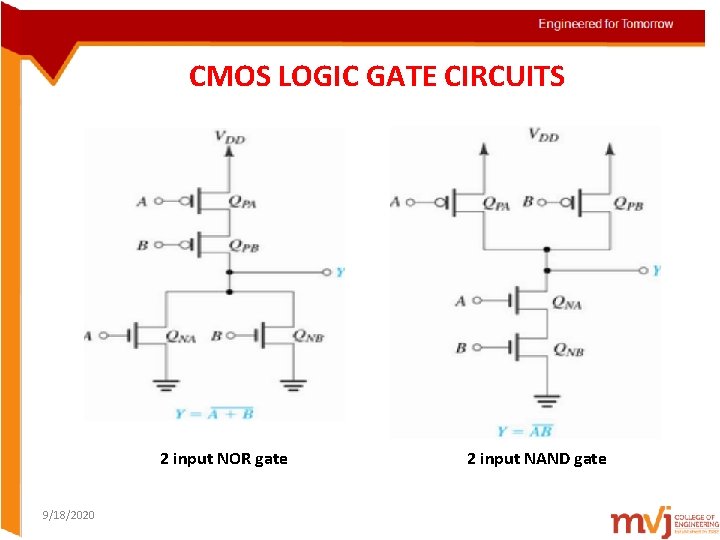

CMOS LOGIC GATE CIRCUITS 2 input NOR gate 9/18/2020 2 input NAND gate

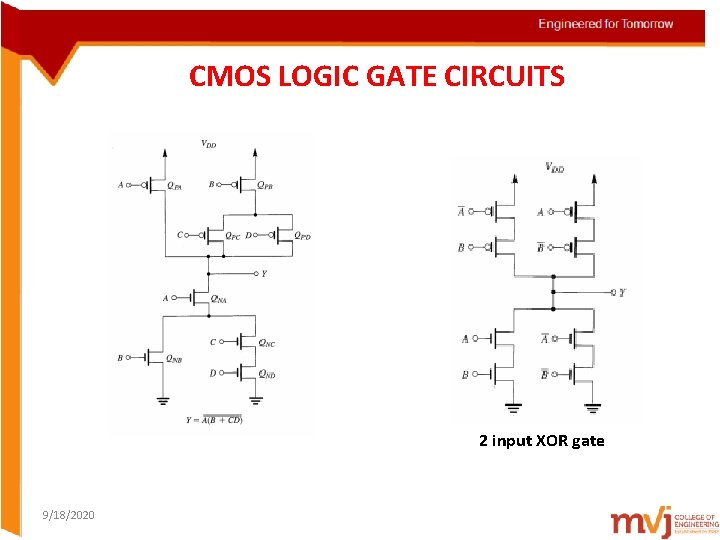

CMOS LOGIC GATE CIRCUITS 2 input XOR gate 9/18/2020

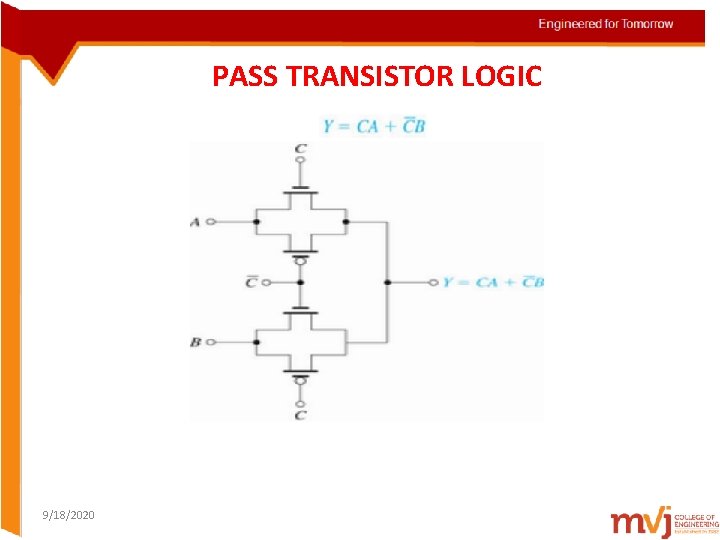

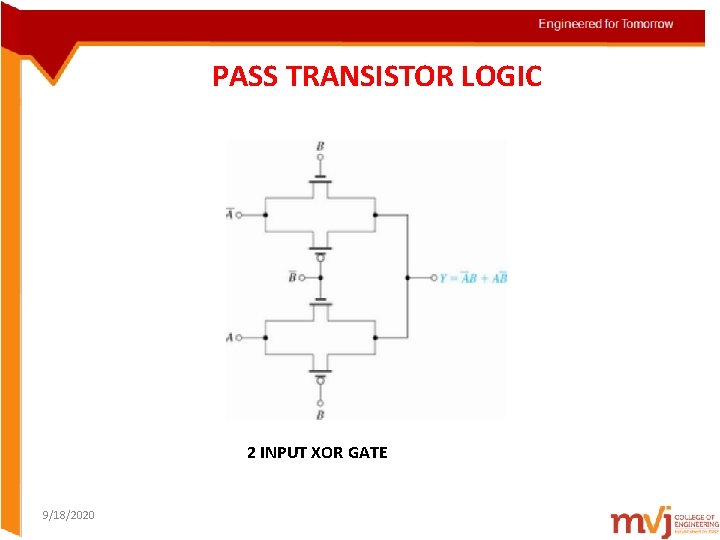

PASS TRANSISTOR LOGIC 9/18/2020

PASS TRANSISTOR LOGIC 2 INPUT XOR GATE 9/18/2020

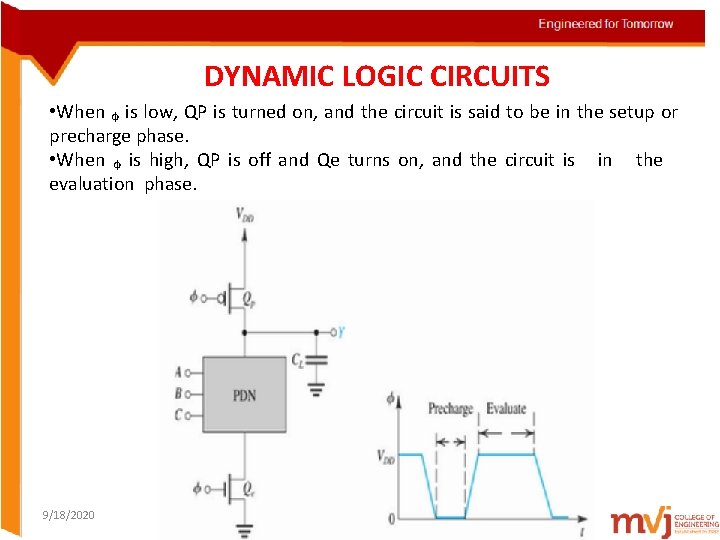

DYNAMIC LOGIC CIRCUITS • When ᵩ is low, QP is turned on, and the circuit is said to be in the setup or precharge phase. • When ᵩ is high, QP is off and Qe turns on, and the circuit is in the evaluation phase. 9/18/2020

- Slides: 23