Subject Name Microelectronics Circuits Subject Code 10 EC

Subject Name: Microelectronics Circuits Subject Code: 10 EC 63 Prepared By: Arshiya Sultana, Sreepriya Kurup Department: ECE Date: 12/05/2015 1/5/2022

Content • UNIT 6: Operational Amplifiers 1/5/2022

UNIT 6 OPERATIONAL AMPLIFIERS Syllabus: v The Ideal Opamp v The Inverting Configuration v The weighted summer v The Non inverting configuration v The difference amplifiers v The Instrumentation Amplifier v Large Signal Operation Of Opamps v DC Imperfections v Integrators v Differentiators 1/5/2022

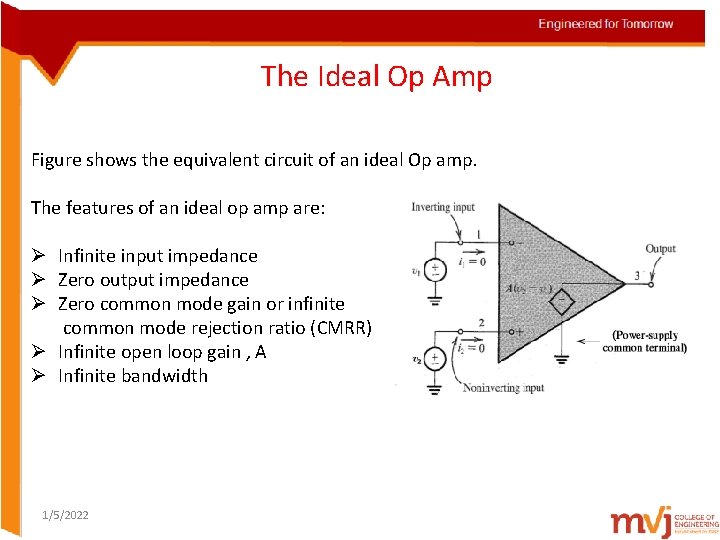

The Ideal Op Amp Figure shows the equivalent circuit of an ideal Op amp. The features of an ideal op amp are: Ø Infinite input impedance Ø Zero output impedance Ø Zero common mode gain or infinite common mode rejection ratio (CMRR) Ø Infinite open loop gain , A Ø Infinite bandwidth 1/5/2022

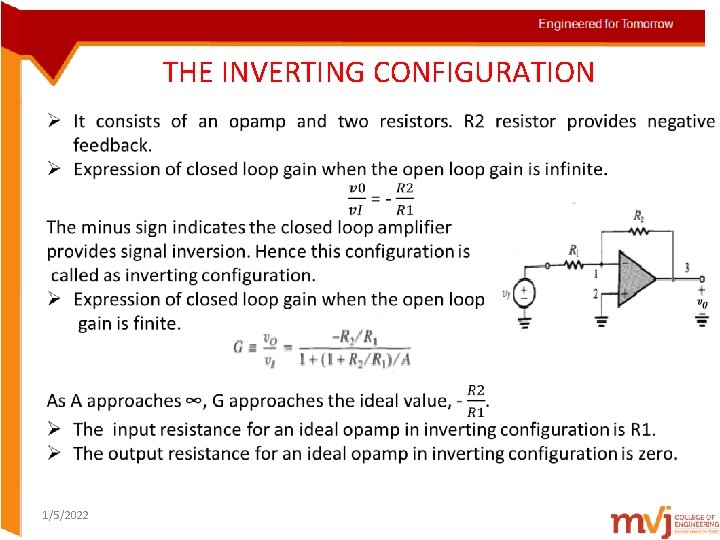

THE INVERTING CONFIGURATION 1/5/2022

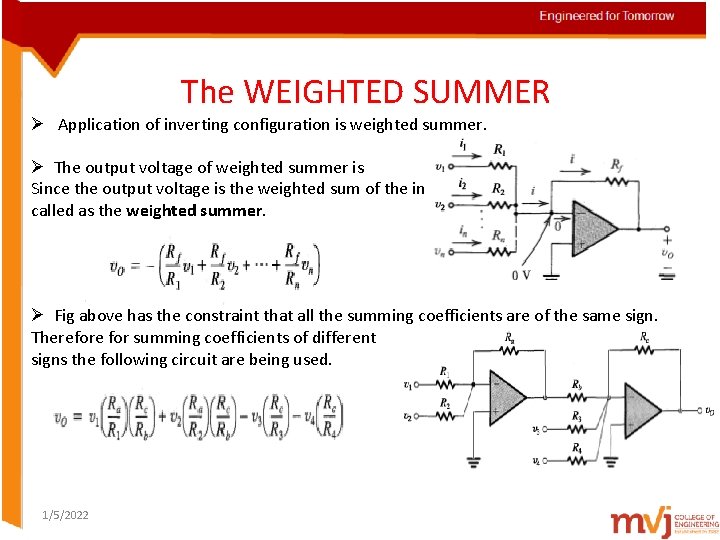

The WEIGHTED SUMMER Ø Application of inverting configuration is weighted summer. Ø The output voltage of weighted summer is Since the output voltage is the weighted sum of the input signals, v 1, v 2, …vn. This circuit is called as the weighted summer. Ø Fig above has the constraint that all the summing coefficients are of the same sign. Therefore for summing coefficients of different signs the following circuit are being used. 1/5/2022

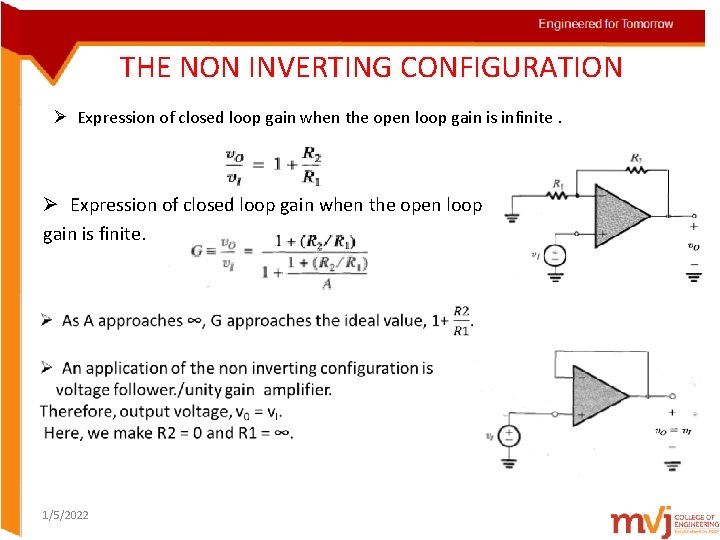

THE NON INVERTING CONFIGURATION Ø Expression of closed loop gain when the open loop gain is infinite. Ø Expression of closed loop gain when the open loop gain is finite. 1/5/2022

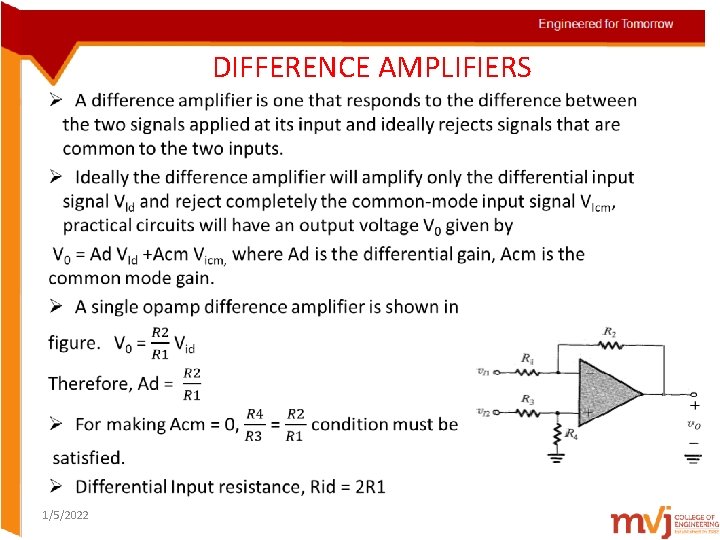

DIFFERENCE AMPLIFIERS • 1/5/2022

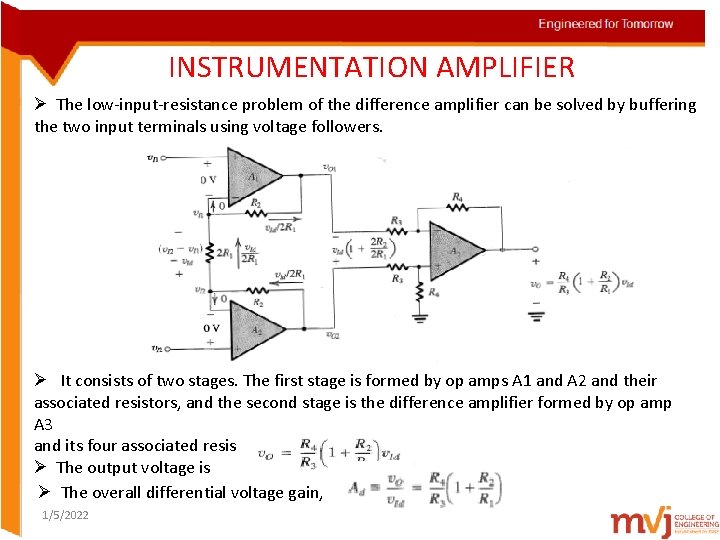

INSTRUMENTATION AMPLIFIER Ø The low-input-resistance problem of the difference amplifier can be solved by buffering the two input terminals using voltage followers. Ø It consists of two stages. The first stage is formed by op amps A 1 and A 2 and their associated resistors, and the second stage is the difference amplifier formed by op amp A 3 and its four associated resistors. Ø The output voltage is Ø The overall differential voltage gain, 1/5/2022

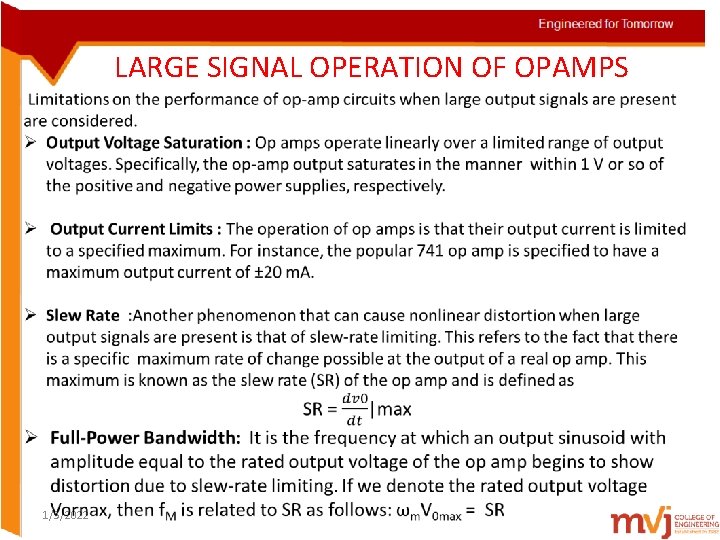

LARGE SIGNAL OPERATION OF OPAMPS 1/5/2022

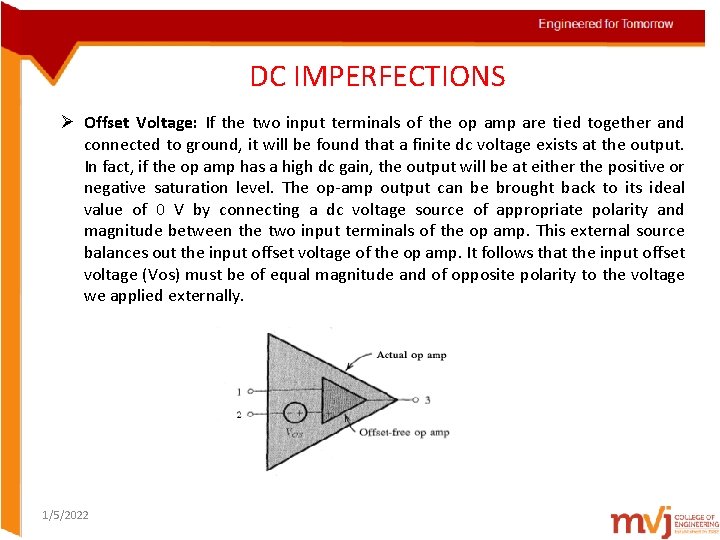

DC IMPERFECTIONS Ø Offset Voltage: If the two input terminals of the op amp are tied together and connected to ground, it will be found that a finite dc voltage exists at the output. In fact, if the op amp has a high dc gain, the output will be at either the positive or negative saturation level. The op-amp output can be brought back to its ideal value of 0 V by connecting a dc voltage source of appropriate polarity and magnitude between the two input terminals of the op amp. This external source balances out the input offset voltage of the op amp. It follows that the input offset voltage (Vos) must be of equal magnitude and of opposite polarity to the voltage we applied externally. 1/5/2022

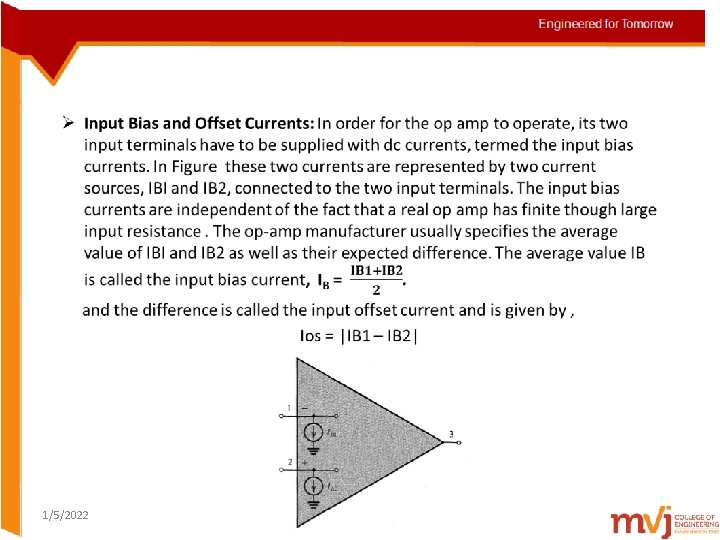

1/5/2022

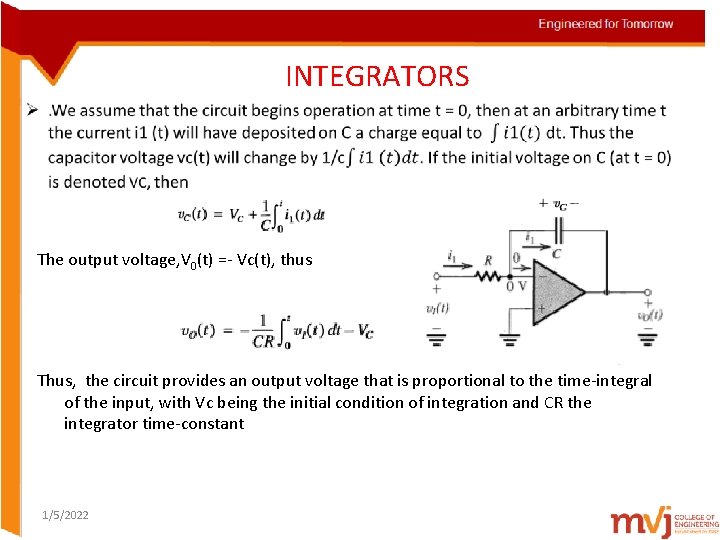

INTEGRATORS The output voltage, V 0(t) =- Vc(t), thus Thus, the circuit provides an output voltage that is proportional to the time-integral of the input, with Vc being the initial condition of integration and CR the integrator time-constant 1/5/2022

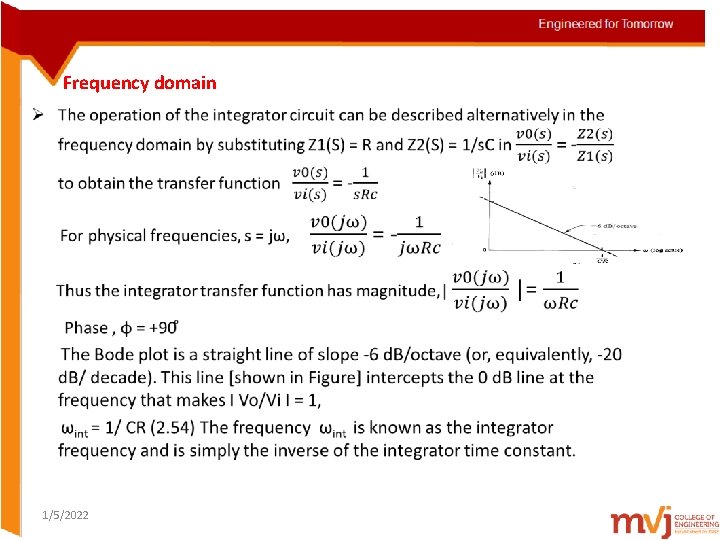

Frequency domain 1/5/2022

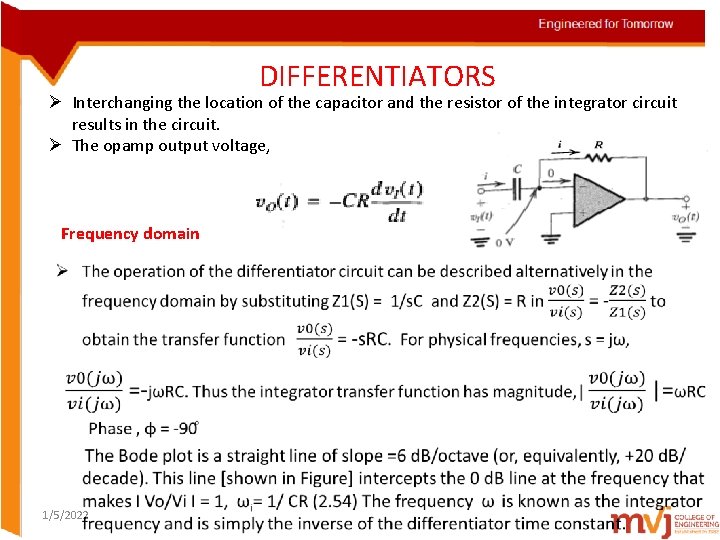

DIFFERENTIATORS Ø Interchanging the location of the capacitor and the resistor of the integrator circuit results in the circuit. Ø The opamp output voltage, Frequency domain 1/5/2022

- Slides: 15