Structural RTL for the br and brl instructions

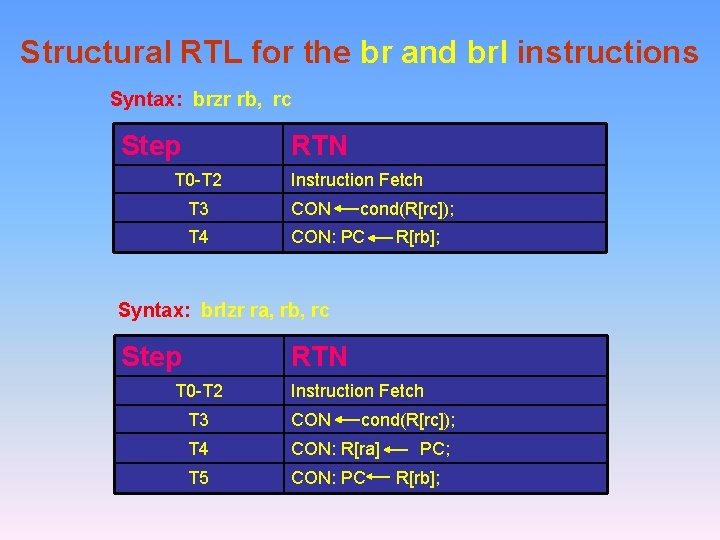

Structural RTL for the br and brl instructions Syntax: brzr rb, rc Step RTN T 0 -T 2 Instruction Fetch T 3 CON cond(R[rc]); T 4 CON: PC R[rb]; Syntax: brlzr ra, rb, rc Step RTN T 0 -T 2 Instruction Fetch T 3 CON cond(R[rc]); T 4 CON: R[ra] T 5 CON: PC PC; R[rb];

Review

CS 501 Advanced Computer Architecture Lecture 13 Dr. Noor Muhammad Sheikh

Structural RTL for the br and brl instructions Syntax: brzr rb, rc Step RTN T 0 -T 2 Instruction Fetch T 3 CON cond(R[rc]); T 4 CON: PC R[rb]; Syntax: brlzr ra, rb, rc Step RTN T 0 -T 2 Instruction Fetch T 3 CON cond(R[rc]); T 4 CON: R[ra] T 5 CON: PC PC; R[rb]; Question: What will be the difference for the br rb, brlnv ra and brl ra, rb instructions ?

Structural RTL for the shr instruction Syntax: shr ra, rb, c 3 OR shr ra, rb, rc Step T 0 -T 2 RTN Instruction fetch T 3 n<4. . 0> IR<4. . 0>; T 4 (N = 0) : (n<4. . 0> T 5 C T 6 R[ra] R[rc]<4. . 0>); Remember: C 3 is the count field, i. e. C 3<4. . 0>: = IR<4. . 0> (Nα 0) © R[rb]<31. . N>; C; n represents a 5 -bit register; IR bits 0 to 4 are copied into it N is the decimal value of the number in this register other instructions that will have similar tables are: shl, shc, shra e. g. , for shra, T 5 will have C← (NαR[rb]<31>) © R[rb]<31. . N>;

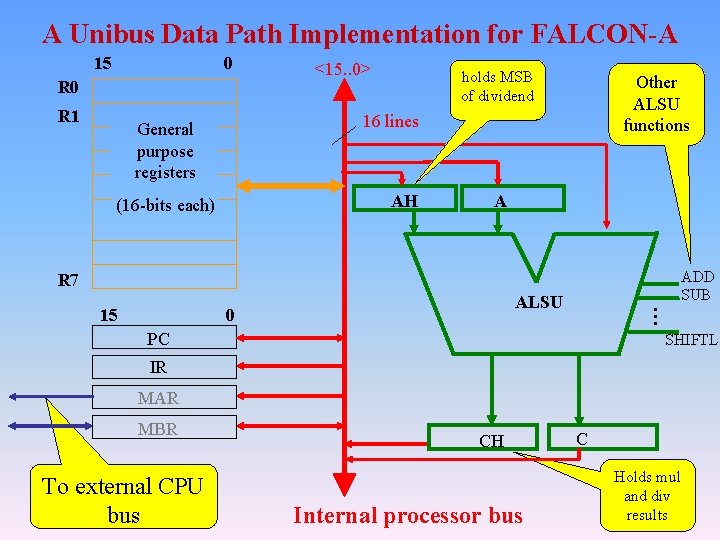

A Unibus Data Path Implementation for FALCON-A 15 0 R 1 <15. . 0> holds MSB of dividend Other ALSU functions 16 lines General purpose registers AH (16 -bits each) A ADD SUB R 7 0 … 15 ALSU PC SHIFTL IR MAR MBR To external CPU bus CH Internal processor bus C Holds mul and div results

Structural RTL for the sub instruction Format: sub ra, rb, rc Step Instruction Fetch Instruction Execute RTL T 0 MAR PC, C PC + 2; T 1 MBR M[MAR], PC T 2 IR T 3 A R[rb]; T 4 C A - R[rc]; T 5 R[ra] C; MBR; C; At the end of each sequence, the timing step generator is initialized to T 0

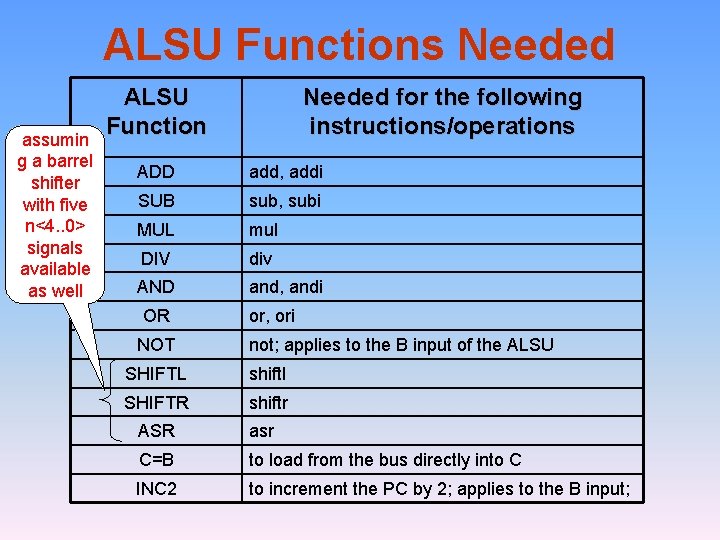

ALSU Functions Needed assumin g a barrel shifter with five n<4. . 0> signals available as well ALSU Function Needed for the following instructions/operations ADD add, addi SUB sub, subi MUL mul DIV div AND and, andi OR NOT or, ori not; applies to the B input of the ALSU SHIFTL shiftl SHIFTR shiftr ASR asr C=B to load from the bus directly into C INC 2 to increment the PC by 2; applies to the B input;

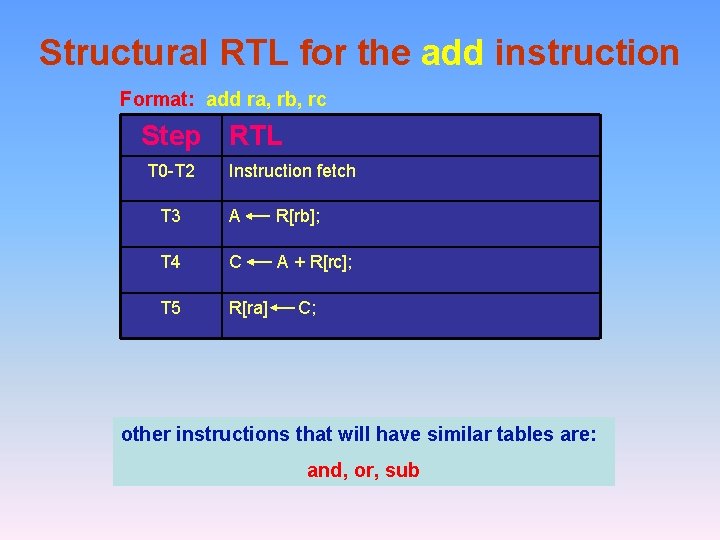

Structural RTL for the add instruction Format: add ra, rb, rc Step RTL T 0 -T 2 Instruction fetch T 3 A R[rb]; T 4 C A + R[rc]; T 5 R[ra] C; other instructions that will have similar tables are: and, or, sub

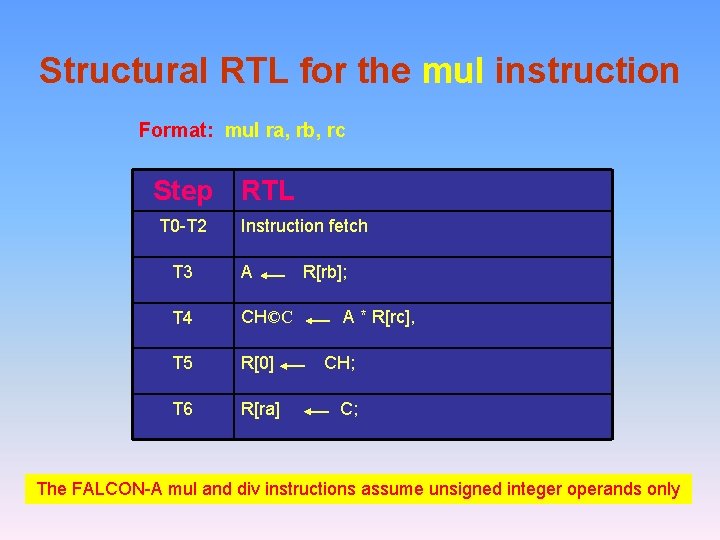

Structural RTL for the mul instruction Format: mul ra, rb, rc Step RTL T 0 -T 2 Instruction fetch T 3 A T 4 CH©C T 5 R[0] T 6 R[ra] R[rb]; A * R[rc], CH; C; The FALCON-A mul and div instructions assume unsigned integer operands only

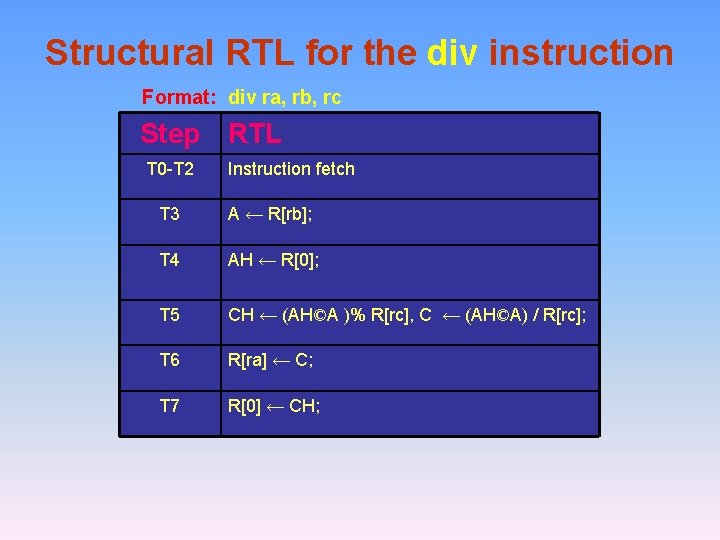

Structural RTL for the div instruction Format: div ra, rb, rc Step RTL T 0 -T 2 Instruction fetch T 3 A ← R[rb]; T 4 AH ← R[0]; T 5 CH ← (AH©A )% R[rc], C ← (AH©A) / R[rc]; T 6 R[ra] ← C; T 7 R[0] ← CH;

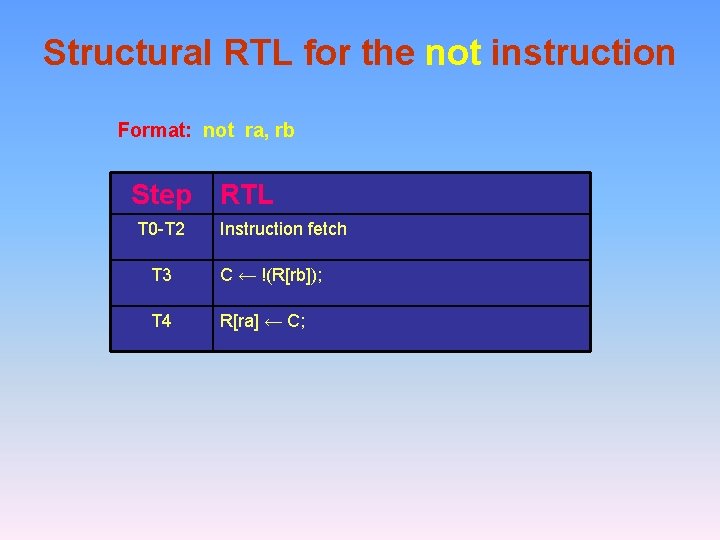

Structural RTL for the not instruction Format: not ra, rb Step RTL T 0 -T 2 Instruction fetch T 3 C ← !(R[rb]); T 4 R[ra] ← C;

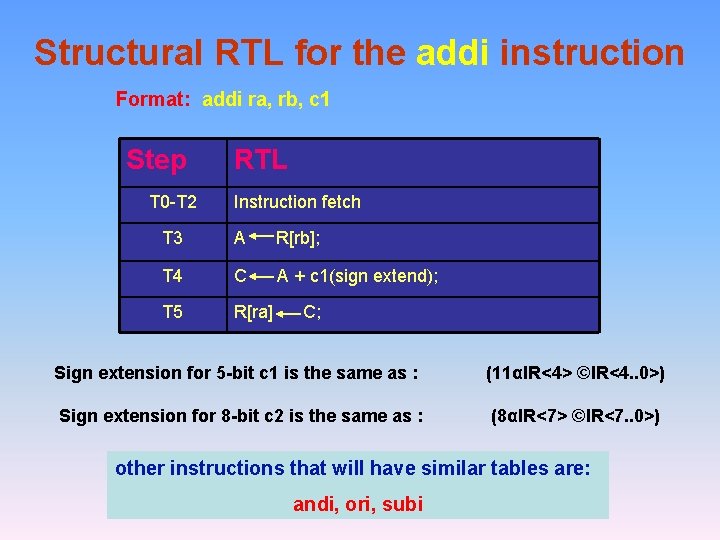

Structural RTL for the addi instruction Format: addi ra, rb, c 1 Step T 0 -T 2 RTL Instruction fetch T 3 A R[rb]; T 4 C A + c 1(sign extend); T 5 R[ra] C; Sign extension for 5 -bit c 1 is the same as : (11αIR<4> ©IR<4. . 0>) Sign extension for 8 -bit c 2 is the same as : (8αIR<7> ©IR<7. . 0>) other instructions that will have similar tables are: andi, ori, subi

![RTL for the load and store instructions Format: load ra, [rb+c 1] Step RTL RTL for the load and store instructions Format: load ra, [rb+c 1] Step RTL](http://slidetodoc.com/presentation_image_h2/abde7a9ab1265d918cc430672d1affa2/image-14.jpg)

RTL for the load and store instructions Format: load ra, [rb+c 1] Step RTL for Id T 0 -T 2 Format: store ra, [rb+c 1] RTL for st Instruction fetch T 3 A A T 4 C A + (11αIR<4> ©IR<4. . 0>); C T 5 MAR C; T 6 MBR M[MAR]; MBR R [ra]; T 7 R[ra] MBR; M[MAR] R[rb]; C; sign extension of c 1 R[rb]; A + (11αIR<4> ©IR<4. . 0>); MBR; load and store are the same up to step T 5

![Structural RTL for the jump instructions Format: jz ra, [c 2] Step T 0 Structural RTL for the jump instructions Format: jz ra, [c 2] Step T 0](http://slidetodoc.com/presentation_image_h2/abde7a9ab1265d918cc430672d1affa2/image-15.jpg)

Structural RTL for the jump instructions Format: jz ra, [c 2] Step T 0 -T 2 RTN Instruction Fetch T 3 CON ← cond(R[ra]); T 4 A ← PC; T 5 C ← A + c 2(sign extend); T 6 PC ← C;

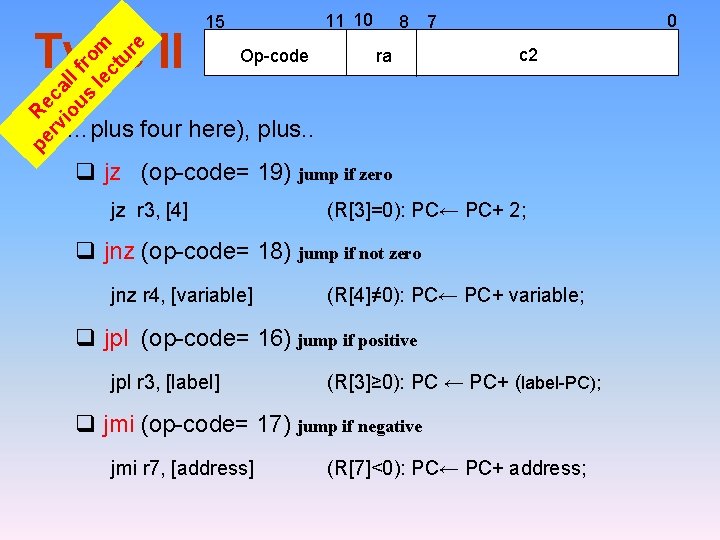

pe Re rv ca io ll us fr le om ct ur e Type II 11 10 15 Op-code 8 ra 0 7 c 2 Ø …plus four here), plus. . q jz (op-code= 19) jump if zero jz r 3, [4] (R[3]=0): PC← PC+ 2; q jnz (op-code= 18) jump if not zero jnz r 4, [variable] (R[4]≠ 0): PC← PC+ variable; q jpl (op-code= 16) jump if positive jpl r 3, [label] (R[3]≥ 0): PC ← PC+ (label-PC); q jmi (op-code= 17) jump if negative jmi r 7, [address] (R[7]<0): PC← PC+ address;

- Slides: 16