STRUCTURAL MODELING II Component Instantiation Structural descriptions consists

![Component instantiation The syntax is Component-label : component_name [port map (association-list)]; � The port Component instantiation The syntax is Component-label : component_name [port map (association-list)]; � The port](https://slidetodoc.com/presentation_image_h2/6131fa7dee603a0580c4718210aff7d8/image-5.jpg)

- Slides: 28

STRUCTURAL MODELING II

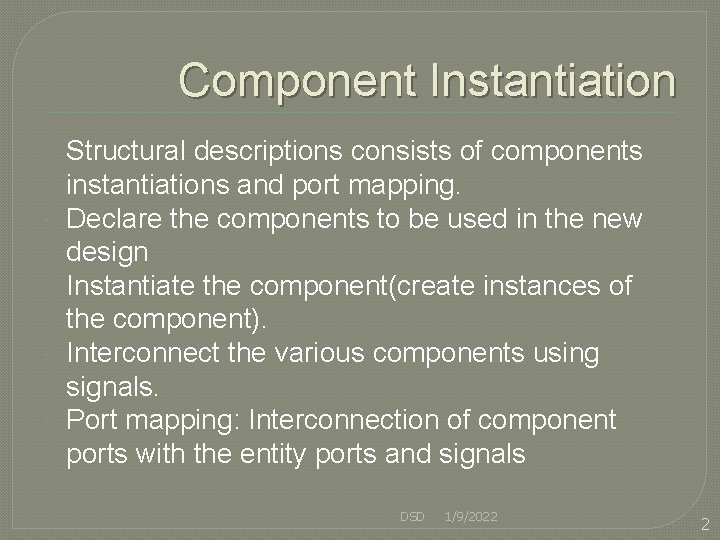

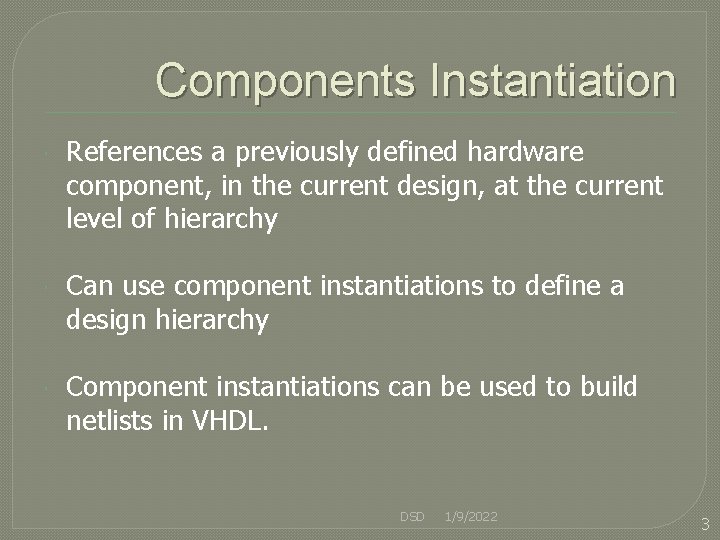

Component Instantiation Structural descriptions consists of components instantiations and port mapping. Declare the components to be used in the new design Instantiate the component(create instances of the component). Interconnect the various components using signals. Port mapping: Interconnection of component ports with the entity ports and signals DSD 1/9/2022 2

Components Instantiation References a previously defined hardware component, in the current design, at the current level of hierarchy Can use component instantiations to define a design hierarchy Component instantiations can be used to build netlists in VHDL. DSD 1/9/2022 3

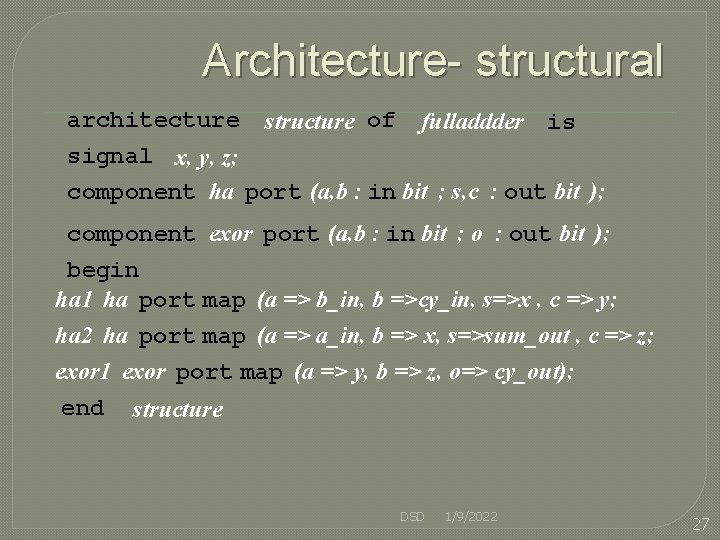

Component instantiation �A component instantiation statement indicates • A name for this instance of the component. • The name of a component to include in the current entity • The connection method for a component’s ports. DSD 1/9/2022 4

![Component instantiation The syntax is Componentlabel componentname port map associationlist The port Component instantiation The syntax is Component-label : component_name [port map (association-list)]; � The port](https://slidetodoc.com/presentation_image_h2/6131fa7dee603a0580c4718210aff7d8/image-5.jpg)

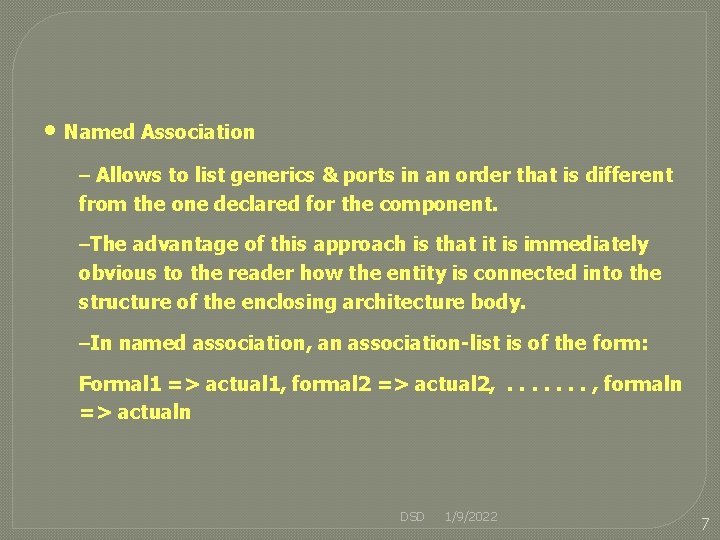

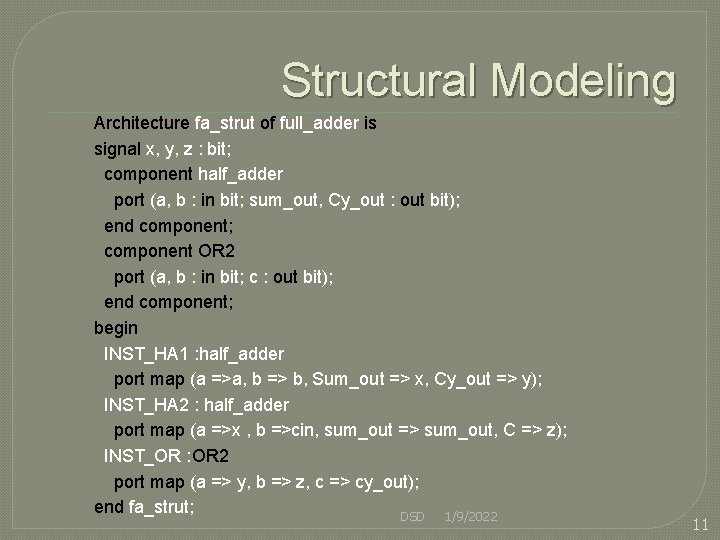

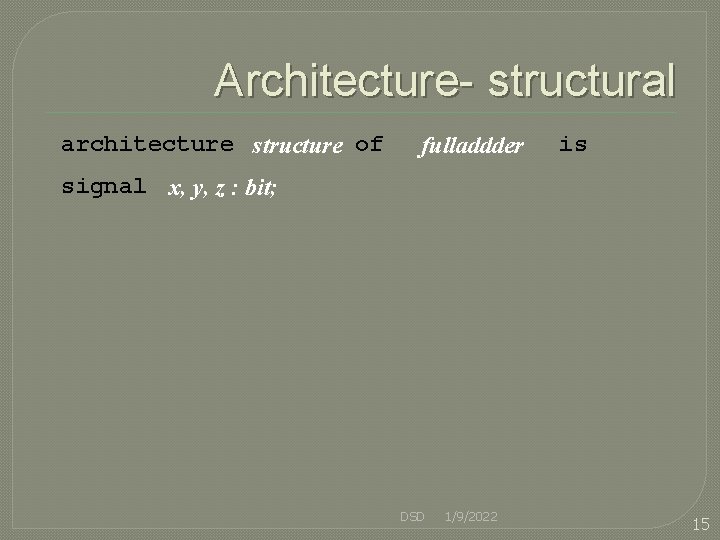

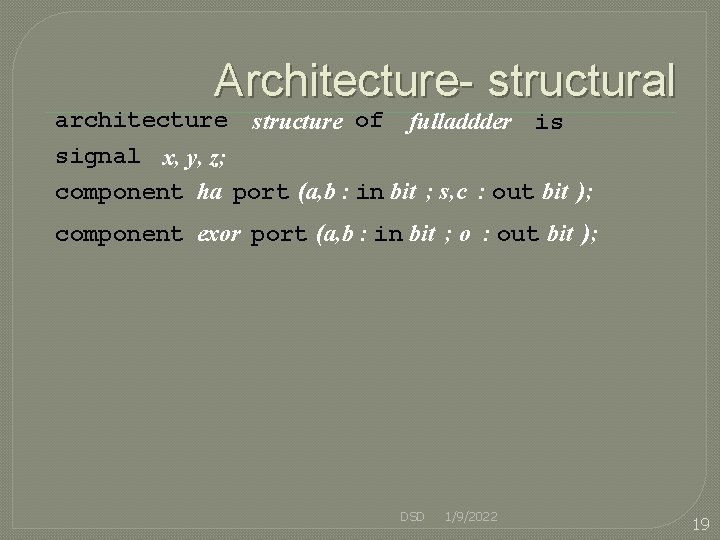

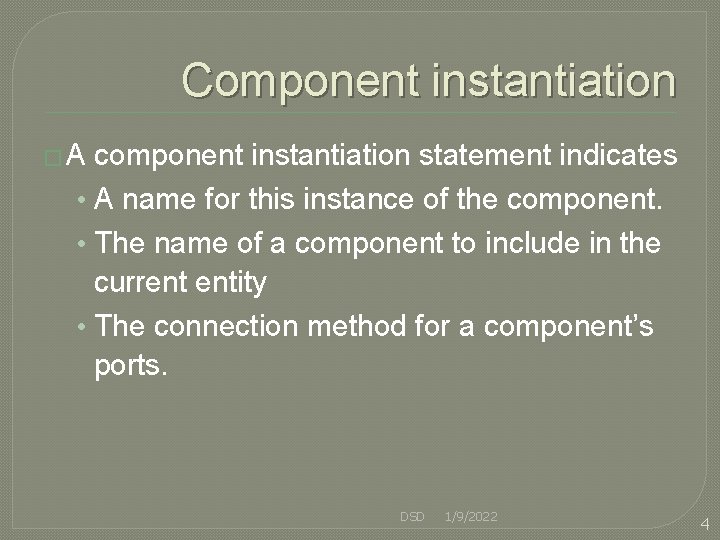

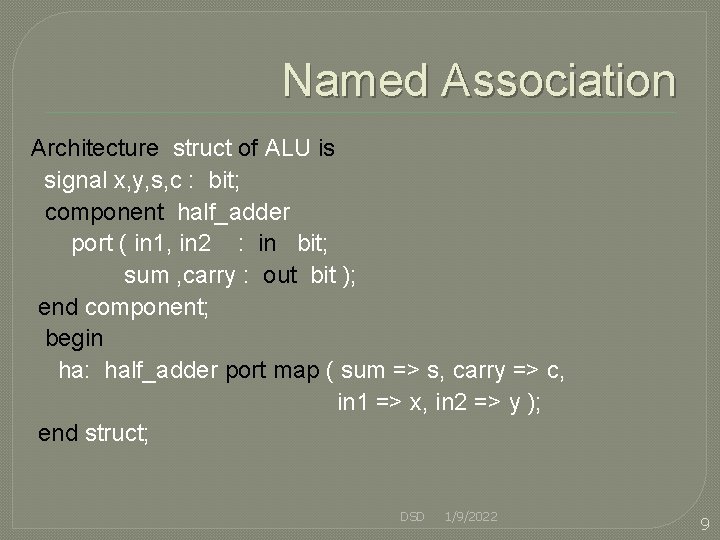

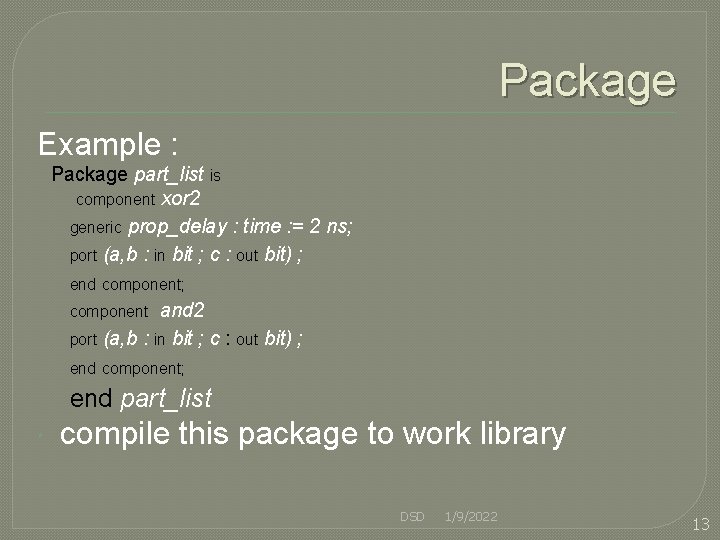

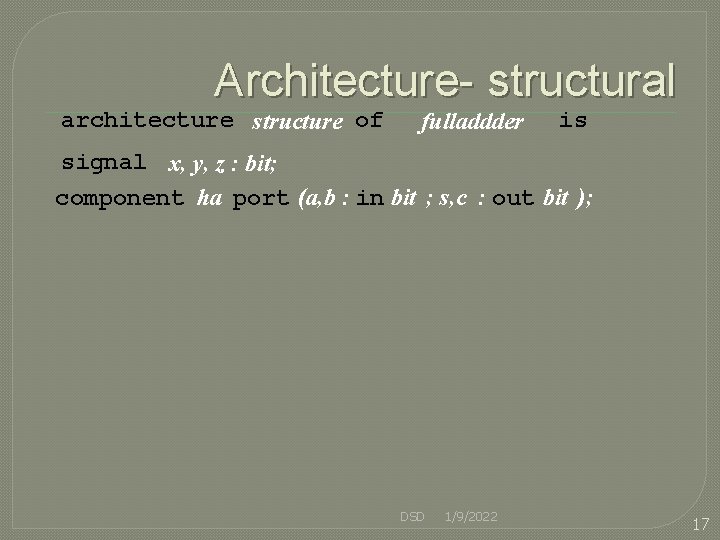

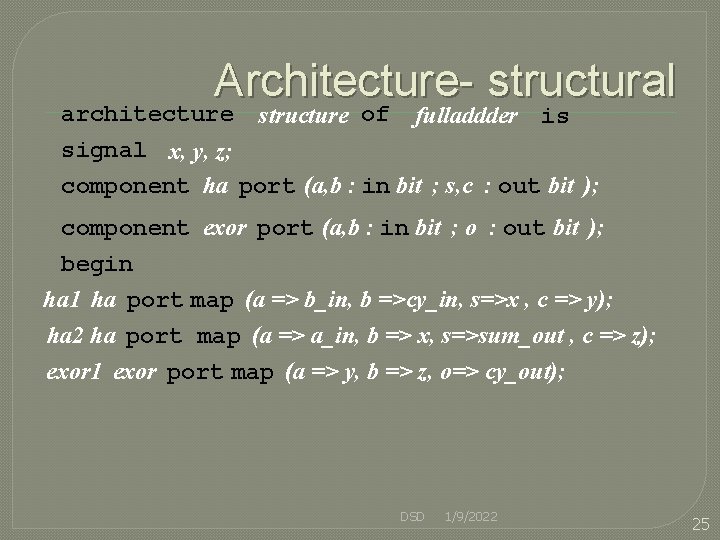

Component instantiation The syntax is Component-label : component_name [port map (association-list)]; � The port map connects each port of this instance of component_name to a single valued expression in the current entity. � The value of the expression can be a single name, an indexed name, a slice name , or an aggregate. � The port is left unconnected if the expression is VHDL reserved word ‘open’. � Ports can be mapped to signals by named or positional association. � DSD 1/9/2022 5

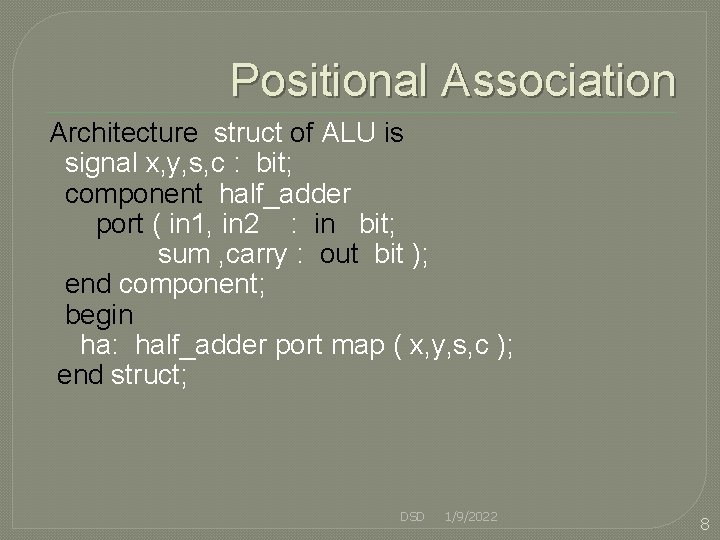

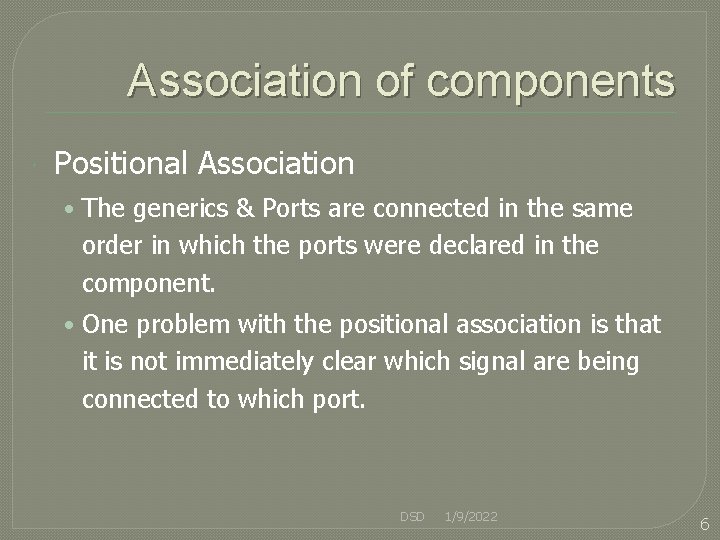

Association of components Positional Association • The generics & Ports are connected in the same order in which the ports were declared in the component. • One problem with the positional association is that it is not immediately clear which signal are being connected to which port. DSD 1/9/2022 6

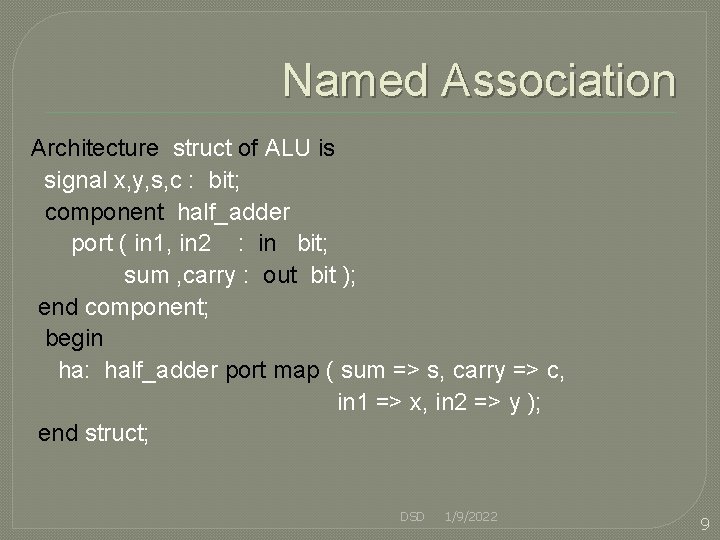

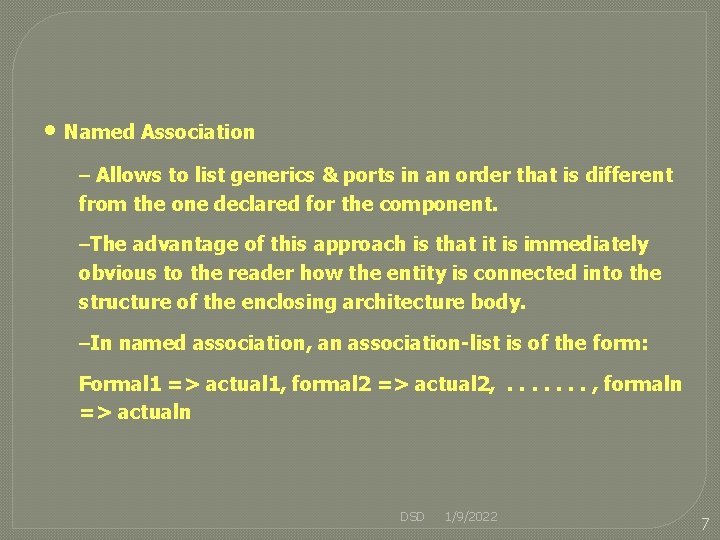

• Named Association – Allows to list generics & ports in an order that is different from the one declared for the component. –The advantage of this approach is that it is immediately obvious to the reader how the entity is connected into the structure of the enclosing architecture body. –In named association, an association-list is of the form: Formal 1 => actual 1, formal 2 => actual 2, . . . . , formaln => actualn DSD 1/9/2022 7

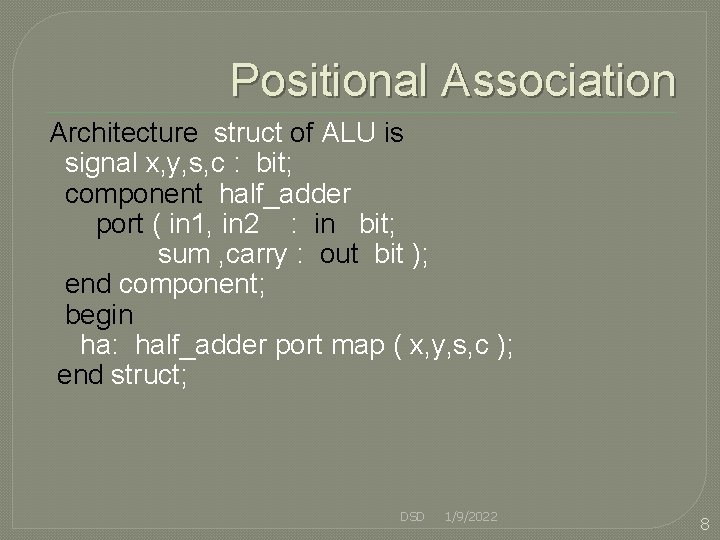

Positional Association Architecture struct of ALU is signal x, y, s, c : bit; component half_adder port ( in 1, in 2 : in bit; sum , carry : out bit ); end component; begin ha: half_adder port map ( x, y, s, c ); end struct; DSD 1/9/2022 8

Named Association Architecture struct of ALU is signal x, y, s, c : bit; component half_adder port ( in 1, in 2 : in bit; sum , carry : out bit ); end component; begin ha: half_adder port map ( sum => s, carry => c, in 1 => x, in 2 => y ); end struct; DSD 1/9/2022 9

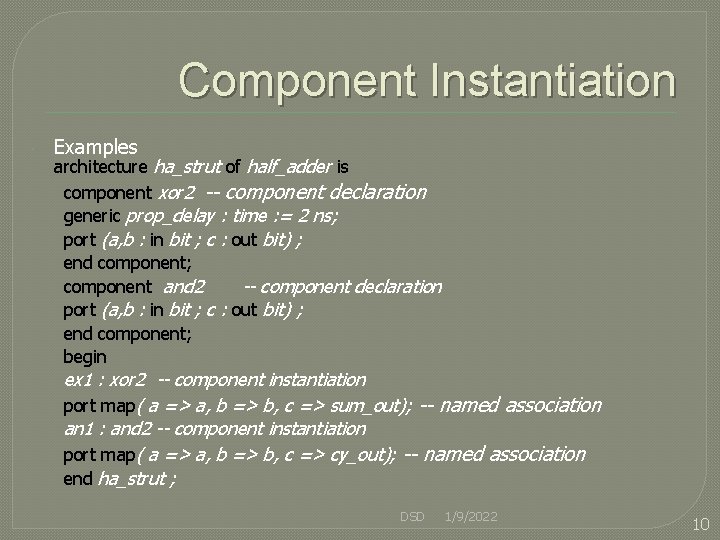

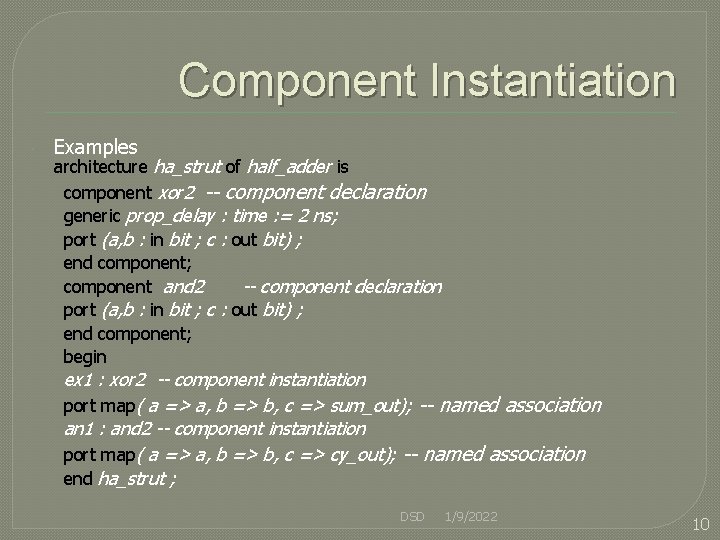

Component Instantiation Examples architecture ha_strut of half_adder is component xor 2 -- component declaration generic prop_delay : time : = 2 ns; port (a, b : in bit ; c : out bit) ; end component; component and 2 -- component declaration port (a, b : in bit ; c : out bit) ; end component; begin ex 1 : xor 2 -- component instantiation port map( a => a, b => b, c => sum_out); -- named association an 1 : and 2 -- component instantiation port map( a => a, b => b, c => cy_out); -- named association end ha_strut ; DSD 1/9/2022 10

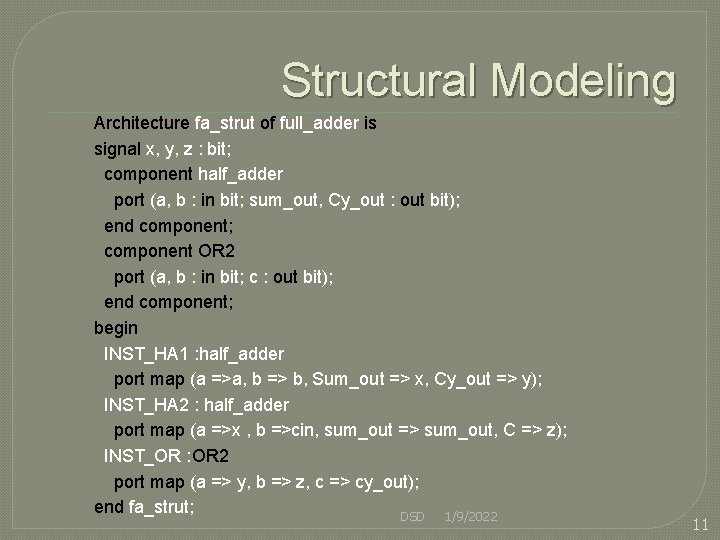

Structural Modeling Architecture fa_strut of full_adder is signal x, y, z : bit; component half_adder port (a, b : in bit; sum_out, Cy_out : out bit); end component; component OR 2 port (a, b : in bit; c : out bit); end component; begin INST_HA 1 : half_adder port map (a =>a, b => b, Sum_out => x, Cy_out => y); INST_HA 2 : half_adder port map (a =>x , b =>cin, sum_out => sum_out, C => z); INST_OR : OR 2 port map (a => y, b => z, c => cy_out); end fa_strut; DSD 1/9/2022 11

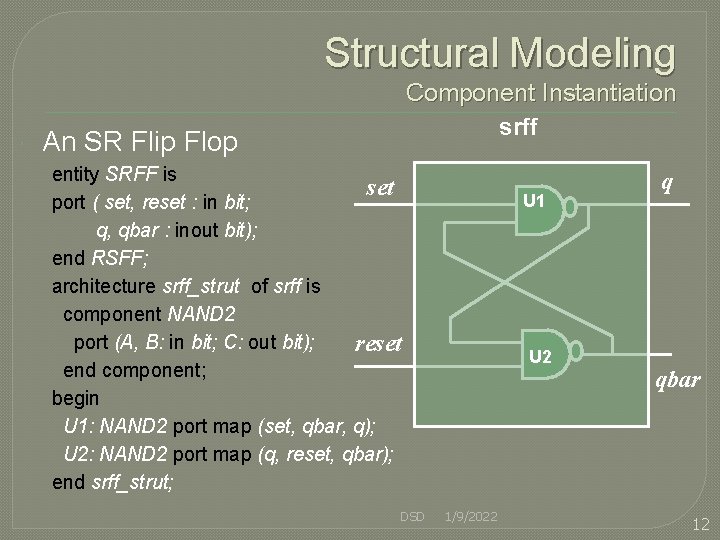

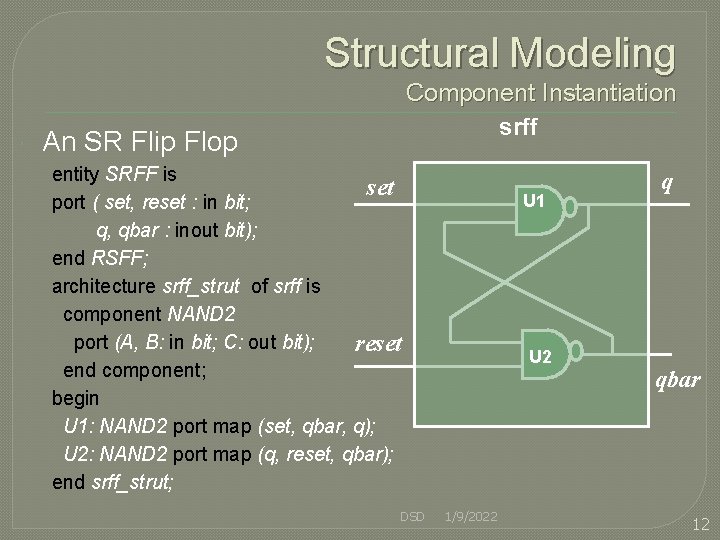

Structural Modeling Component Instantiation srff An SR Flip Flop entity SRFF is set port ( set, reset : in bit; q, qbar : inout bit); end RSFF; architecture srff_strut of srff is component NAND 2 port (A, B: in bit; C: out bit); reset end component; begin U 1: NAND 2 port map (set, qbar, q); U 2: NAND 2 port map (q, reset, qbar); end srff_strut; DSD U 1 U 2 1/9/2022 q qbar 12

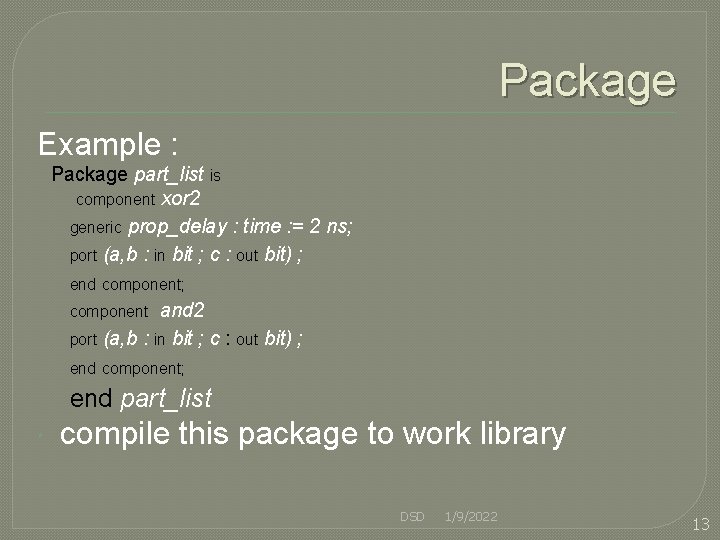

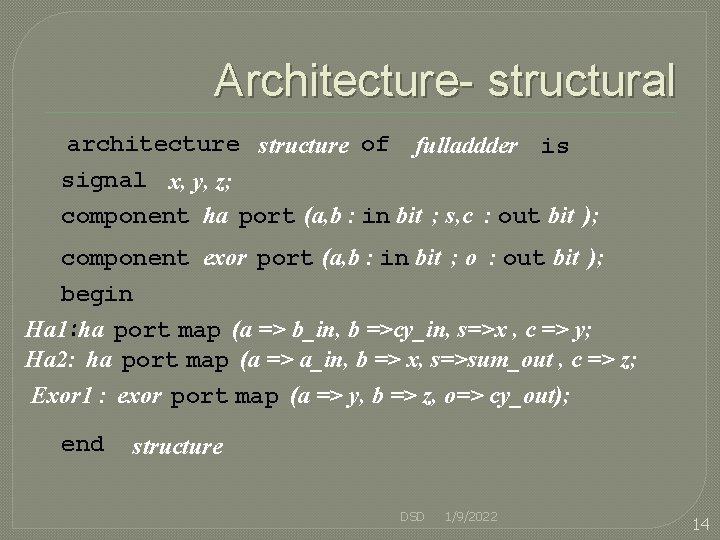

Package Example : Package part_list is component xor 2 generic prop_delay : time : = 2 ns; port (a, b : in bit ; c : out bit) ; end component; and 2 port (a, b : in bit ; c : out bit) ; component end component; end part_list compile this package to work library DSD 1/9/2022 13

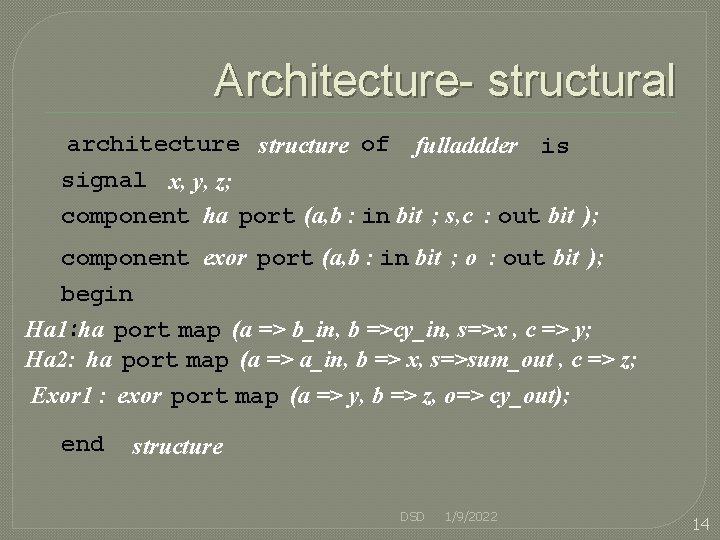

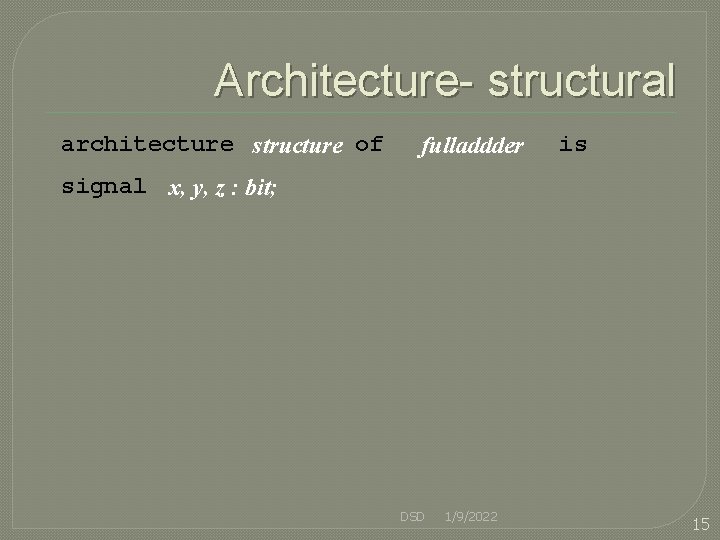

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); begin Ha 1: ha port map (a => b_in, b =>cy_in, s=>x , c => y; Ha 2: ha port map (a => a_in, b => x, s=>sum_out , c => z; Exor 1 : exor port map (a => y, b => z, o=> cy_out); end structure DSD 1/9/2022 14

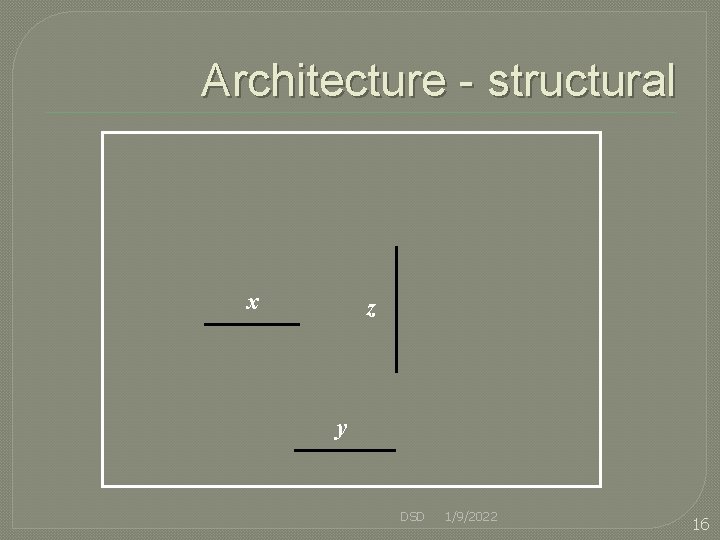

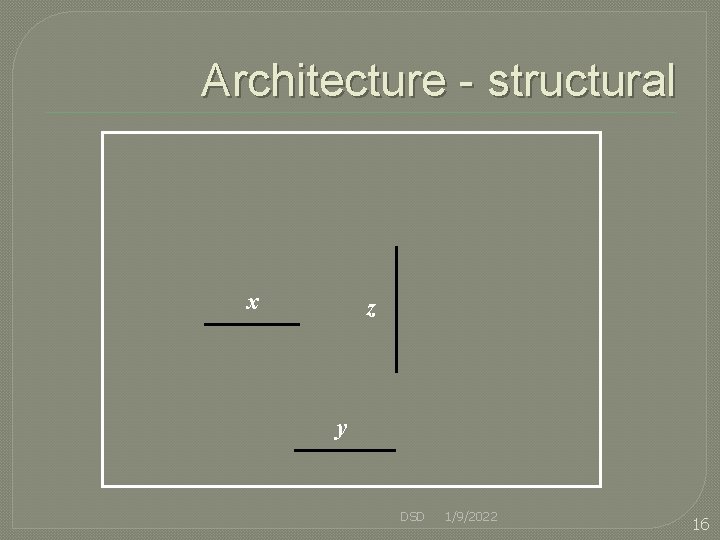

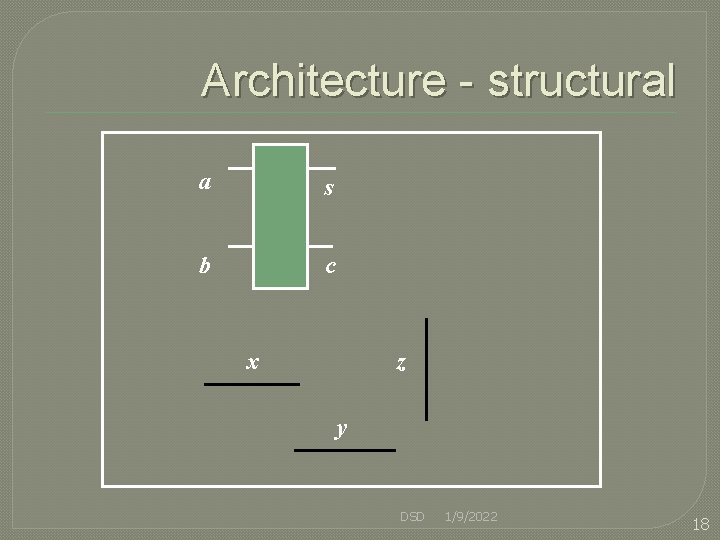

Architecture- structural architecture structure of fulladdder is signal x, y, z : bit; DSD 1/9/2022 15

Architecture - structural x z y DSD 1/9/2022 16

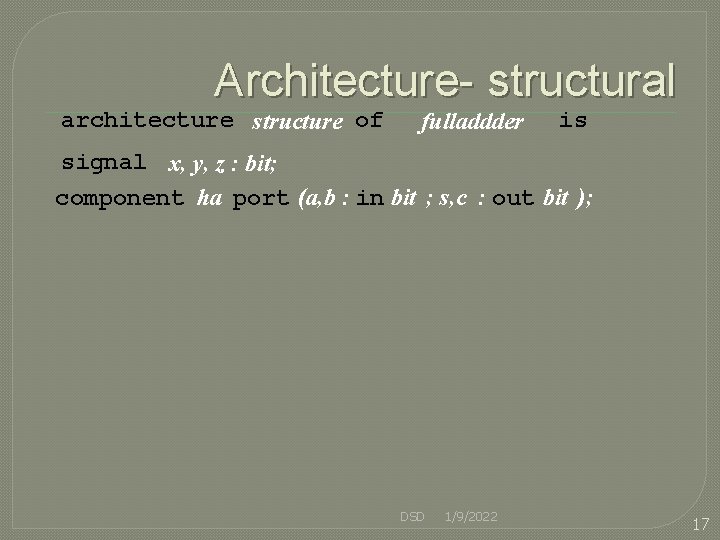

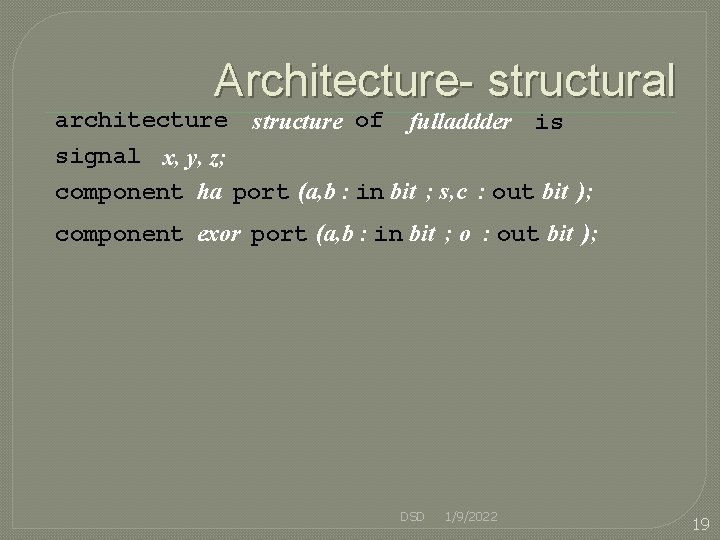

Architecture- structural architecture structure of fulladdder is signal x, y, z : bit; component ha port (a, b : in bit ; s, c : out bit ); DSD 1/9/2022 17

Architecture - structural a s b c x z y DSD 1/9/2022 18

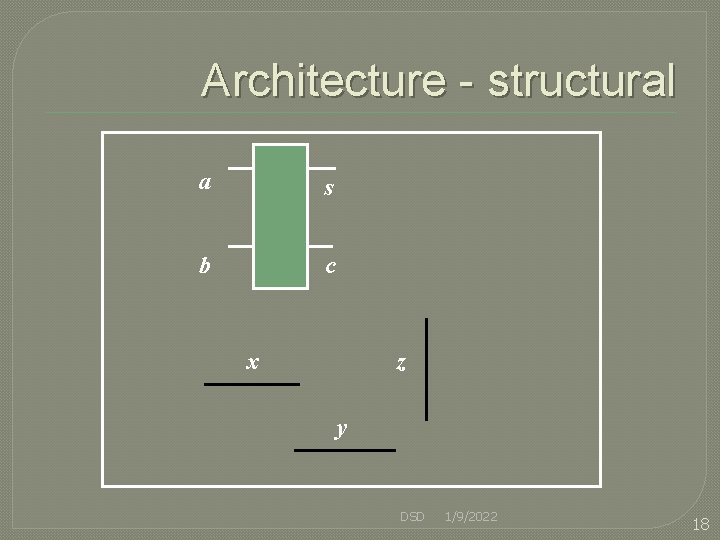

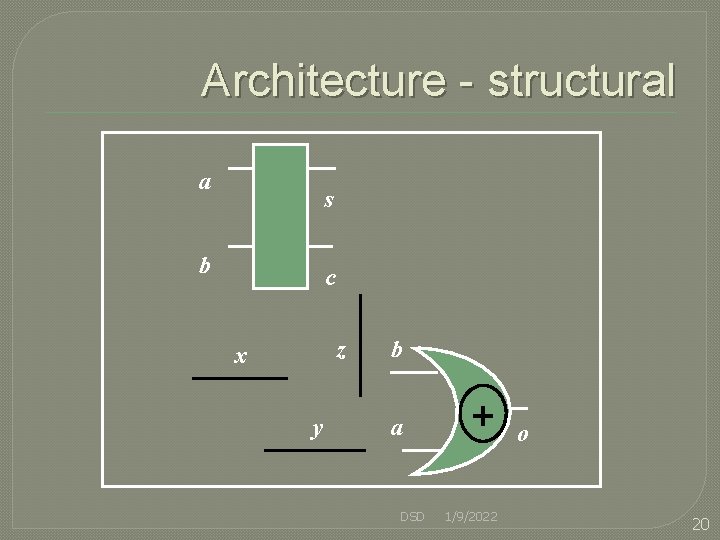

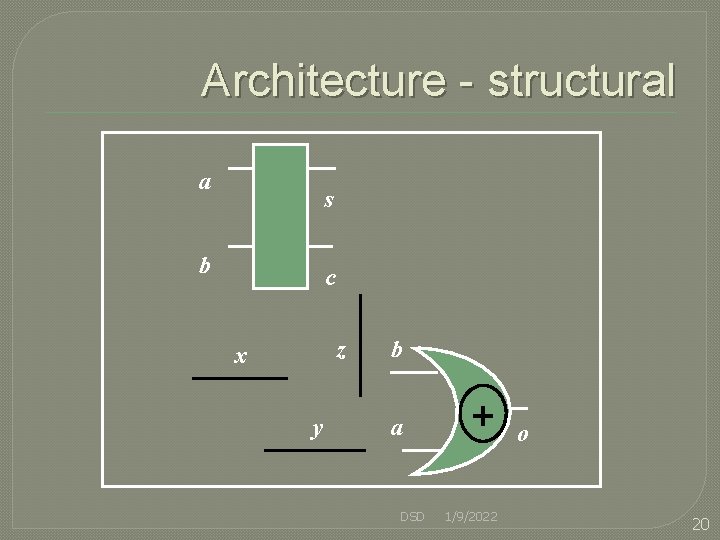

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); DSD 1/9/2022 19

Architecture - structural a s b c z x y b a DSD + 1/9/2022 o 20

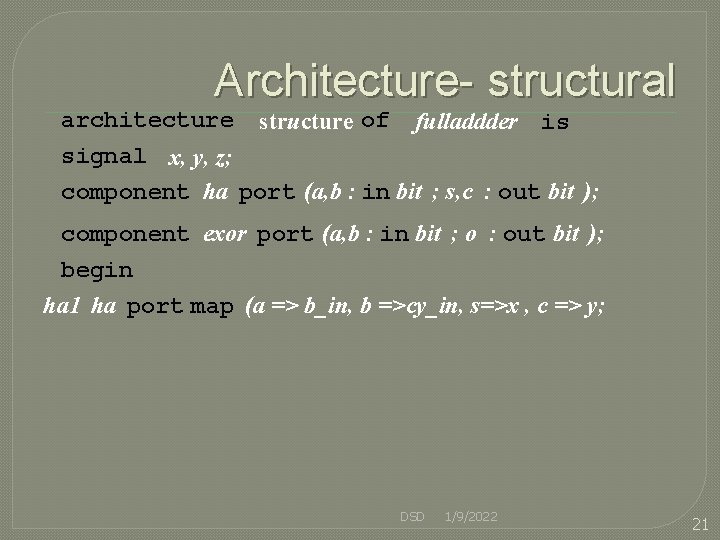

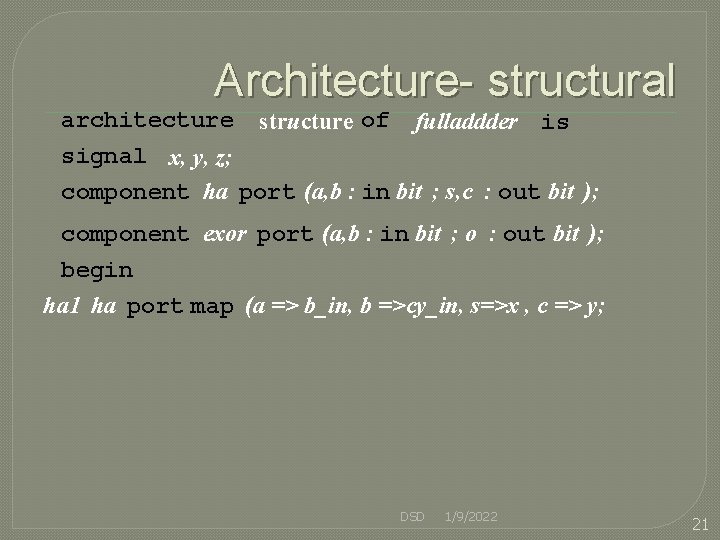

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); begin ha 1 ha port map (a => b_in, b =>cy_in, s=>x , c => y; DSD 1/9/2022 21

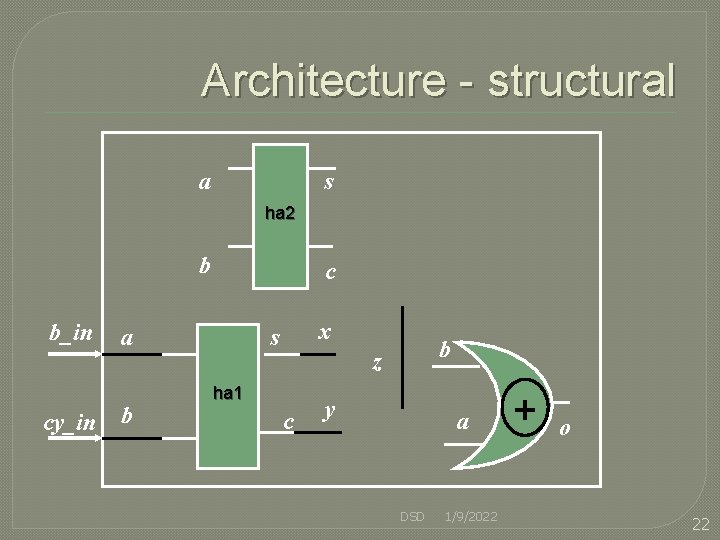

Architecture - structural a s ha 2 b b_in cy_in c a b x s b z ha 1 c y a DSD 1/9/2022 + o 22

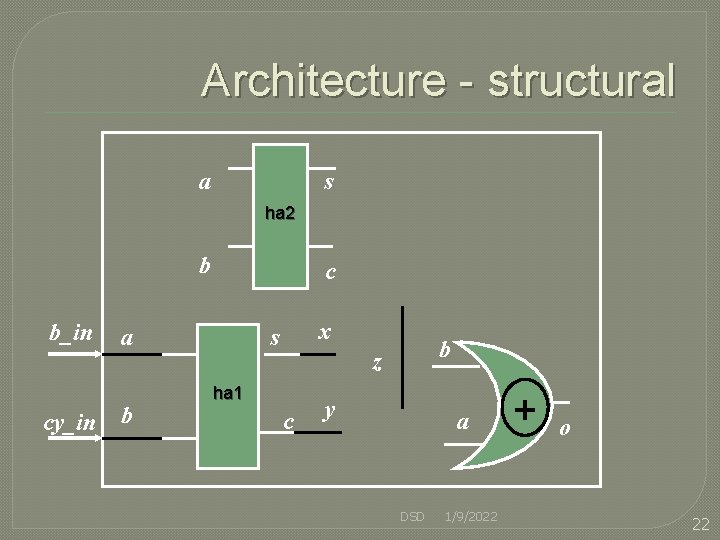

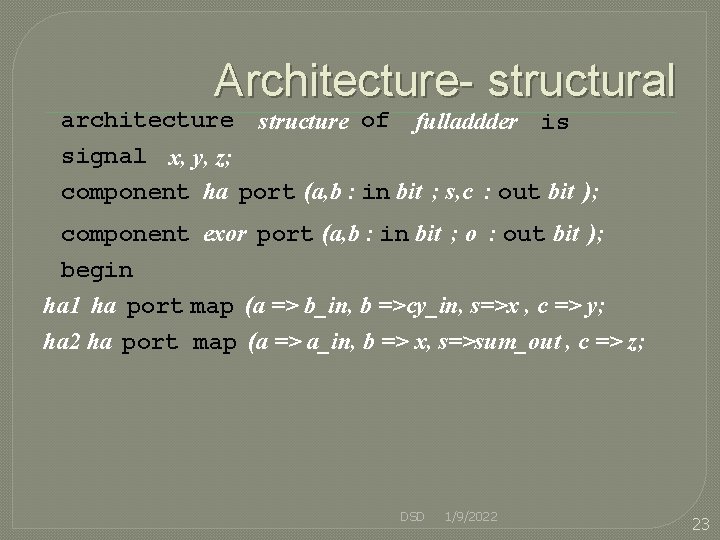

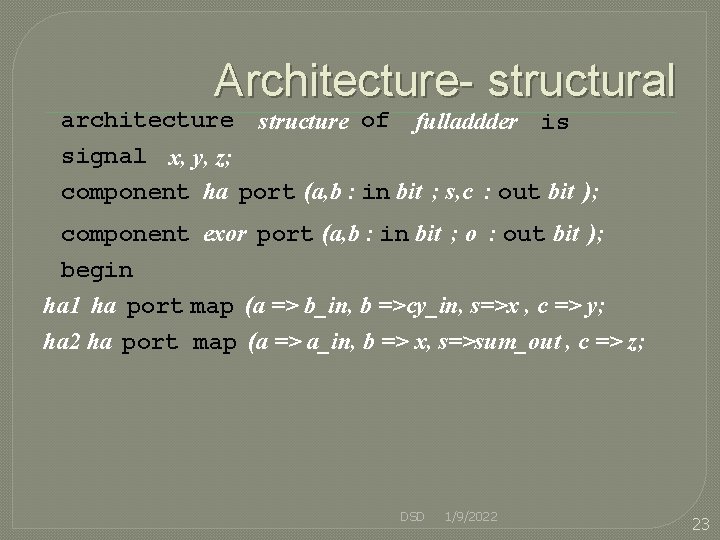

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); begin ha 1 ha port map (a => b_in, b =>cy_in, s=>x , c => y; ha 2 ha port map (a => a_in, b => x, s=>sum_out , c => z; DSD 1/9/2022 23

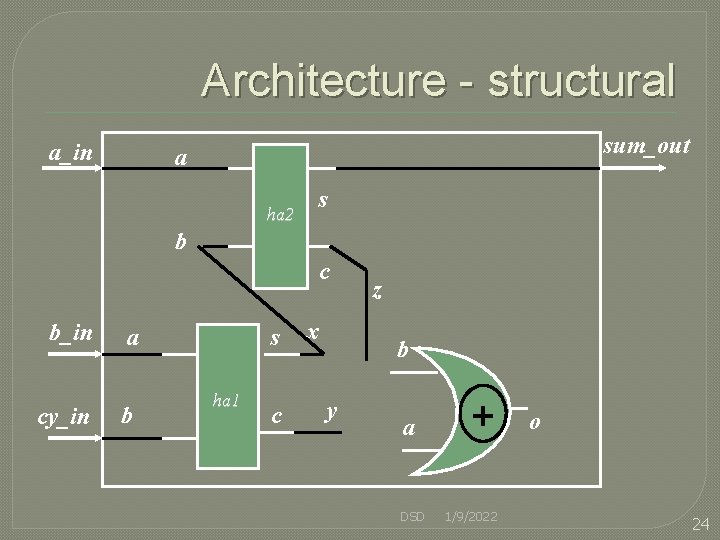

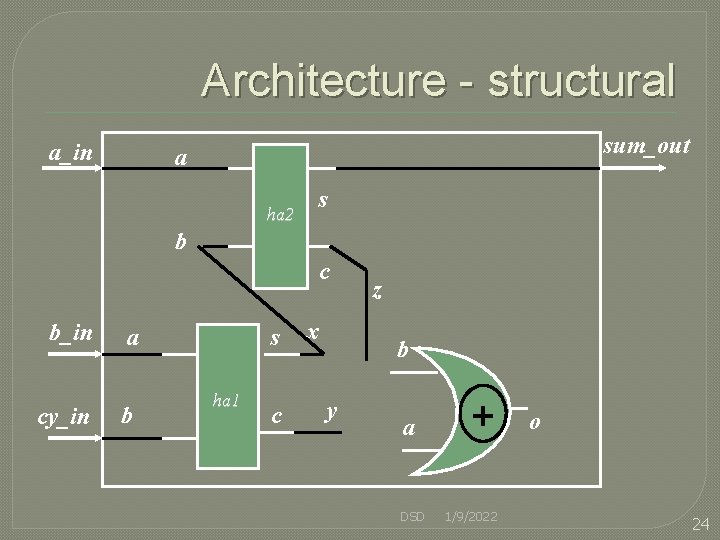

Architecture - structural a_in sum_out a s ha 2 b c b_in cy_in a b s ha 1 c x z b y a DSD + 1/9/2022 o 24

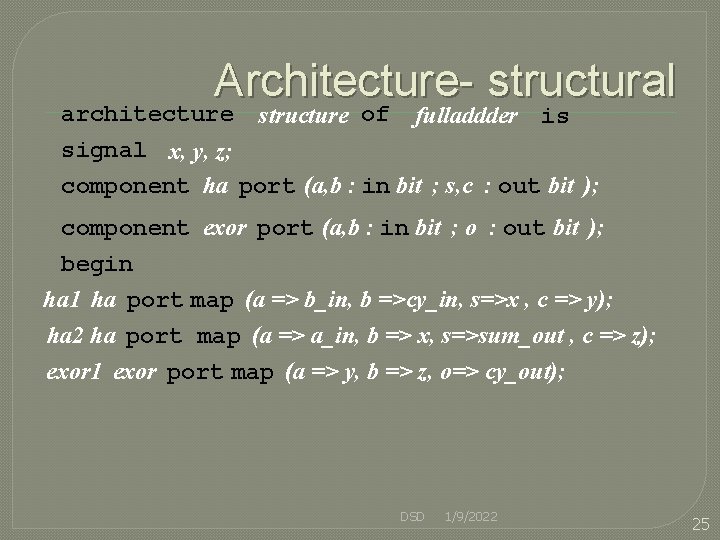

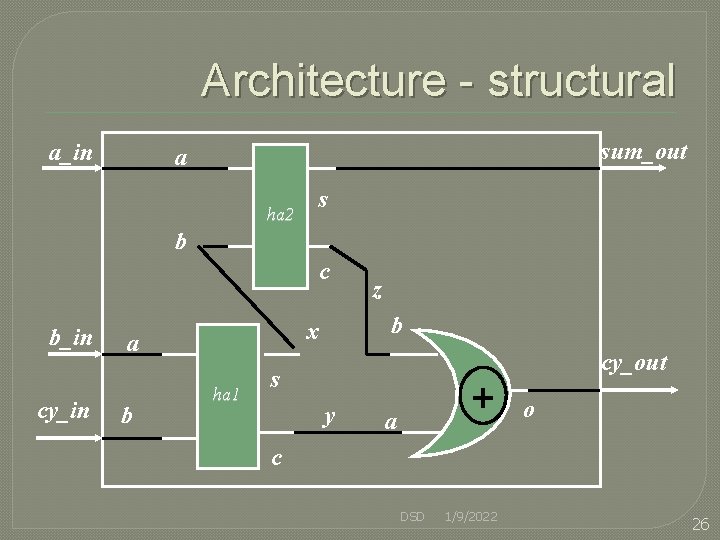

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); begin ha 1 ha port map (a => b_in, b =>cy_in, s=>x , c => y); ha 2 ha port map (a => a_in, b => x, s=>sum_out , c => z); exor 1 exor port map (a => y, b => z, o=> cy_out); DSD 1/9/2022 25

Architecture - structural a_in sum_out a s ha 2 b c b_in cy_in b b x a ha 1 z cy_out s y + a o c DSD 1/9/2022 26

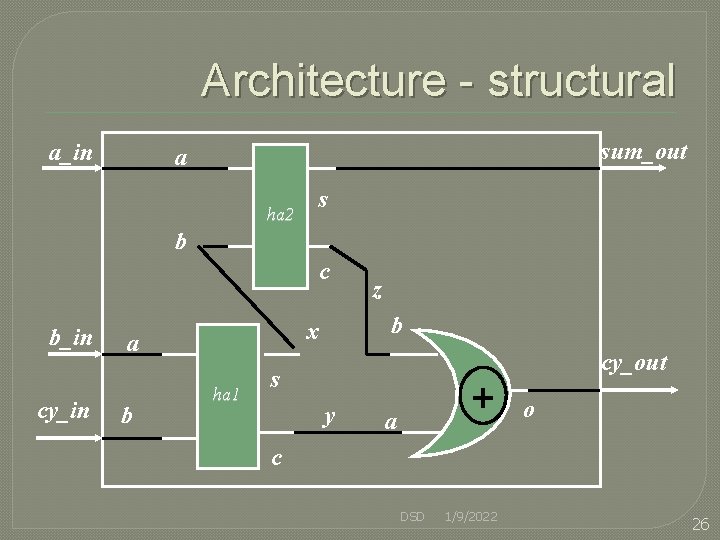

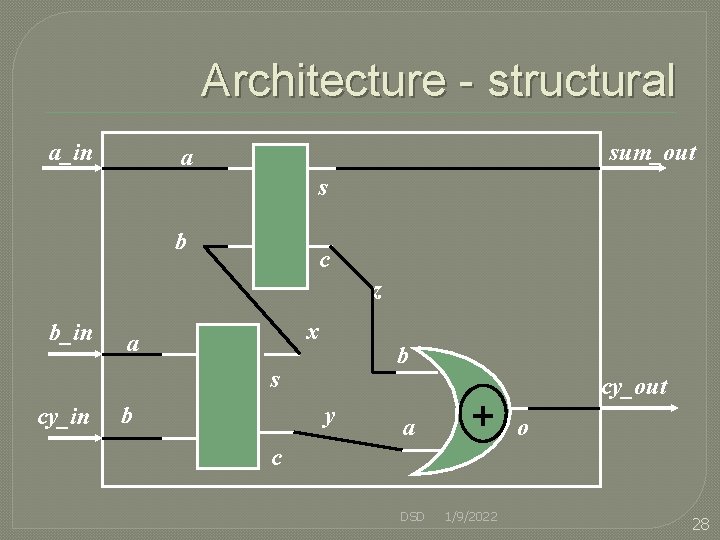

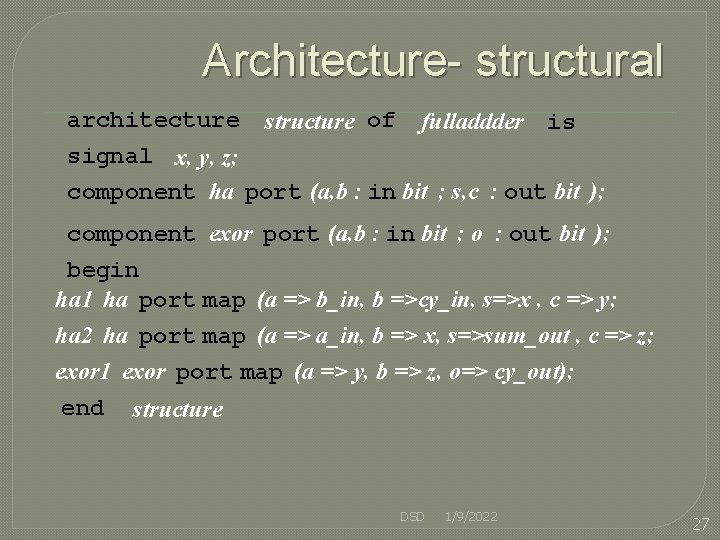

Architecture- structural architecture structure of fulladdder is signal x, y, z; component ha port (a, b : in bit ; s, c : out bit ); component exor port (a, b : in bit ; o : out bit ); begin ha 1 ha port map (a => b_in, b =>cy_in, s=>x , c => y; ha 2 ha port map (a => a_in, b => x, s=>sum_out , c => z; exor 1 exor port map (a => y, b => z, o=> cy_out); end structure DSD 1/9/2022 27

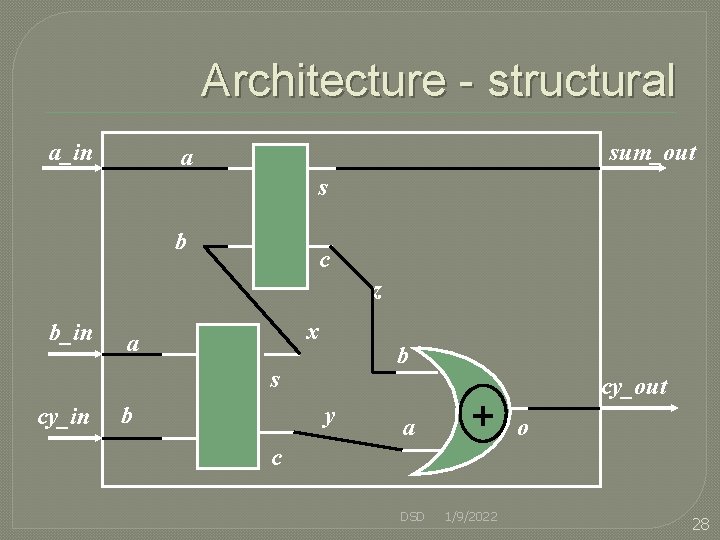

Architecture - structural a_in sum_out a s b c z b_in x a b s cy_in b y a + cy_out o c DSD 1/9/2022 28