Structura procesoarelor din familia INTEL Structura procesorului 286

- Slides: 23

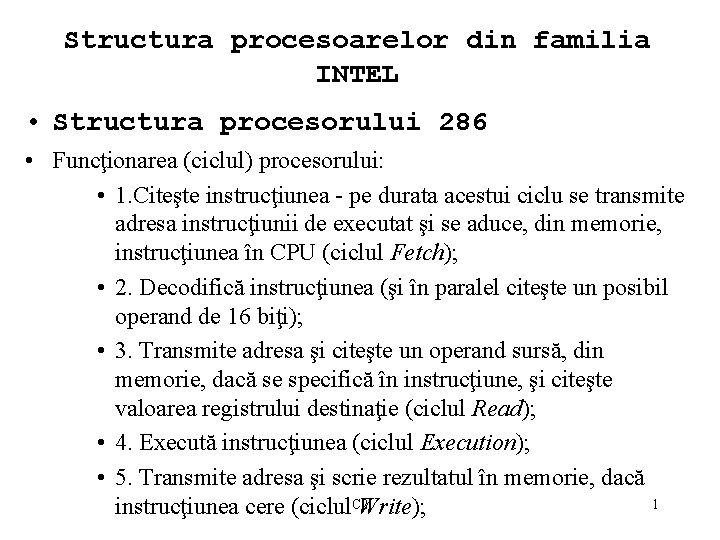

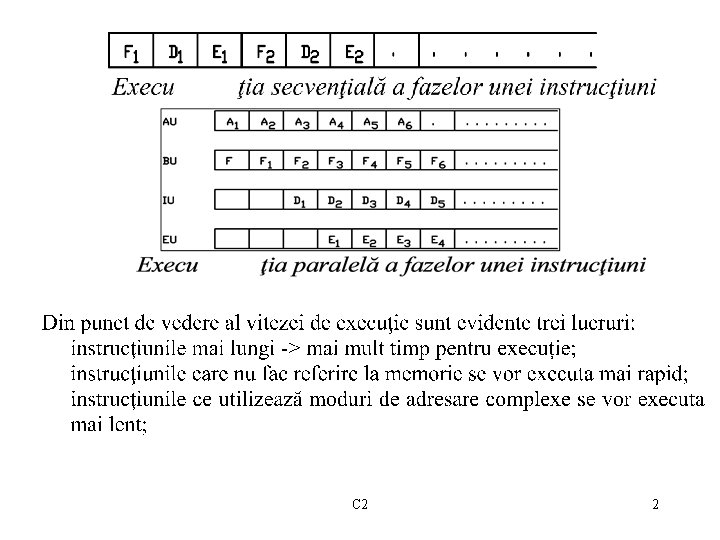

Structura procesoarelor din familia INTEL • Structura procesorului 286 • Funcţionarea (ciclul) procesorului: • 1. Citeşte instrucţiunea - pe durata acestui ciclu se transmite adresa instrucţiunii de executat şi se aduce, din memorie, instrucţiunea în CPU (ciclul Fetch); • 2. Decodifică instrucţiunea (şi în paralel citeşte un posibil operand de 16 biţi); • 3. Transmite adresa şi citeşte un operand sursă, din memorie, dacă se specifică în instrucţiune, şi citeşte valoarea registrului destinaţie (ciclul Read); • 4. Execută instrucţiunea (ciclul Execution); • 5. Transmite adresa şi scrie rezultatul în memorie, dacă 1 instrucţiunea cere (ciclul. C 2 Write);

C 2 2

C 2 3

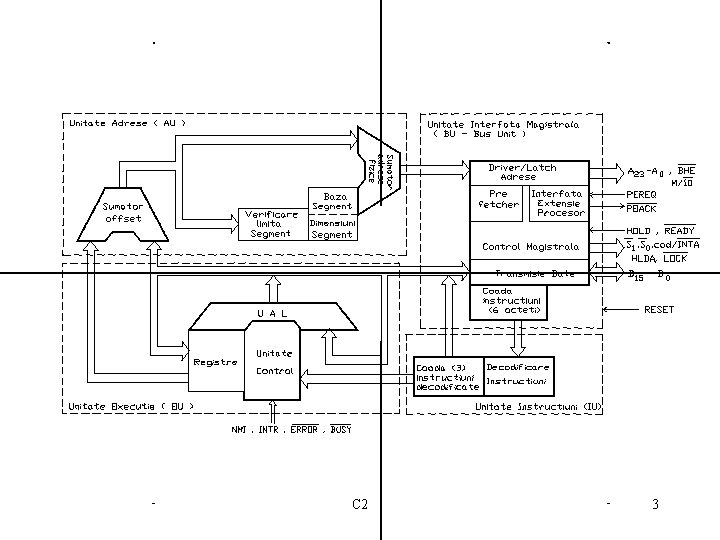

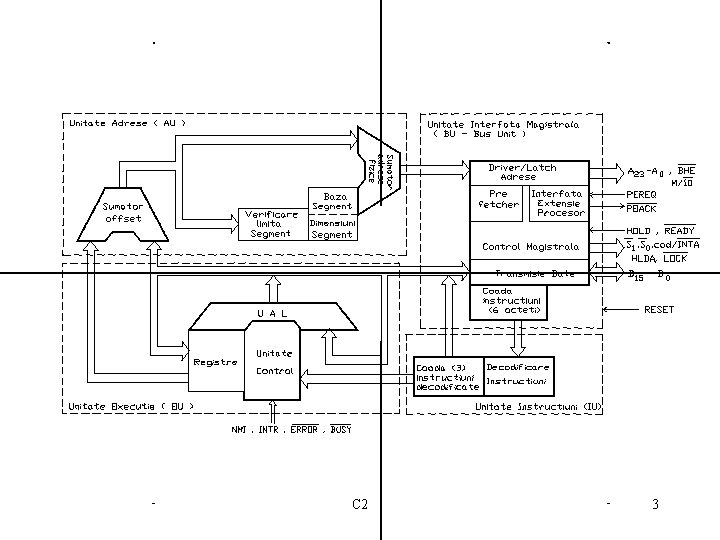

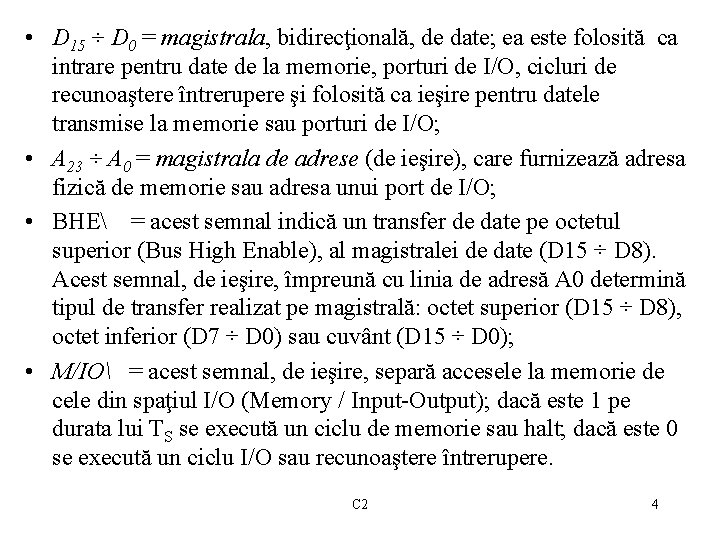

• D 15 ÷ D 0 = magistrala, bidirecţională, de date; ea este folosită ca intrare pentru date de la memorie, porturi de I/O, cicluri de recunoaştere întrerupere şi folosită ca ieşire pentru datele transmise la memorie sau porturi de I/O; • A 23 ÷ A 0 = magistrala de adrese (de ieşire), care furnizează adresa fizică de memorie sau adresa unui port de I/O; • BHE = acest semnal indică un transfer de date pe octetul superior (Bus High Enable), al magistralei de date (D 15 ÷ D 8). Acest semnal, de ieşire, împreună cu linia de adresă A 0 determină tipul de transfer realizat pe magistrală: octet superior (D 15 ÷ D 8), octet inferior (D 7 ÷ D 0) sau cuvânt (D 15 ÷ D 0); • M/IO = acest semnal, de ieşire, separă accesele la memorie de cele din spaţiul I/O (Memory / Input-Output); dacă este 1 pe durata lui TS se execută un ciclu de memorie sau halt; dacă este 0 se execută un ciclu I/O sau recunoaştere întrerupere. C 2 4

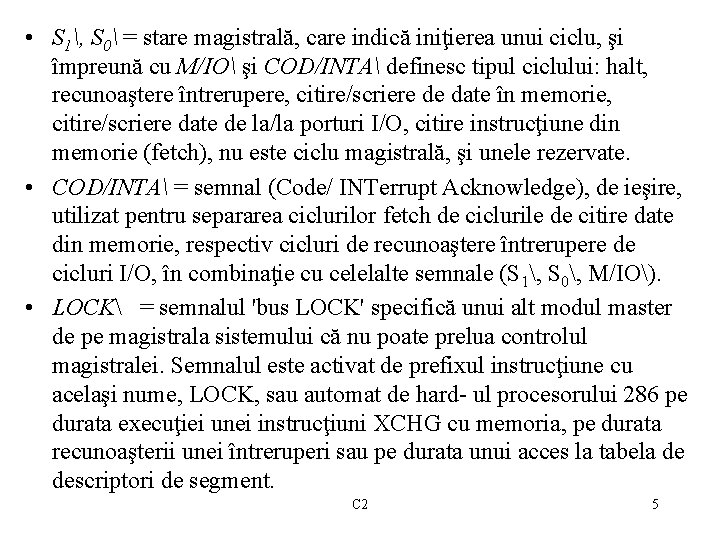

• S 1, S 0 = stare magistrală, care indică iniţierea unui ciclu, şi împreună cu M/IO şi COD/INTA definesc tipul ciclului: halt, recunoaştere întrerupere, citire/scriere de date în memorie, citire/scriere date de la/la porturi I/O, citire instrucţiune din memorie (fetch), nu este ciclu magistrală, şi unele rezervate. • COD/INTA = semnal (Code/ INTerrupt Acknowledge), de ieşire, utilizat pentru separarea ciclurilor fetch de ciclurile de citire date din memorie, respectiv cicluri de recunoaştere întrerupere de cicluri I/O, în combinaţie cu celelalte semnale (S 1, S 0, M/IO). • LOCK = semnalul 'bus LOCK' specifică unui alt modul master de pe magistrala sistemului că nu poate prelua controlul magistralei. Semnalul este activat de prefixul instrucţiune cu acelaşi nume, LOCK, sau automat de hard- ul procesorului 286 pe durata execuţiei unei instrucţiuni XCHG cu memoria, pe durata recunoaşterii unei întreruperi sau pe durata unui acces la tabela de descriptori de segment. C 2 5

• READY = semnalul de intrare 'bus READY' termină un ciclu de magistrală; ciclurile de magistrală sunt extinse fără limită până când semnalul READY devine activ (LOW). • HOLD, HLDA = cele două semnale 'bus HOLD request' şi 'bus HOLD Acknowledge', primul de intrare, iar cel de-al doilea de ieşire permit controlul magistralei; semnalul HOLD permite unui alt modul master (procesor) să ceară controlul asupra magistralei locale; când controlul este recunoscut (cedat), procesorul 286 trece magistrala sa (date, adrese, stări) în starea de mare impedanţă, şi activează semnalul de răspuns HLDA, intrând în starea 'hold' (magistrala suspendată). Magistrala este preluată de celalalt master (procesor) până când semnalul HOLD devine inactiv (LOW), iar procesorul 286 dezactivează linia HLDA, recâştigând controlul asupra magistralei locale. C 2 6

• INTR = activarea acestui semnal, de intrare, (HIGH) va cere procesorului 286 să-şi suspende execuţia programului curent şi să servească o cerere externă ('INTerrupt Request'). Întreruperile pot fi mascate (anulate), când IF = 0. Când 286 răspunde la o cerere de întrerupere, el realizează 2 cicluri magistrală de recunoaştere întrerupere, pentru a citi un vector de întrerupere, de 8 biţi, care identifică sursa întreruperii. Pentru a asigura întreruperea programului, INTR trebuie să rămână activ până este completat primul ciclu de recunoaştere întrerupere, pe durata căruia se transmite semnalul de recunoaştere a întreruperii INTA. • NMI = semnalul de intrare 'Non Maskable Interrupt', activ (HIGH), reprezintă tot o cerere de întrerupere externă, dar nemascabilă, deci nu are nici o semnificaţie starea indicatorului IF pentru acest semnal. Pentru această întrerupere nu se realizează cicluri de recunoaştere întrerupere, şi se generează un vector de întrerupere intern, cu valoarea 2. C 2 7

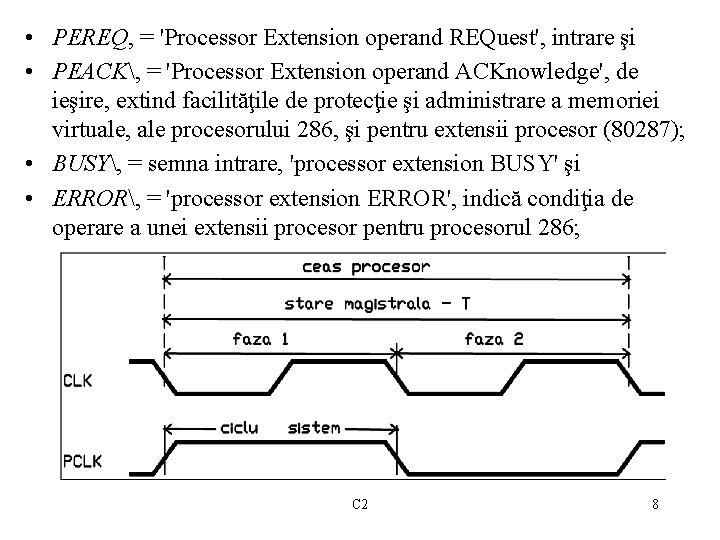

• PEREQ, = 'Processor Extension operand REQuest', intrare şi • PEACK, = 'Processor Extension operand ACKnowledge', de ieşire, extind facilităţile de protecţie şi administrare a memoriei virtuale, ale procesorului 286, şi pentru extensii procesor (80287); • BUSY, = semna intrare, 'processor extension BUSY' şi • ERROR, = 'processor extension ERROR', indică condiţia de operare a unei extensii procesor pentru procesorul 286; C 2 8

C 2 9

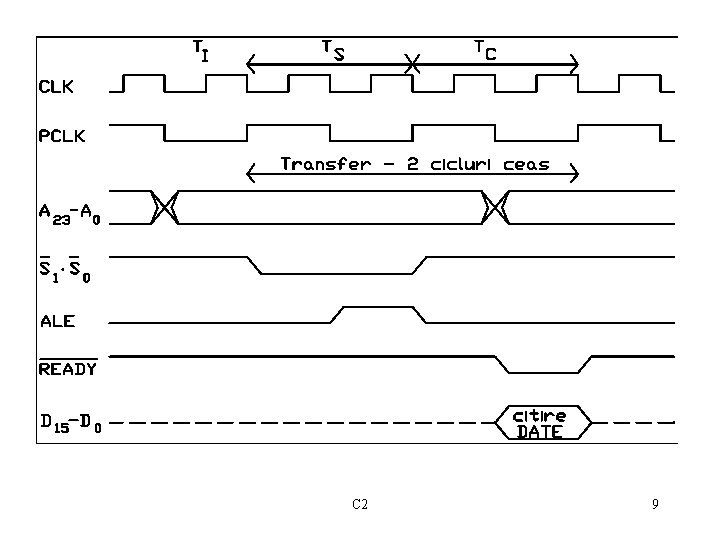

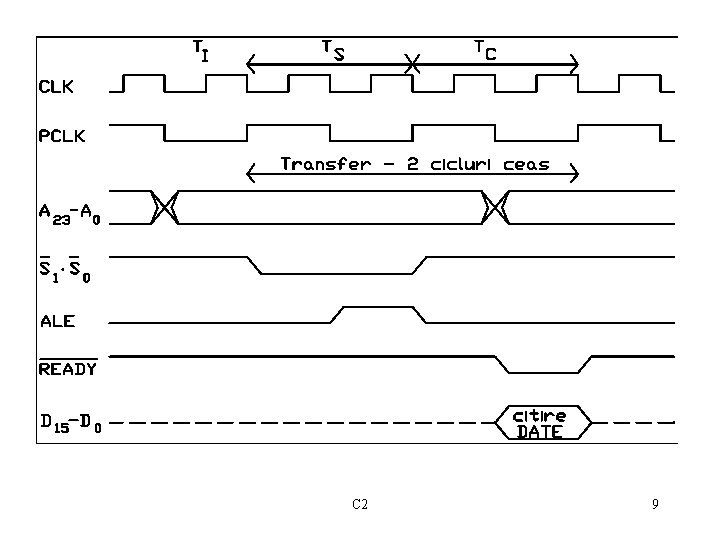

• Pe durata unui ciclu de magistrală se realizează operaţiile: · se activează pe magistrala de adrese, adresa unei locaţii de memorie, sau a unui port I/O, şi se memorează într-un registru de adrese, extern; · se generează semnalul de comandă corespunzător, pentru citire/scriere date; · dispozitivul selectat (memoria sau portul I/O) realizează transferul de date, şi transmite procesorului un semnal de răspuns, pentru a încheia ciclul. • Controllerul de magistrală (82288) decodifică semnalele de stare (S 1, S 0, M/IO, COD/INTA şi READY) pentru a genera comenzi de citire /scriere (MRDC, MWTC, IORC, IOWC) şi semnale pentru comanda latch-urilor de adrese şi transmisie/recepţie date (ALE, DEN, DT/R). C 2 10

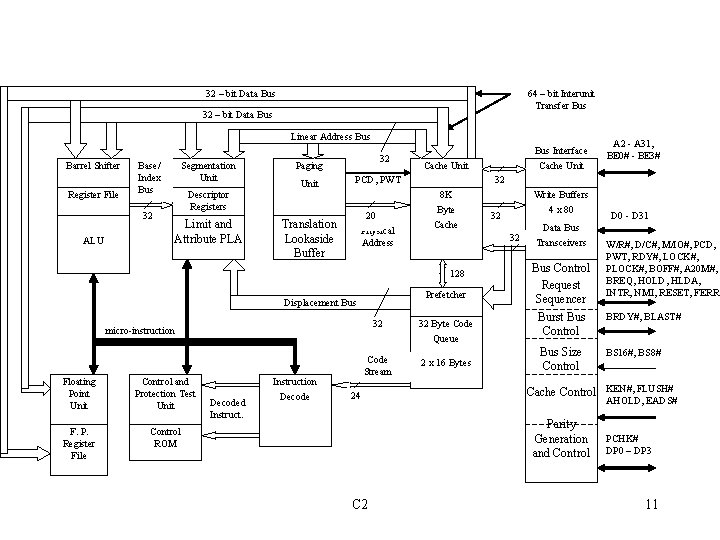

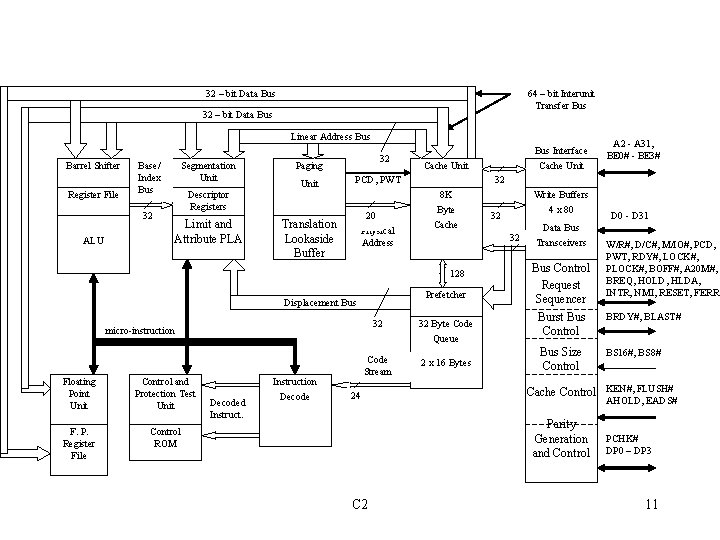

64 – bit Interunit Transfer Bus 32 – bit Data Bus Linear Address Bus Barrel Shifter Register File 32 ALU Segmentation Unit Base/ Index Bus Descriptor Registers Limit and Attribute PLA 32 Paging Unit Cache Unit PCD, PWT 20 Physical Address Translation Lookaside Buffer 8 K Byte Cache Floating Point Unit Control and Protection Test Unit F. P. Register File Control ROM Decoded Instruction Decode 32 32 Byte Code Queue Code Stream 2 x 16 Bytes 24 Write Buffers 4 x 80 32 32 Prefetcher micro-instruction Data Bus Transceivers Bus Control Request Sequencer Burst Bus Control Bus Size Control D 0 - D 31 W/R#, D/C#, M/IO#, PCD, PWT, RDY#, LOCK#, PLOCK#, BOFF#, A 20 M#, BREQ, HOLD, HLDA, INTR, NMI, RESET, FERR BRDY#, BLAST# BS 16#, BS 8# Cache Control KEN#, FLUSH# AHOLD, EADS# Parity Generation and Control C 2 A 2 - A 31, BE 0# - BE 3# 32 128 Displacement Bus Interface Cache Unit PCHK# DP 0 – DP 3 11

C 2 12

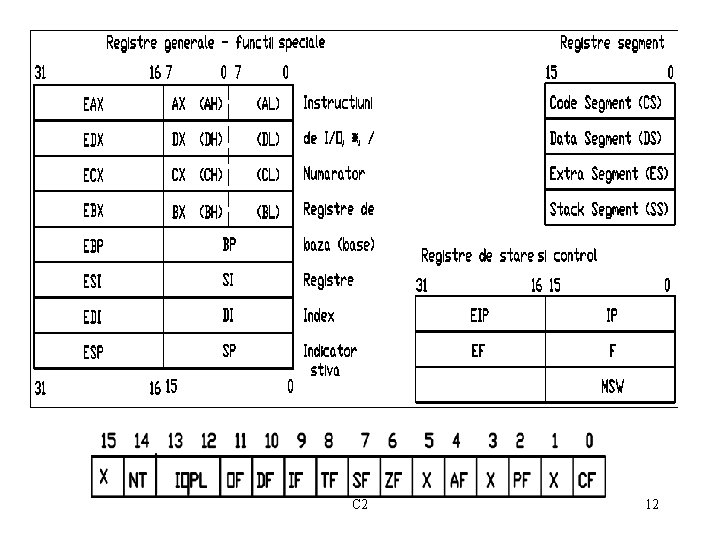

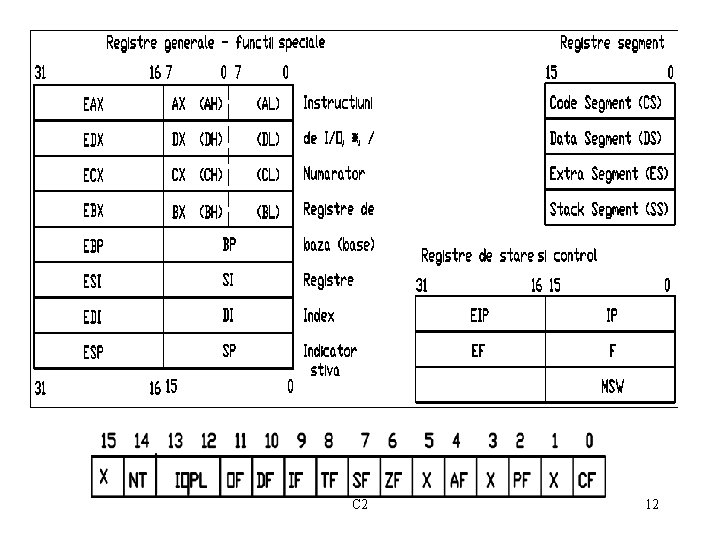

• La procesorul 386/486 acest registru (EFLAGS) are 32 biţi, dintre care ultimii 16 sunt identici cu aceştia, dar în plus mai sunt utilizaţi încă doi biţi (16 şi 17) care au următoarea semnificaţie: • RF (Resume Flag) - acest indicator dezactivează, temporar, excepţiile de depanare (debug), astfel încât să se poată restarta o instrucţiune după o excepţie de depanare, fără a se genera, imediat, o altă excepţie de depanare; adică nu se execută o instrucţiune de breakpoint, dacă este returnat controlul de excepţia de depanare direct la o astfel de instrucţiune. • VM (Virtual 8086 Mode) - acest bit indică că se execută un program 8086, dacă este poziţionat pe 1. Bitul VM furnizează modul V 86, in modul protejat de operare C 2 13

C 2 14

C 2 15

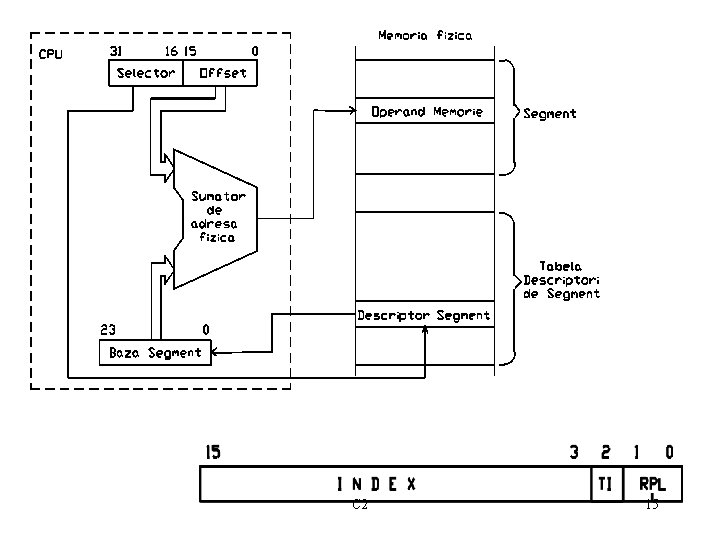

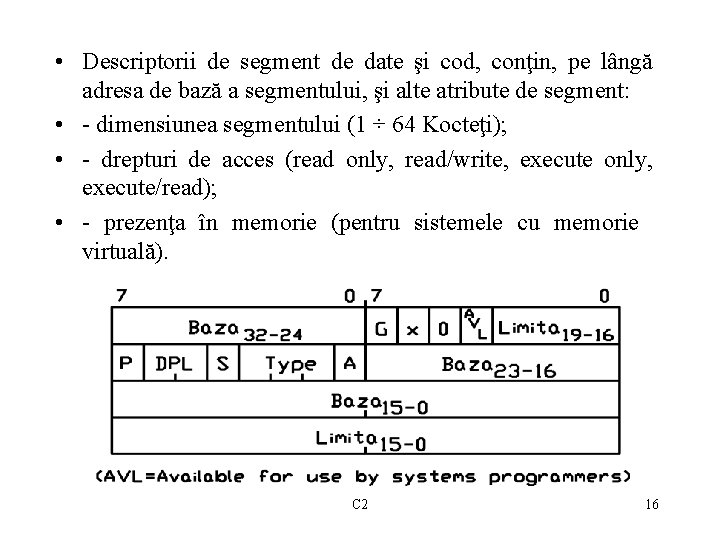

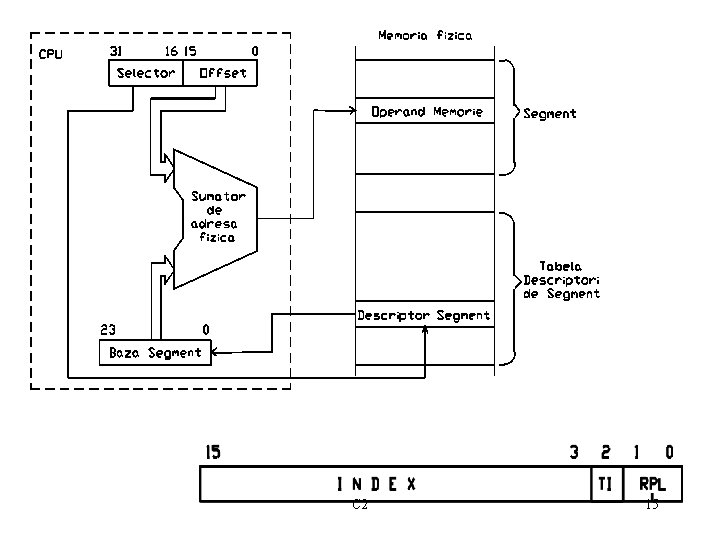

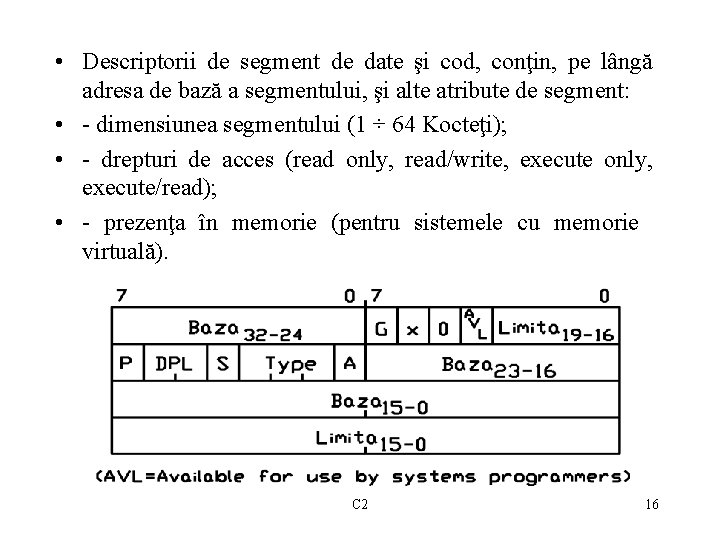

• Descriptorii de segment de date şi cod, conţin, pe lângă adresa de bază a segmentului, şi alte atribute de segment: • - dimensiunea segmentului (1 ÷ 64 Kocteţi); • - drepturi de acces (read only, read/write, execute only, execute/read); • - prezenţa în memorie (pentru sistemele cu memorie virtuală). C 2 16

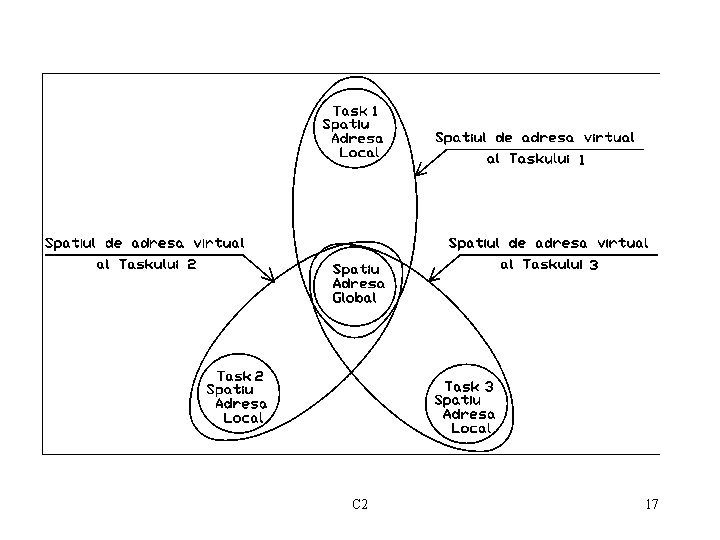

C 2 17

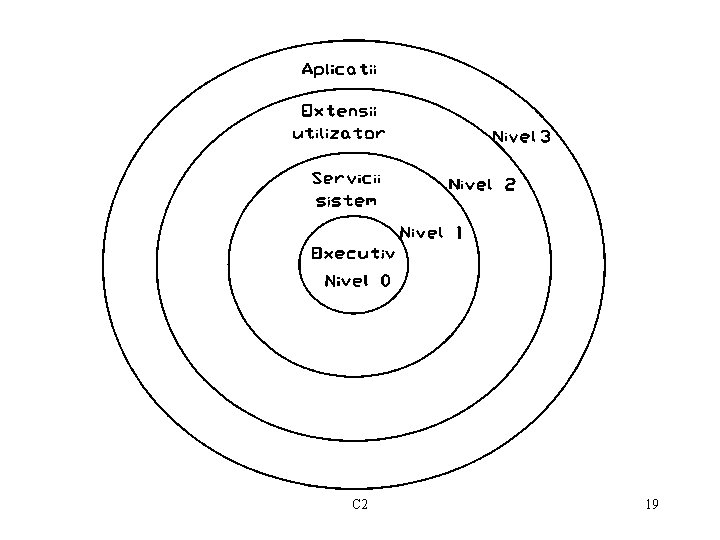

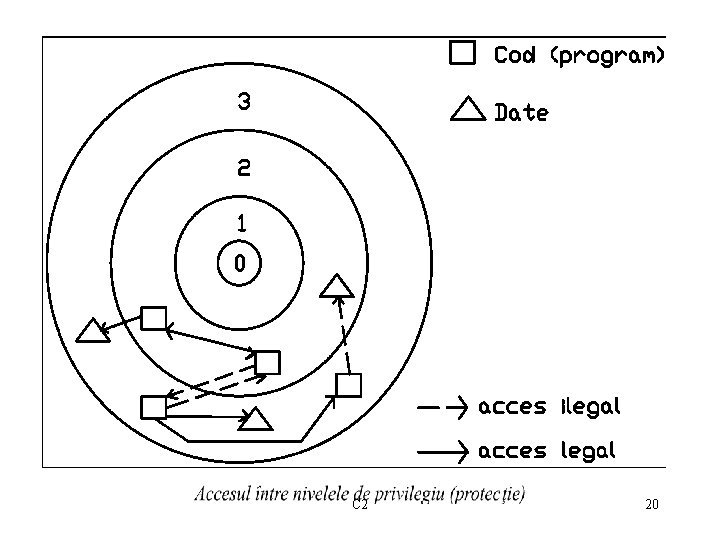

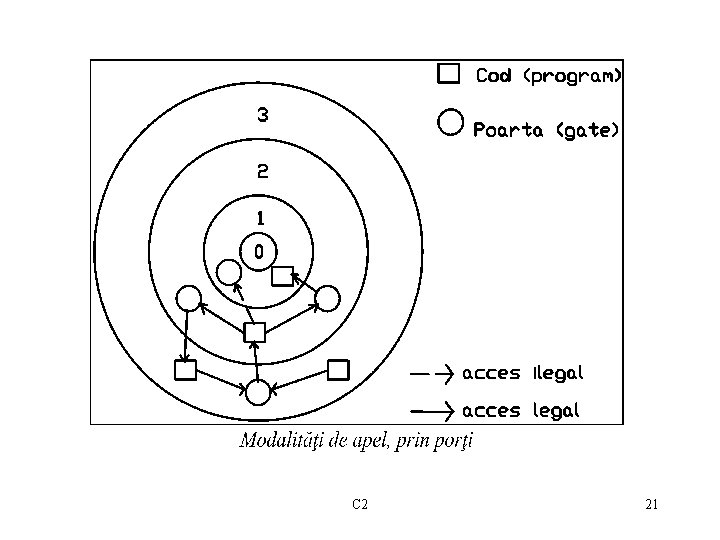

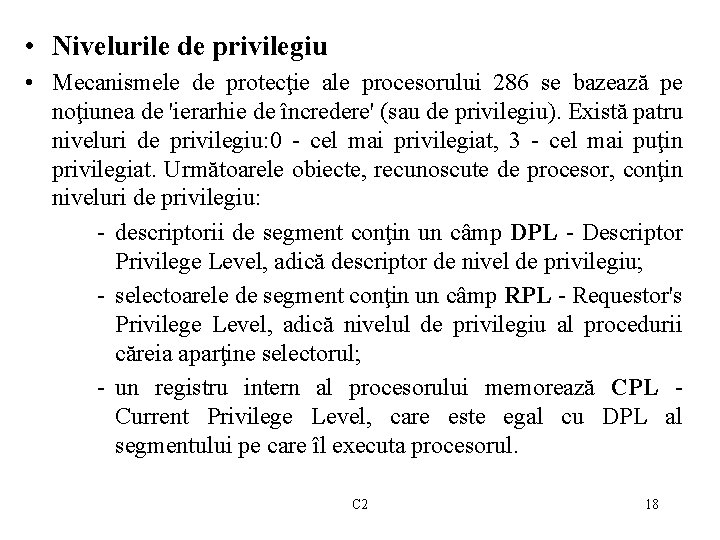

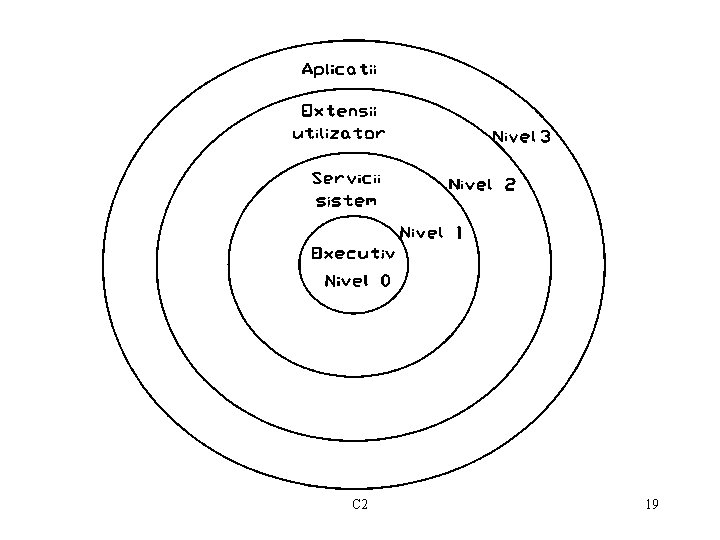

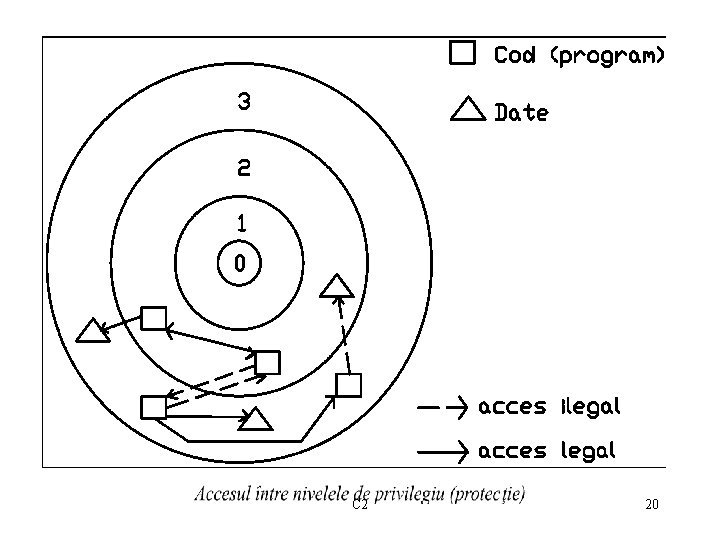

• Nivelurile de privilegiu • Mecanismele de protecţie ale procesorului 286 se bazează pe noţiunea de 'ierarhie de încredere' (sau de privilegiu). Există patru niveluri de privilegiu: 0 - cel mai privilegiat, 3 - cel mai puţin privilegiat. Următoarele obiecte, recunoscute de procesor, conţin niveluri de privilegiu: - descriptorii de segment conţin un câmp DPL - Descriptor Privilege Level, adică descriptor de nivel de privilegiu; - selectoarele de segment conţin un câmp RPL - Requestor's Privilege Level, adică nivelul de privilegiu al procedurii căreia aparţine selectorul; - un registru intern al procesorului memorează CPL Current Privilege Level, care este egal cu DPL al segmentului pe care îl executa procesorul. C 2 18

C 2 19

C 2 20

C 2 21

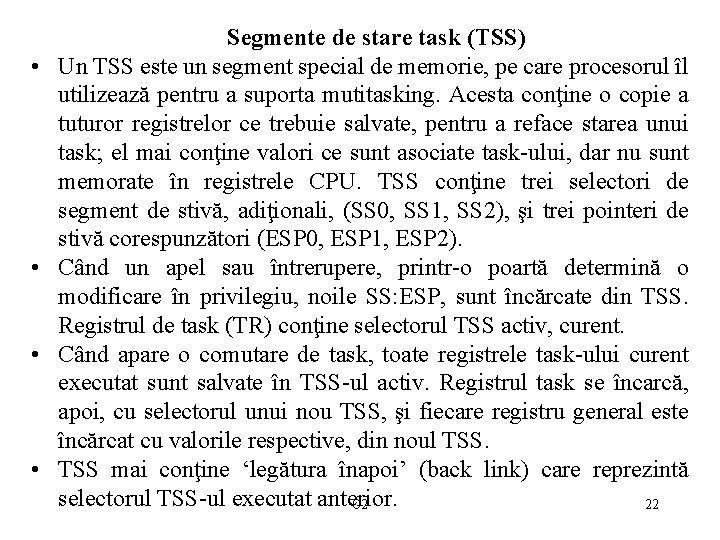

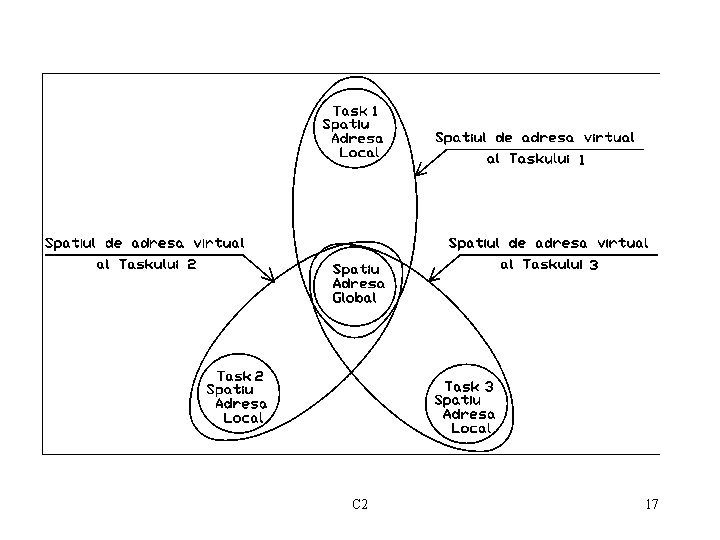

• • Segmente de stare task (TSS) Un TSS este un segment special de memorie, pe care procesorul îl utilizează pentru a suporta mutitasking. Acesta conţine o copie a tuturor registrelor ce trebuie salvate, pentru a reface starea unui task; el mai conţine valori ce sunt asociate task-ului, dar nu sunt memorate în registrele CPU. TSS conţine trei selectori de segment de stivă, adiţionali, (SS 0, SS 1, SS 2), şi trei pointeri de stivă corespunzători (ESP 0, ESP 1, ESP 2). Când un apel sau întrerupere, printr-o poartă determină o modificare în privilegiu, noile SS: ESP, sunt încărcate din TSS. Registrul de task (TR) conţine selectorul TSS activ, curent. Când apare o comutare de task, toate registrele task-ului curent executat sunt salvate în TSS-ul activ. Registrul task se încarcă, apoi, cu selectorul unui nou TSS, şi fiecare registru general este încărcat cu valorile respective, din noul TSS mai conţine ‘legătura înapoi’ (back link) care reprezintă selectorul TSS-ul executat anterior. C 2 22

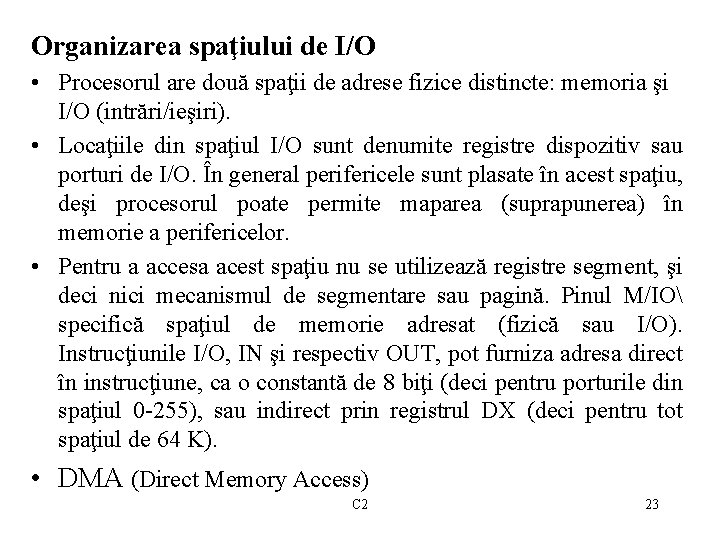

Organizarea spaţiului de I/O • Procesorul are două spaţii de adrese fizice distincte: memoria şi I/O (intrări/ieşiri). • Locaţiile din spaţiul I/O sunt denumite registre dispozitiv sau porturi de I/O. În general perifericele sunt plasate în acest spaţiu, deşi procesorul poate permite maparea (suprapunerea) în memorie a perifericelor. • Pentru a accesa acest spaţiu nu se utilizează registre segment, şi deci nici mecanismul de segmentare sau pagină. Pinul M/IO specifică spaţiul de memorie adresat (fizică sau I/O). Instrucţiunile I/O, IN şi respectiv OUT, pot furniza adresa direct în instrucţiune, ca o constantă de 8 biţi (deci pentru porturile din spaţiul 0 -255), sau indirect prin registrul DX (deci pentru tot spaţiul de 64 K). • DMA (Direct Memory Access) C 2 23