Structura pipeline a unui procesor MIPS 1 Consideraii

- Slides: 38

Structura pipeline a unui procesor MIPS 1

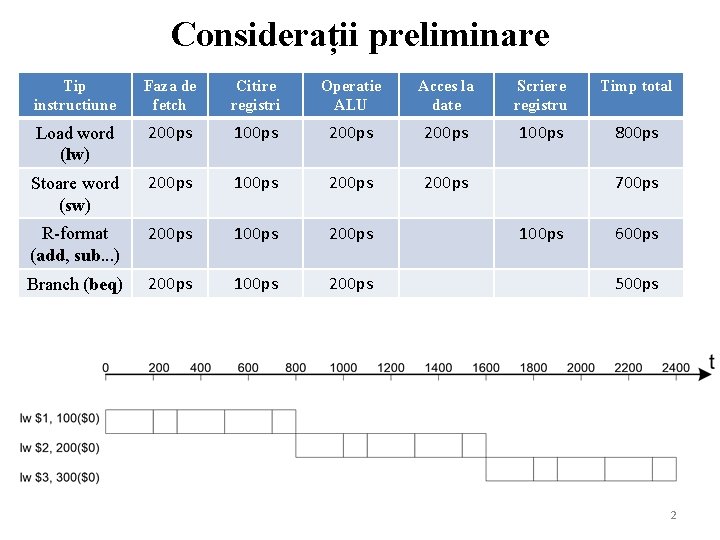

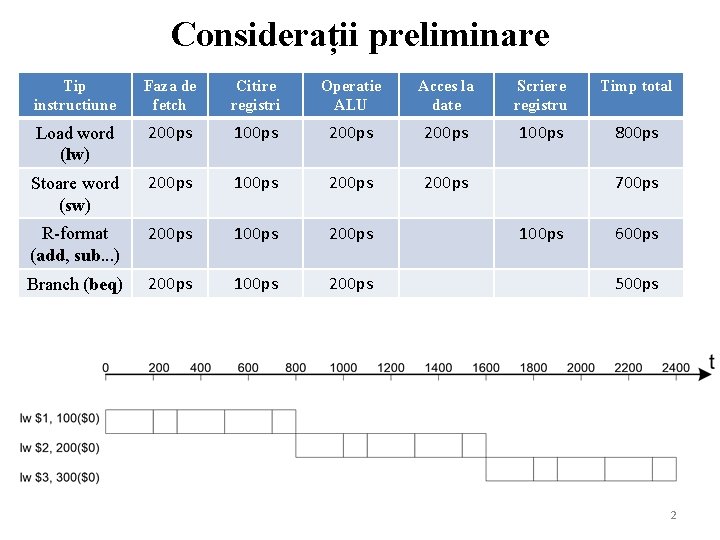

Considerații preliminare Tip instructiune Faza de fetch Citire registri Operatie ALU Acces la date Scriere registru Timp total Load word (lw) 200 ps 100 ps 800 ps Stoare word (sw) 200 ps 100 ps 200 ps R-format (add, sub. . . ) 200 ps 100 ps 200 ps Branch (beq) 200 ps 100 ps 200 ps 700 ps 100 ps 600 ps 500 ps 2

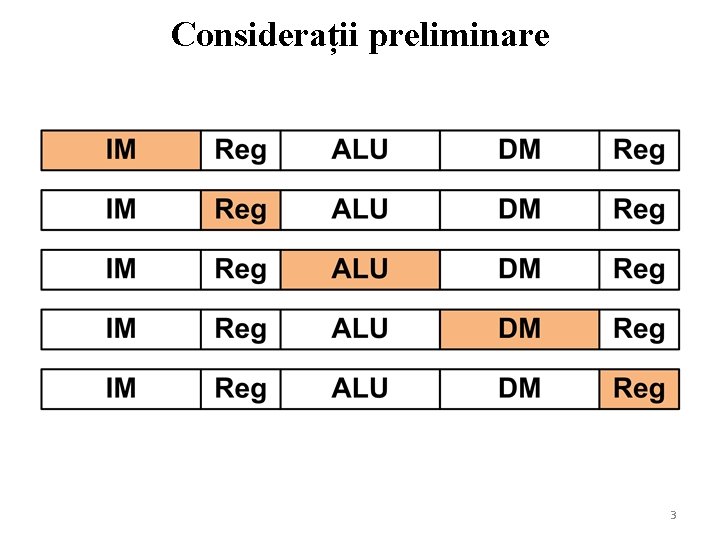

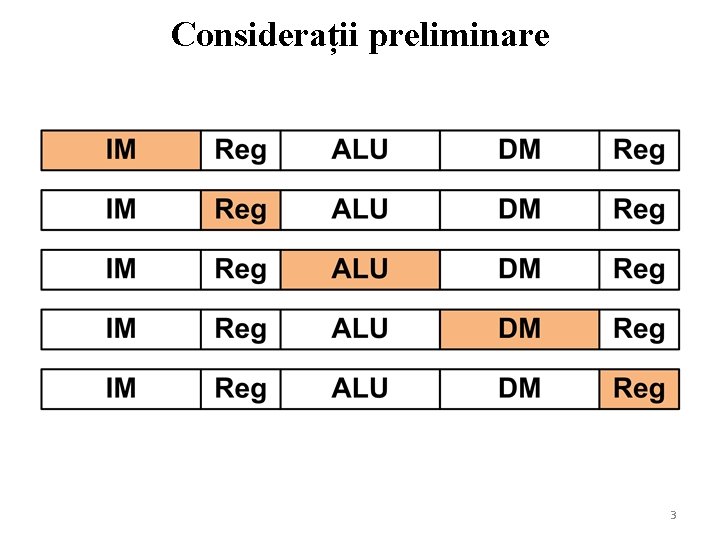

Considerații preliminare 3

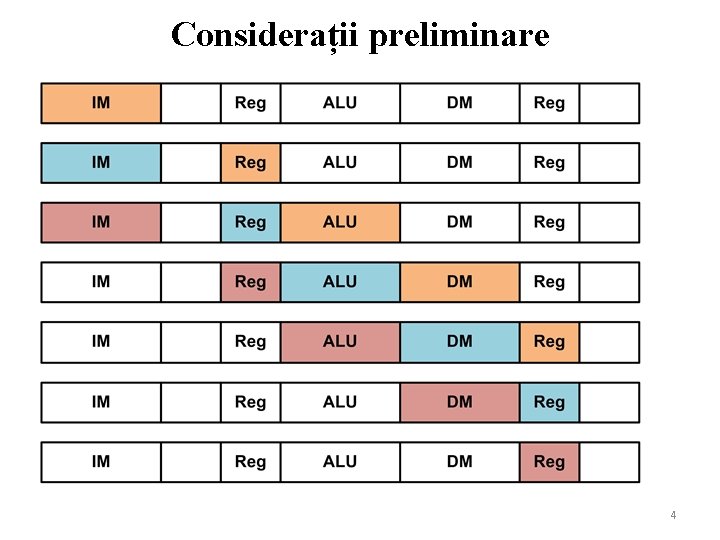

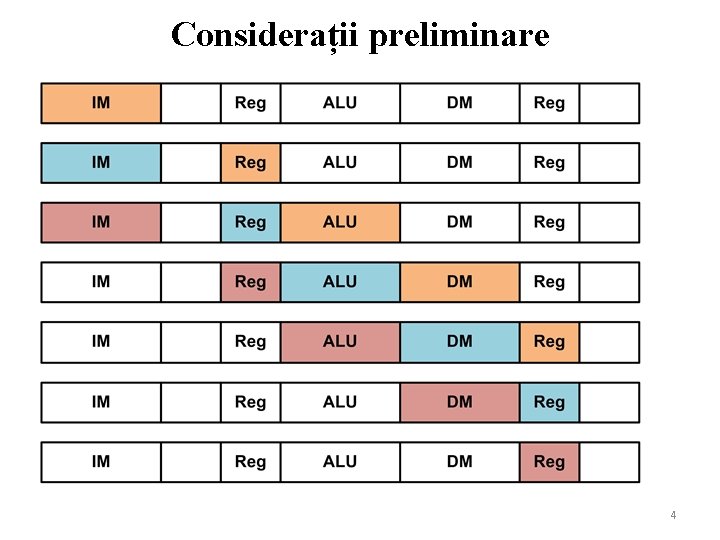

Considerații preliminare 4

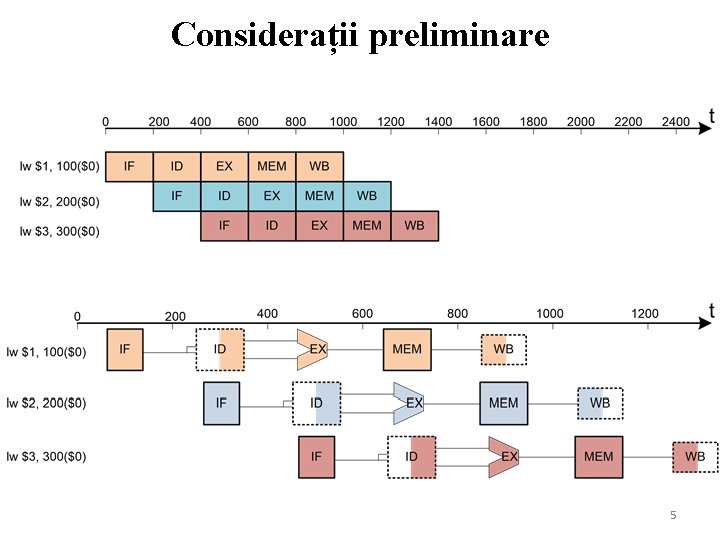

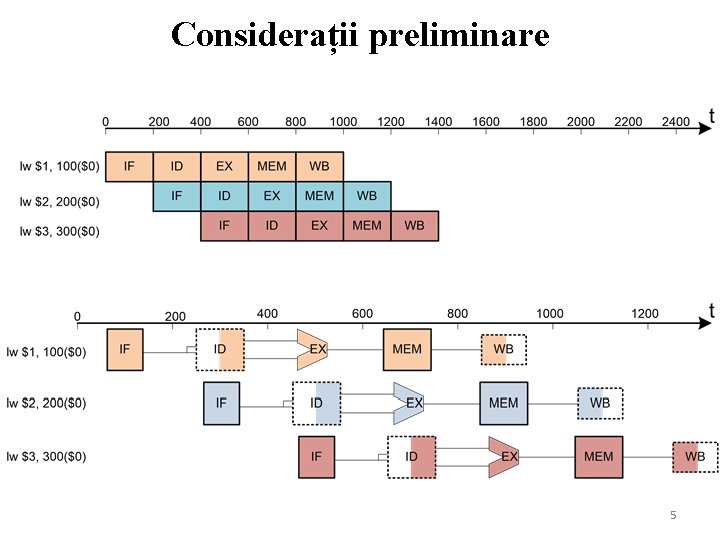

Considerații preliminare 5

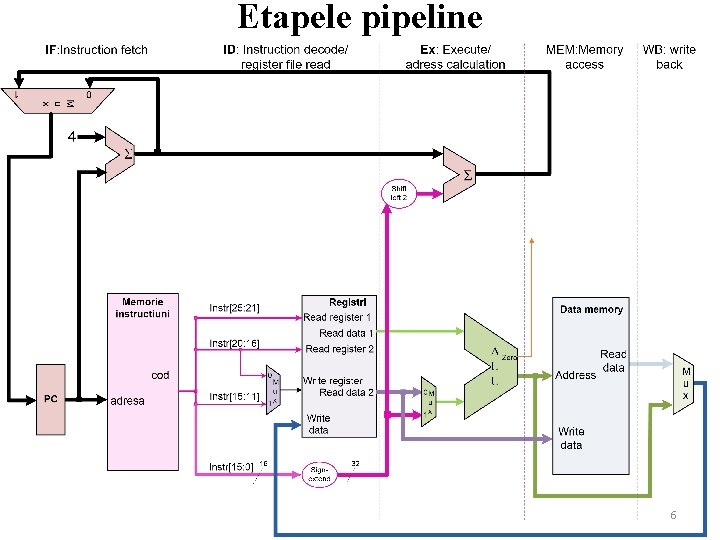

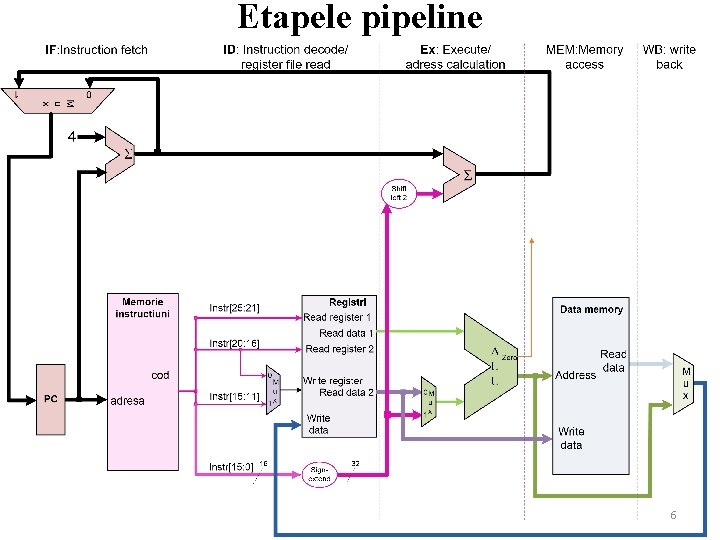

Etapele pipeline 6

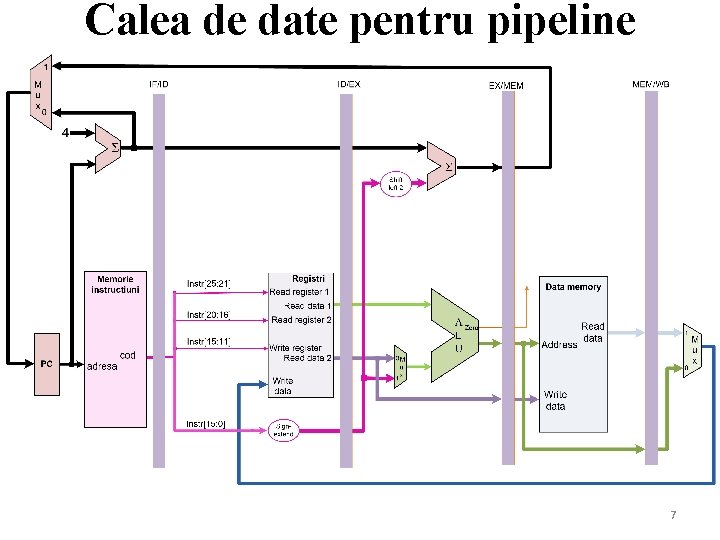

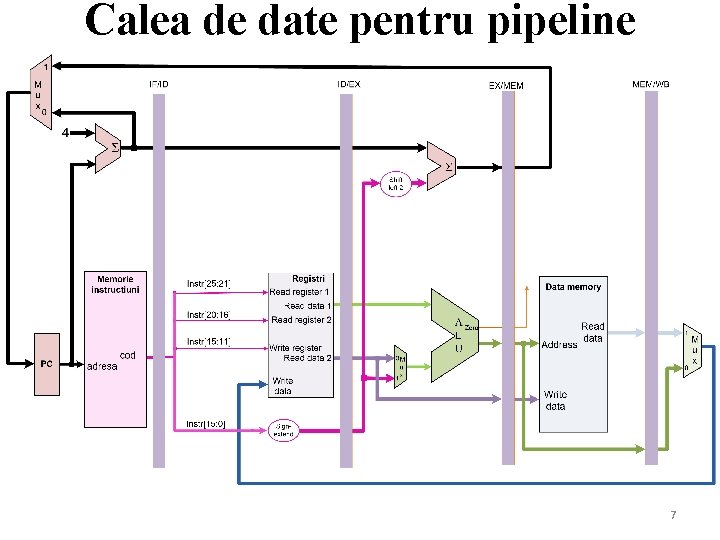

Calea de date pentru pipeline 7

Execuţia instrucţiunii lw – IF 8

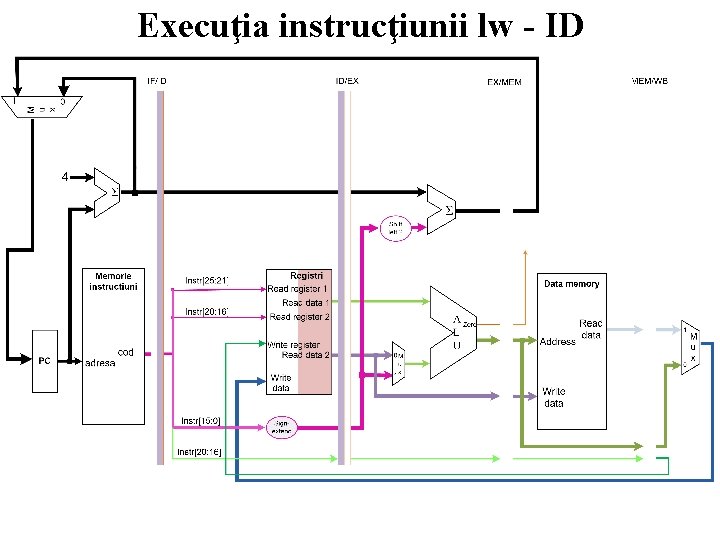

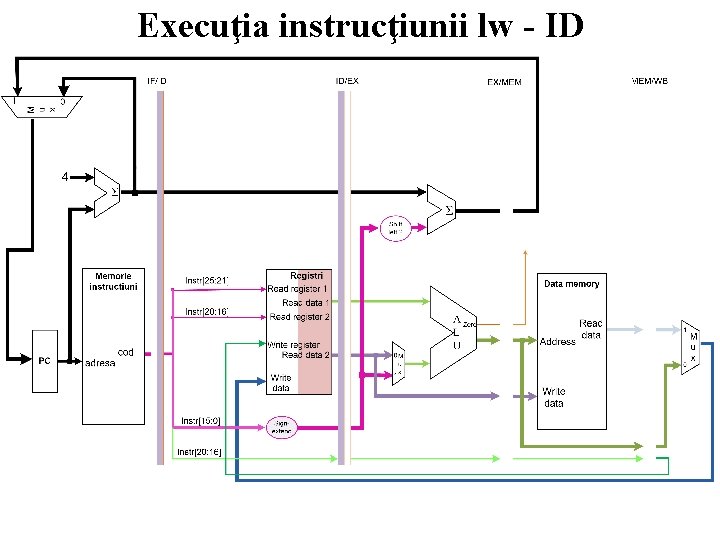

Execuţia instrucţiunii lw - ID

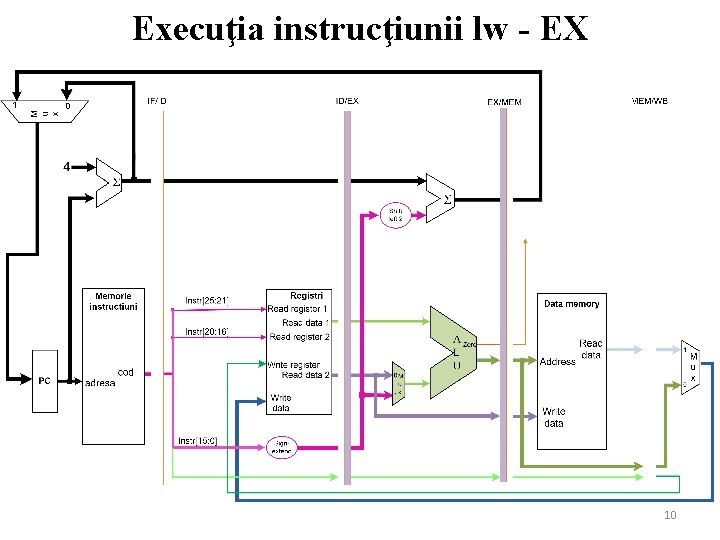

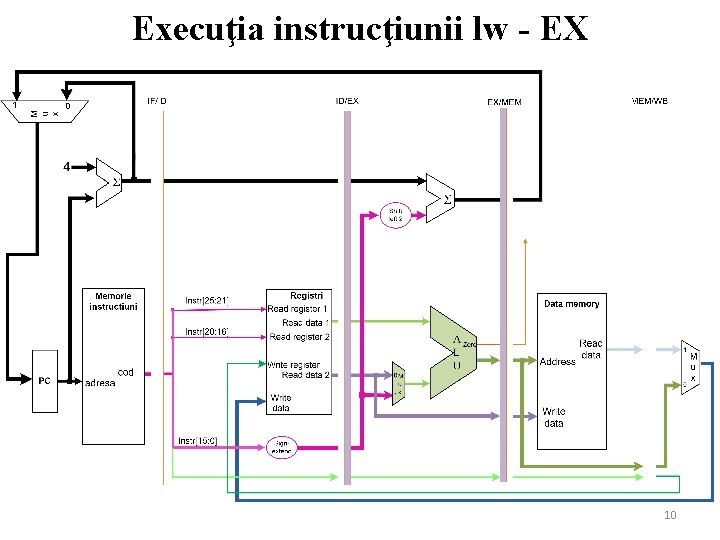

Execuţia instrucţiunii lw - EX 10

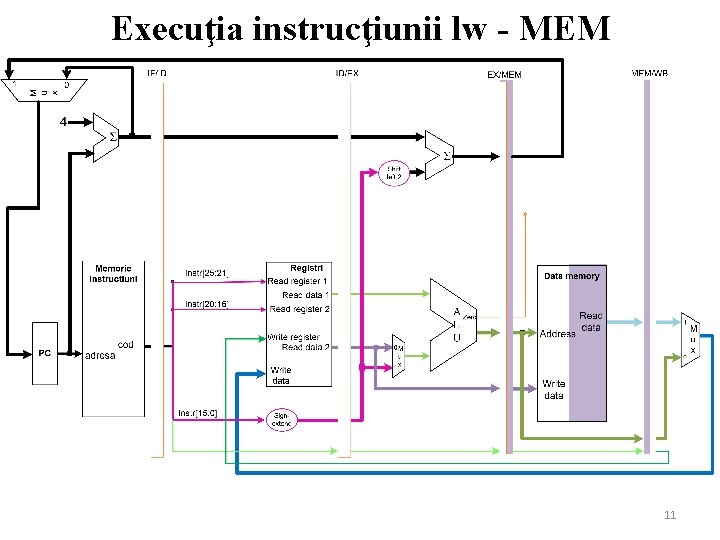

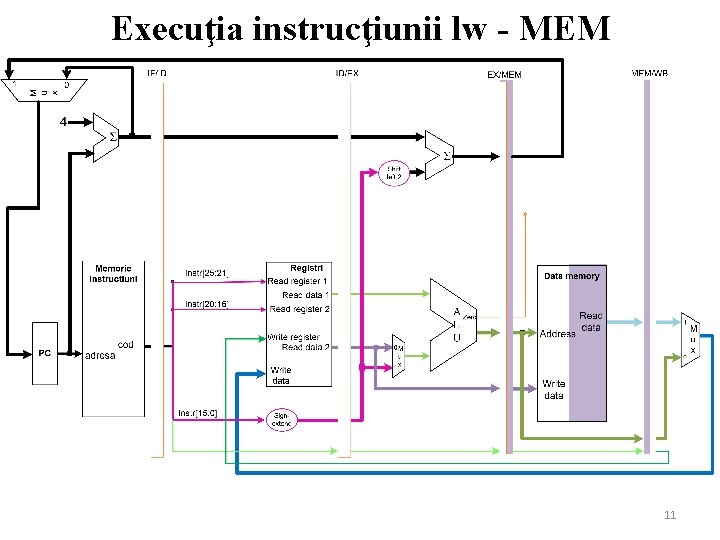

Execuţia instrucţiunii lw - MEM 11

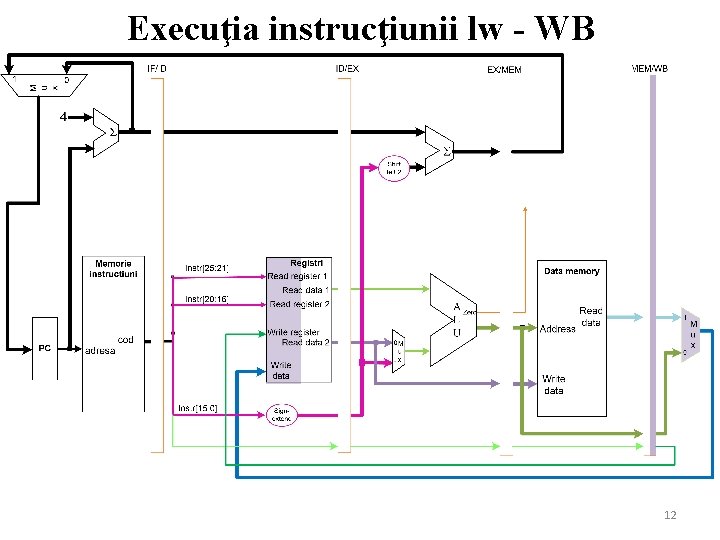

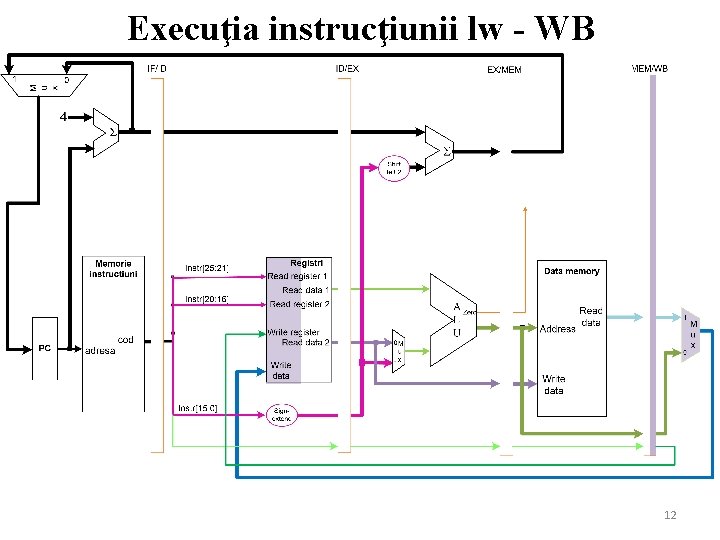

Execuţia instrucţiunii lw - WB 12

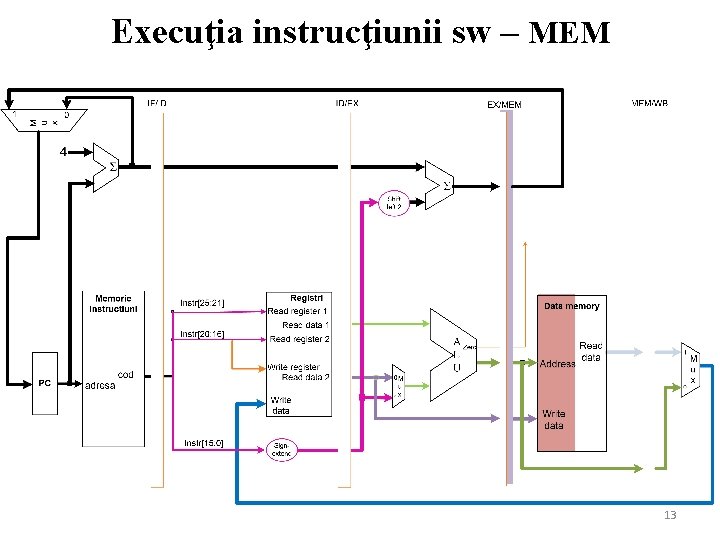

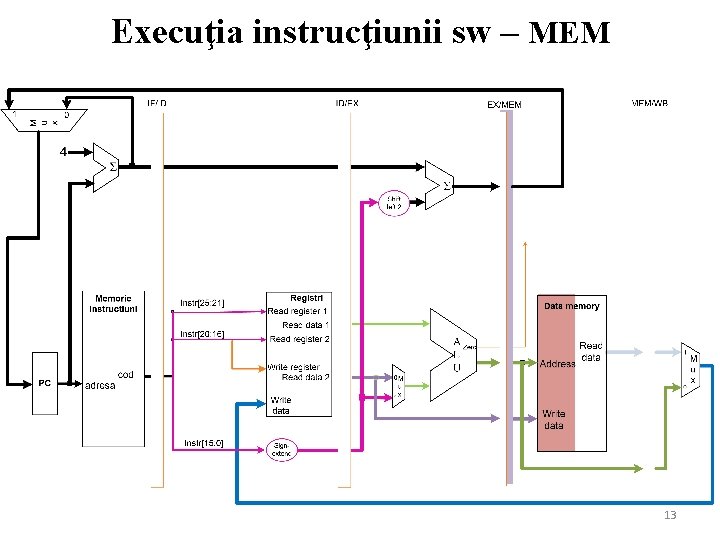

Execuţia instrucţiunii sw – MEM 13

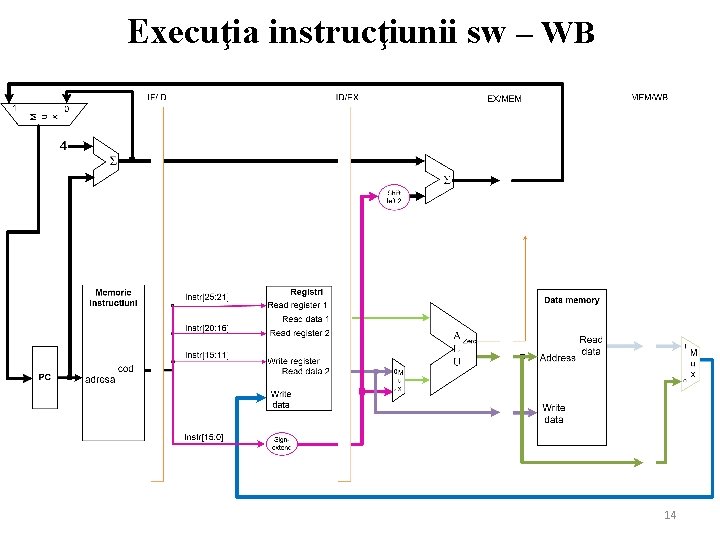

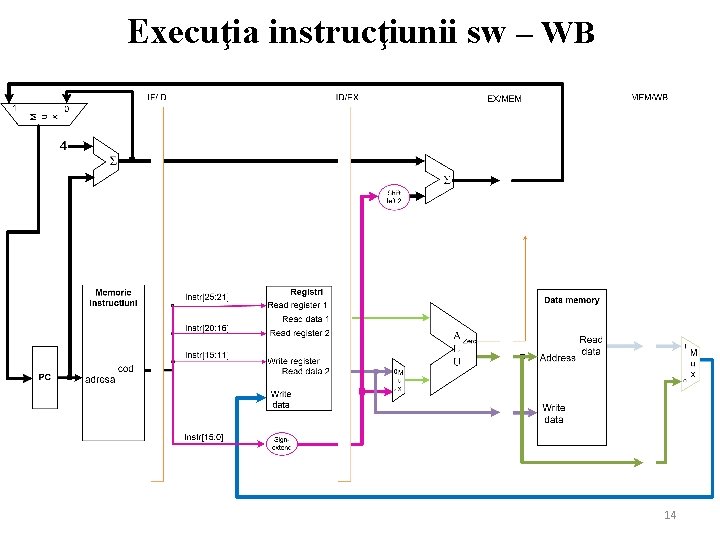

Execuţia instrucţiunii sw – WB 14

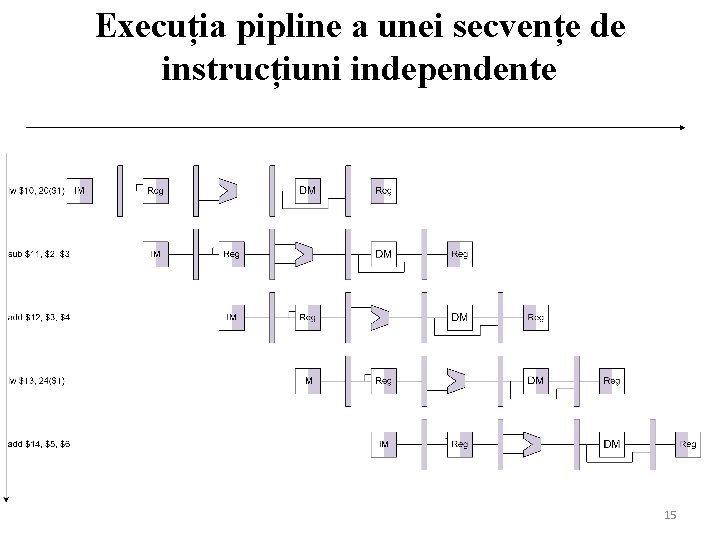

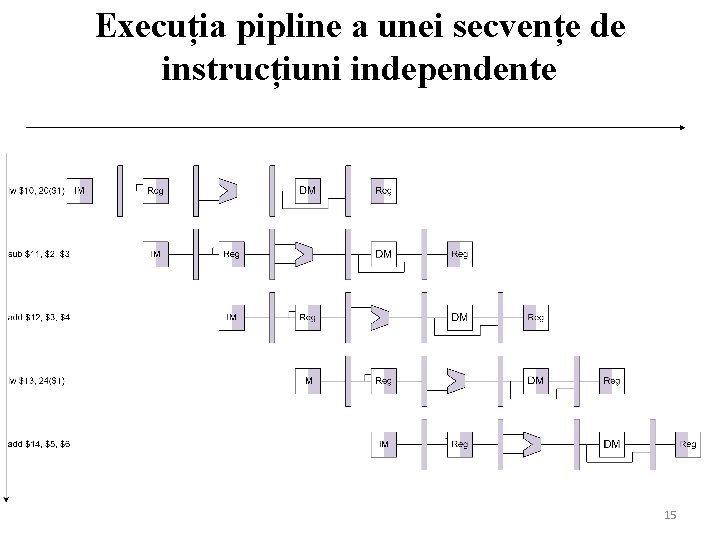

Execuția pipline a unei secvențe de instrucțiuni independente 15

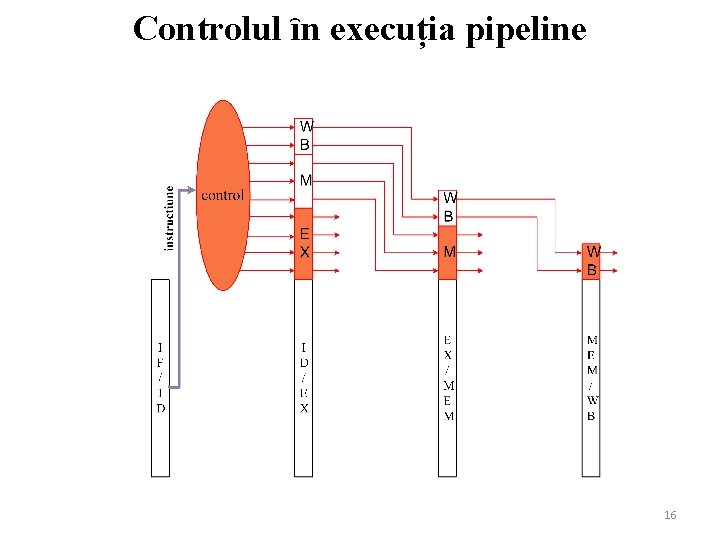

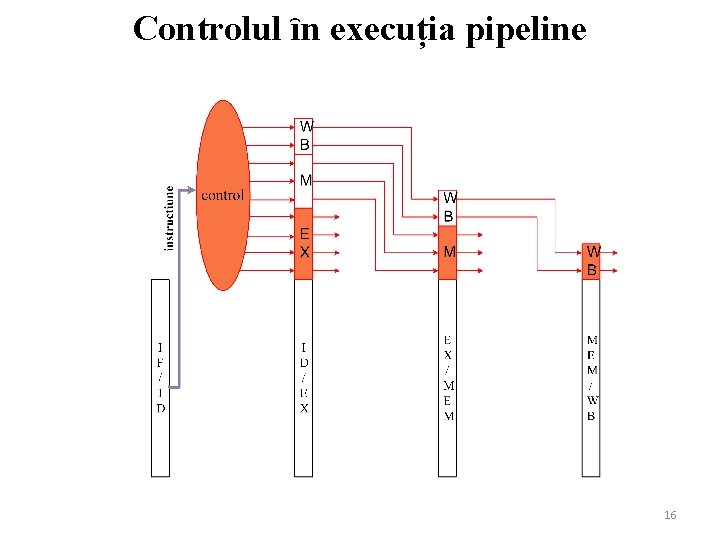

Controlul ȋn execuția pipeline 16

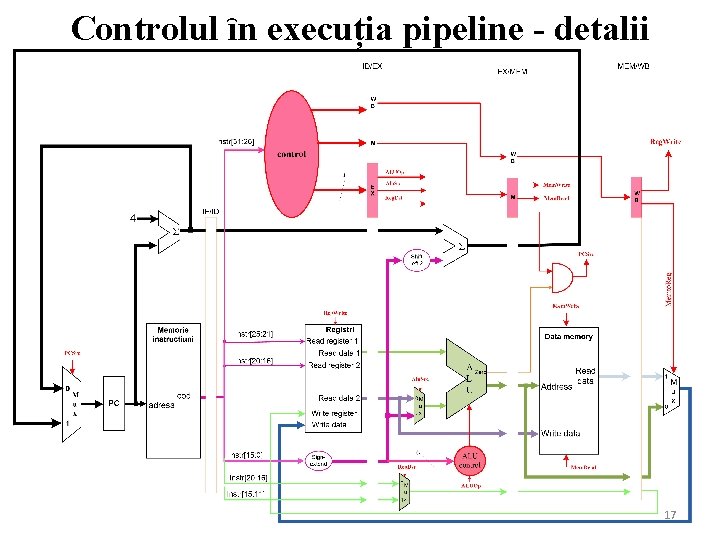

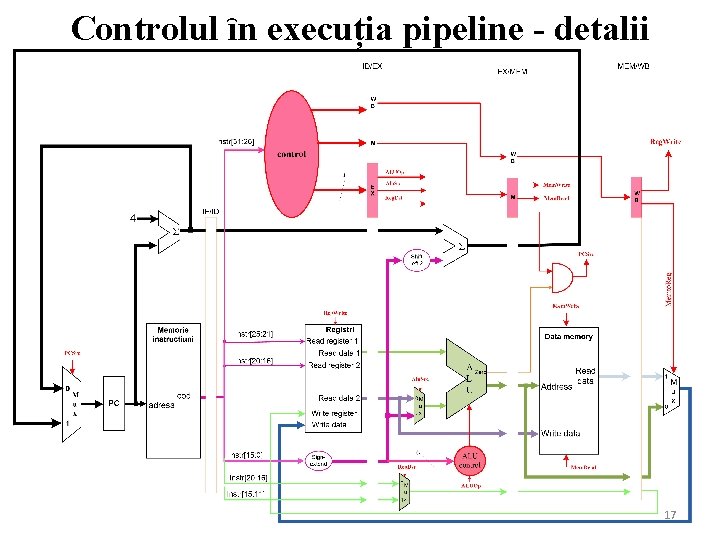

Controlul ȋn execuția pipeline - detalii 17

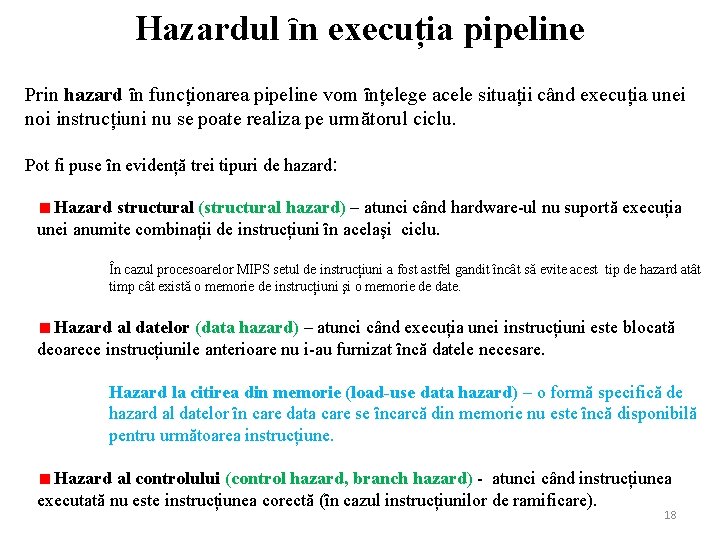

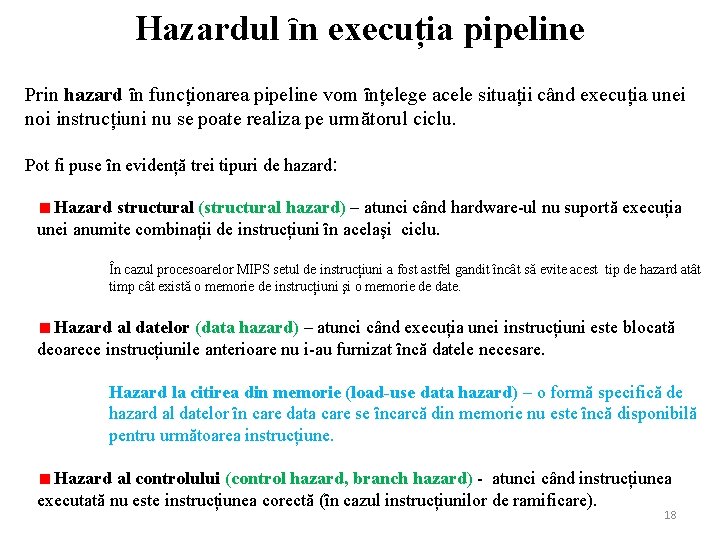

Hazardul ȋn execuția pipeline Prin hazard ȋn funcționarea pipeline vom ȋnțelege acele situații când execuția unei noi instrucțiuni nu se poate realiza pe următorul ciclu. Pot fi puse ȋn evidență trei tipuri de hazard: Hazard structural (structural hazard) – atunci când hardware-ul nu suportă execuția unei anumite combinații de instrucțiuni ȋn acelaşi ciclu. În cazul procesoarelor MIPS setul de instrucțiuni a fost astfel gandit ȋncât să evite acest tip de hazard atât timp cât există o memorie de instrucțiuni şi o memorie de date. Hazard al datelor (data hazard) – atunci când execuția unei instrucțiuni este blocată deoarece instrucțiunile anterioare nu i-au furnizat ȋncă datele necesare. Hazard la citirea din memorie (load-use data hazard) – o formă specifică de hazard al datelor ȋn care data care se ȋncarcă din memorie nu este ȋncă disponibilă pentru următoarea instrucțiune. Hazard al controlului (control hazard, branch hazard) - atunci când instrucțiunea executată nu este instrucțiunea corectă (ȋn cazul instrucțiunilor de ramificare). 18

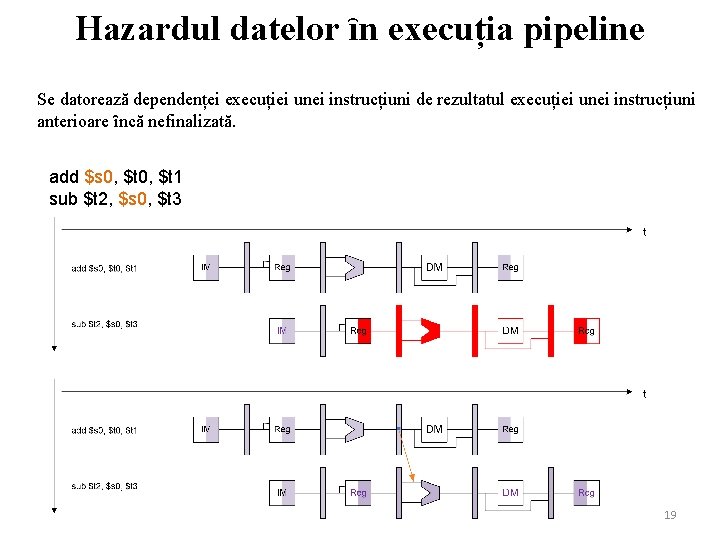

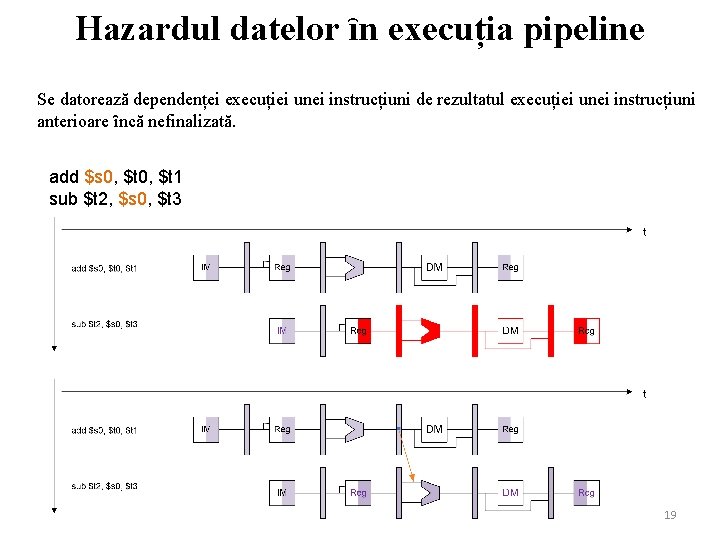

Hazardul datelor ȋn execuția pipeline Se datorează dependenței execuției unei instrucțiuni de rezultatul execuției unei instrucțiuni anterioare ȋncă nefinalizată. add $s 0, $t 1 sub $t 2, $s 0, $t 3 19

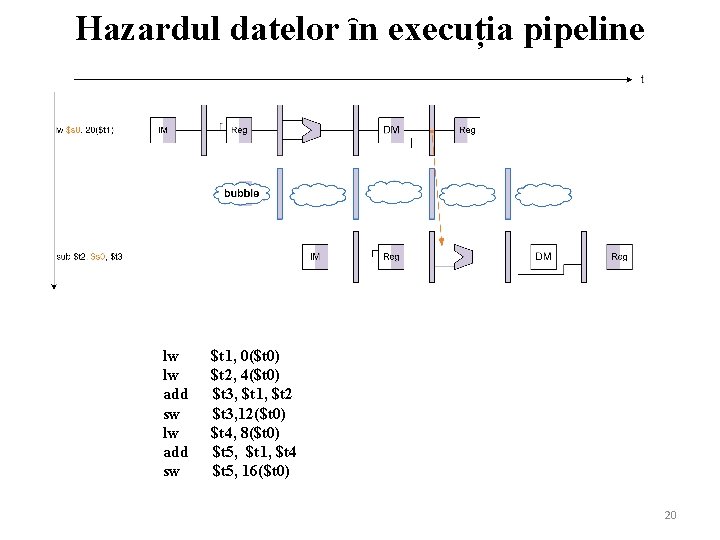

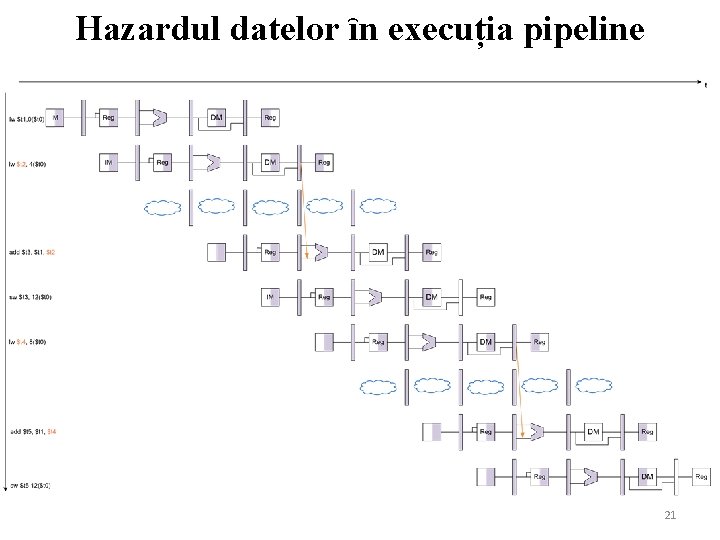

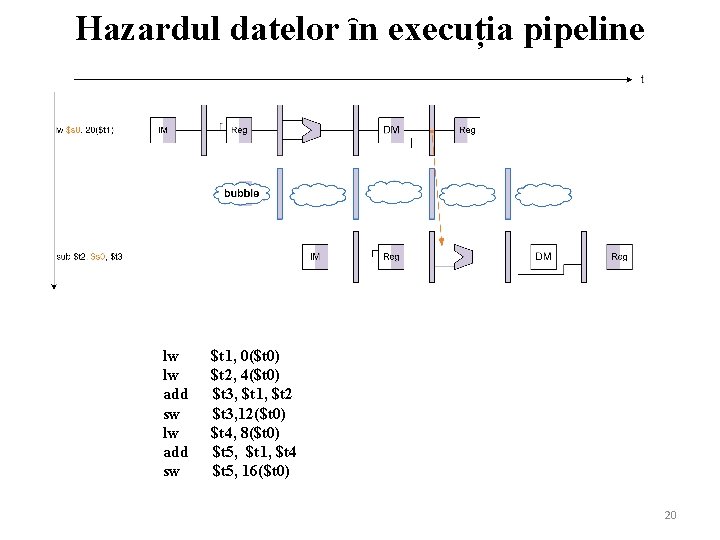

Hazardul datelor ȋn execuția pipeline lw lw add sw $t 1, 0($t 0) $t 2, 4($t 0) $t 3, $t 1, $t 2 $t 3, 12($t 0) $t 4, 8($t 0) $t 5, $t 1, $t 4 $t 5, 16($t 0) lw lw lw add sw $t 1, 0($t 0) $t 2, 4($t 0) $t 4, 8($t 0) $t 3, $t 1, $t 2 $t 3, 12($t 0) $t 5, $t 1, $t 4 $5, 16($t 0) 20

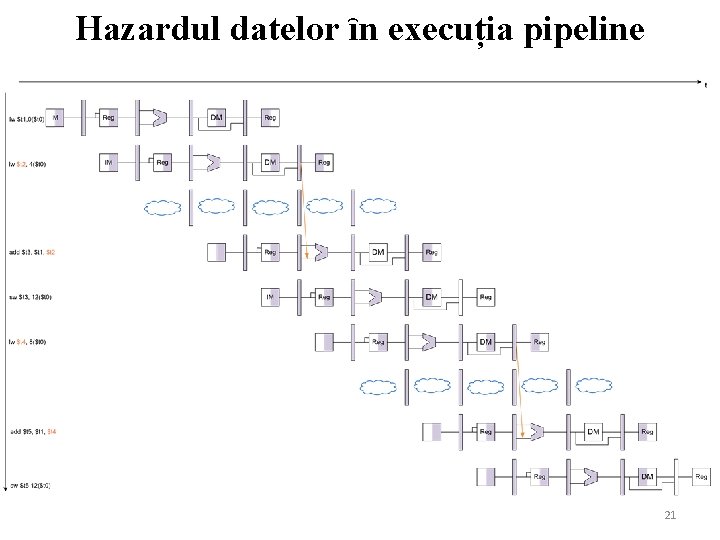

Hazardul datelor ȋn execuția pipeline 21

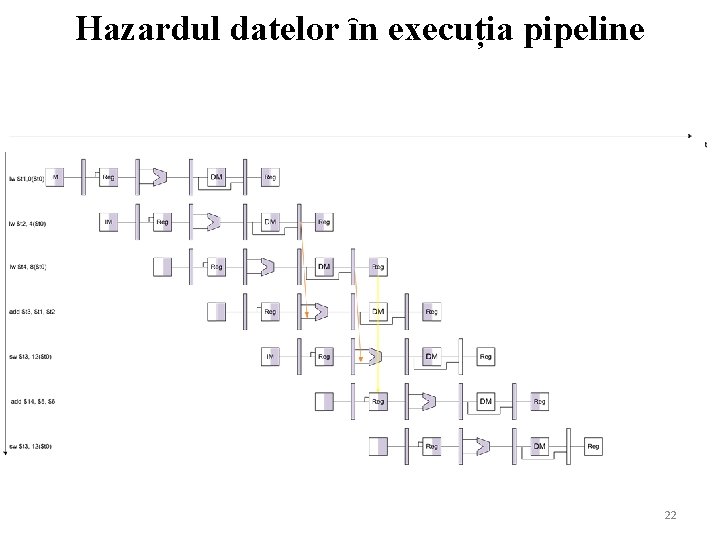

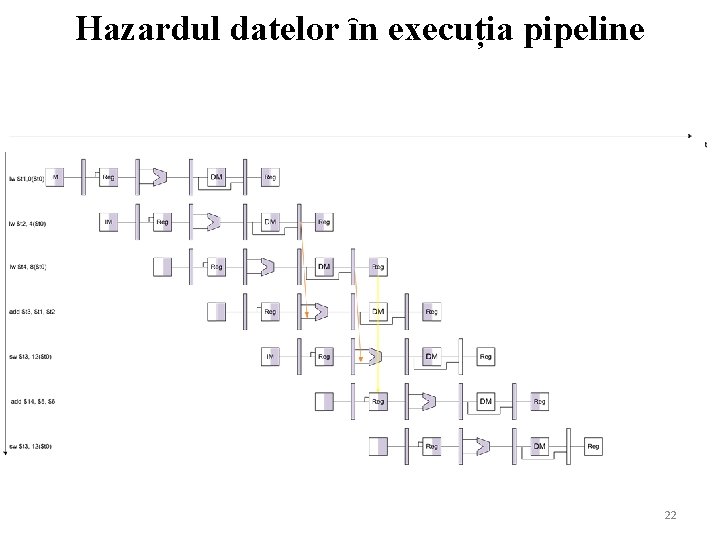

Hazardul datelor ȋn execuția pipeline 22

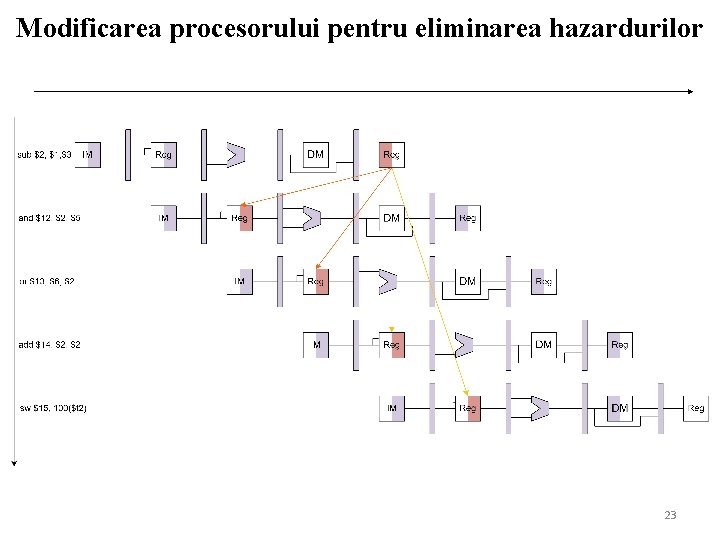

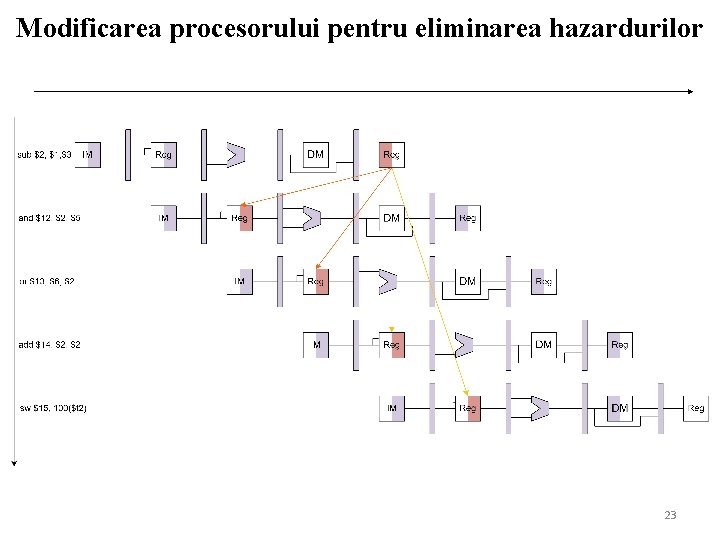

Modificarea procesorului pentru eliminarea hazardurilor 23

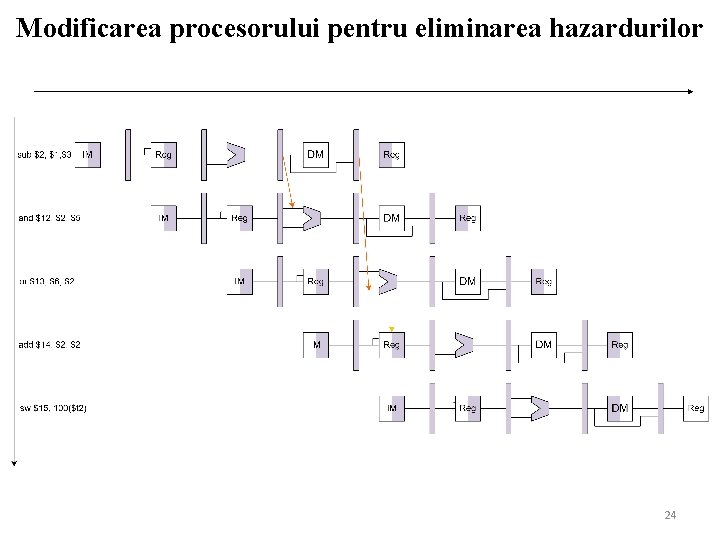

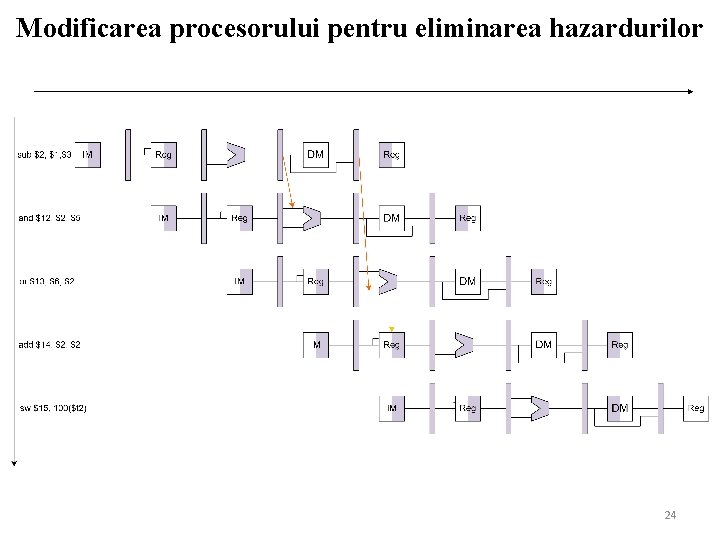

Modificarea procesorului pentru eliminarea hazardurilor 24

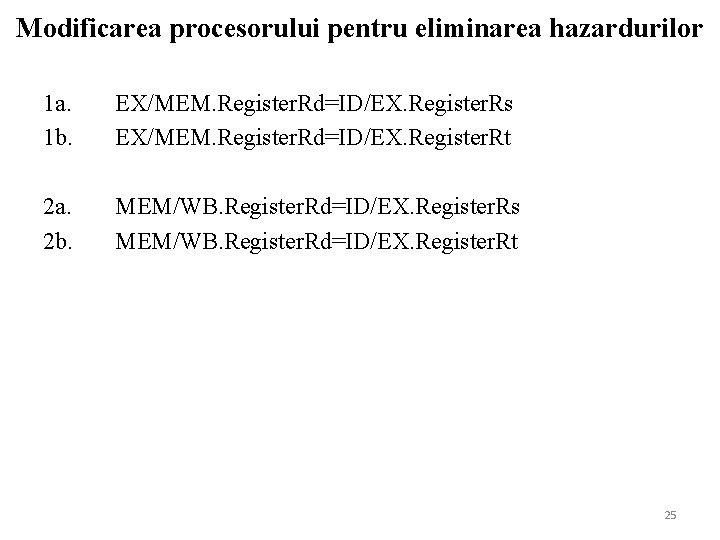

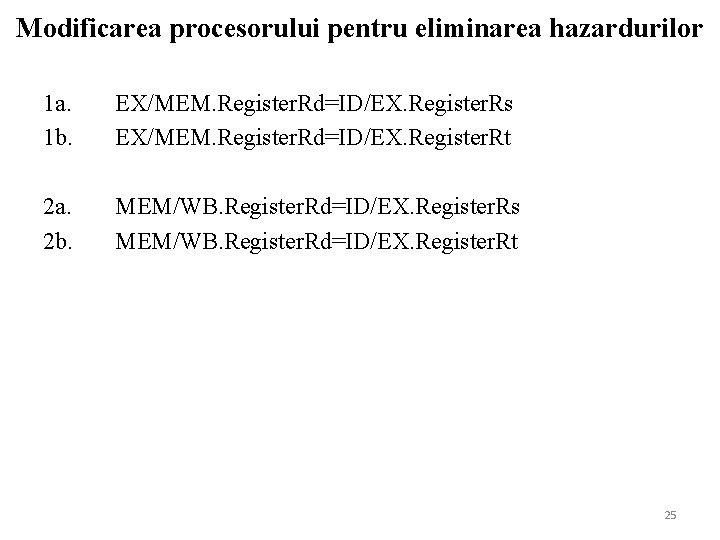

Modificarea procesorului pentru eliminarea hazardurilor 1 a. 1 b. EX/MEM. Register. Rd=ID/EX. Register. Rs EX/MEM. Register. Rd=ID/EX. Register. Rt 2 a. 2 b. MEM/WB. Register. Rd=ID/EX. Register. Rs MEM/WB. Register. Rd=ID/EX. Register. Rt 25

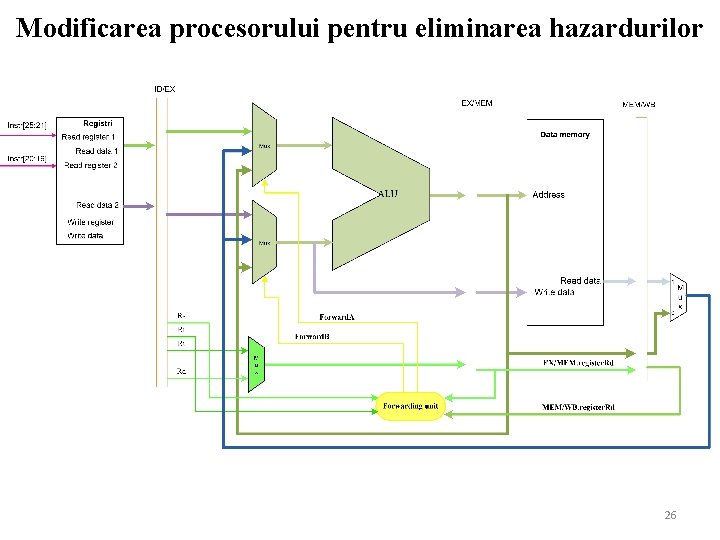

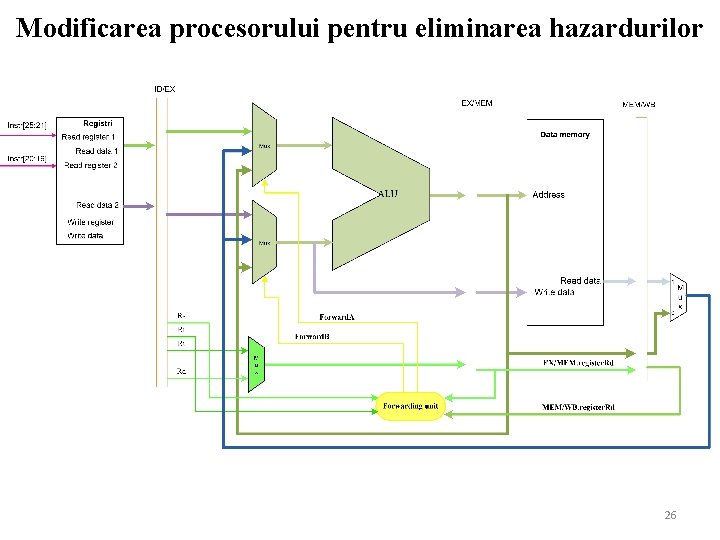

Modificarea procesorului pentru eliminarea hazardurilor 26

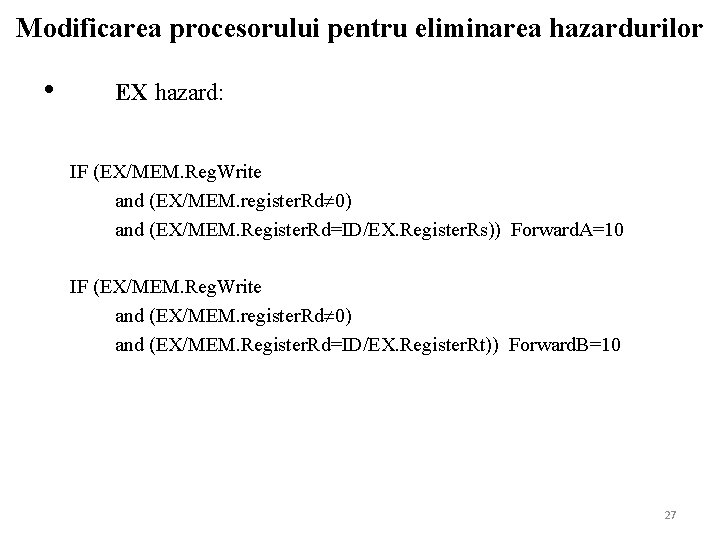

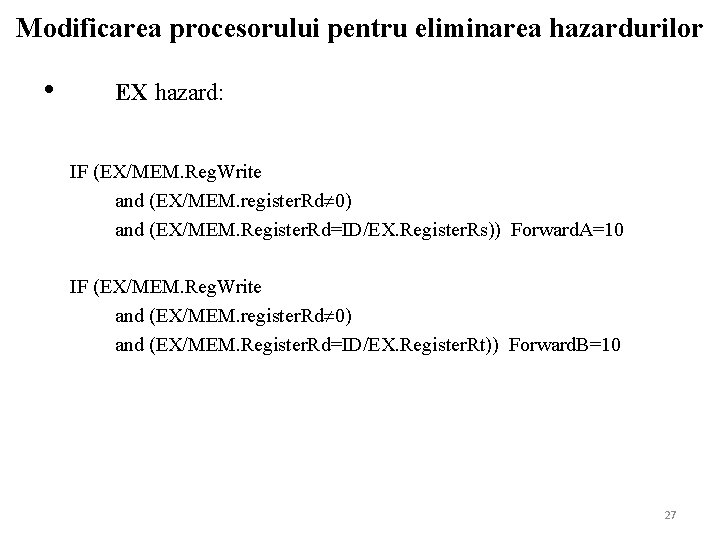

Modificarea procesorului pentru eliminarea hazardurilor • EX hazard: IF (EX/MEM. Reg. Write and (EX/MEM. register. Rd 0) and (EX/MEM. Register. Rd=ID/EX. Register. Rs)) Forward. A=10 IF (EX/MEM. Reg. Write and (EX/MEM. register. Rd 0) and (EX/MEM. Register. Rd=ID/EX. Register. Rt)) Forward. B=10 27

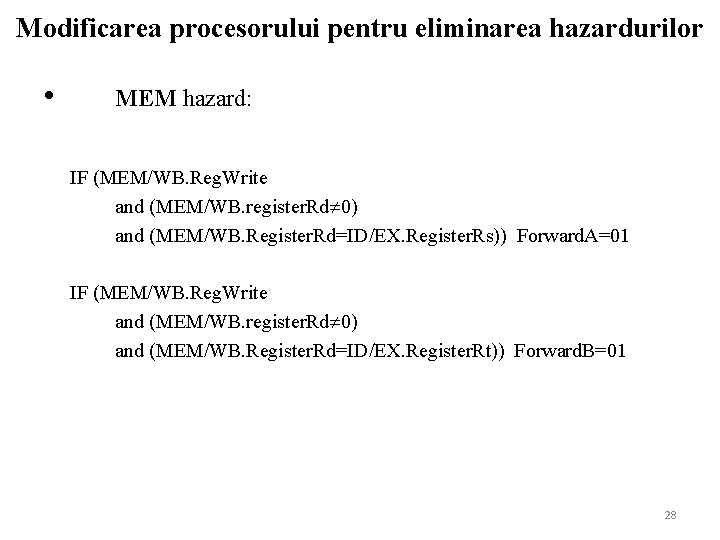

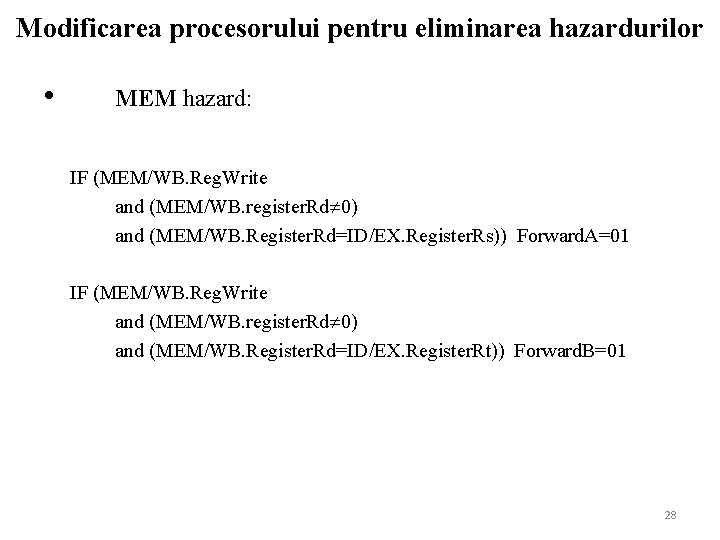

Modificarea procesorului pentru eliminarea hazardurilor • MEM hazard: IF (MEM/WB. Reg. Write and (MEM/WB. register. Rd 0) and (MEM/WB. Register. Rd=ID/EX. Register. Rs)) Forward. A=01 IF (MEM/WB. Reg. Write and (MEM/WB. register. Rd 0) and (MEM/WB. Register. Rd=ID/EX. Register. Rt)) Forward. B=01 28

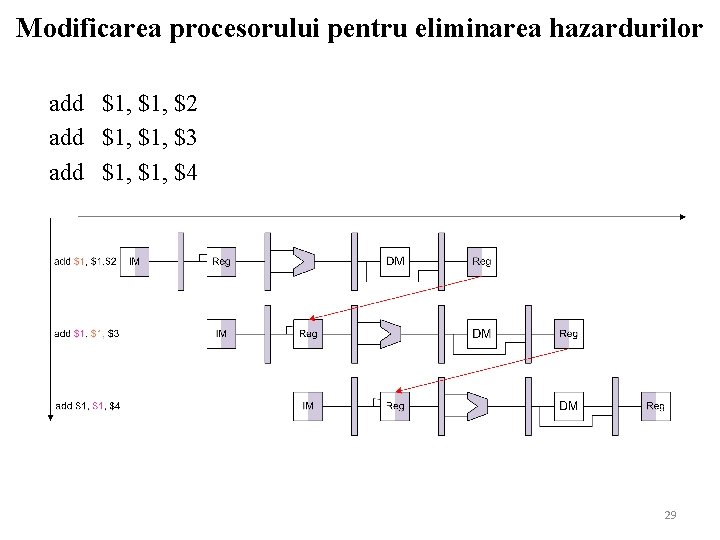

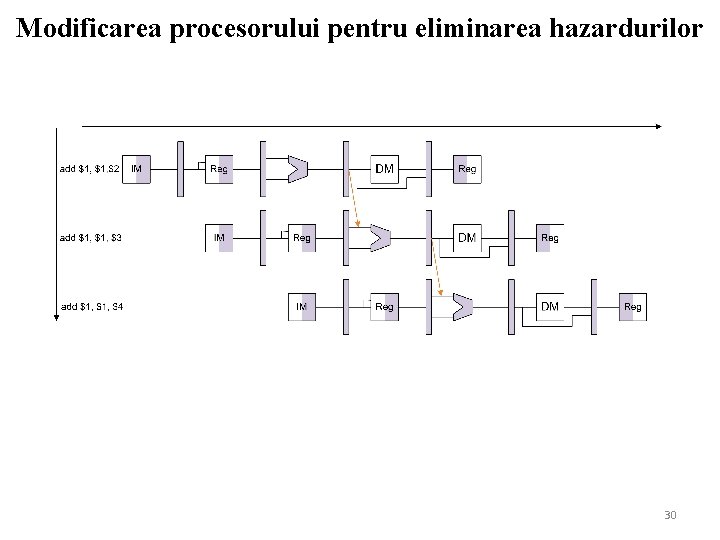

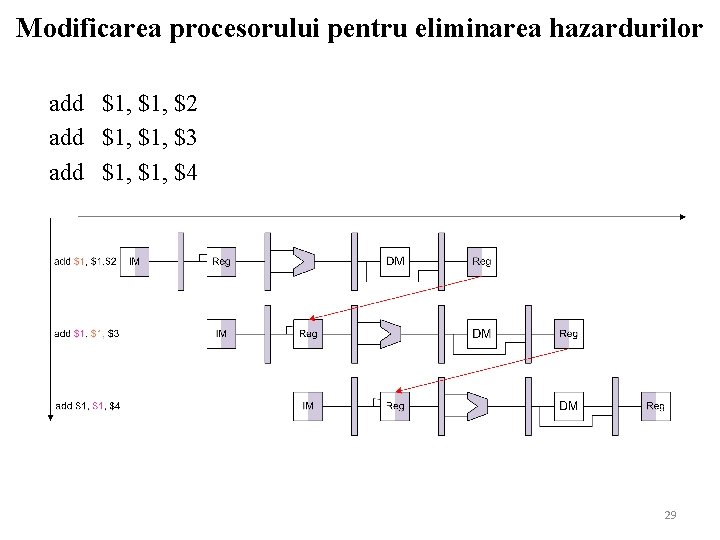

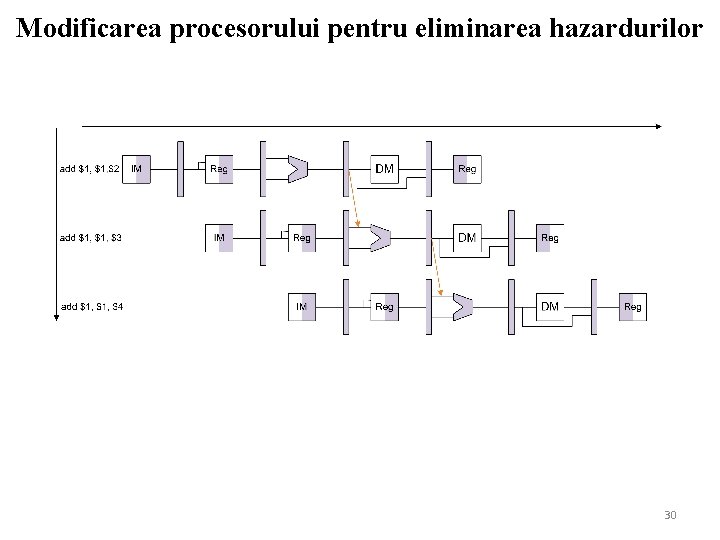

Modificarea procesorului pentru eliminarea hazardurilor add $1, $2 add $1, $3 add $1, $4 29

Modificarea procesorului pentru eliminarea hazardurilor 30

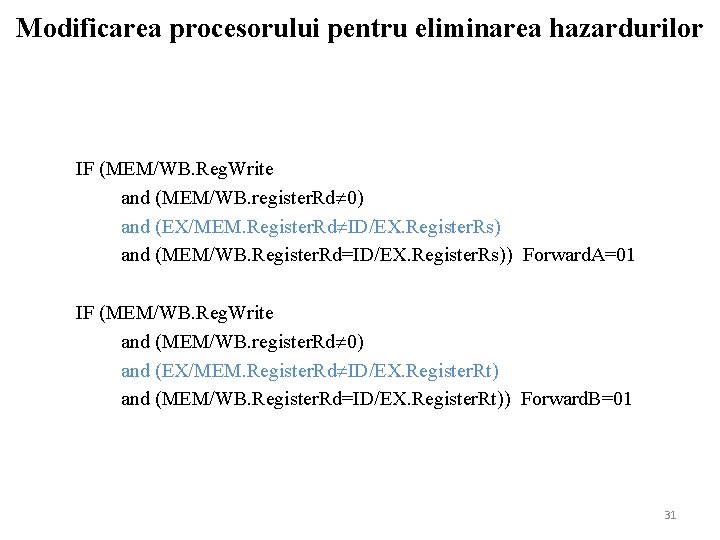

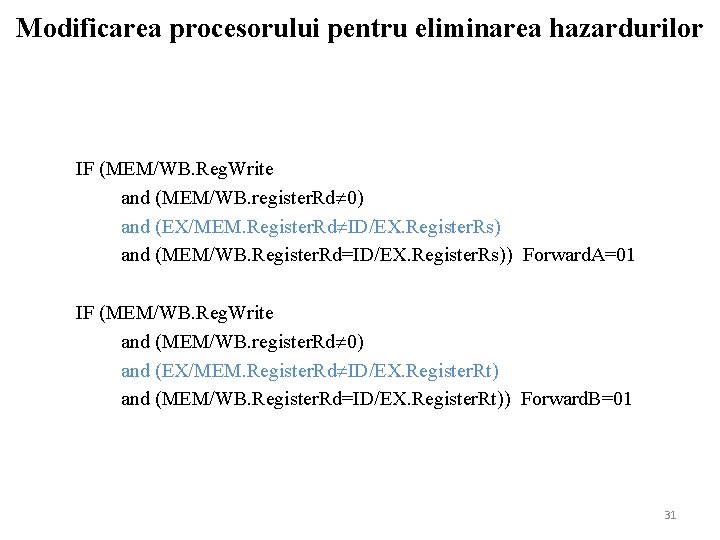

Modificarea procesorului pentru eliminarea hazardurilor IF (MEM/WB. Reg. Write and (MEM/WB. register. Rd 0) and (EX/MEM. Register. Rd ID/EX. Register. Rs) and (MEM/WB. Register. Rd=ID/EX. Register. Rs)) Forward. A=01 IF (MEM/WB. Reg. Write and (MEM/WB. register. Rd 0) and (EX/MEM. Register. Rd ID/EX. Register. Rt) and (MEM/WB. Register. Rd=ID/EX. Register. Rt)) Forward. B=01 31

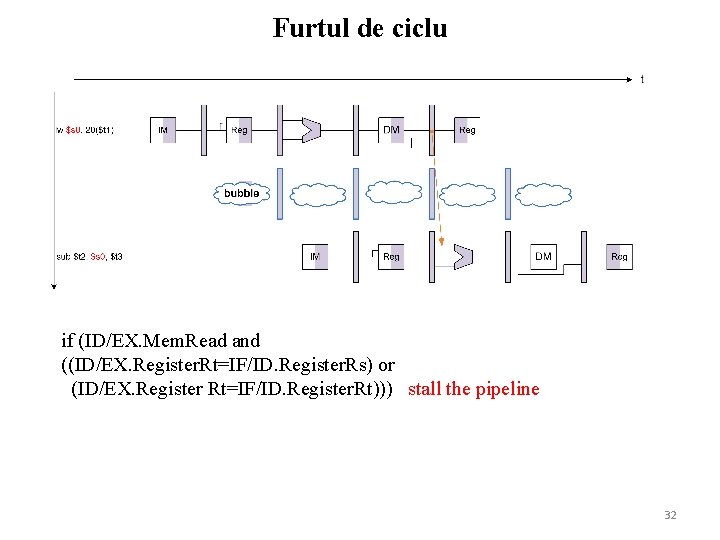

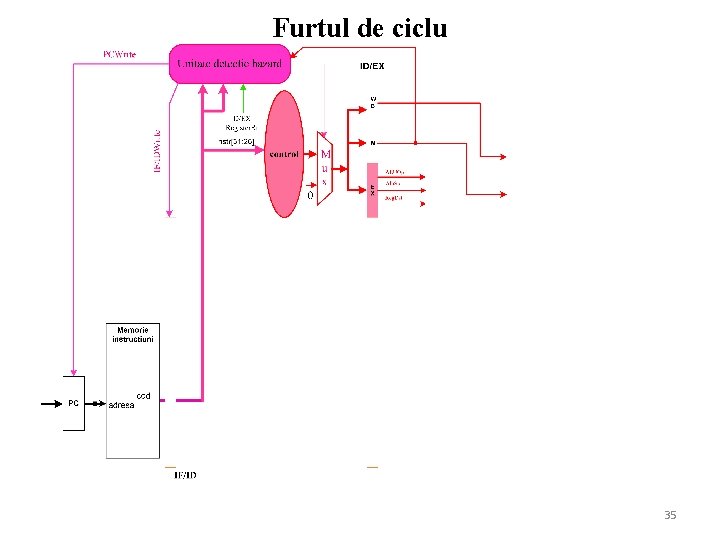

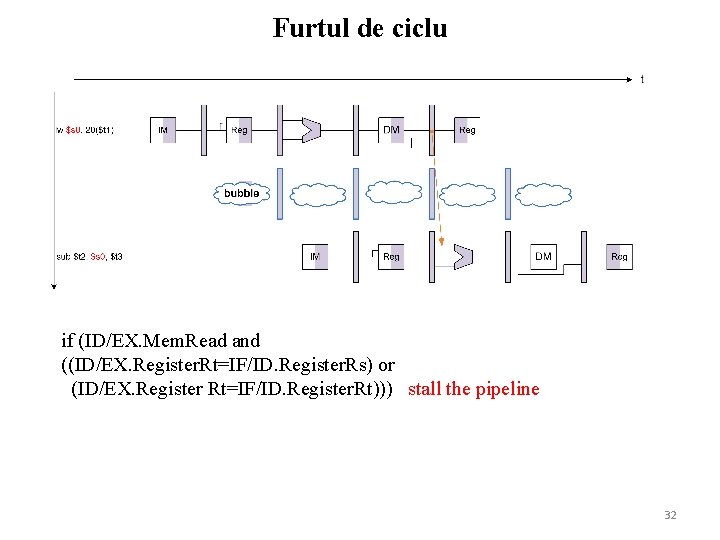

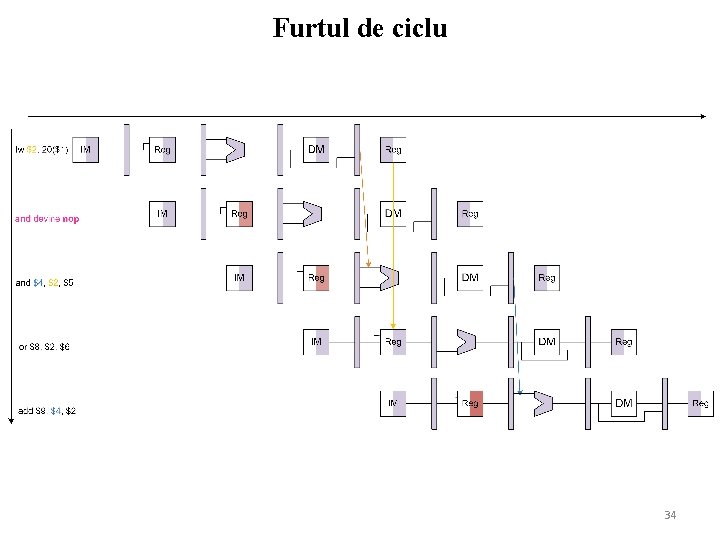

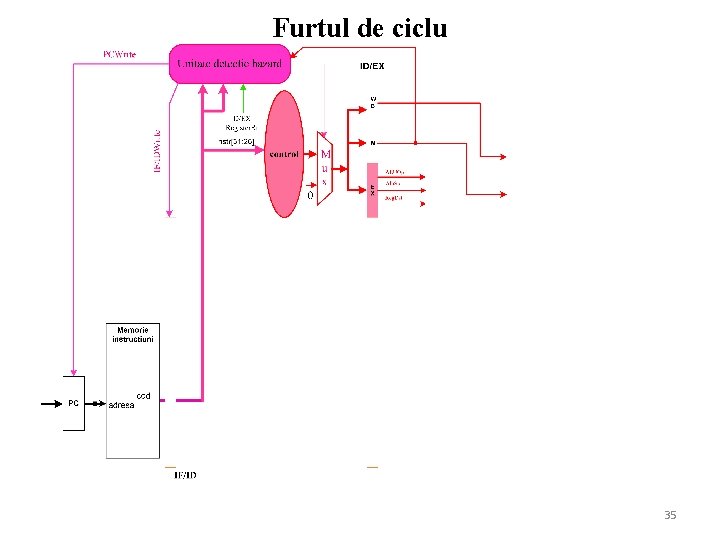

Furtul de ciclu if (ID/EX. Mem. Read and ((ID/EX. Register. Rt=IF/ID. Register. Rs) or (ID/EX. Register Rt=IF/ID. Register. Rt))) stall the pipeline 32

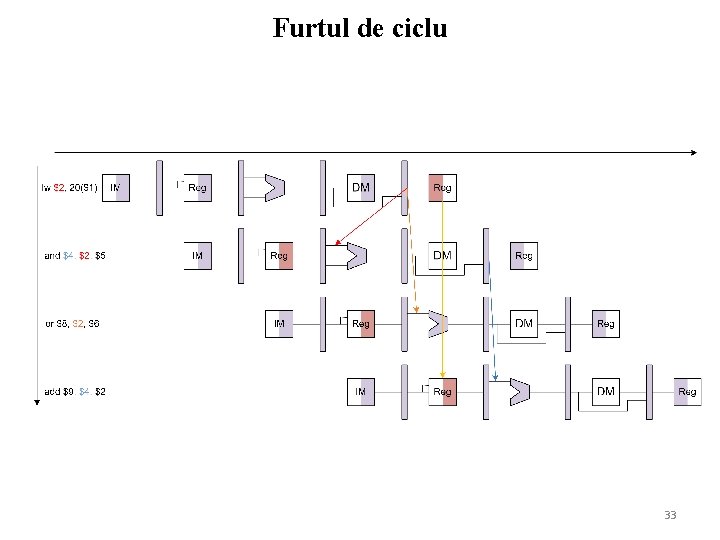

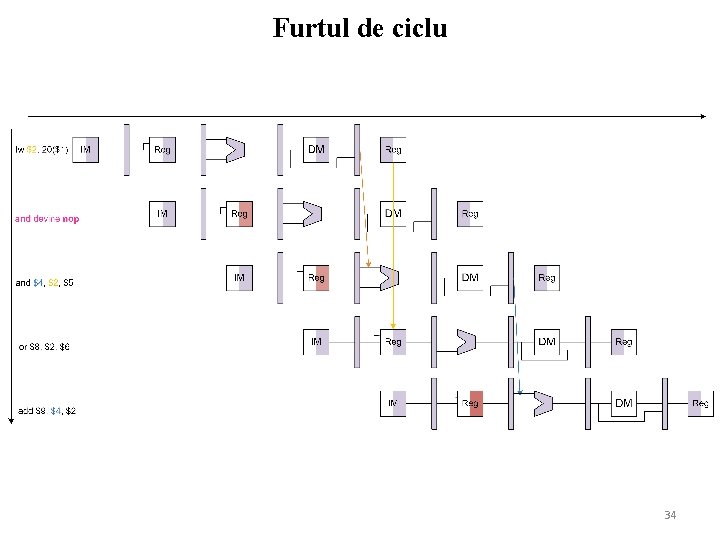

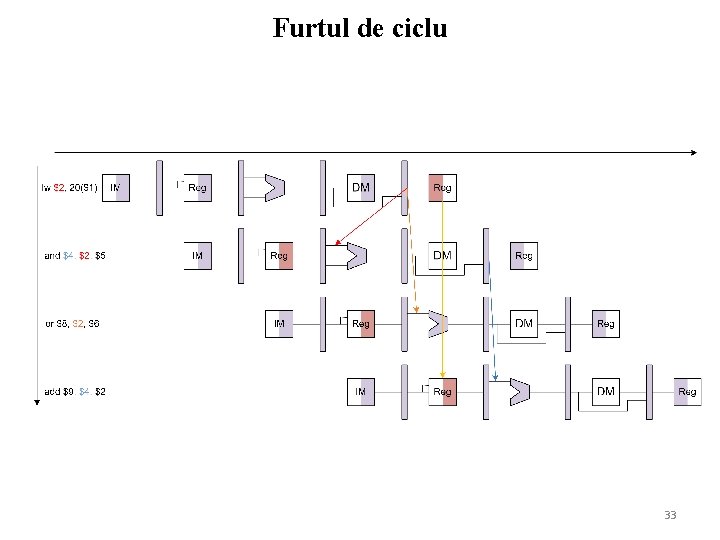

Furtul de ciclu 33

Furtul de ciclu 34

Furtul de ciclu 35

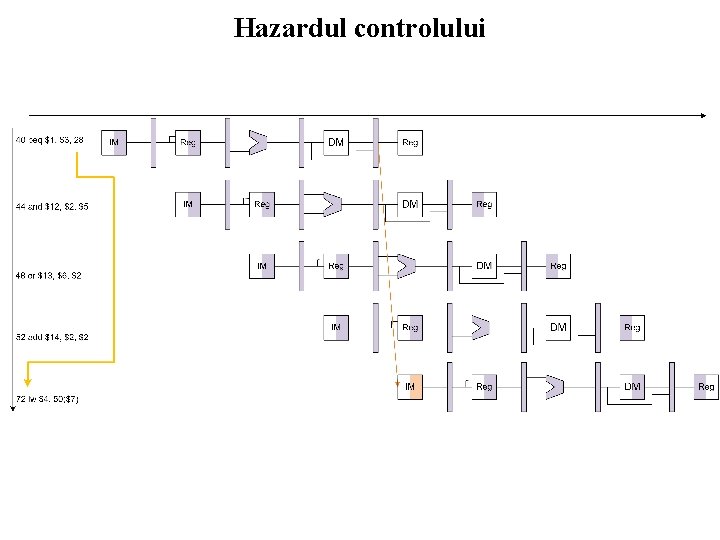

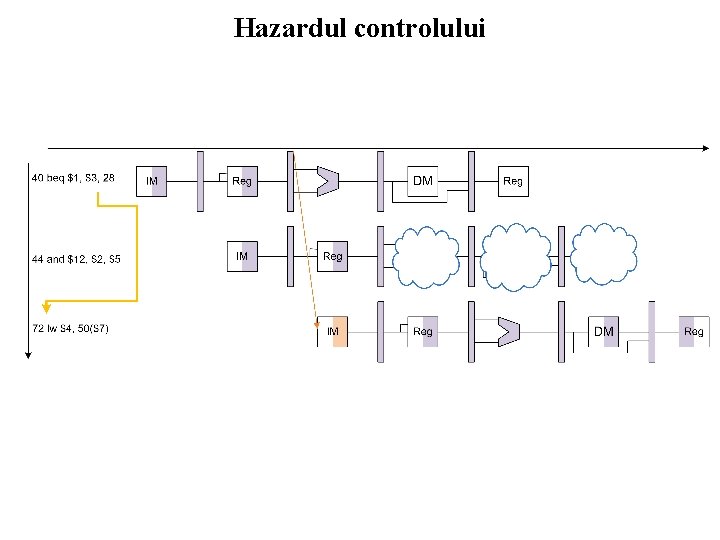

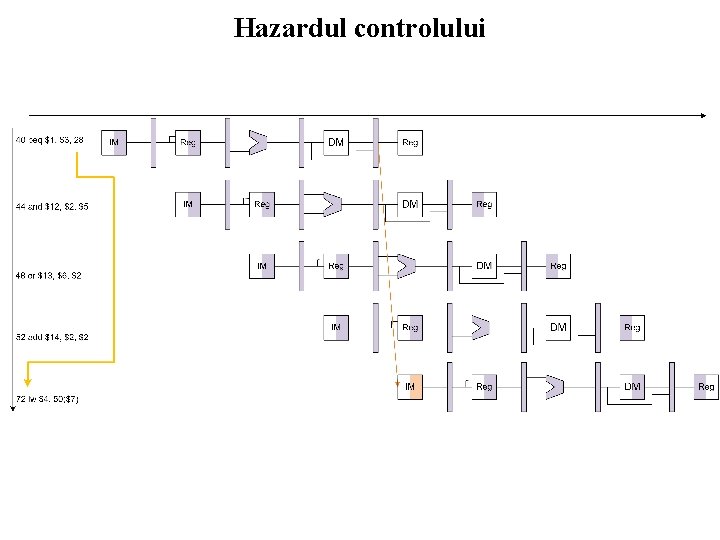

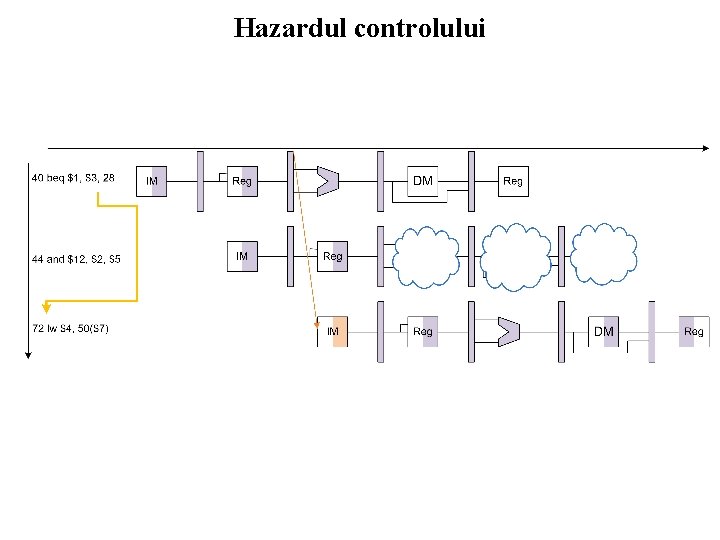

Hazardul controlului

Hazardul controlului

b e r t n Î ? i r ă 38