Stratix 10 External Memory Interface Board Guidelines Quartus

Stratix 10 External Memory Interface Board Guidelines Quartus Prime Software v 17. 0 ir 3 Stratix 10 EMIF Board Guidelines are preliminary and subject to change

Introduction § This slide deck covers the following topics: – Layout recommendations – Signal matching/skew § For more details regarding board design, refer to the appropriate Board Design Guidelines section in the External Memory Interface Handbook – DDR 2, DDR 3, and DDR 4 SDRAM Board Design Guidelines – LPDDR 2 and LPDDR 3 SDRAM Board Design Guidelines – RLDRAM II and RLDRAM 3 Board Design Guidelines – QDR II and QDR-IV SRAM Board Design Guidelines *EMIF = External Memory Interface 2

Software Requirements § Quartus Prime Software v 17. 0 ir 3 3

Disclaimer § This slide deck covers layout guidance for DDR 3 and DDR 4 – This document only covers key board layout requirements – Please check with your DRAM vendor for any additional layout guidance § Length matching guidelines are recommendations – Should not be considered as hard guidelines § Board-level simulation must be performed to ensure there are no signal integrity or ISI/Crosstalk related issues § To ensure there are no timing violations – Enter accurate information in the Board tab of the EMIF IP GUI § For more details on simulation guidance refer to this wiki page 4

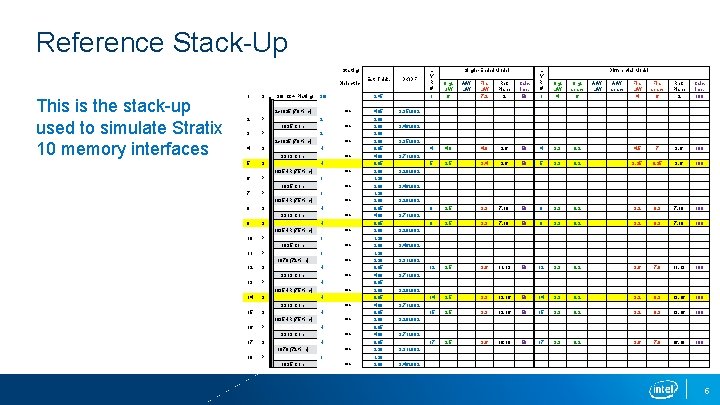

Reference Stack-Up Starting Dielectric This is the stack-up used to simulate Stratix 10 memory interfaces 1 S 2 P 3/8 oz + Platting 3/8 2 x 1025 (70% rc) => 1035 Core 4 => 2 S => H 3313 Core 5 S => H 1035 HR (75% rc) 6 P 7 P 8 S => 1 1035 Core => 1 1035 HR (75% rc) => H 3313 Core 9 S 10 P 11 P 12 S => H 1035 HR (75% rc) => 1 1035 Core => 1 1078 (72% rc) => H 3313 Core 13 P 14 S => H 1035 HR (75% rc) => H 3313 Core 15 S => H 1035 HR (75% rc) 16 P 17 S => H 3313 Core => H 1078 (72% rc) 18 P => 1 1035 Core DK/DF 2. 45 2 2 x 1035 (70% rc) Est. Thick. => 4. 05 2. 60 2. 00 2. 60 3. 60 0. 65 4. 00 0. 65 2. 00 1. 30 2. 00 0. 65 4. 00 0. 65 2. 00 1. 30 3. 20 0. 65 4. 00 0. 65 2. 00 0. 65 4. 00 0. 65 3. 20 1. 30 2. 00 L Y R # Single-Ended Model 1 Org. L/W 6 4 A/W L/W Fin. L/W 7. 2 Ref. Plane 2 Calc. Imp. 50 4. 8 3, 6 5 3. 4 8 3. 5 9 L Y R # Differential Model 1 Org. L/W 4 Org. space 6 50 4 3. 3 3, 6 50 5 3. 3 7, 10 50 3. 5 3. 3 7, 10 12 3. 5 3. 6 14 3. 5 15 17 A/W L/W A/W space Fin. L/W 4 Fin. space 6 Ref. Plane 2 Calc. Imp. 100 8. 2 4. 5 7 3, 6 100 3. 3 8. 2 3. 25 8. 25 3, 6 100 8 3. 3 8. 2 3. 2 8. 3 7, 10 100 50 9 3. 3 8. 2 3. 2 8. 3 7, 10 100 11, 13 50 12 3. 3 8. 2 3. 6 7. 9 11, 13 100 3. 3 13, 16 50 14 3. 3 8. 2 3. 2 8. 3 13, 16 100 3. 5 3. 3 13, 16 50 15 3. 3 8. 2 3. 2 8. 3 13, 16 100 3. 5 3. 6 16, 18 50 17 3. 3 8. 2 3. 6 7. 9 16, 18 100 3. 35/. 002 3. 46/. 002 3. 35/. 002 3. 71/. 002 3. 28/. 002 3. 46/. 002 3. 28/. 002 3. 71/. 002 3. 28/. 002 3. 46/. 002 3. 31/. 002 3. 71/. 002 3. 28/. 002 3. 71/. 002 3. 31/. 002 3. 46/. 002 5

General Board Guidelines The following slides cover board guidelines for DDR 3 and DDR 4 protocols § Trace impedance plays an important role in signal integrity § Based on the stack-up (mentioned on the previous slide), these impedances are recommended: – 45Ω for single-ended traces – 90Ω for differential traces § To minimize PCB layer propagation variance, it is recommended to route signals from the same net group on the same layer – Use 45° angles (not 90° corners) – Disallow critical signals across split planes – Route over appropriate VCC and GND planes – Keep signal routing layers close to GND and power planes 6

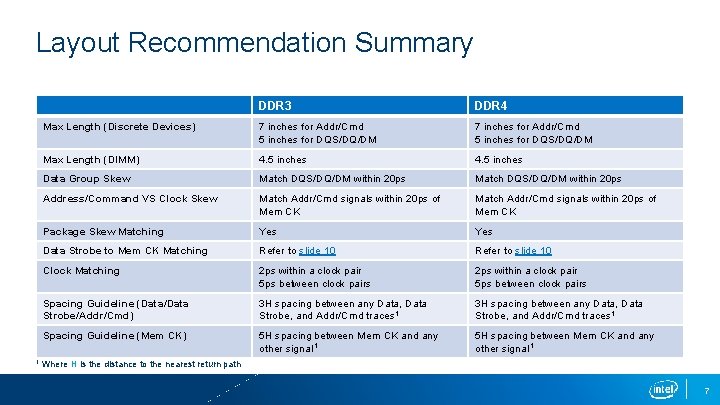

Layout Recommendation Summary 1 DDR 3 DDR 4 Max Length (Discrete Devices) 7 inches for Addr/Cmd 5 inches for DQS/DQ/DM Max Length (DIMM) 4. 5 inches Data Group Skew Match DQS/DQ/DM within 20 ps Address/Command VS Clock Skew Match Addr/Cmd signals within 20 ps of Mem CK Package Skew Matching Yes Data Strobe to Mem CK Matching Refer to slide 10 Clock Matching 2 ps within a clock pair 5 ps between clock pairs Spacing Guideline (Data/Data Strobe/Addr/Cmd) 3 H spacing between any Data, Data Strobe, and Addr/Cmd traces 1 Spacing Guideline (Mem CK) 5 H spacing between Mem CK and any other signal 1 Where H is the distance to the nearest return path 7

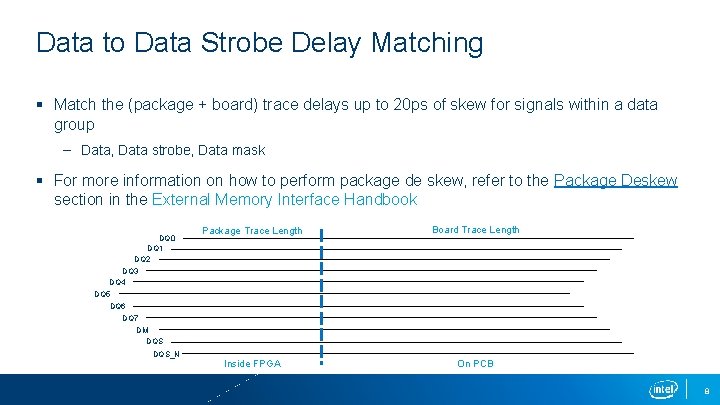

Data to Data Strobe Delay Matching § Match the (package + board) trace delays up to 20 ps of skew for signals within a data group – Data, Data strobe, Data mask § For more information on how to perform package de skew, refer to the Package Deskew section in the External Memory Interface Handbook DQ 0 DQ 1 DQ 2 Package Trace Length Board Trace Length Inside FPGA On PCB DQ 3 DQ 4 DQ 5 DQ 6 DQ 7 DM DQS_N 8

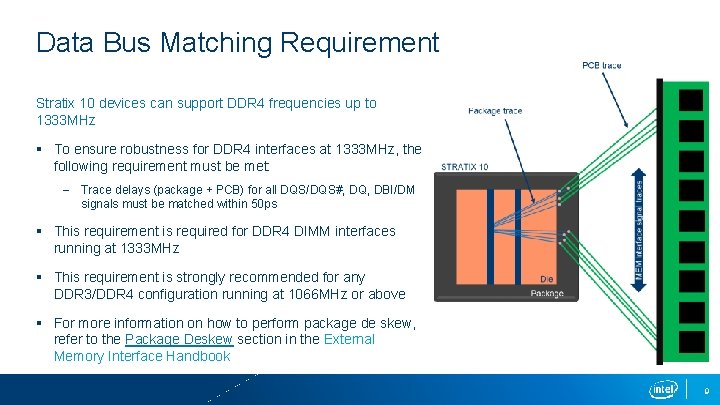

Data Bus Matching Requirement Stratix 10 devices can support DDR 4 frequencies up to 1333 MHz § To ensure robustness for DDR 4 interfaces at 1333 MHz, the following requirement must be met: – Trace delays (package + PCB) for all DQS/DQS#, DQ, DBI/DM signals must be matched within 50 ps § This requirement is required for DDR 4 DIMM interfaces running at 1333 MHz § This requirement is strongly recommended for any DDR 3/DDR 4 configuration running at 1066 MHz or above § For more information on how to perform package de skew, refer to the Package Deskew section in the External Memory Interface Handbook 9

Address/Command/Control Skew The following slides go into detail explaining board guidelines in reference to Address/Command/Control signals § All Addr/Cmd/Control signals should match up to ± 20 ps compared to the Mem CK trace § For example: If Mem CK trace delay is 500 ps – Allowed range for Addr/Cmd/Control signals is 480 ps to 520 ps § For discrete components: – Make sure ± 20 ps recommendation is met for each component in fly-by chain § For DIMMs: – Make sure the ± 20 ps recommendation is met at each DIMM connector – Applicable to single and multiple DIMM configurations 10

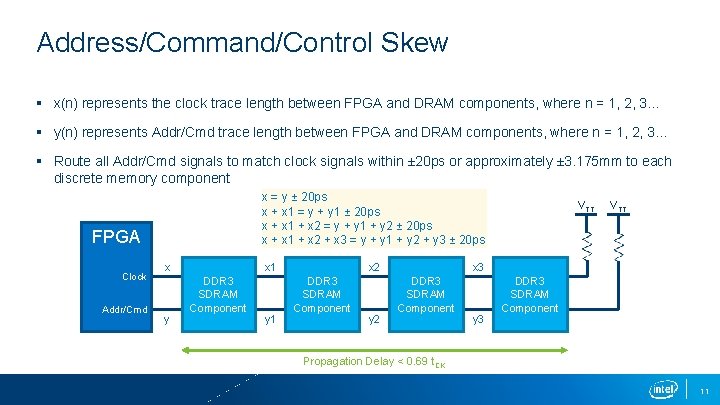

Address/Command/Control Skew § x(n) represents the clock trace length between FPGA and DRAM components, where n = 1, 2, 3… § y(n) represents Addr/Cmd trace length between FPGA and DRAM components, where n = 1, 2, 3… § Route all Addr/Cmd signals to match clock signals within ± 20 ps or approximately ± 3. 175 mm to each discrete memory component x = y ± 20 ps x + x 1 = y + y 1 ± 20 ps x + x 1 + x 2 = y + y 1 + y 2 ± 20 ps x + x 1 + x 2 + x 3 = y + y 1 + y 2 + y 3 ± 20 ps FPGA Clock Addr/Cmd x 1 x y DDR 3 SDRAM Component y 1 x 2 DDR 3 SDRAM Component y 2 VTT x 3 DDR 3 SDRAM Component y 3 DDR 3 SDRAM Component Propagation Delay < 0. 69 t. CK 11

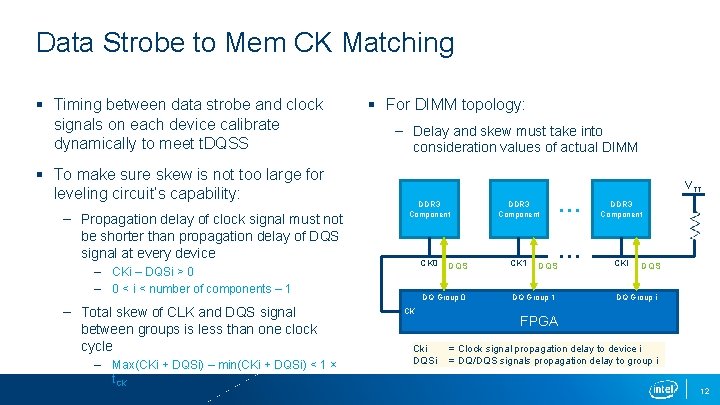

Data Strobe to Mem CK Matching § Timing between data strobe and clock signals on each device calibrate dynamically to meet t. DQSS § To make sure skew is not too large for leveling circuit’s capability: – Propagation delay of clock signal must not be shorter than propagation delay of DQS signal at every device § For DIMM topology: – Delay and skew must take into consideration values of actual DIMM DDR 3 Component CK 0 CK 1 – CKi – DQSi > 0 – 0 < i < number of components – 1 – Total skew of CLK and DQS signal between groups is less than one clock cycle – Max(CKi + DQSi) – min(CKi + DQSi) < 1 × t. CK DQS DQ Group 0 CK Cki DQS DQ Group 1 … … VTT DDR 3 Component CKi DQS DQ Group i FPGA = Clock signal propagation delay to device i = DQ/DQS signals propagation delay to group i 12

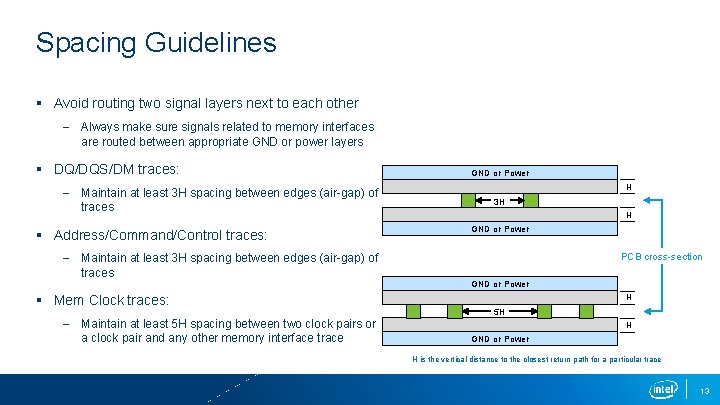

Spacing Guidelines § Avoid routing two signal layers next to each other – Always make sure signals related to memory interfaces are routed between appropriate GND or power layers § DQ/DQS/DM traces: – Maintain at least 3 H spacing between edges (air-gap) of traces § Address/Command/Control traces: – Maintain at least 3 H spacing between edges (air-gap) of traces § Mem Clock traces: – Maintain at least 5 H spacing between two clock pairs or a clock pair and any other memory interface trace GND or Power H 3 H H GND or Power PCB cross-section GND or Power H 5 H H GND or Power H is the vertical distance to the closest return path for a particular trace 13

- Slides: 14