Strained Si Patent Survey Buo Wen Chen Department

Strained Si Patent Survey Buo - Wen Chen Department of Electrical Engineering and Graduate Institute of Electronics Engineering National Taiwan University, Taipei, Taiwan, R. O. C. Department of Electrical Engineering, National Taiwan University

專利分析 專利地圖分析 專利內容與用途分析 重要專利摘要 Department of Electrical Engineering, National Taiwan University

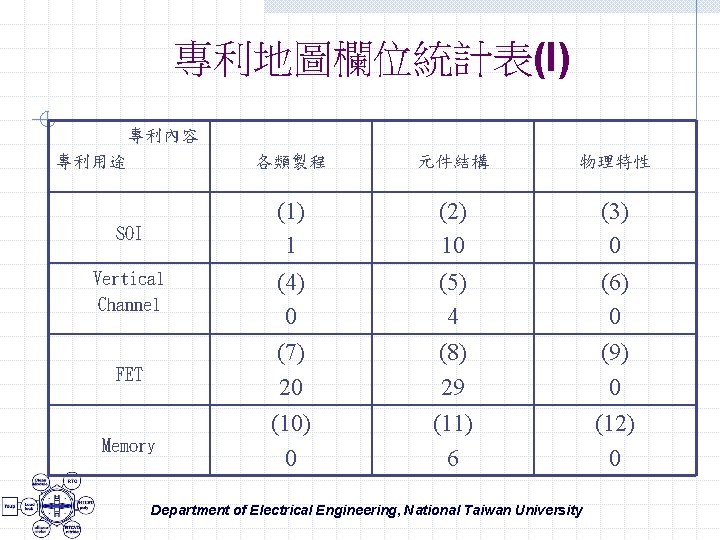

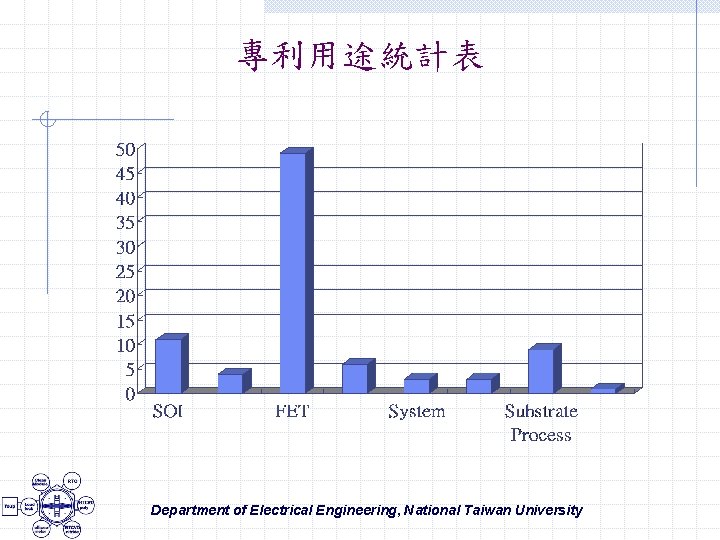

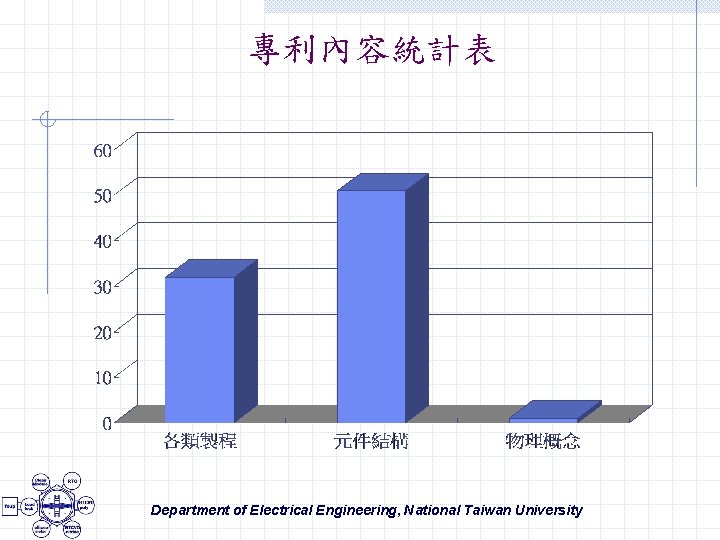

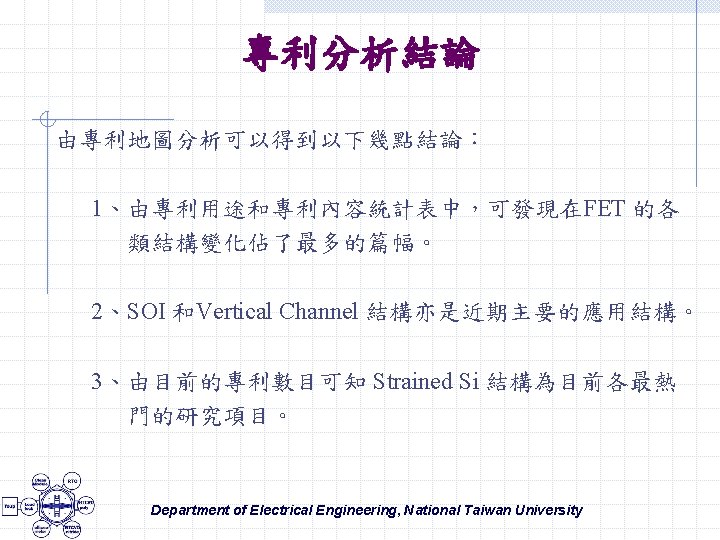

專利地圖欄位統計表(I) 專利內容 專利用途 各類製程 元件結構 物理特性 SOI (1) 1 (2) 10 (3) 0 Vertical Channel (4) 0 (5) 4 (6) 0 FET (7) 20 (8) 29 (9) 0 Memory (10) 0 (11) 6 (12) 0 Department of Electrical Engineering, National Taiwan University

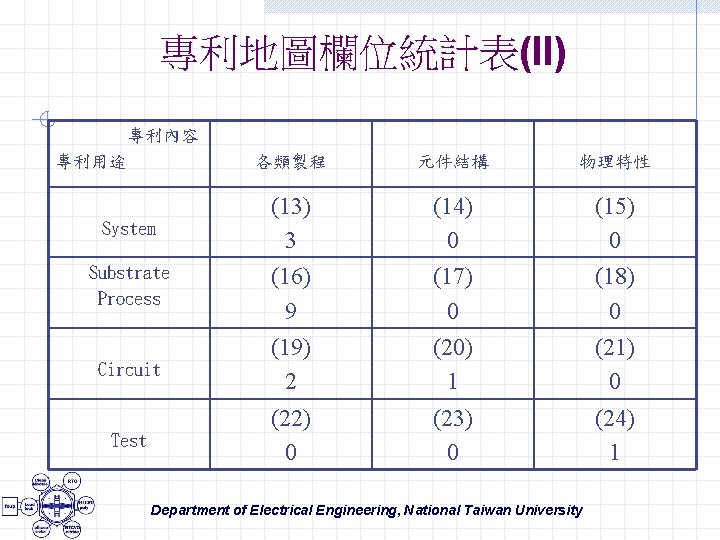

專利地圖欄位統計表(II) 專利內容 專利用途 System Substrate Process Circuit Test 各類製程 元件結構 物理特性 (13) 3 (14) 0 (15) 0 (16) 9 (19) 2 (17) 0 (20) 1 (18) 0 (21) 0 (22) 0 (23) 0 (24) 1 Department of Electrical Engineering, National Taiwan University

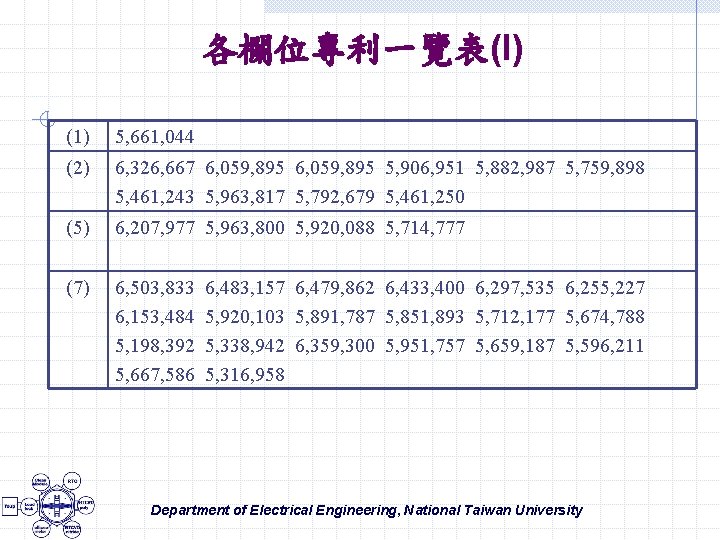

各欄位專利一覽表(I) (1) 5, 661, 044 (2) 6, 326, 667 6, 059, 895 5, 906, 951 5, 882, 987 5, 759, 898 5, 461, 243 5, 963, 817 5, 792, 679 5, 461, 250 (5) 6, 207, 977 5, 963, 800 5, 920, 088 5, 714, 777 (7) 6, 503, 833 6, 153, 484 5, 198, 392 5, 667, 586 6, 483, 157 6, 479, 862 6, 433, 400 6, 297, 535 6, 255, 227 5, 920, 103 5, 891, 787 5, 851, 893 5, 712, 177 5, 674, 788 5, 338, 942 6, 359, 300 5, 951, 757 5, 659, 187 5, 596, 211 5, 316, 958 Department of Electrical Engineering, National Taiwan University

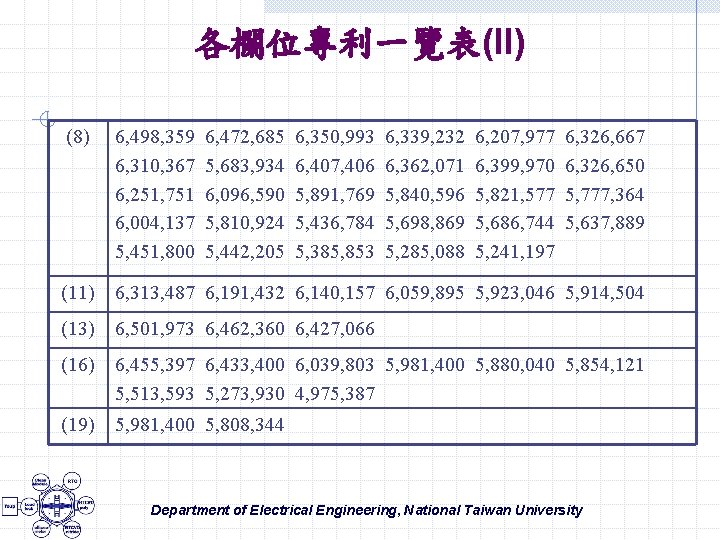

各欄位專利一覽表(II) (8) 6, 498, 359 6, 310, 367 6, 251, 751 6, 004, 137 5, 451, 800 6, 472, 685 5, 683, 934 6, 096, 590 5, 810, 924 5, 442, 205 6, 350, 993 6, 407, 406 5, 891, 769 5, 436, 784 5, 385, 853 6, 339, 232 6, 362, 071 5, 840, 596 5, 698, 869 5, 285, 088 6, 207, 977 6, 399, 970 5, 821, 577 5, 686, 744 5, 241, 197 6, 326, 667 6, 326, 650 5, 777, 364 5, 637, 889 (11) 6, 313, 487 6, 191, 432 6, 140, 157 6, 059, 895 5, 923, 046 5, 914, 504 (13) 6, 501, 973 6, 462, 360 6, 427, 066 (16) 6, 455, 397 6, 433, 400 6, 039, 803 5, 981, 400 5, 880, 040 5, 854, 121 5, 513, 593 5, 273, 930 4, 975, 387 (19) 5, 981, 400 5, 808, 344 Department of Electrical Engineering, National Taiwan University

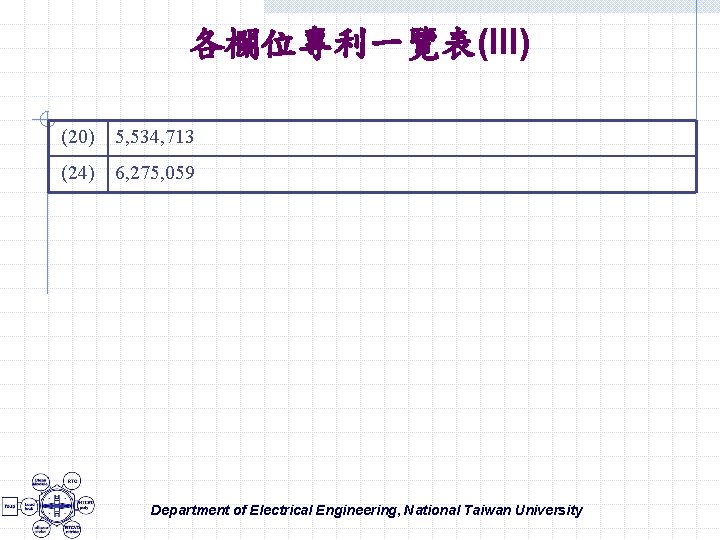

各欄位專利一覽表(III) (20) 5, 534, 713 (24) 6, 275, 059 Department of Electrical Engineering, National Taiwan University

專利用途統計表 Department of Electrical Engineering, National Taiwan University

專利內容統計表 Department of Electrical Engineering, National Taiwan University

重要專利摘要 Department of Electrical Engineering, National Taiwan University

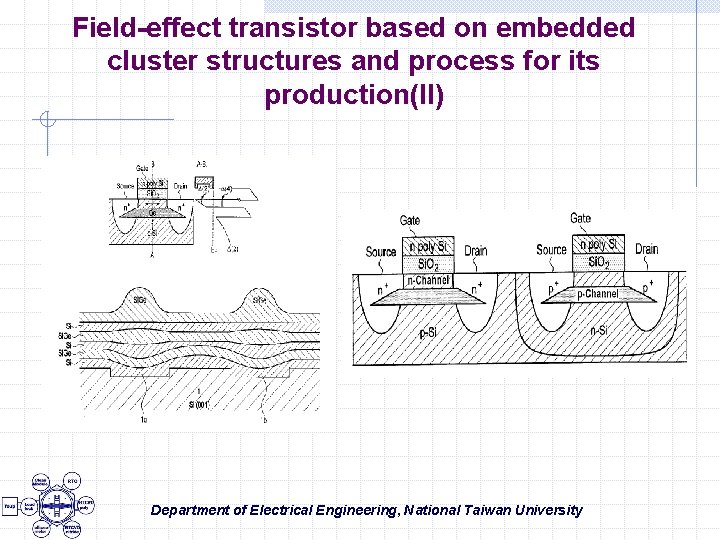

Field-effect transistor based on embedded cluster structures and process for its production(I) Inventors: Schmidt; Oliver G. (Stuttgart, DE); Eberl; Karl (Weil der Stadt, DE) Assignee:International Business Machines Corporation (Armonk, NY) Patent No. : 6, 498, 359 Date of Patent:December 24, 2002 Abstract: In field-effect transistors, semiconductor clusters, which can extend from the source region to the drain region and which can be implemented in two ways, are embedded in one or a plurality of layers. In a first embodiment, the semiconductor material of the adjacent channel region can be strained by the clusters and the effective mass can thus be reduced by altering the energy band structure and the charge carrier mobility can be increased. In a second embodiment, the clusters themselves can be used as a canal region. These two embodiments can also appear in mixed forms. The invention can be applied to the Si material system with Si. Ge clusters or to the Ga. As material system with In. Ga. As clusters or to other material systems. Department of Electrical Engineering, National Taiwan University

Field-effect transistor based on embedded cluster structures and process for its production(II) Department of Electrical Engineering, National Taiwan University

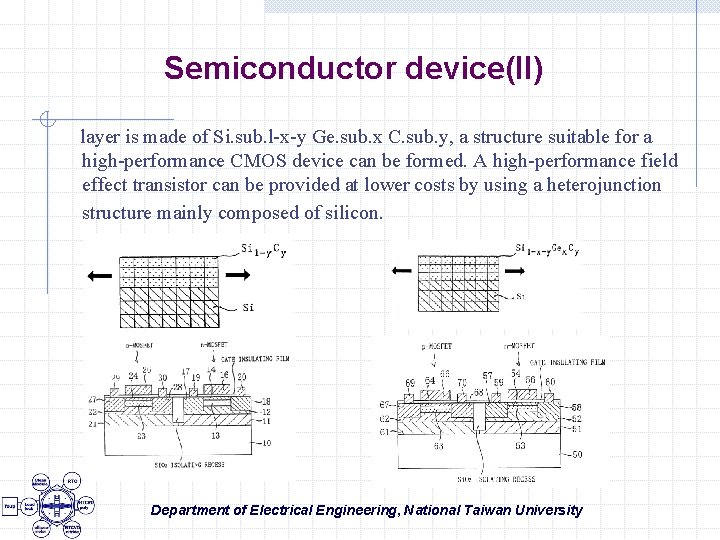

Semiconductor device(I) Inventors: Takagi; Takeshi (Kyoto, JP) Assignee:Matsushita Electric Industrial Co. , Ltd. (Osaka, JP) Patent No. : 6, 472, 685 Date of Patent:October 29, 2002 Abstract: A first silicon layer (Si layer), a second silicon layer (Si. sub. 1 C. sub. y layer) containing carbon and a third silicon layer not containing carbon are stacked in this order on a silicon substrate. Since the lattice constant of the Si. sub. 1 -y C. sub. y layer is smaller than that of the Si layer, the conduction band the valence band of the second silicon layer receive a tensile strain to be split. Electrons having a smaller effective mass, which have been induced by an electric field applied to a gate electrode, are confined in the second silicon layer, and move in the channel direction. Thus, an n-MOSFET having extremely high mobility can be obtained. Furthermore, if the second silicon Department of Electrical Engineering, National Taiwan University

Semiconductor device(II) layer is made of Si. sub. l-x-y Ge. sub. x C. sub. y, a structure suitable for a high-performance CMOS device can be formed. A high-performance field effect transistor can be provided at lower costs by using a heterojunction structure mainly composed of silicon. Department of Electrical Engineering, National Taiwan University

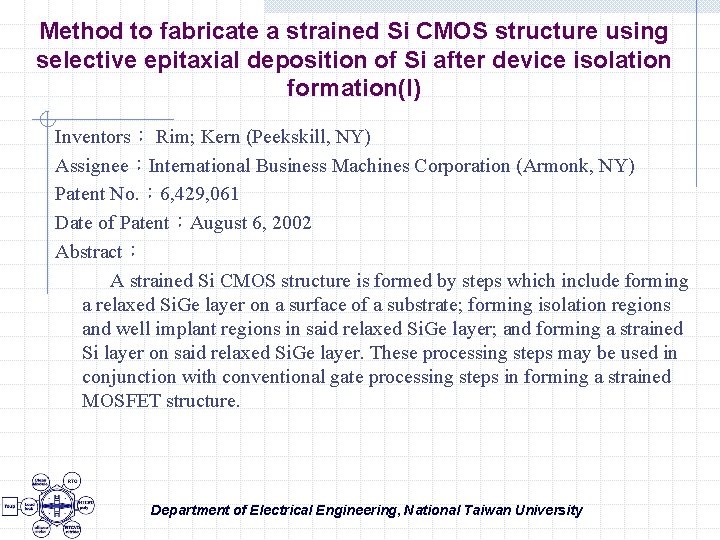

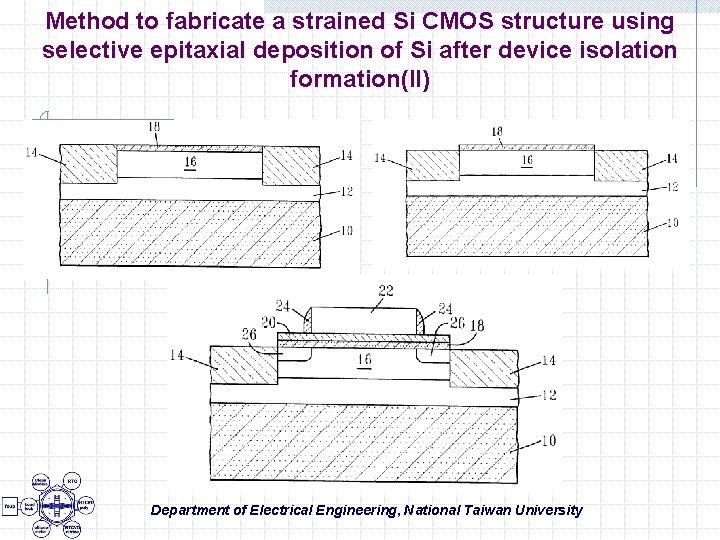

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation(I) Inventors: Rim; Kern (Peekskill, NY) Assignee:International Business Machines Corporation (Armonk, NY) Patent No. : 6, 429, 061 Date of Patent:August 6, 2002 Abstract: A strained Si CMOS structure is formed by steps which include forming a relaxed Si. Ge layer on a surface of a substrate; forming isolation regions and well implant regions in said relaxed Si. Ge layer; and forming a strained Si layer on said relaxed Si. Ge layer. These processing steps may be used in conjunction with conventional gate processing steps in forming a strained MOSFET structure. Department of Electrical Engineering, National Taiwan University

Method to fabricate a strained Si CMOS structure using selective epitaxial deposition of Si after device isolation formation(II) Department of Electrical Engineering, National Taiwan University

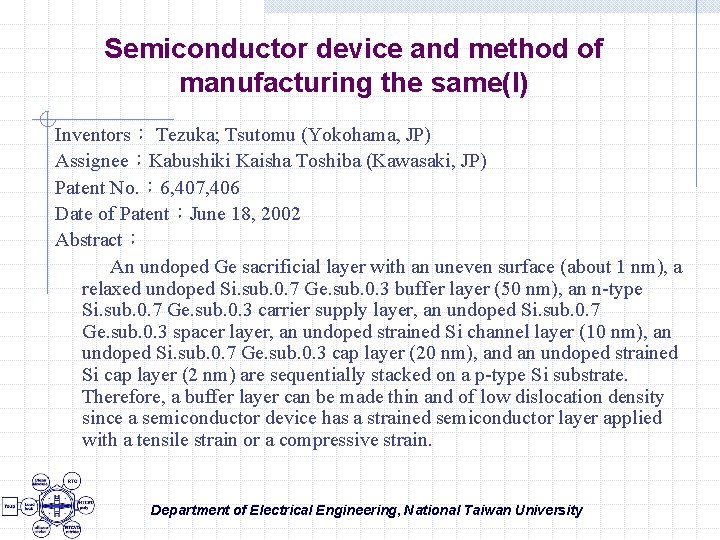

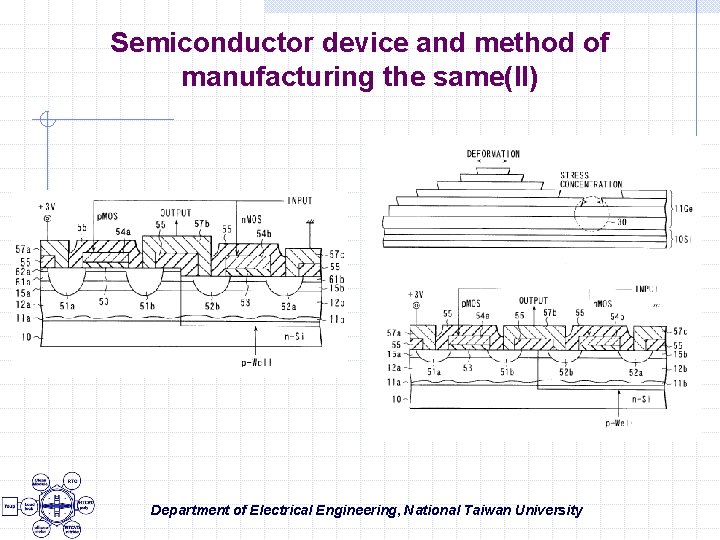

Semiconductor device and method of manufacturing the same(I) Inventors: Tezuka; Tsutomu (Yokohama, JP) Assignee:Kabushiki Kaisha Toshiba (Kawasaki, JP) Patent No. : 6, 407, 406 Date of Patent:June 18, 2002 Abstract: An undoped Ge sacrificial layer with an uneven surface (about 1 nm), a relaxed undoped Si. sub. 0. 7 Ge. sub. 0. 3 buffer layer (50 nm), an n-type Si. sub. 0. 7 Ge. sub. 0. 3 carrier supply layer, an undoped Si. sub. 0. 7 Ge. sub. 0. 3 spacer layer, an undoped strained Si channel layer (10 nm), an undoped Si. sub. 0. 7 Ge. sub. 0. 3 cap layer (20 nm), and an undoped strained Si cap layer (2 nm) are sequentially stacked on a p-type Si substrate. Therefore, a buffer layer can be made thin and of low dislocation density since a semiconductor device has a strained semiconductor layer applied with a tensile strain or a compressive strain. Department of Electrical Engineering, National Taiwan University

Semiconductor device and method of manufacturing the same(II) Department of Electrical Engineering, National Taiwan University

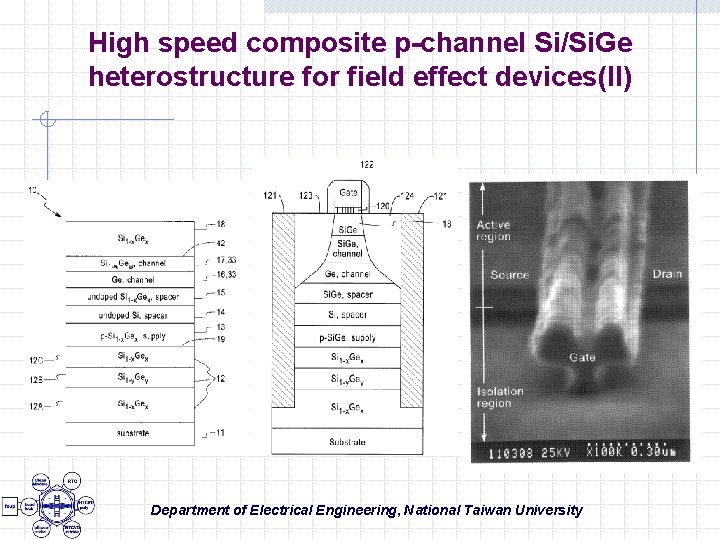

High speed composite p-channel Si/Si. Ge heterostructure for field effect devices(I) Inventors: Chu; Jack Oon (Manhasset Hills, NY) et al. Assignee:International Business Machines Corporation (Armonk, NY) Patent No. : 6, 350, 993 Date of Patent:February 26, 2002 Abstract: A method and a layered heterostructure forming p-channel field effect transistors is described incorporating a plurality of semiconductor layers on a semiconductor substrate, a composite channel structure of a first epitaxial Ge layer and a second compressively strained Si. Ge layer having a higher barrier or a deeper confining quantum well and having extremely high hole mobility. The invention overcomes the problem of a limited hole mobility for a p-channel device with only a single compressively strained Si. Ge channel layer. Department of Electrical Engineering, National Taiwan University

High speed composite p-channel Si/Si. Ge heterostructure for field effect devices(II) Department of Electrical Engineering, National Taiwan University

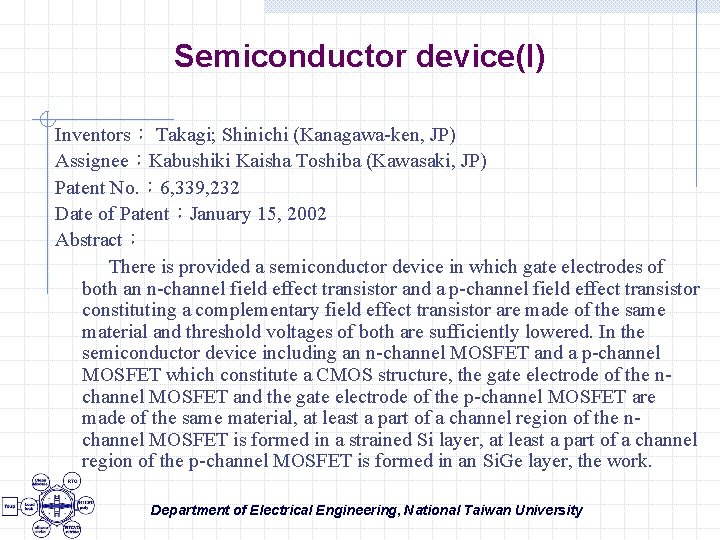

Semiconductor device(I) Inventors: Takagi; Shinichi (Kanagawa-ken, JP) Assignee:Kabushiki Kaisha Toshiba (Kawasaki, JP) Patent No. : 6, 339, 232 Date of Patent:January 15, 2002 Abstract: There is provided a semiconductor device in which gate electrodes of both an n-channel field effect transistor and a p-channel field effect transistor constituting a complementary field effect transistor are made of the same material and threshold voltages of both are sufficiently lowered. In the semiconductor device including an n-channel MOSFET and a p-channel MOSFET which constitute a CMOS structure, the gate electrode of the nchannel MOSFET and the gate electrode of the p-channel MOSFET are made of the same material, at least a part of a channel region of the nchannel MOSFET is formed in a strained Si layer, at least a part of a channel region of the p-channel MOSFET is formed in an Si. Ge layer, the work. Department of Electrical Engineering, National Taiwan University

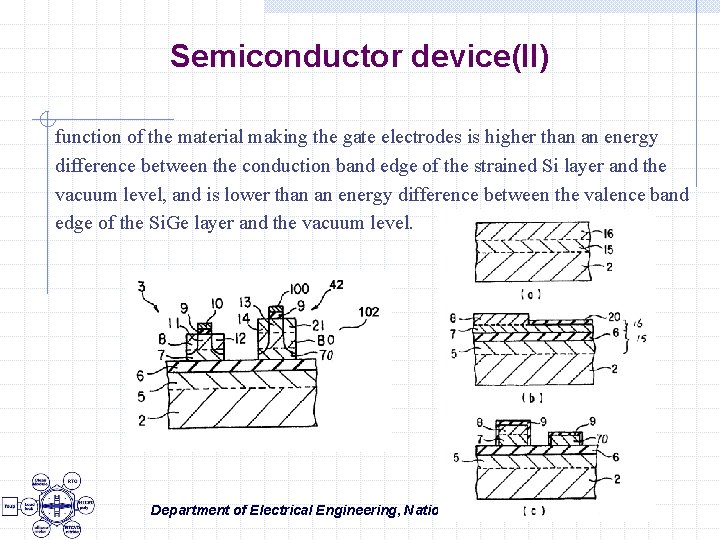

Semiconductor device(II) function of the material making the gate electrodes is higher than an energy difference between the conduction band edge of the strained Si layer and the vacuum level, and is lower than an energy difference between the valence band edge of the Si. Ge layer and the vacuum level. Department of Electrical Engineering, National Taiwan University

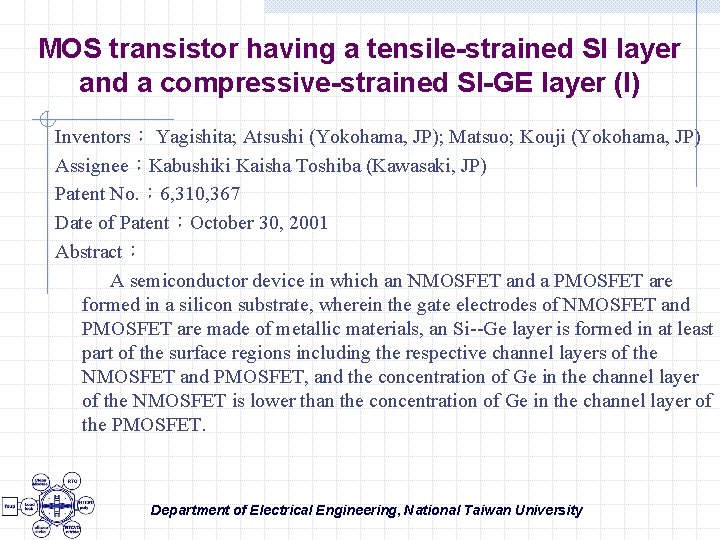

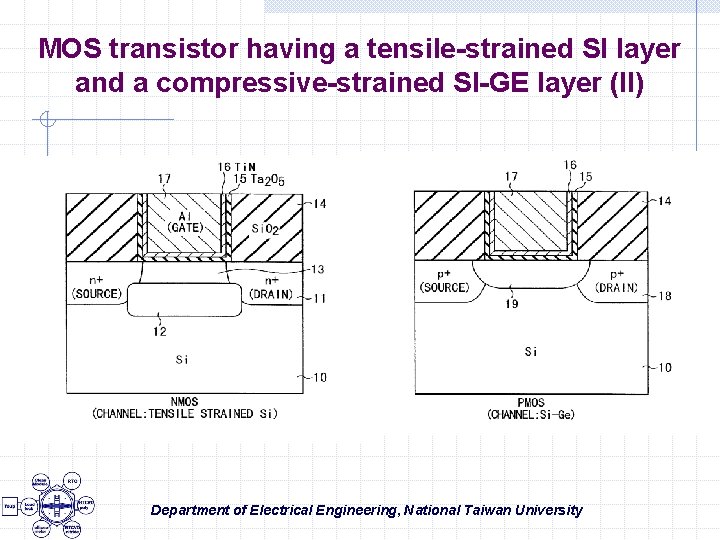

MOS transistor having a tensile-strained SI layer and a compressive-strained SI-GE layer (I) Inventors: Yagishita; Atsushi (Yokohama, JP); Matsuo; Kouji (Yokohama, JP) Assignee:Kabushiki Kaisha Toshiba (Kawasaki, JP) Patent No. : 6, 310, 367 Date of Patent:October 30, 2001 Abstract: A semiconductor device in which an NMOSFET and a PMOSFET are formed in a silicon substrate, wherein the gate electrodes of NMOSFET and PMOSFET are made of metallic materials, an Si--Ge layer is formed in at least part of the surface regions including the respective channel layers of the NMOSFET and PMOSFET, and the concentration of Ge in the channel layer of the NMOSFET is lower than the concentration of Ge in the channel layer of the PMOSFET. Department of Electrical Engineering, National Taiwan University

MOS transistor having a tensile-strained SI layer and a compressive-strained SI-GE layer (II) Department of Electrical Engineering, National Taiwan University

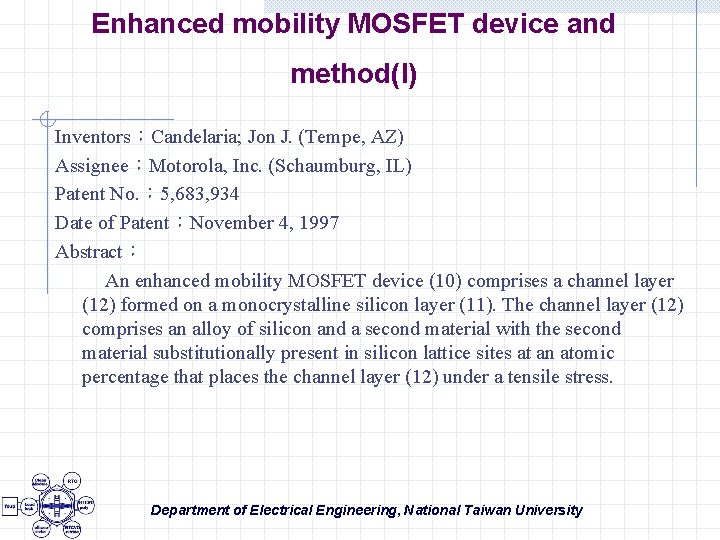

Enhanced mobility MOSFET device and method(I) Inventors:Candelaria; Jon J. (Tempe, AZ) Assignee:Motorola, Inc. (Schaumburg, IL) Patent No. : 5, 683, 934 Date of Patent:November 4, 1997 Abstract: An enhanced mobility MOSFET device (10) comprises a channel layer (12) formed on a monocrystalline silicon layer (11). The channel layer (12) comprises an alloy of silicon and a second material with the second material substitutionally present in silicon lattice sites at an atomic percentage that places the channel layer (12) under a tensile stress. Department of Electrical Engineering, National Taiwan University

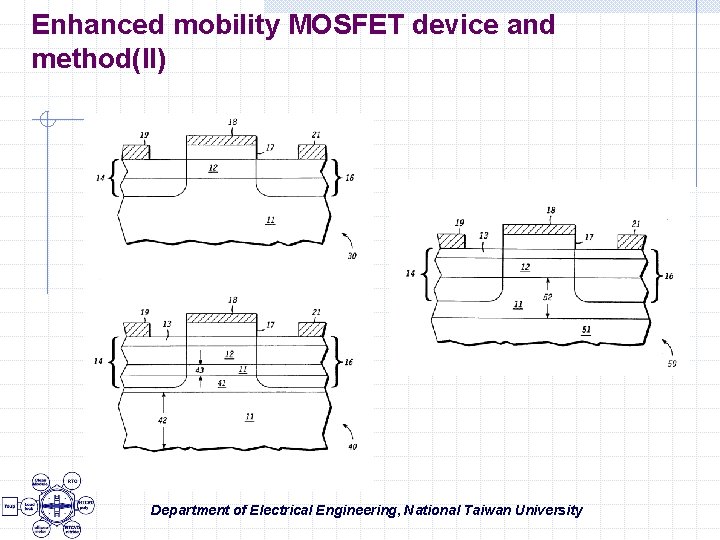

Enhanced mobility MOSFET device and method(II) Department of Electrical Engineering, National Taiwan University

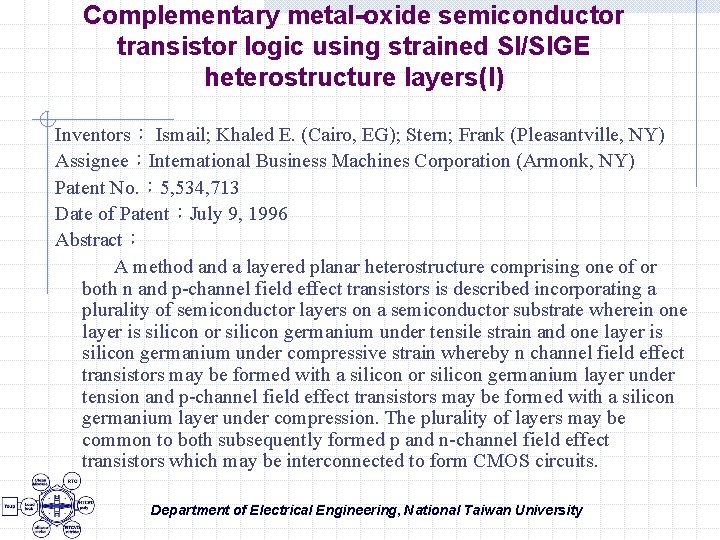

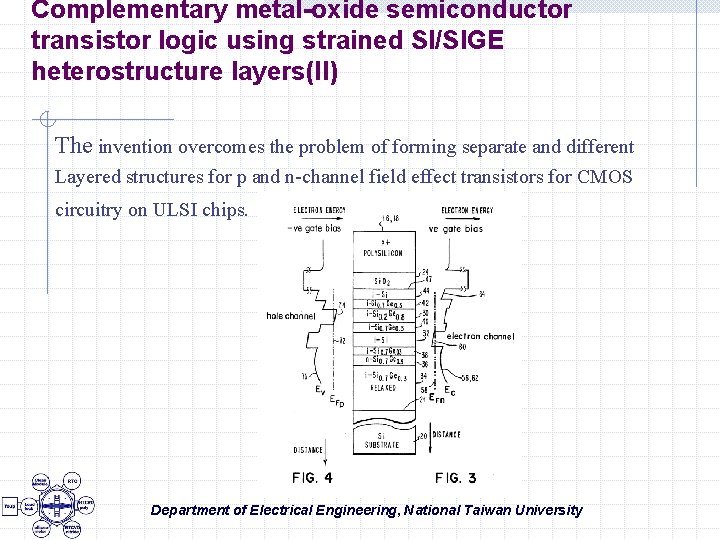

Complementary metal-oxide semiconductor transistor logic using strained SI/SIGE heterostructure layers(I) Inventors: Ismail; Khaled E. (Cairo, EG); Stern; Frank (Pleasantville, NY) Assignee:International Business Machines Corporation (Armonk, NY) Patent No. : 5, 534, 713 Date of Patent:July 9, 1996 Abstract: A method and a layered planar heterostructure comprising one of or both n and p-channel field effect transistors is described incorporating a plurality of semiconductor layers on a semiconductor substrate wherein one layer is silicon or silicon germanium under tensile strain and one layer is silicon germanium under compressive strain whereby n channel field effect transistors may be formed with a silicon or silicon germanium layer under tension and p-channel field effect transistors may be formed with a silicon germanium layer under compression. The plurality of layers may be common to both subsequently formed p and n-channel field effect transistors which may be interconnected to form CMOS circuits. Department of Electrical Engineering, National Taiwan University

Complementary metal-oxide semiconductor transistor logic using strained SI/SIGE heterostructure layers(II) The invention overcomes the problem of forming separate and different Layered structures for p and n-channel field effect transistors for CMOS circuitry on ULSI chips. Department of Electrical Engineering, National Taiwan University

報告結束~~THANK YOU! Department of Electrical Engineering, National Taiwan University

- Slides: 30