Status Report on ADC developments LPC ClermontFerrand Laurent

- Slides: 25

Status Report on ADC developments @ LPC Clermont-Ferrand Laurent ROYER, Samuel MANEN Royer @ Calice/Eudet electronic meeting London 2008 1

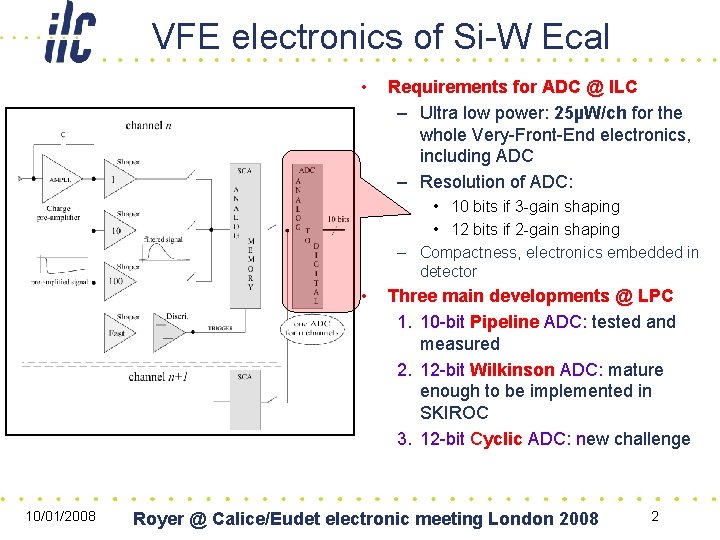

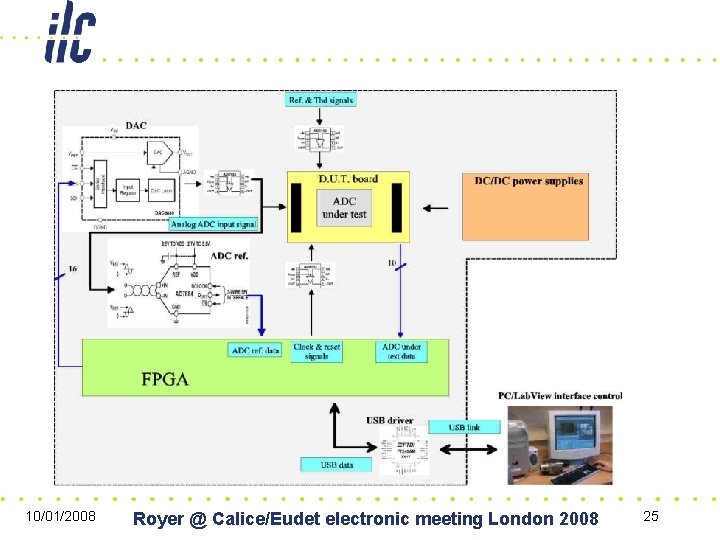

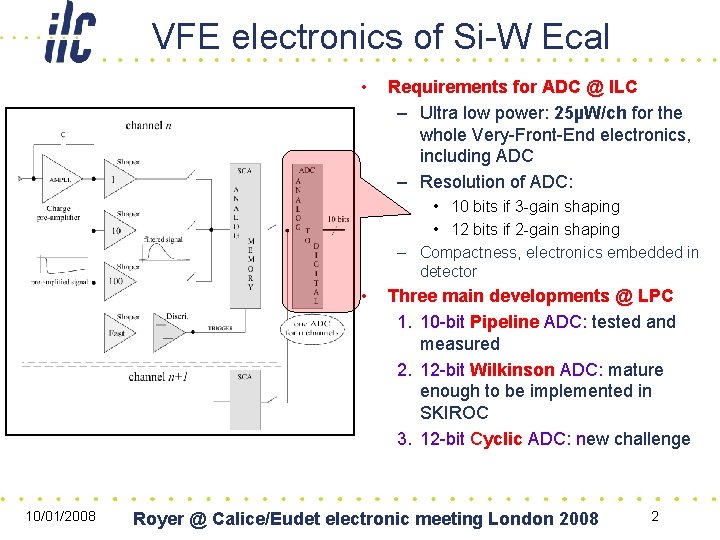

VFE electronics of Si-W Ecal • Requirements for ADC @ ILC – Ultra low power: 25µW/ch for the whole Very-Front-End electronics, including ADC – Resolution of ADC: • 10 bits if 3 -gain shaping • 12 bits if 2 -gain shaping – Compactness, electronics embedded in detector • 10/01/2008 Three main developments @ LPC 1. 10 -bit Pipeline ADC: tested and measured 2. 12 -bit Wilkinson ADC: mature enough to be implemented in SKIROC 3. 12 -bit Cyclic ADC: new challenge Royer @ Calice/Eudet electronic meeting London 2008 2

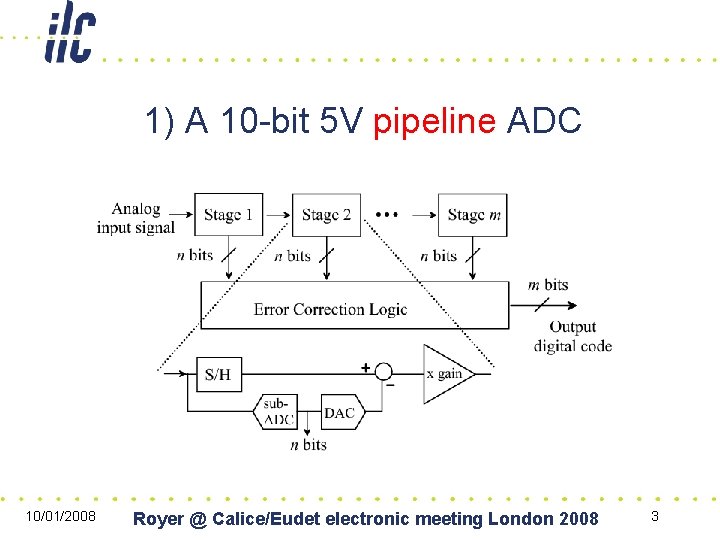

1) A 10 -bit 5 V pipeline ADC 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 3

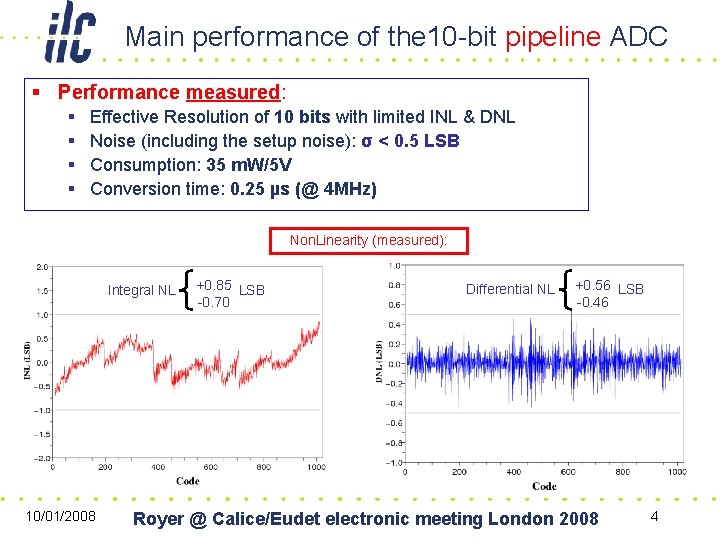

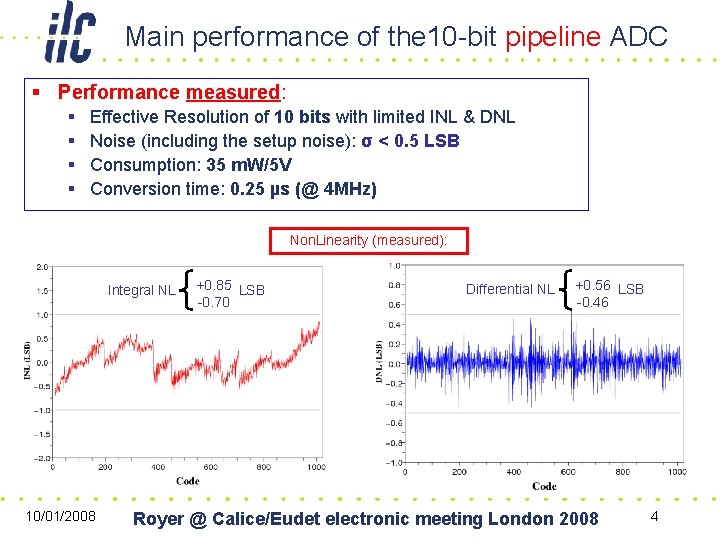

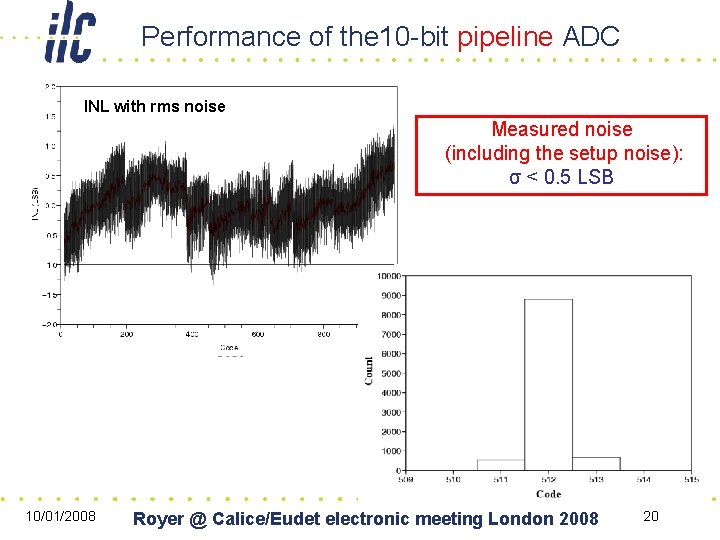

Main performance of the 10 -bit pipeline ADC § Performance measured: § § Effective Resolution of 10 bits with limited INL & DNL Noise (including the setup noise): σ < 0. 5 LSB Consumption: 35 m. W/5 V Conversion time: 0. 25 µs (@ 4 MHz) Non. Linearity (measured): Integral NL +0. 85 LSB -0. 70 Differential NL +0. 56 LSB -0. 46 Mettre vue du schéma skiroc avec ADC 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 4

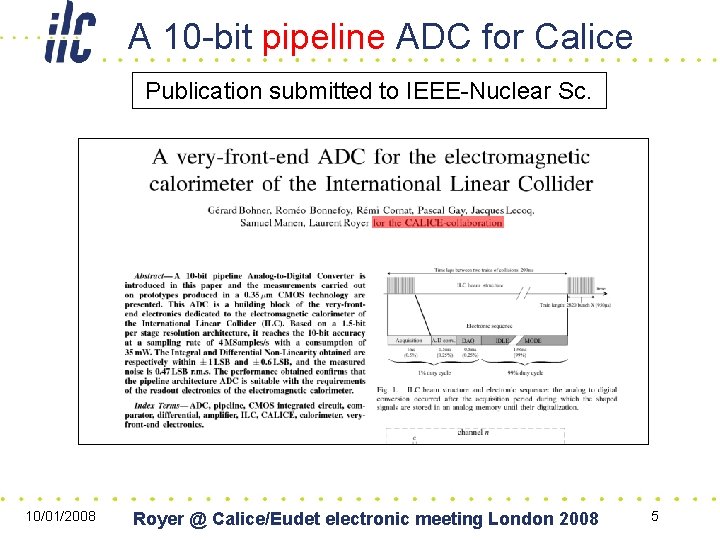

A 10 -bit pipeline ADC for Calice Publication submitted to IEEE-Nuclear Sc. 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 5

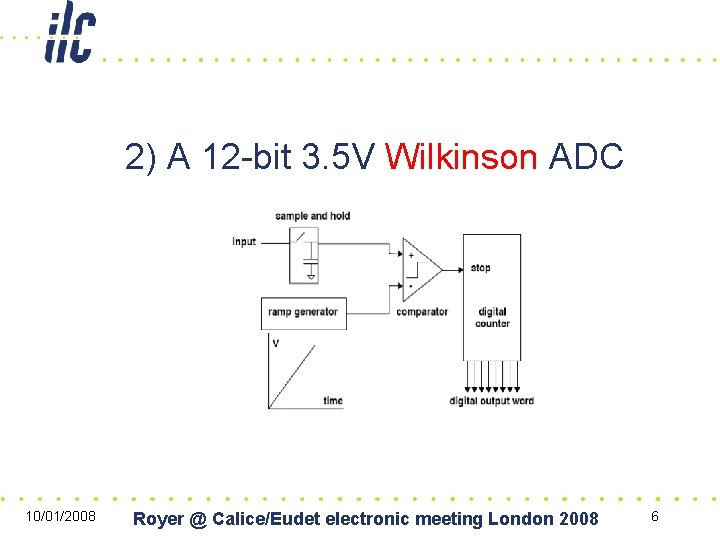

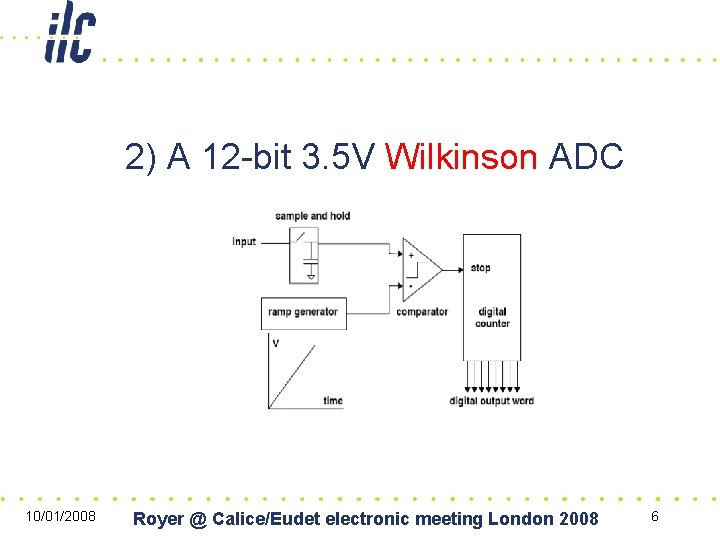

2) A 12 -bit 3. 5 V Wilkinson ADC 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 6

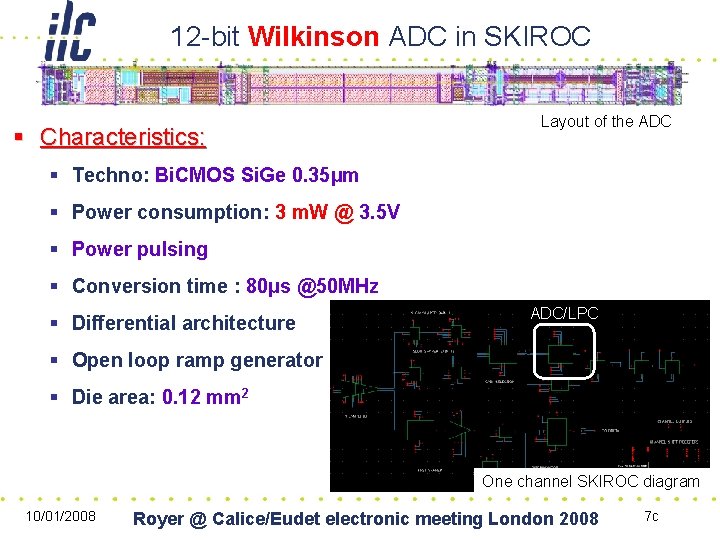

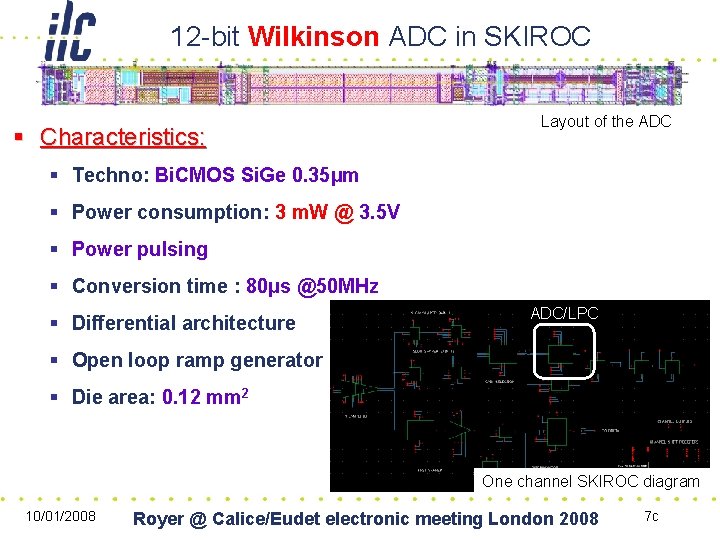

12 -bit Wilkinson ADC in SKIROC § Characteristics: Layout of the ADC § Techno: Bi. CMOS Si. Ge 0. 35µm § Power consumption: 3 m. W @ 3. 5 V § Power pulsing § Conversion time : 80µs @50 MHz § Differential architecture ADC/LPC § Open loop ramp generator § Die area: 0. 12 mm 2 One channel SKIROC diagram 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 7 c

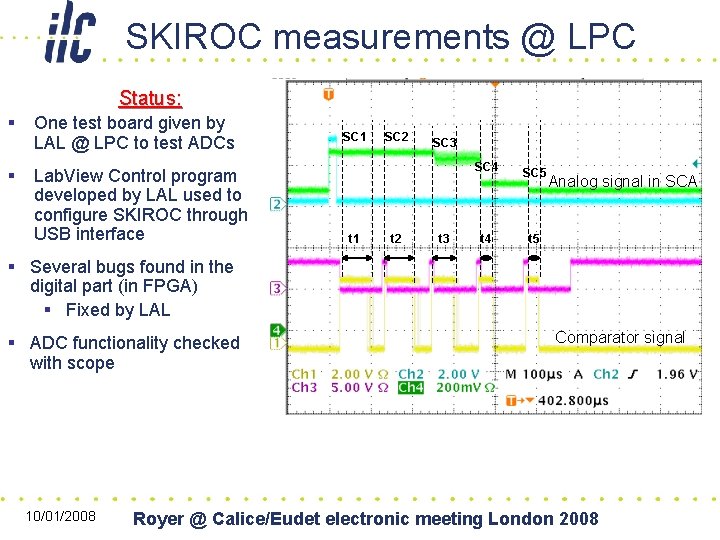

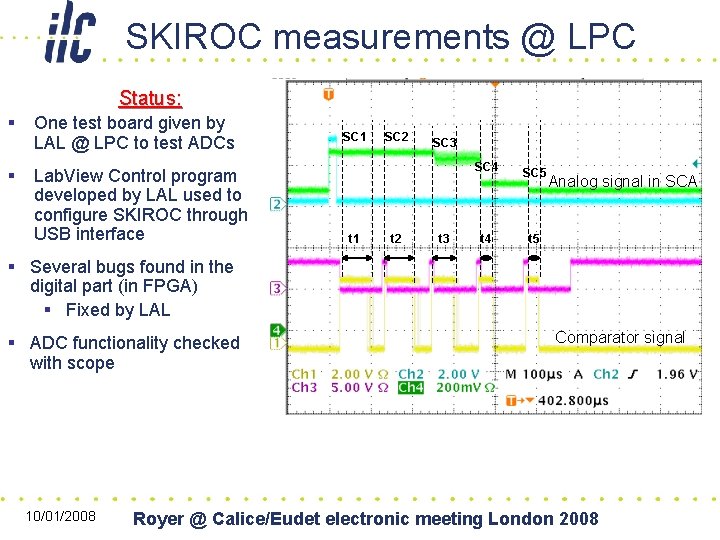

SKIROC measurements @ LPC Status: § § One test board given by LAL @ LPC to test ADCs Lab. View Control program developed by LAL used to configure SKIROC through USB interface SC 1 t 1 SC 2 t 2 SC 3 t 3 SC 4 SC 5 t 4 t 5 Analog signal in SCA § Several bugs found in the digital part (in FPGA) § Fixed by LAL § ADC functionality checked with scope 10/01/2008 Comparator signal 8 Royer @ Calice/Eudet electronic meeting London 2008

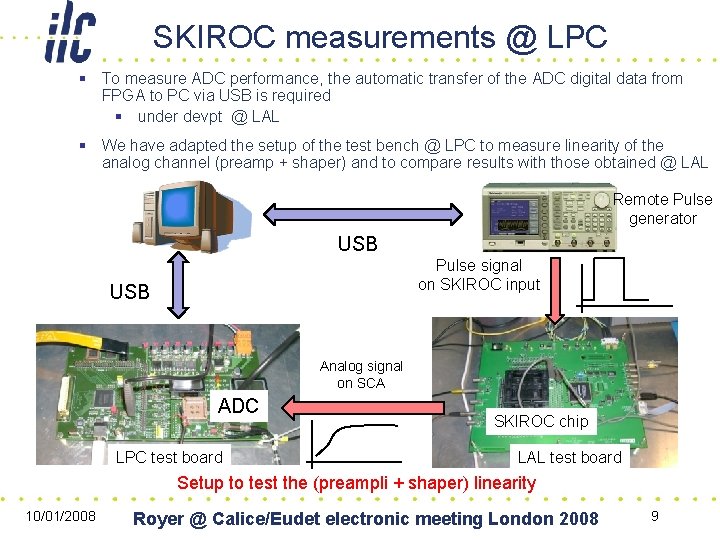

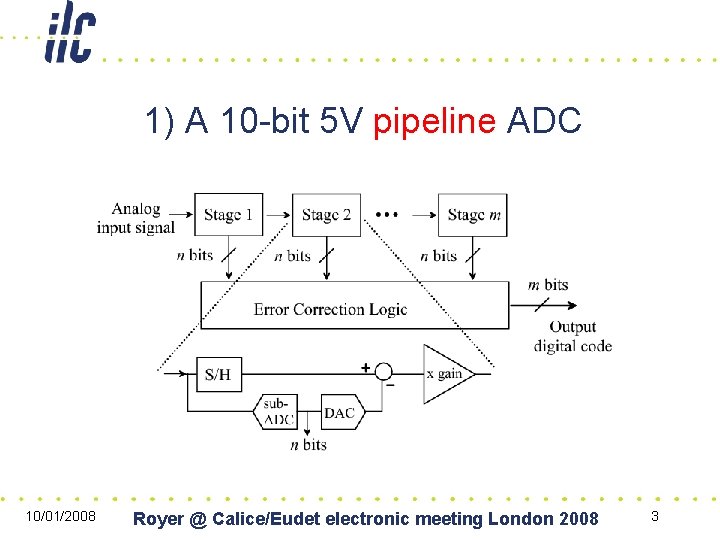

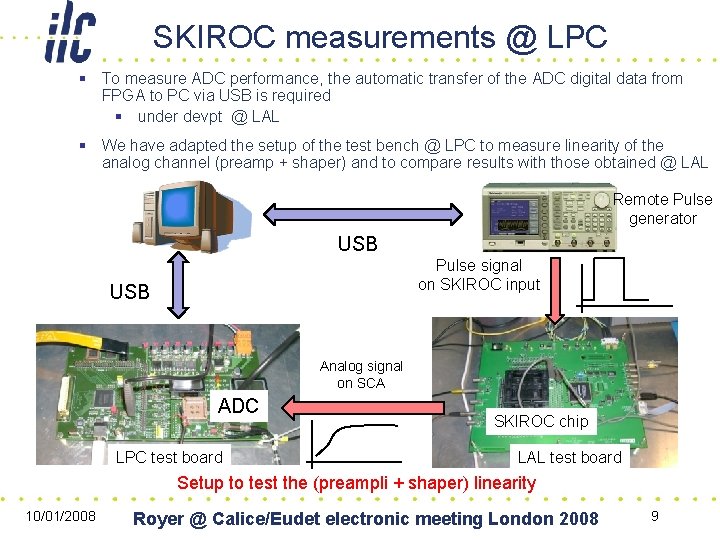

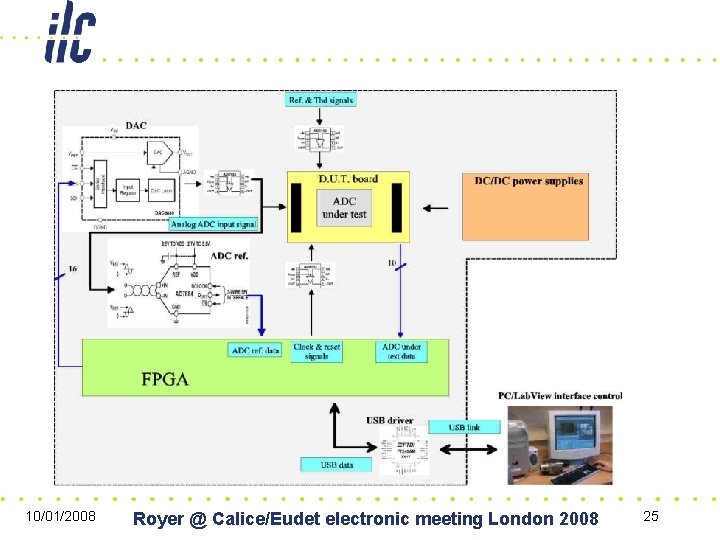

SKIROC measurements @ LPC § To measure ADC performance, the automatic transfer of the ADC digital data from FPGA to PC via USB is required § under devpt @ LAL § We have adapted the setup of the test bench @ LPC to measure linearity of the analog channel (preamp + shaper) and to compare results with those obtained @ LAL Remote Pulse generator USB Pulse signal on SKIROC input USB Analog signal on SCA ADC LPC test board SKIROC chip LAL test board Setup to test the (preampli + shaper) linearity 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 9

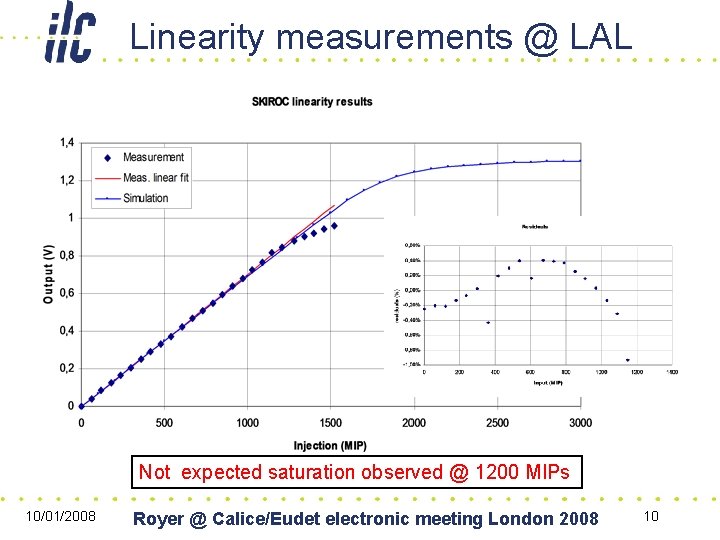

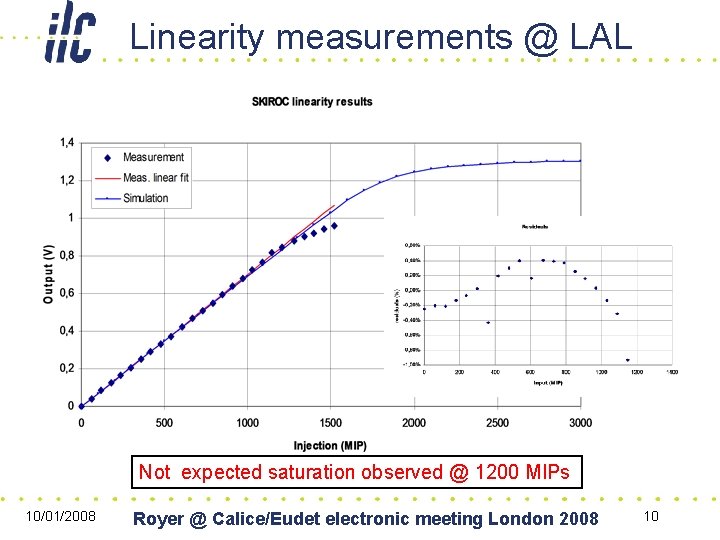

Linearity measurements @ LAL Not expected saturation observed @ 1200 MIPs 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 10

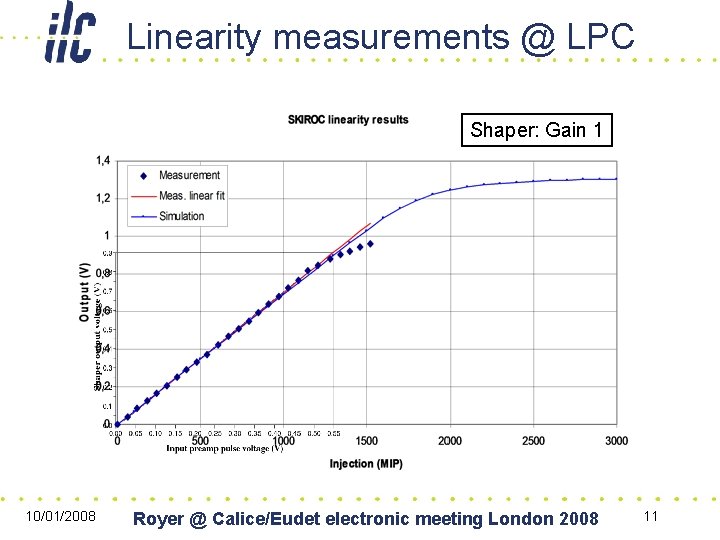

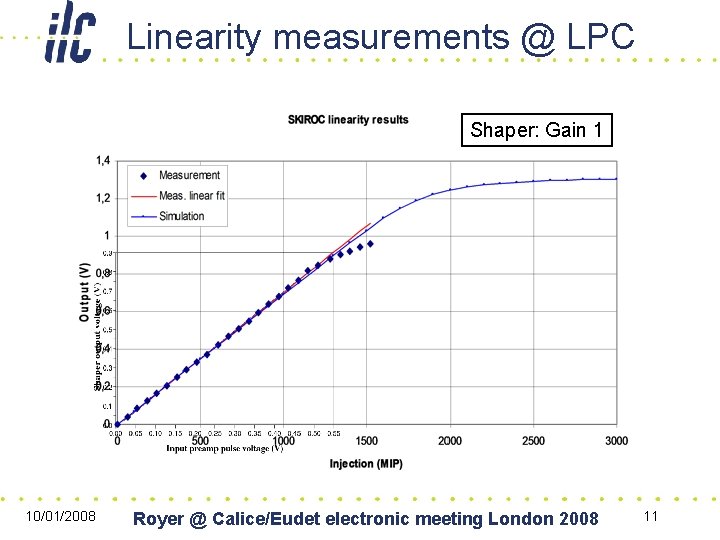

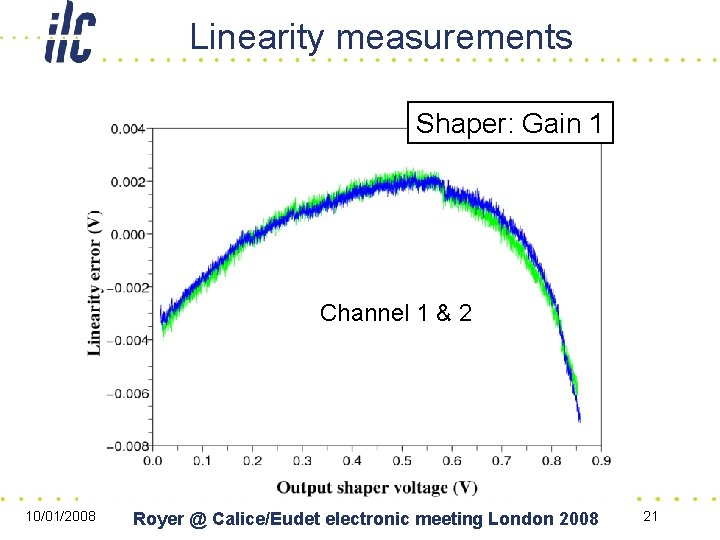

Linearity measurements @ LPC Shaper: Gain 1 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 11

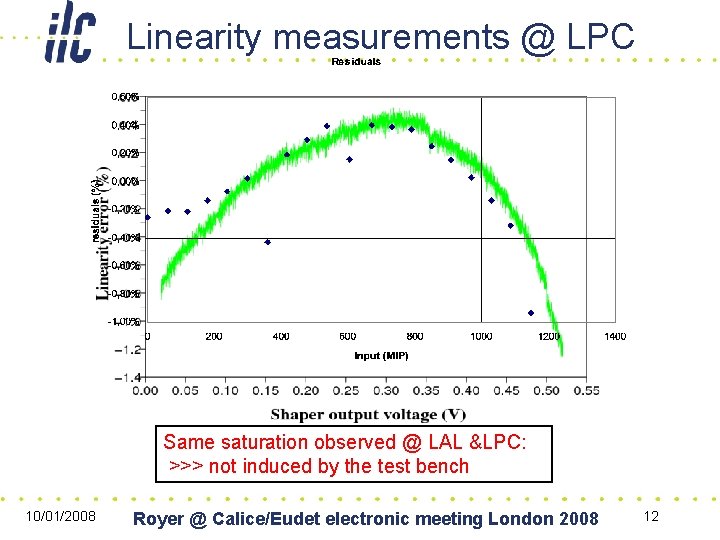

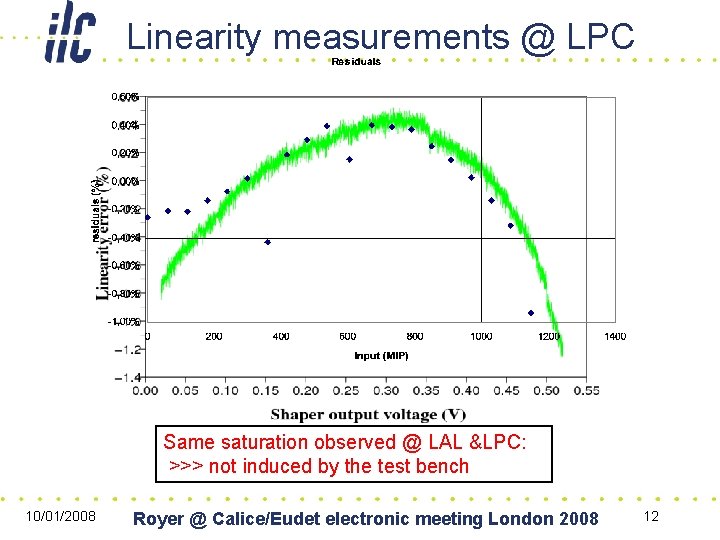

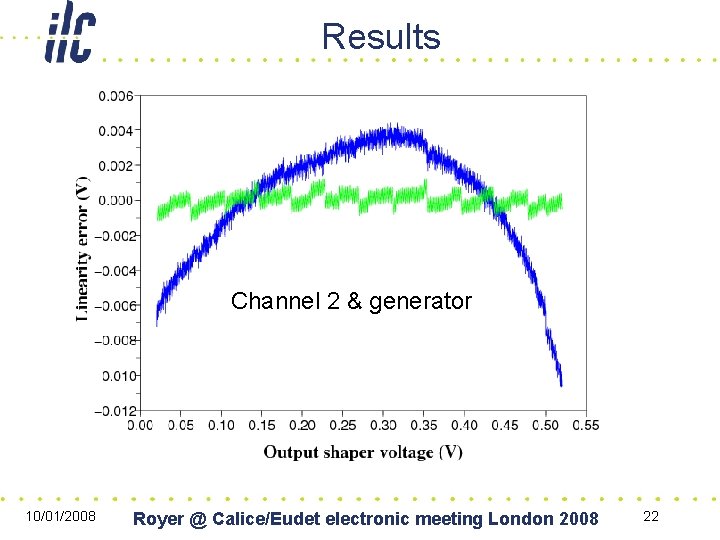

Linearity measurements @ LPC Same saturation observed @ LAL &LPC: >>> not induced by the test bench 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 12

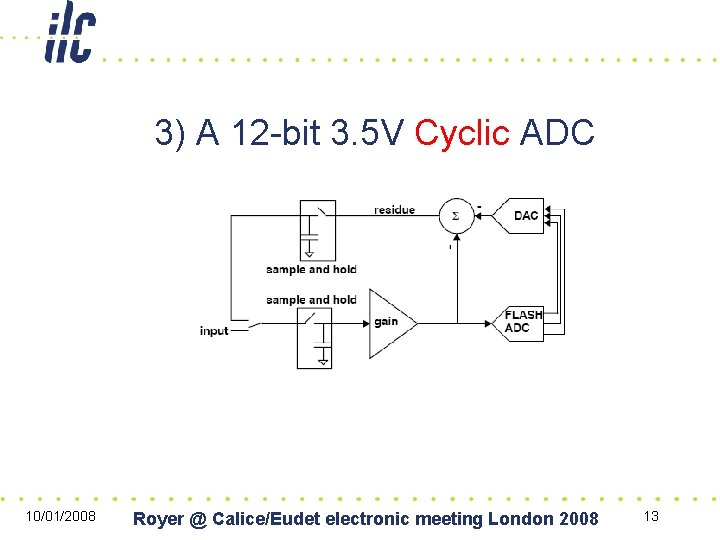

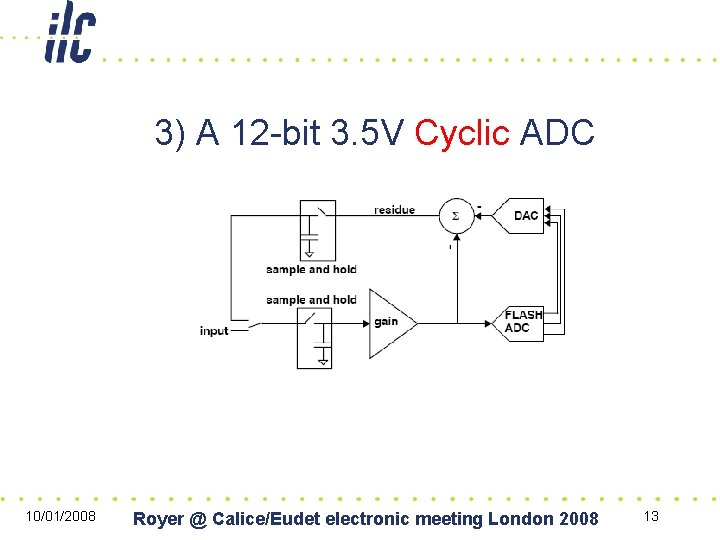

3) A 12 -bit 3. 5 V Cyclic ADC 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 13

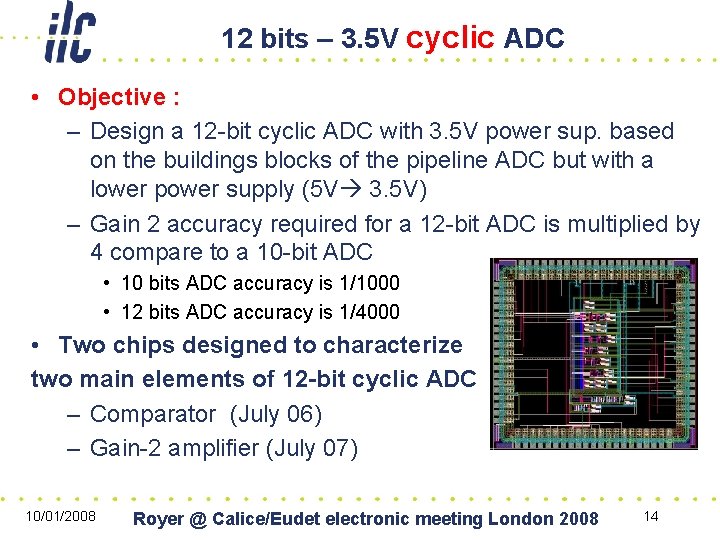

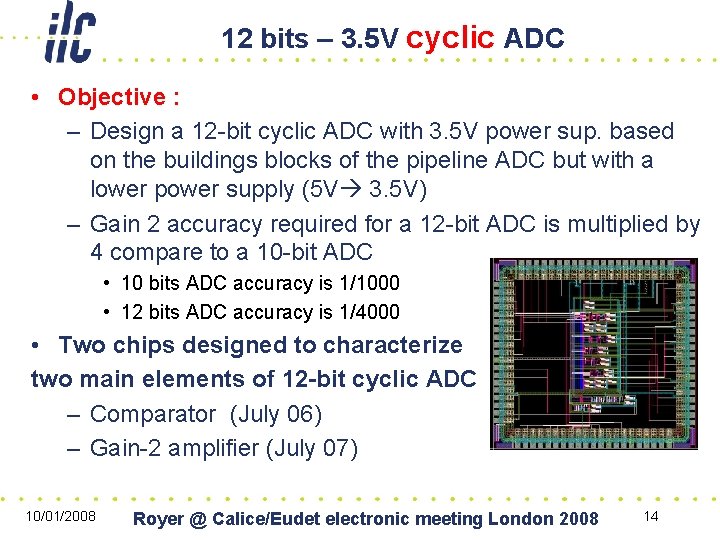

12 bits – 3. 5 V cyclic ADC • Objective : – Design a 12 -bit cyclic ADC with 3. 5 V power sup. based on the buildings blocks of the pipeline ADC but with a lower power supply (5 V 3. 5 V) – Gain 2 accuracy required for a 12 -bit ADC is multiplied by 4 compare to a 10 -bit ADC • 10 bits ADC accuracy is 1/1000 • 12 bits ADC accuracy is 1/4000 • Two chips designed to characterize two main elements of 12 -bit cyclic ADC – Comparator (July 06) – Gain-2 amplifier (July 07) 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 14

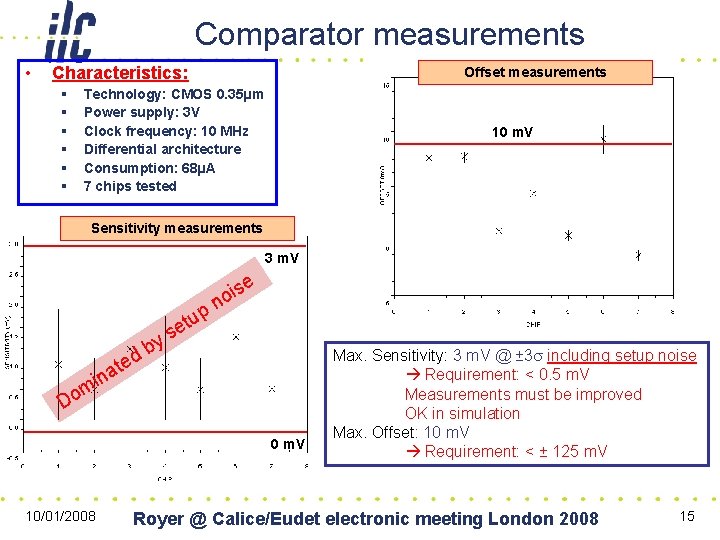

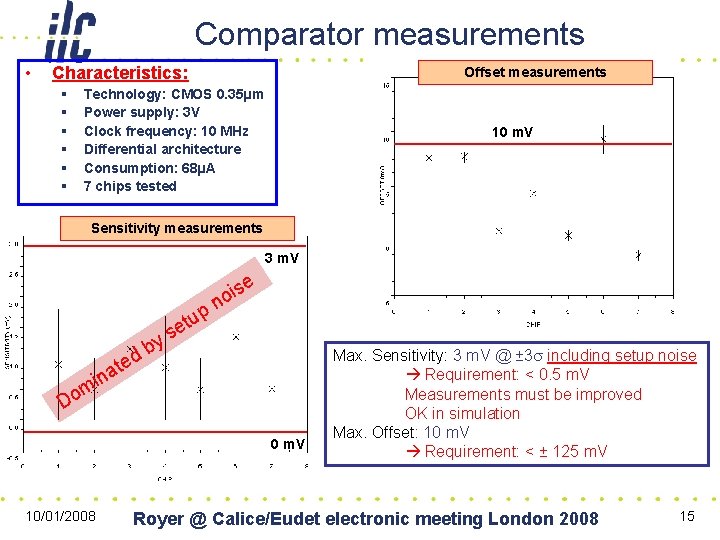

Comparator measurements • Characteristics: § § § Offset measurements Technology: CMOS 0. 35µm Power supply: 3 V Clock frequency: 10 MHz Differential architecture Consumption: 68µA 7 chips tested 10 m. V Sensitivity measurements 3 m. V y na i m b d te tu e s i o pn Do 0 m. V 10/01/2008 Max. Sensitivity: 3 m. V @ ± 3 including setup noise Requirement: < 0. 5 m. V Measurements must be improved OK in simulation Max. Offset: 10 m. V Requirement: < ± 125 m. V Royer @ Calice/Eudet electronic meeting London 2008 15

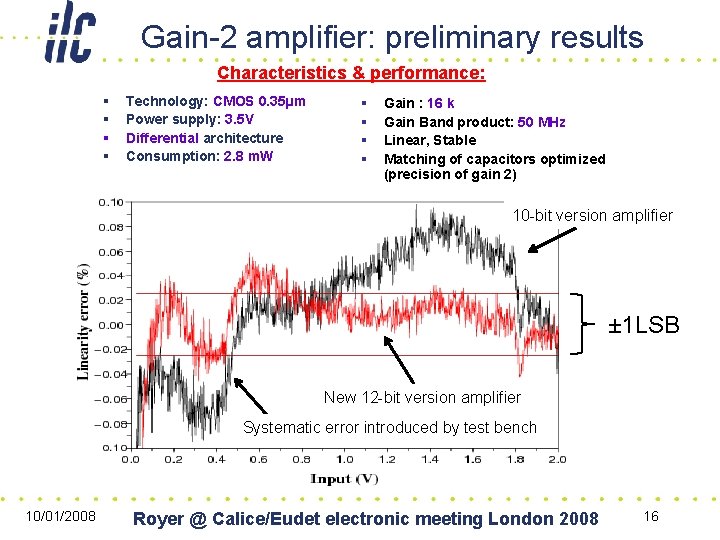

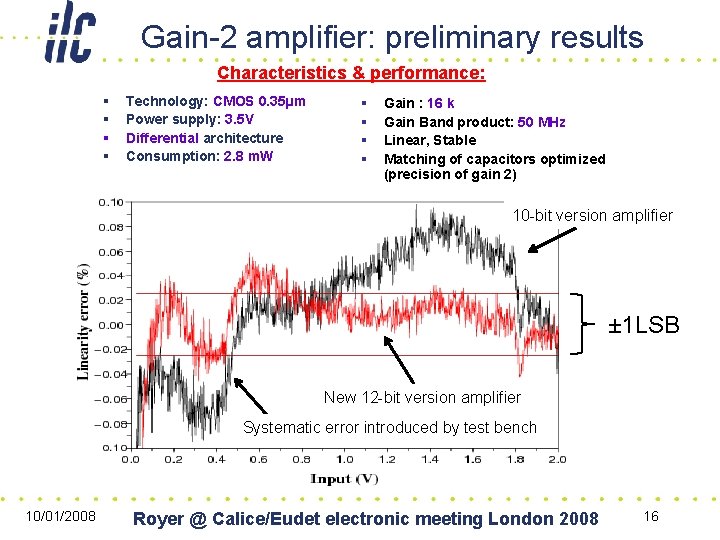

Gain-2 amplifier: preliminary results Characteristics & performance: § § Technology: CMOS 0. 35µm Power supply: 3. 5 V Differential architecture Consumption: 2. 8 m. W § § Gain : 16 k Gain Band product: 50 MHz Linear, Stable Matching of capacitors optimized (precision of gain 2) 10 -bit version amplifier ± 1 LSB New 12 -bit version amplifier Systematic error introduced by test bench 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 16

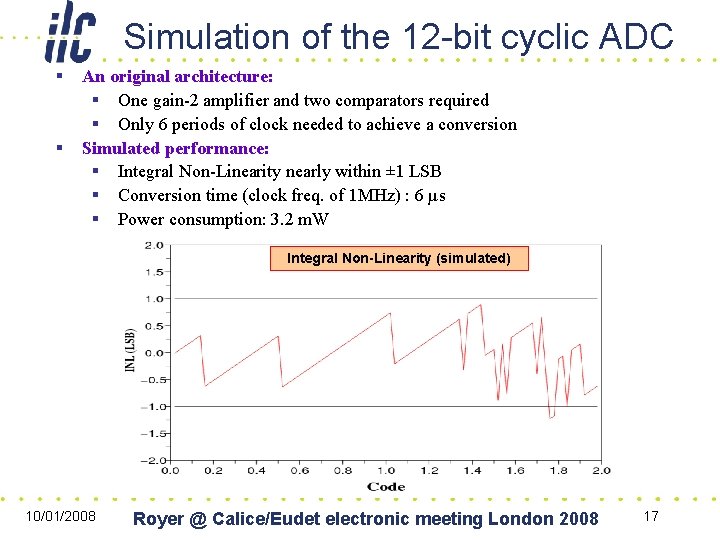

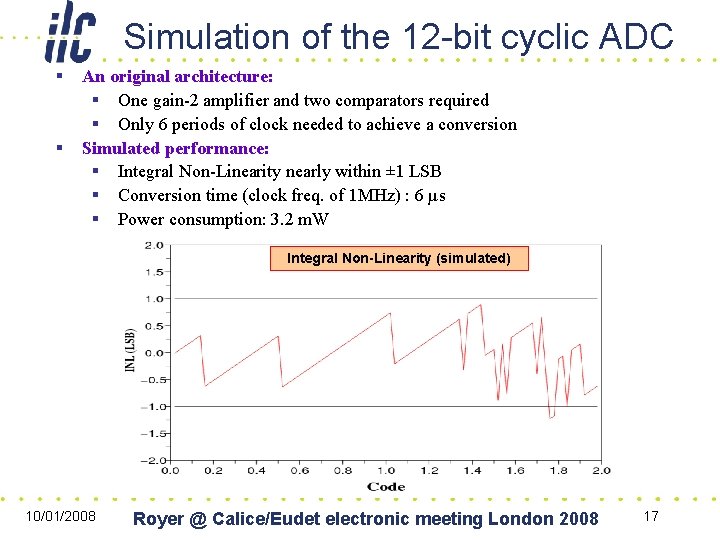

Simulation of the 12 -bit cyclic ADC § § An original architecture: § One gain-2 amplifier and two comparators required § Only 6 periods of clock needed to achieve a conversion Simulated performance: § Integral Non-Linearity nearly within ± 1 LSB § Conversion time (clock freq. of 1 MHz) : 6 µs § Power consumption: 3. 2 m. W Integral Non-Linearity (simulated) 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 17

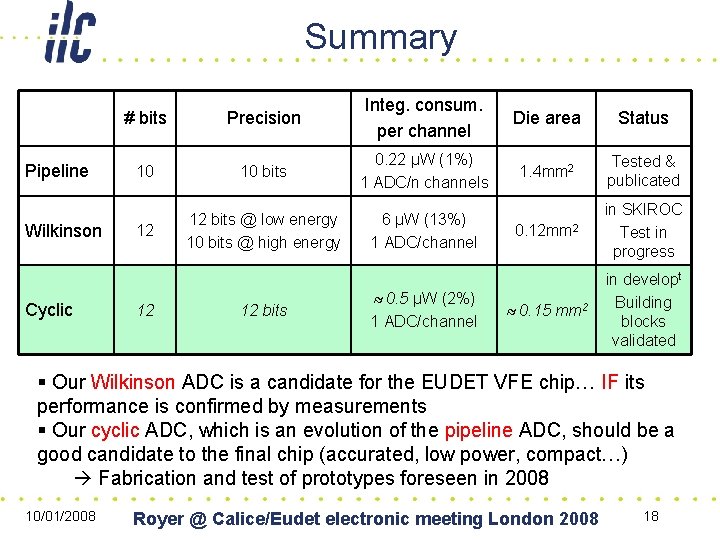

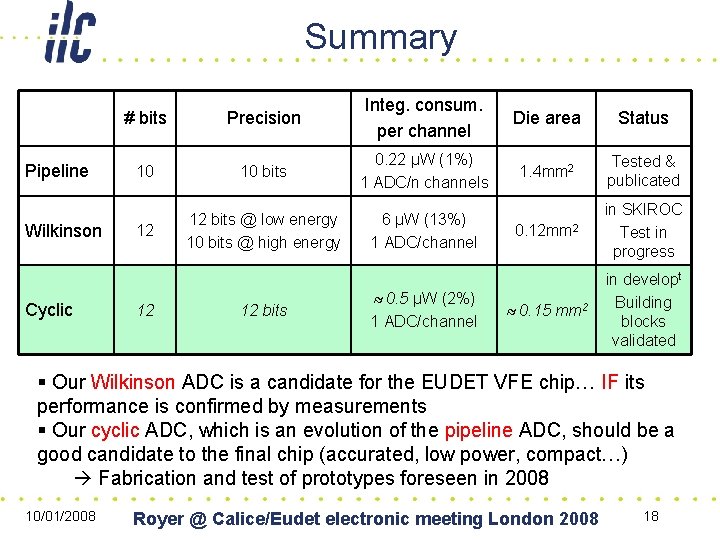

Summary Pipeline Wilkinson Cyclic # bits Precision Integ. consum. per channel 10 10 bits 0. 22 µW (1%) 1 ADC/n channels 12 12 bits @ low energy 10 bits @ high energy 6 µW (13%) 1 ADC/channel 12 12 bits 0. 5 µW (2%) 1 ADC/channel Die area Status 1. 4 mm 2 Tested & publicated 0. 12 mm 2 in SKIROC Test in progress 0. 15 mm 2 in developt Building blocks validated § Our Wilkinson ADC is a candidate for the EUDET VFE chip… IF its performance is confirmed by measurements § Our cyclic ADC, which is an evolution of the pipeline ADC, should be a good candidate to the final chip (accurated, low power, compact…) Fabrication and test of prototypes foreseen in 2008 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 18

SPARE SLIDES 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 19

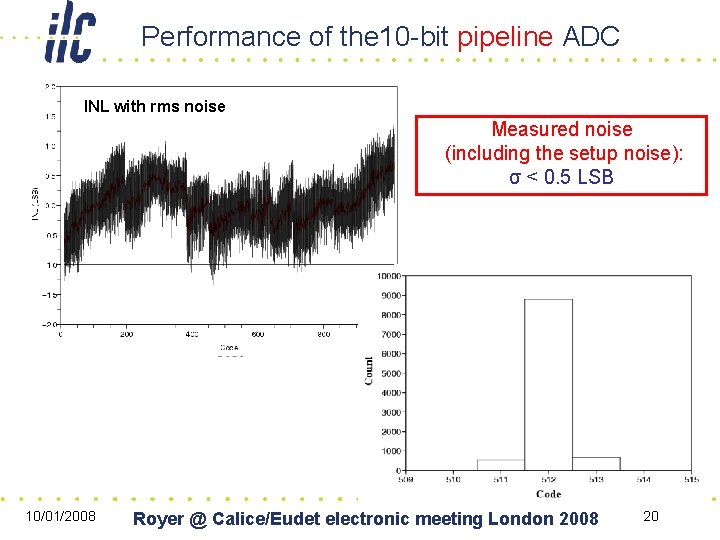

Performance of the 10 -bit pipeline ADC INL with rms noise Measured noise (including the setup noise): σ < 0. 5 LSB Codes distribution @ code center (512) 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 20

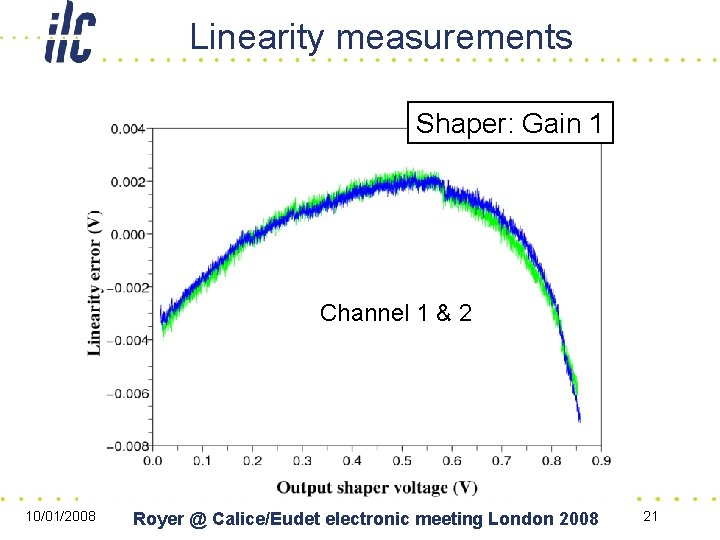

Linearity measurements Shaper: Gain 1 Channel 1 & 2 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 21

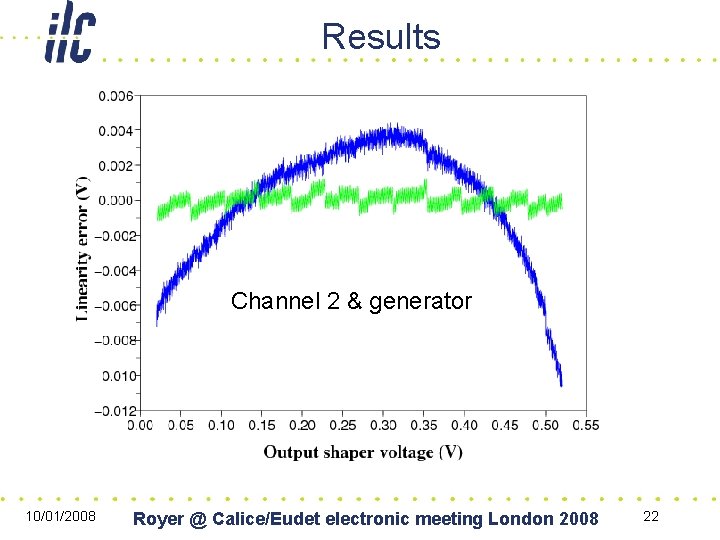

Results Channel 2 & generator 10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 22

10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 23

10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 24

10/01/2008 Royer @ Calice/Eudet electronic meeting London 2008 25