Status of OTIS 1 0 OTIS Review 2003

- Slides: 14

Status of OTIS 1. 0 OTIS Review 2003, June 5 OTIS GROUP, Heidelberg University Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Heidelberg University 1

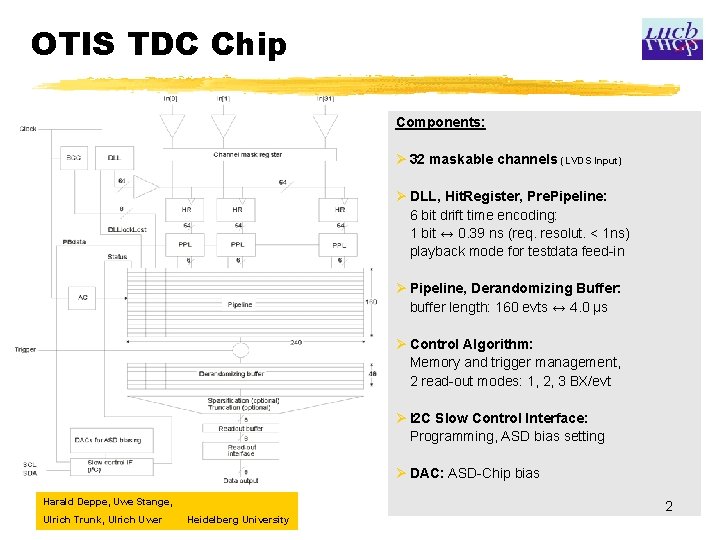

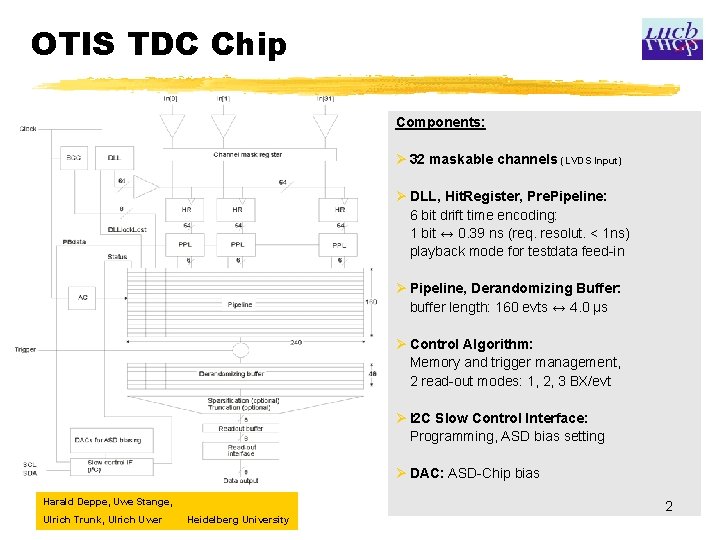

OTIS TDC Chip Components: Ø 32 maskable channels (LVDS Input) Ø DLL, Hit. Register, Pre. Pipeline: 6 bit drift time encoding: 1 bit ↔ 0. 39 ns (req. resolut. < 1 ns) playback mode for testdata feed-in Ø Pipeline, Derandomizing Buffer: buffer length: 160 evts ↔ 4. 0 μs Ø Control Algorithm: Memory and trigger management, 2 read-out modes: 1, 2, 3 BX/evt Ø I 2 C Slow Control Interface: Programming, ASD bias setting Ø DAC: ASD-Chip bias Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 2 Heidelberg University

OTIS TDC Ó 3. 250 OTIS-TDCs with 32 channels each Ó 4 OTIS TDCs are connected to one GOL (fast serializer chip) one fibre per 128 channels Ó Radiation hard layout 0. 25 µm CMOS Ó DLL fine time resolution 6 bit Ó Dual Ported Memory with 1. 2 Gb/s, 240 bit width (low power design) Ó Synchronous clock driven readout Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 3 Heidelberg University

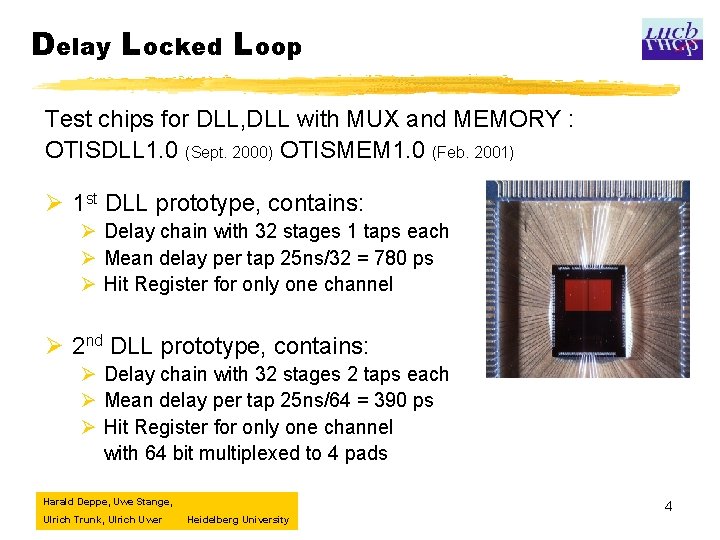

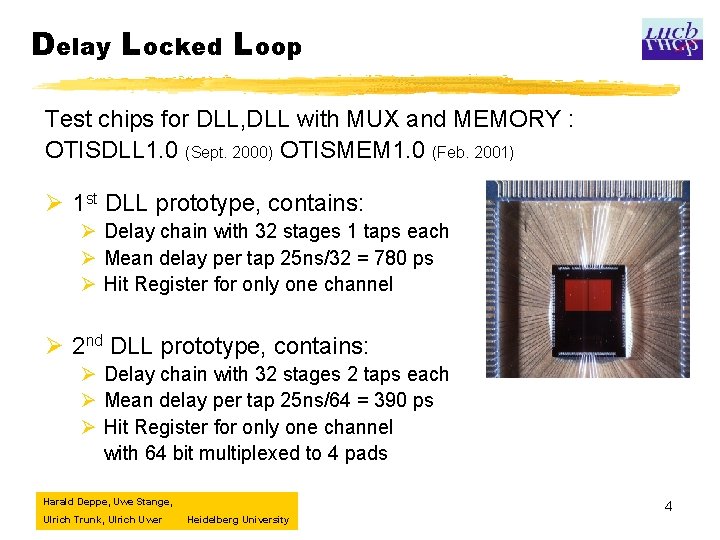

Delay Locked Loop Test chips for DLL, DLL with MUX and MEMORY : OTISDLL 1. 0 (Sept. 2000) OTISMEM 1. 0 (Feb. 2001) Ø 1 st DLL prototype, contains: Ø Delay chain with 32 stages 1 taps each Ø Mean delay per tap 25 ns/32 = 780 ps Ø Hit Register for only one channel Ø 2 nd DLL prototype, contains: Ø Delay chain with 32 stages 2 taps each Ø Mean delay per tap 25 ns/64 = 390 ps Ø Hit Register for only one channel with 64 bit multiplexed to 4 pads Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 4 Heidelberg University

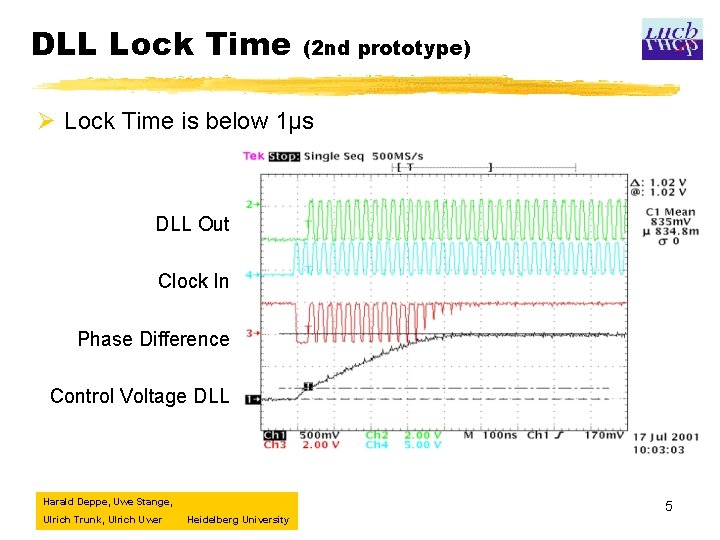

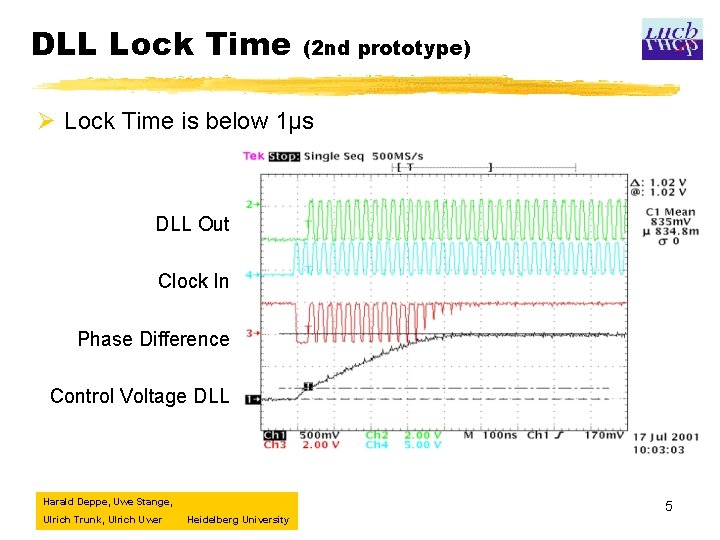

DLL Lock Time (2 nd prototype) Ø Lock Time is below 1µs DLL Out Clock In Phase Difference Control Voltage DLL Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 5 Heidelberg University

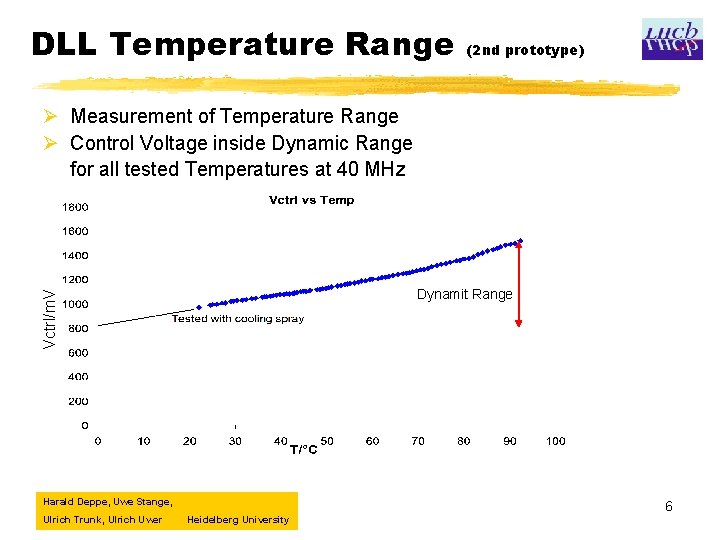

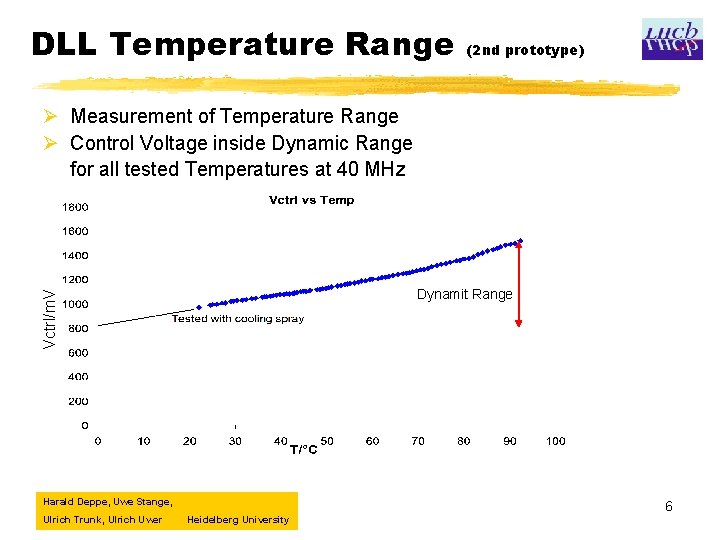

DLL Temperature Range (2 nd prototype) Ø Measurement of Temperature Range Ø Control Voltage inside Dynamic Range for all tested Temperatures at 40 MHz Vctrl/m. V Dynamit Range Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 6 Heidelberg University

Measurements on OTIS 1. 0 Ø Ø DLL Lock Range DLL Lock –Time Fine. Time Measurements Differential Non-Linearity Ø ALL limitations on the functionality of OTIS 1. 0 concerning Finetime and Hit. Bit encoding are due to parasitics. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 7 Heidelberg University

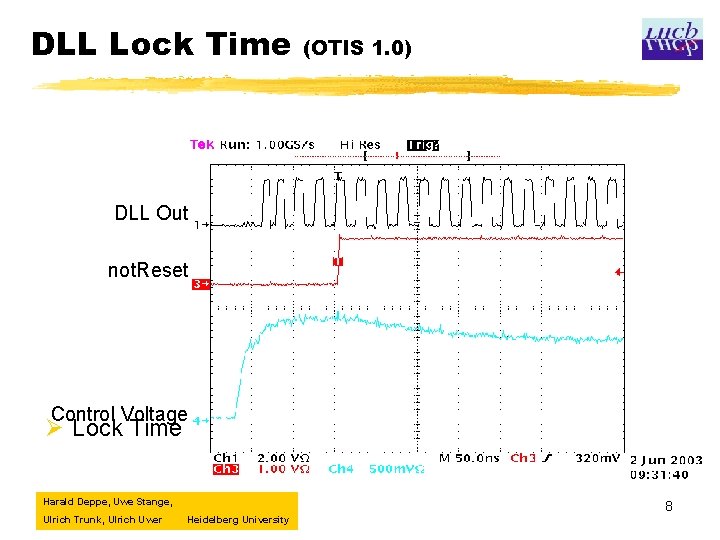

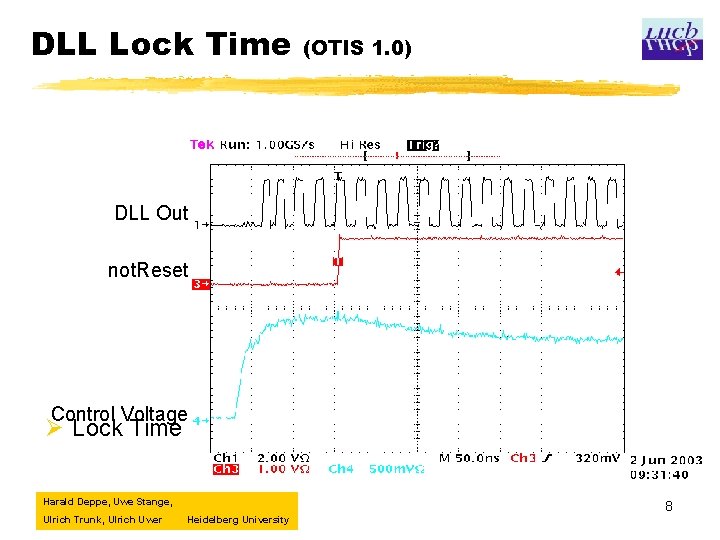

DLL Lock Time (OTIS 1. 0) DLL Out not. Reset Control Voltage Ø Lock Time is below 1µs Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 8 Heidelberg University

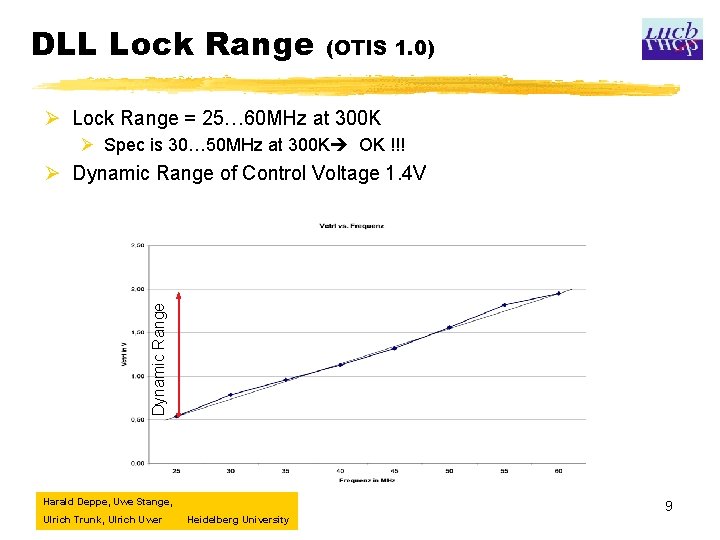

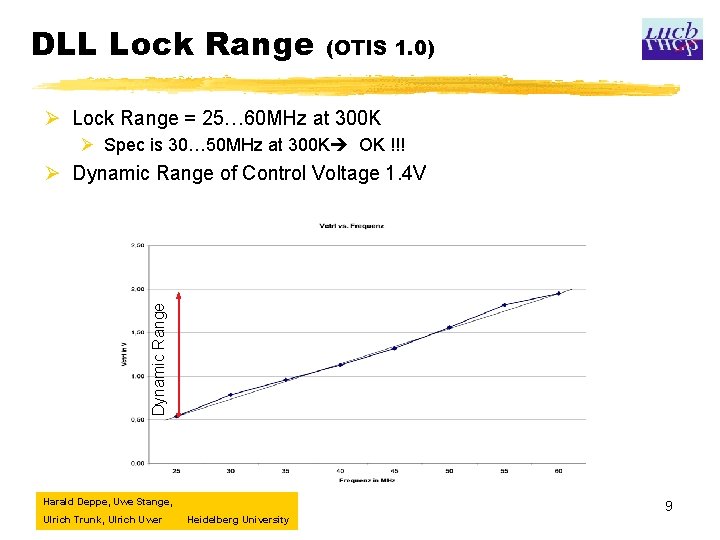

DLL Lock Range (OTIS 1. 0) Ø Lock Range = 25… 60 MHz at 300 K Ø Spec is 30… 50 MHz at 300 K OK !!! Dynamic Range Ø Dynamic Range of Control Voltage 1. 4 V Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 9 Heidelberg University

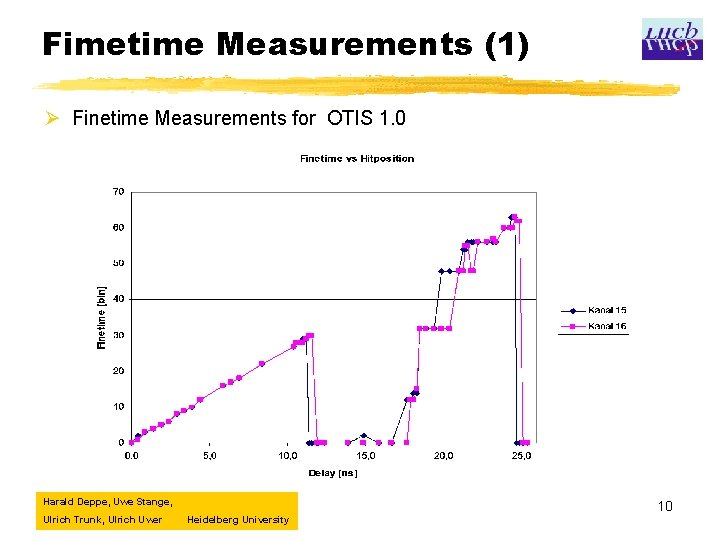

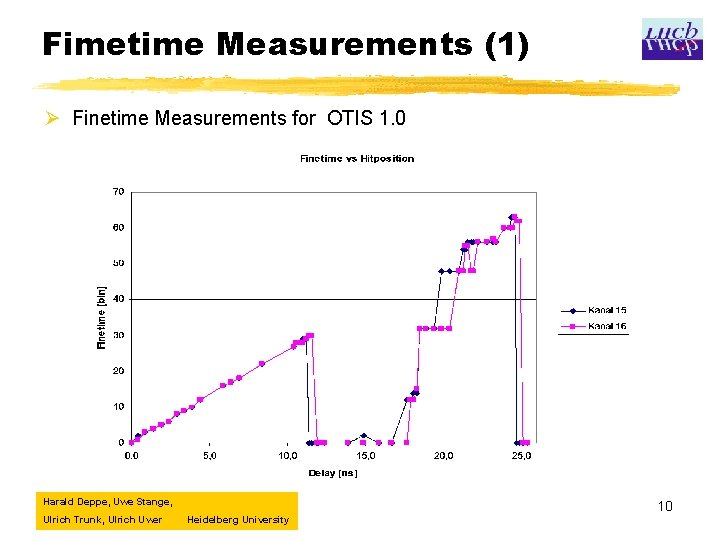

Fimetime Measurements (1) Ø Finetime Measurements for OTIS 1. 0 Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 10 Heidelberg University

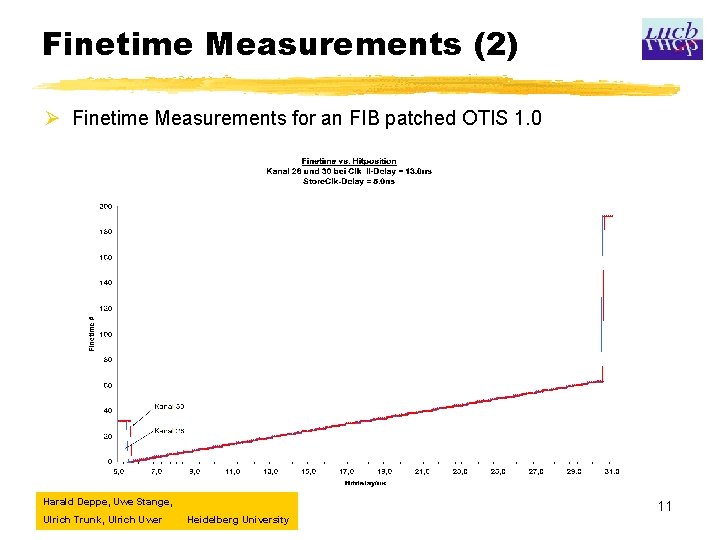

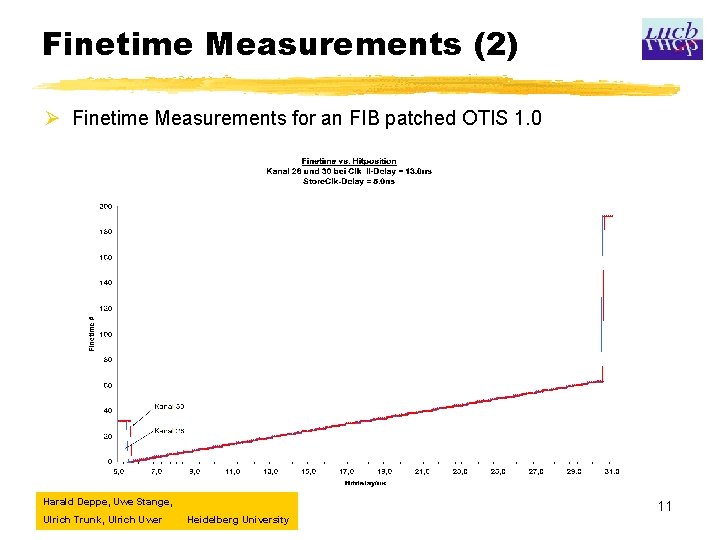

Finetime Measurements (2) Ø Finetime Measurements for an FIB patched OTIS 1. 0 Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 11 Heidelberg University

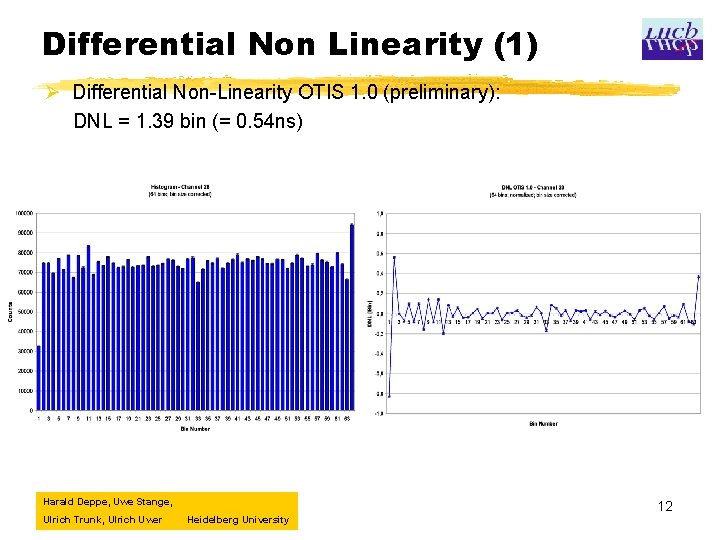

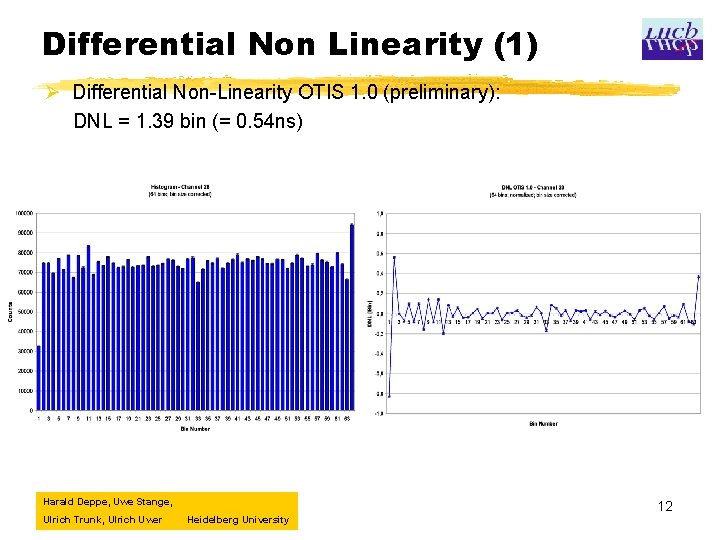

Differential Non Linearity (1) Ø Differential Non-Linearity OTIS 1. 0 (preliminary): DNL = 1. 39 bin (= 0. 54 ns) Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 12 Heidelberg University

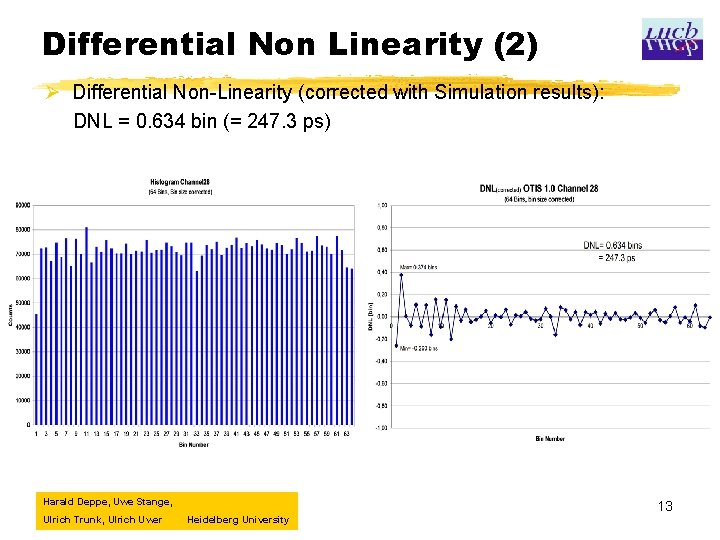

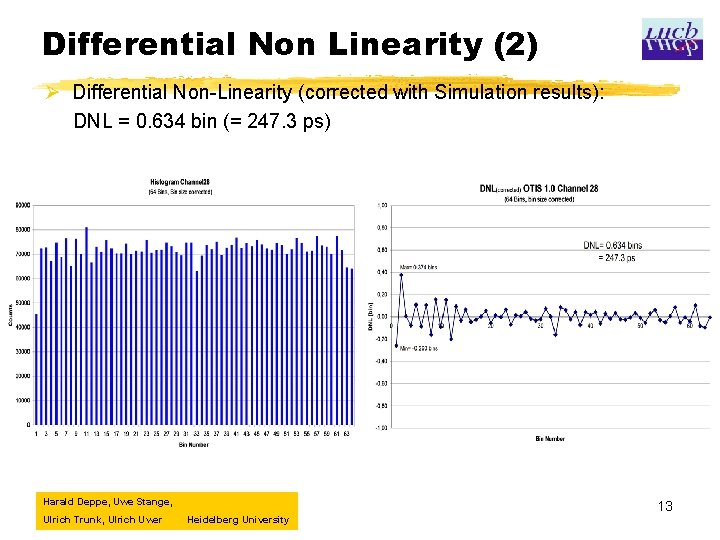

Differential Non Linearity (2) Ø Differential Non-Linearity (corrected with Simulation results): DNL = 0. 634 bin (= 247. 3 ps) Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 13 Heidelberg University

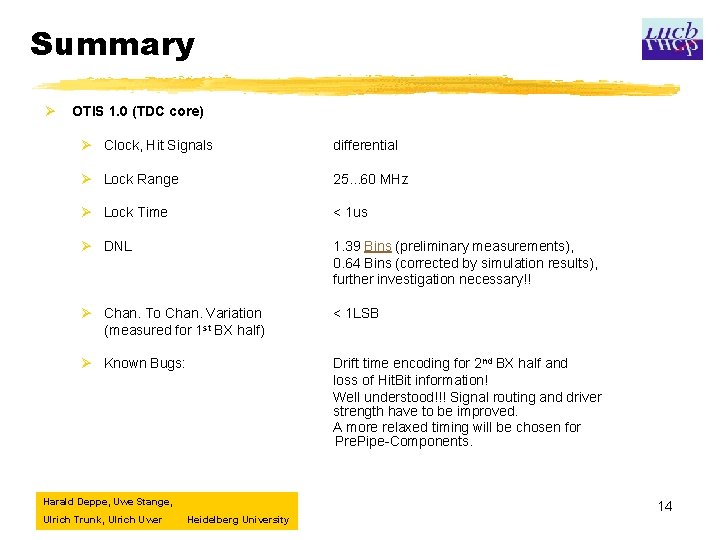

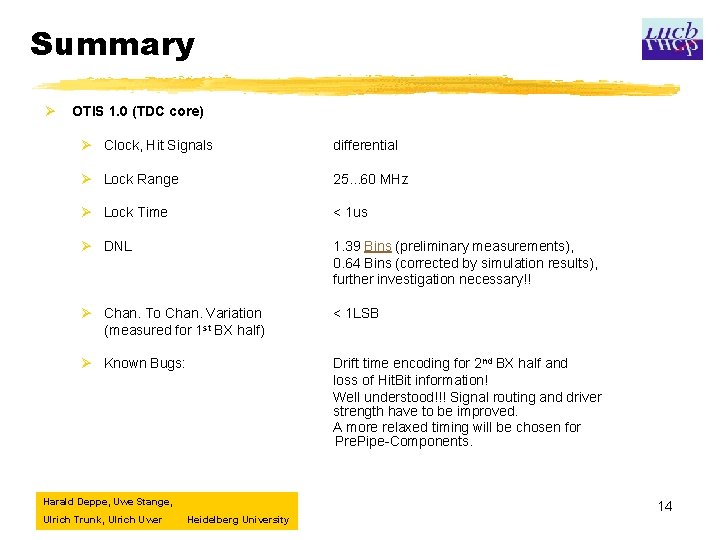

Summary Ø OTIS 1. 0 (TDC core) Ø Clock, Hit Signals differential Ø Lock Range 25. . . 60 MHz Ø Lock Time < 1 us Ø DNL 1. 39 Bins (preliminary measurements), 0. 64 Bins (corrected by simulation results), further investigation necessary!! Ø Chan. To Chan. Variation (measured for 1 st BX half) < 1 LSB Ø Known Bugs: Drift time encoding for 2 nd BX half and loss of Hit. Bit information! Well understood!!! Signal routing and driver strength have to be improved. A more relaxed timing will be chosen for Pre. Pipe-Components. Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer 14 Heidelberg University