State Machine Design with an HDL A methodology

- Slides: 27

State Machine Design with an HDL A methodology that works for documenting the design, simulation and verification of the design, and synthesis for FPGA, or a custom ASIC generated using synthesis. 1/8/2007 - L 20 Project Step 8 Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 1

Lecture overview o o o State machine basics HDL methodology State machine example 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 2

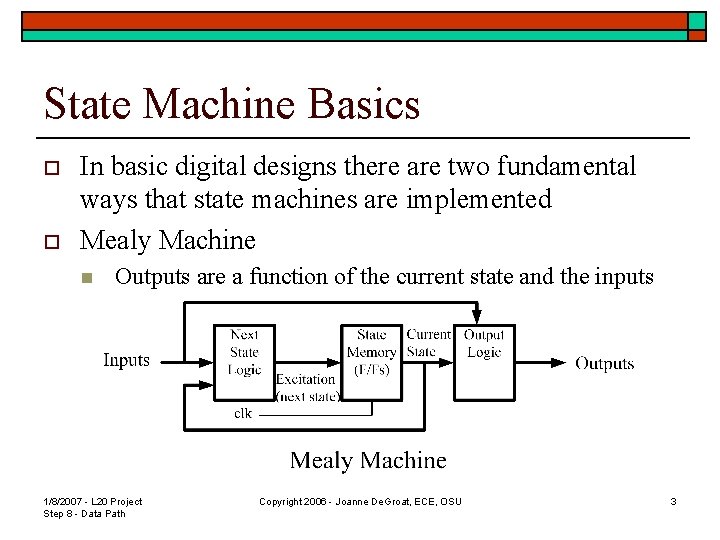

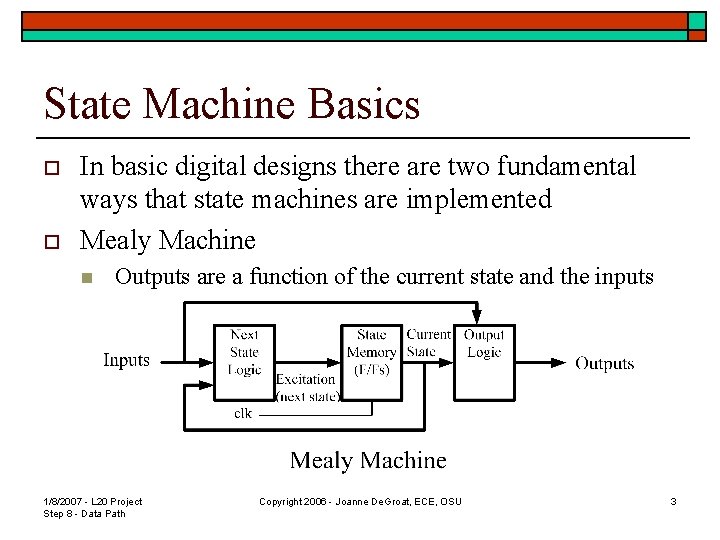

State Machine Basics o o In basic digital designs there are two fundamental ways that state machines are implemented Mealy Machine n Outputs are a function of the current state and the inputs 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 3

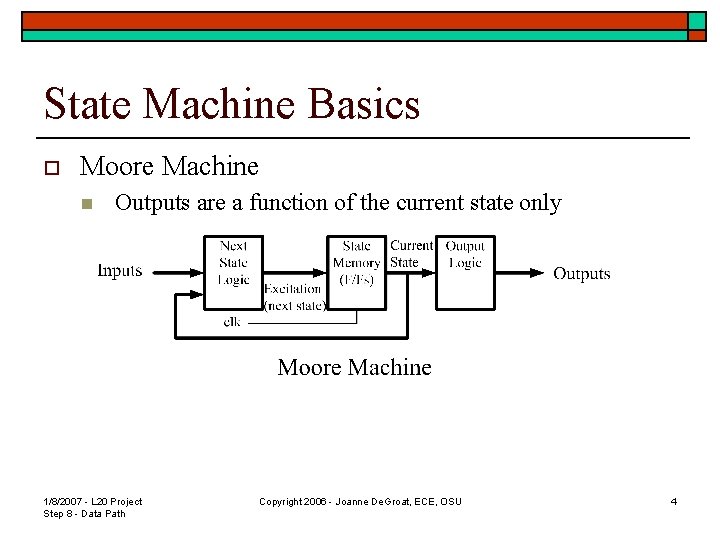

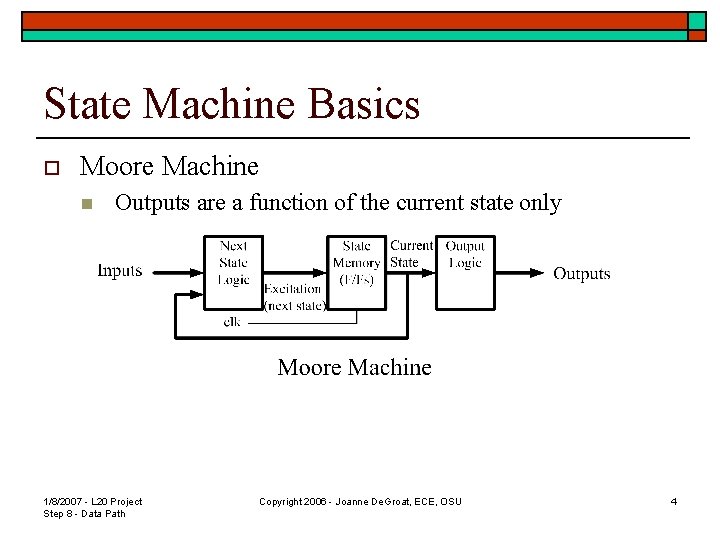

State Machine Basics o Moore Machine n Outputs are a function of the current state only 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 4

Some interesting info o o Mealy machine is names after George H. Mealy who presented a paper in 1955, “A Method for Synthesizing Sequential Circuits. ” Formal definition – A Mealy machine is a 6 -tuple, n n n A finite set of states A start state (initial state) A finite set called the input alphabet A finite set called the output alphabet A transition function (T: S x S S) mapping pairs of a state and an input symbol to the corresponding next state. An output function (G : S x S D) mapping pairs of a state and an input symbol to a corresponding output symbol. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 5

and o o Moore machine is names after Edward F. Moore who presented a paper in 1956, “Gedanken-experments on Sequential Machines. ” Formal Definition: n n n A finite set of states A start state (initial state) A finite set called the input alphabet A finite set called the output alphabet A transition function (T: S x S S) mapping a state and the input alphabet to the next state. An output function (G : S D) mapping each state to the output alphabet. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 6

HDL code o Coding a state machine in an HDL n Can simply implement an algorithm o o n Can code for a Mealy or Moore machine in a single process o o n Documents poorly Synthesis results are unpredictable Can follow a structured style o o o Documents poorly Cannot be synthesized (possibly but less than optimal result) Documents very well Synthesizes very well and results are predictable Simulation of the three possibilities is ~ the same 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 7

The coding style o o o The style applies to any HDL – VHDL, Verilog, System Verilog, and System C Documents well Easily maintainable – excellent during development as changes are easily made Style maps to physical logic – using this style can predict the number of state elements (~) that should be produced by synthesis All three styles on the last slide simulate equally well, but this style also synthesizes well. Works in XILINX and Altera tools. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 8

Style guide for sequential circuits o o o Use a process to describe the next state logic, often in a case statement used for determination of the next state. Will see this in the example. Use a process to represent the latching/loading of the calculated next_state such that it becomes the current_state. This is the only process that generates sequential elements (F/Fs). The other processes represent combinational logic. Can use a template. Use a third process to represent the generation of the outputs from the current state and possibly the inputs. This process will have as its inputs, the current state and, depending on the type of state machine, the state machine inputs. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 9

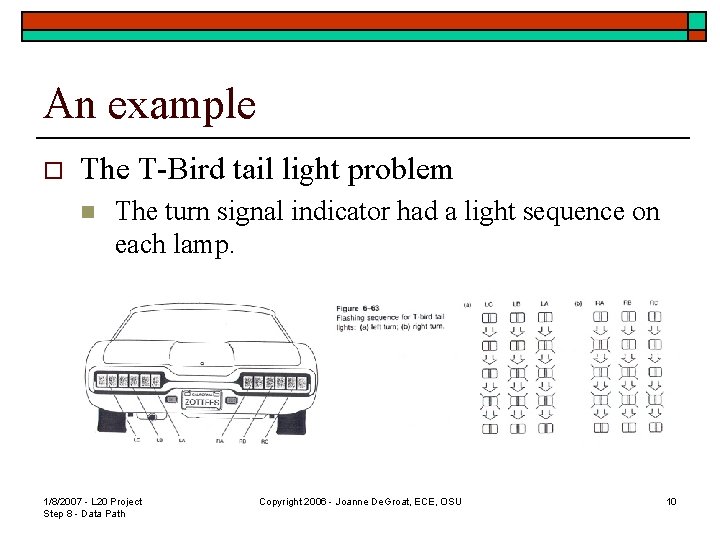

An example o The T-Bird tail light problem n The turn signal indicator had a light sequence on each lamp. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 10

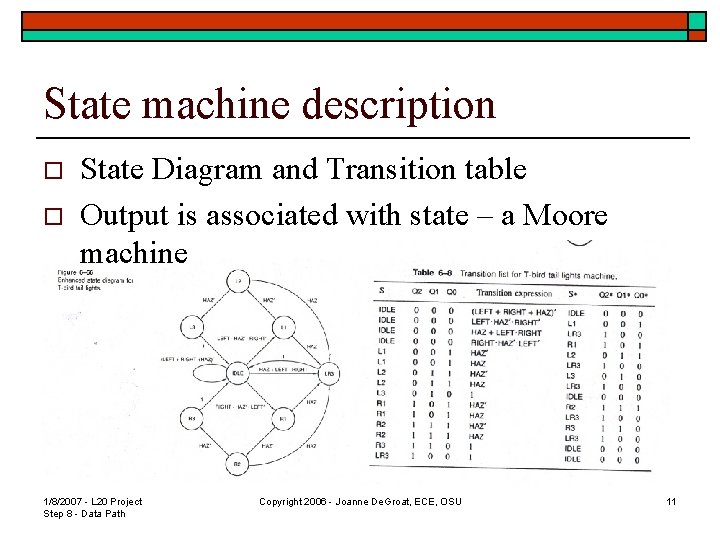

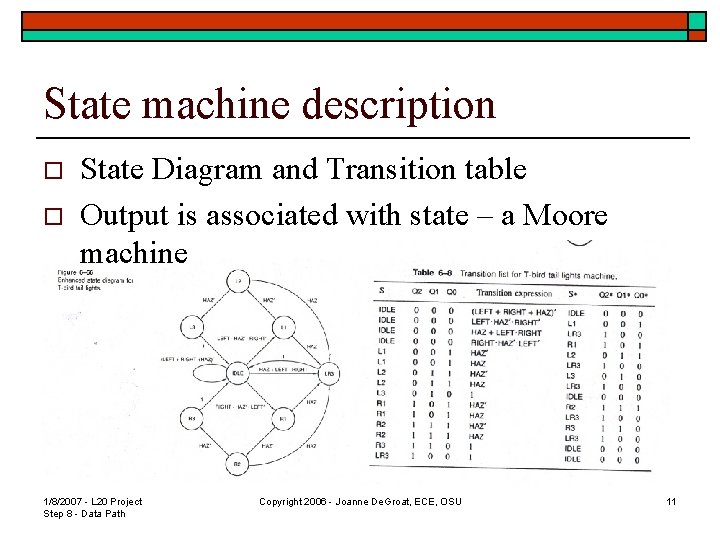

State machine description o o State Diagram and Transition table Output is associated with state – a Moore machine 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 11

Design with HDL o o You still start with a state diagram You may or may not generate a transition table Will now look at the code Where to start – THE INTERFACE n What are the inputs and the outputs? 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 12

The Entity o Inputs are a signal for n n o Right turn signal Left turn signal Hazard Clock Outputs are the signals for the lights n n lc, lb, la rc, rb, ra 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 13

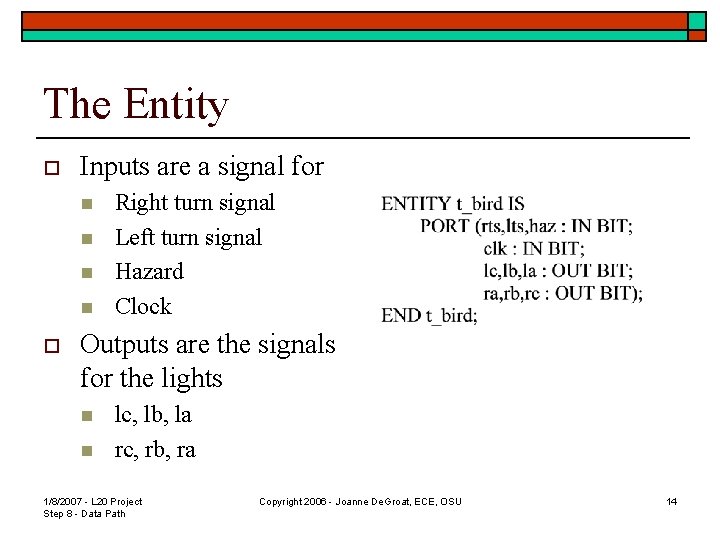

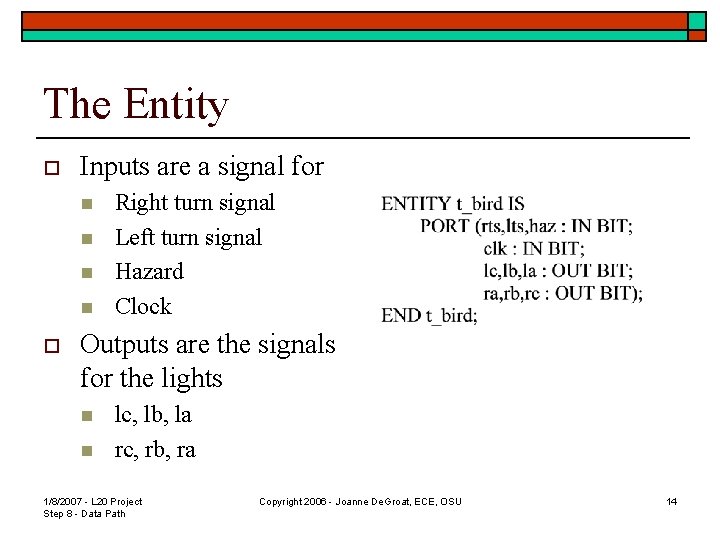

The Entity o Inputs are a signal for n n o Right turn signal Left turn signal Hazard Clock Outputs are the signals for the lights n n lc, lb, la rc, rb, ra 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 14

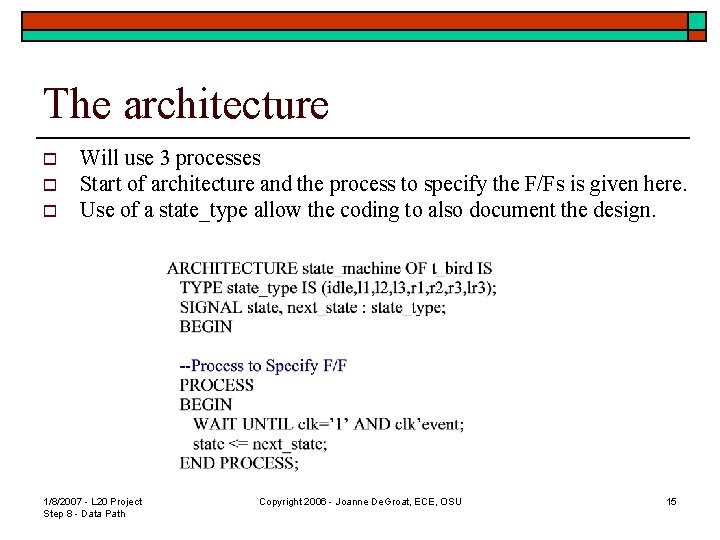

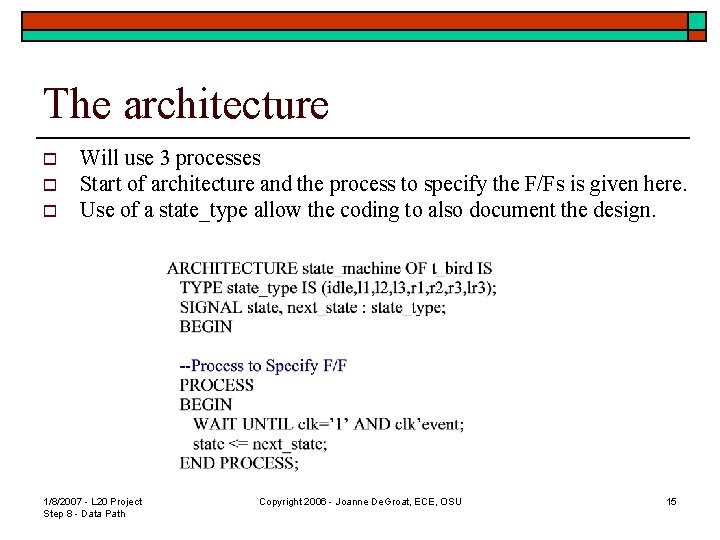

The architecture o o o Will use 3 processes Start of architecture and the process to specify the F/Fs is given here. Use of a state_type allow the coding to also document the design. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 15

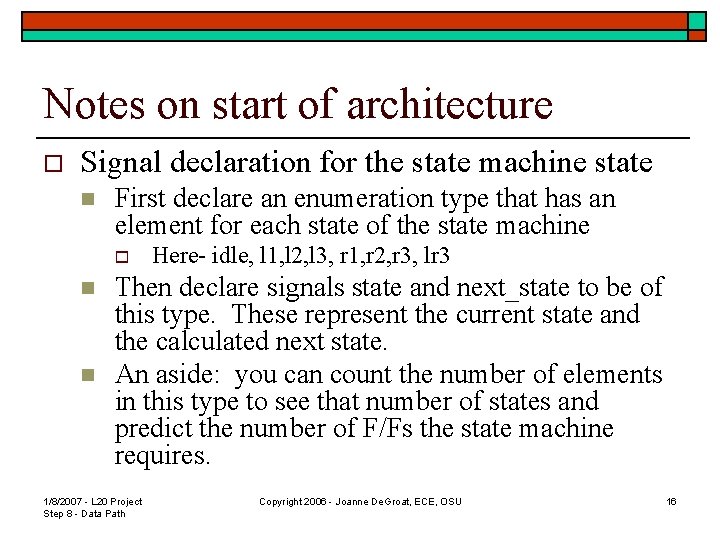

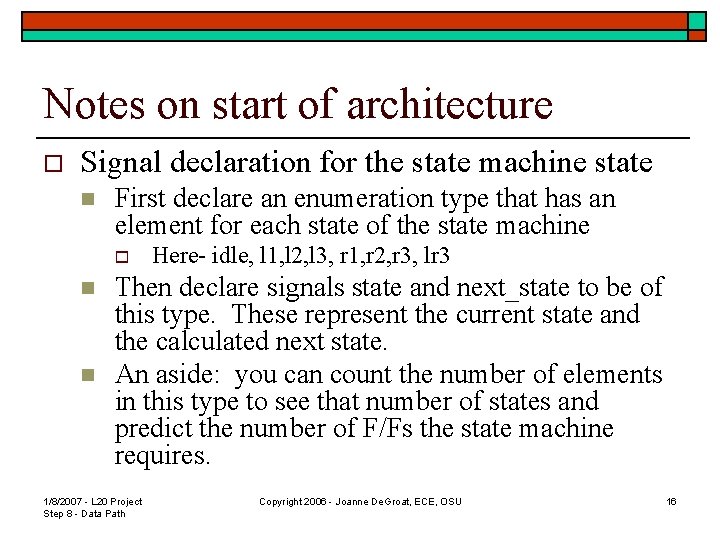

Notes on start of architecture o Signal declaration for the state machine state n First declare an enumeration type that has an element for each state of the state machine o n n Here- idle, l 1, l 2, l 3, r 1, r 2, r 3, lr 3 Then declare signals state and next_state to be of this type. These represent the current state and the calculated next state. An aside: you can count the number of elements in this type to see that number of states and predict the number of F/Fs the state machine requires. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 16

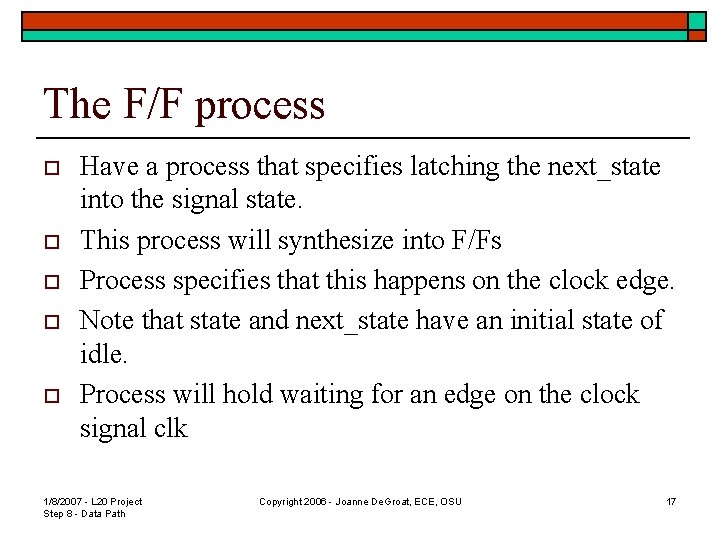

The F/F process o o o Have a process that specifies latching the next_state into the signal state. This process will synthesize into F/Fs Process specifies that this happens on the clock edge. Note that state and next_state have an initial state of idle. Process will hold waiting for an edge on the clock signal clk 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 17

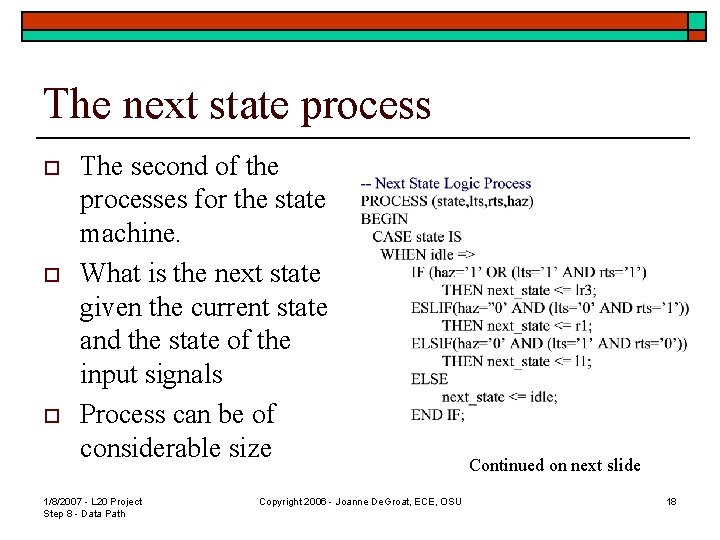

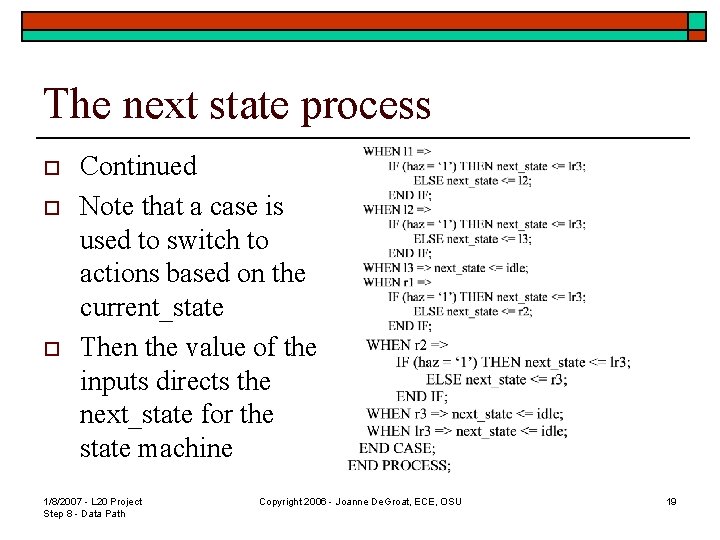

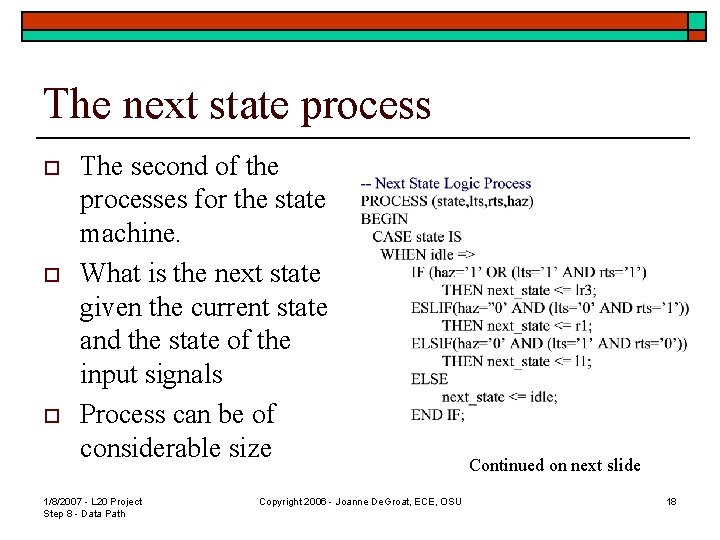

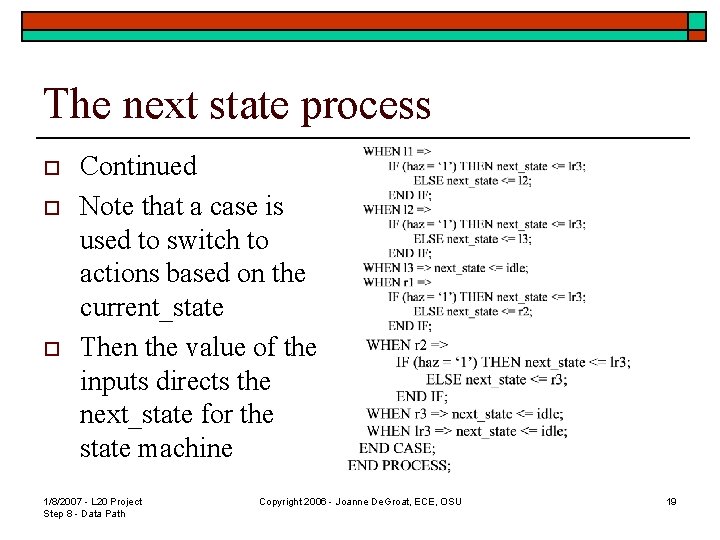

The next state process o o o The second of the processes for the state machine. What is the next state given the current state and the state of the input signals Process can be of considerable size 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU Continued on next slide 18

The next state process o o o Continued Note that a case is used to switch to actions based on the current_state Then the value of the inputs directs the next_state for the state machine 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 19

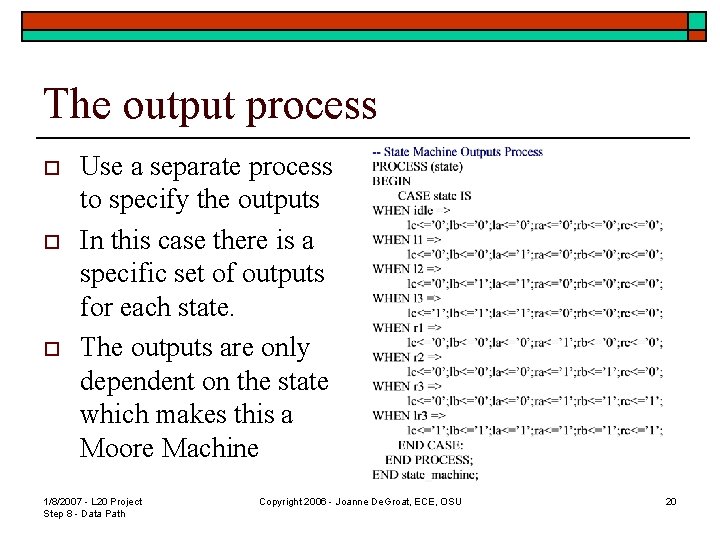

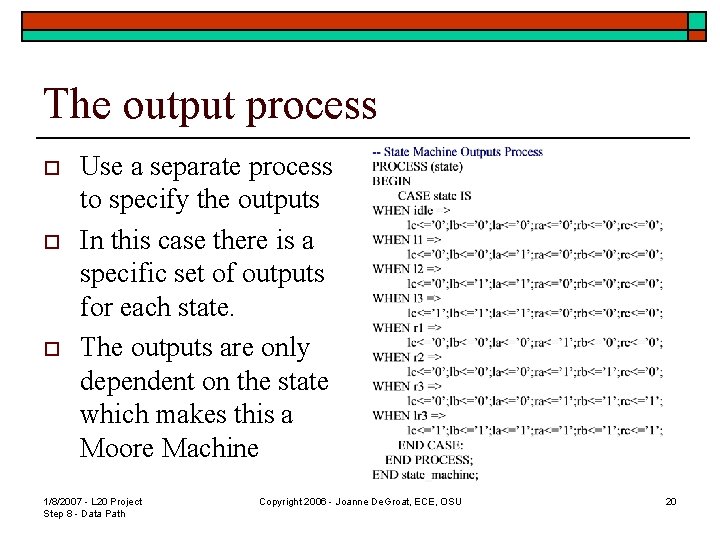

The output process o o o Use a separate process to specify the outputs In this case there is a specific set of outputs for each state. The outputs are only dependent on the state which makes this a Moore Machine 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 20

Once you have state machine description o o Simulate it in a test suite to verify the design meets specifications. This is the HDL topic of verification Then can synthesize the design to generate an FPGA implementation or use standard cells and generate the standard cells which can be sent to a place and route program for automatic generation of the circuit for a custom IC. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 21

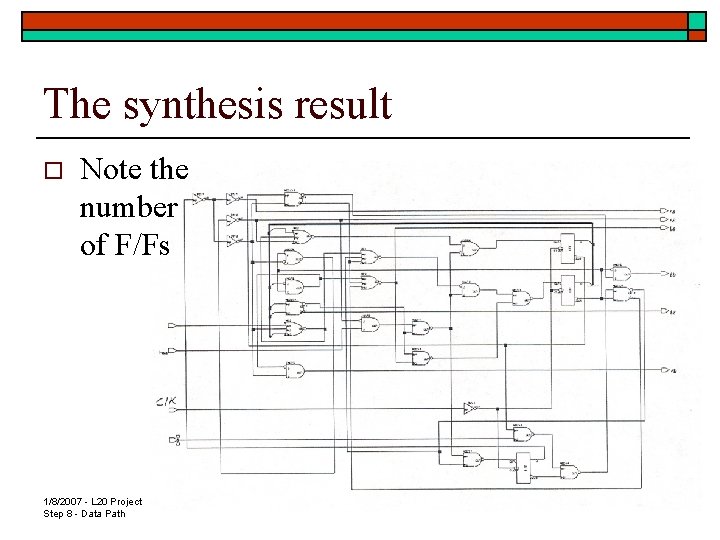

If this is done o What would you expect n o For the example you would expect 3 FFs. n o How many F/Fs? ? ? Why? There are 8 states You could even ballpark the number of gates, but that is a bit much. 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 22

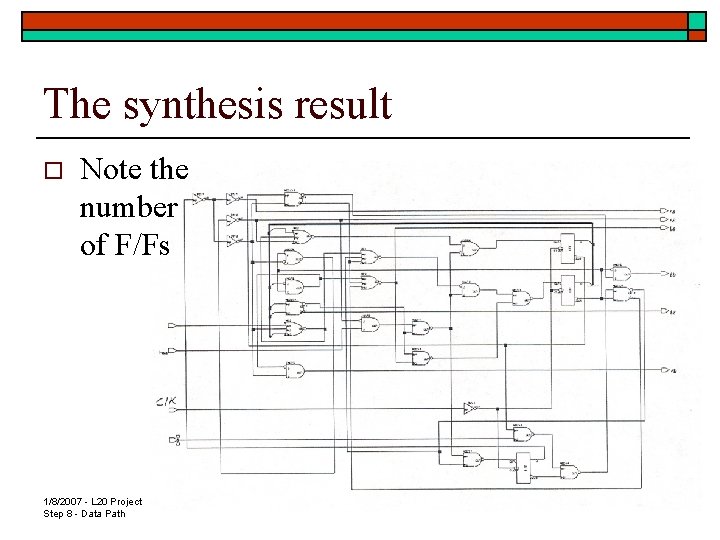

The synthesis result o Note the number of F/Fs 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 23

The VHDL Style - summary o 3 Processes n n One process for the F/Fs One process for the Next State Generation o o n Breaks down nicely using a case state structure Documents the state transitions nicely and easy to maintain One process for the Output Generation from the state or from the state and current inputs 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 24

The F/F process o The form presented in the example is a simple edge triggered latch/F/F, in this case rising edge n n PROCESS BEGIN o o n WAIT UNITL clk=‘ 1’ AND clk’event; state <= next_state; END PROCESS; 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 25

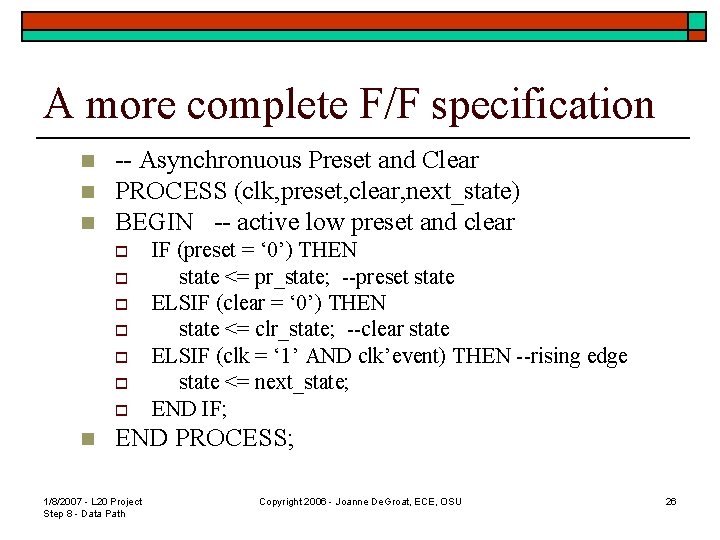

A more complete F/F specification n -- Asynchronuous Preset and Clear PROCESS (clk, preset, clear, next_state) BEGIN -- active low preset and clear o o o o n IF (preset = ‘ 0’) THEN state <= pr_state; --preset state ELSIF (clear = ‘ 0’) THEN state <= clr_state; --clear state ELSIF (clk = ‘ 1’ AND clk’event) THEN --rising edge state <= next_state; END IF; END PROCESS; 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 26

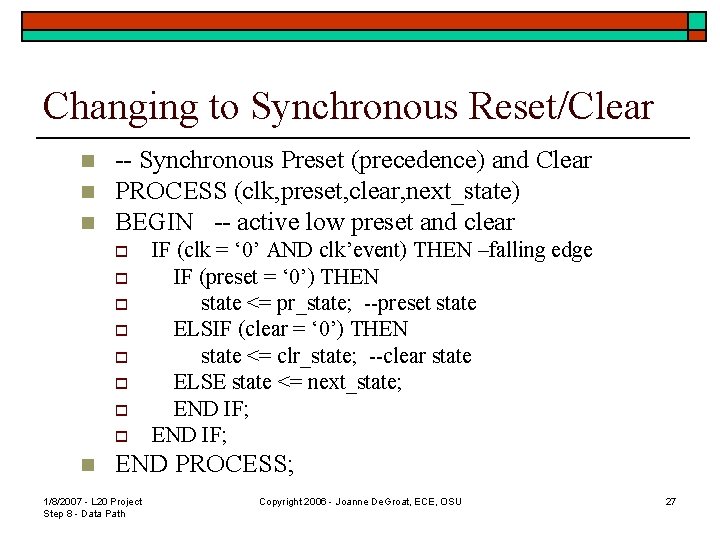

Changing to Synchronous Reset/Clear n n n -- Synchronous Preset (precedence) and Clear PROCESS (clk, preset, clear, next_state) BEGIN -- active low preset and clear o o o o n IF (clk = ‘ 0’ AND clk’event) THEN –falling edge IF (preset = ‘ 0’) THEN state <= pr_state; --preset state ELSIF (clear = ‘ 0’) THEN state <= clr_state; --clear state ELSE state <= next_state; END IF; END PROCESS; 1/8/2007 - L 20 Project Step 8 - Data Path Copyright 2006 - Joanne De. Groat, ECE, OSU 27