Staggered TwistedBundle Interconnect for Crosstalk and Delay Reduction

Staggered Twisted-Bundle Interconnect for Crosstalk and Delay Reduction Hao Yu and Lei He Electrical Engineering Dept. UCLA http//: eda. ee. ucla. edu This work is sponsored by SRC grant (1100. 001) 1

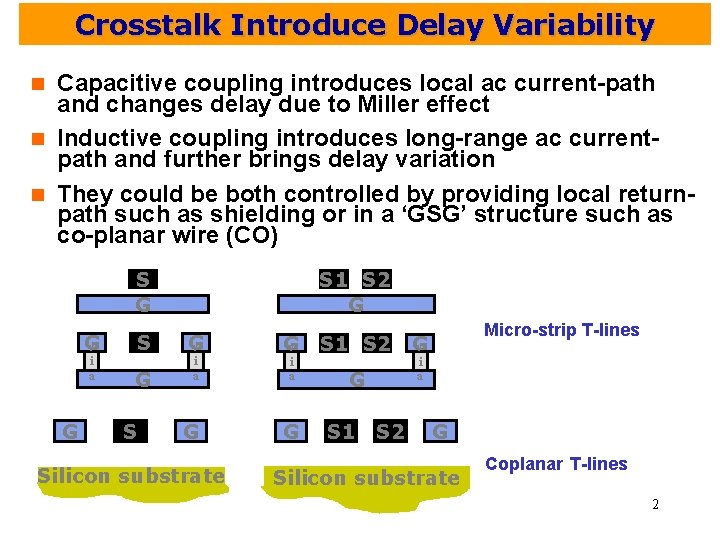

Crosstalk Introduce Delay Variability Capacitive coupling introduces local ac current-path and changes delay due to Miller effect n Inductive coupling introduces long-range ac currentpath and further brings delay variation n They could be both controlled by providing local returnpath such as shielding or in a ‘GSG’ structure such as co-planar wire (CO) n S G G v i a G S S 1 S 2 G G v i a G Silicon substrate G v i a G S 1 S 2 G v i a G S 1 Micro-strip T-lines S 2 G Silicon substrate Coplanar T-lines 2

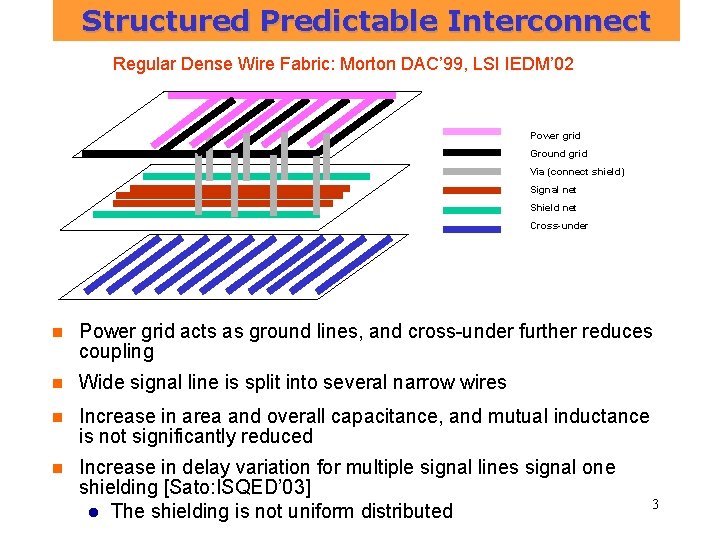

Structured Predictable Interconnect Regular Dense Wire Fabric: Morton DAC’ 99, LSI IEDM’ 02 Power grid Ground grid Via (connect shield) Signal net Shield net Cross-under n Power grid acts as ground lines, and cross-under further reduces coupling n Wide signal line is split into several narrow wires n Increase in area and overall capacitance, and mutual inductance is not significantly reduced n Increase in delay variation for multiple signal lines signal one shielding [Sato: ISQED’ 03] l The shielding is not uniform distributed 3

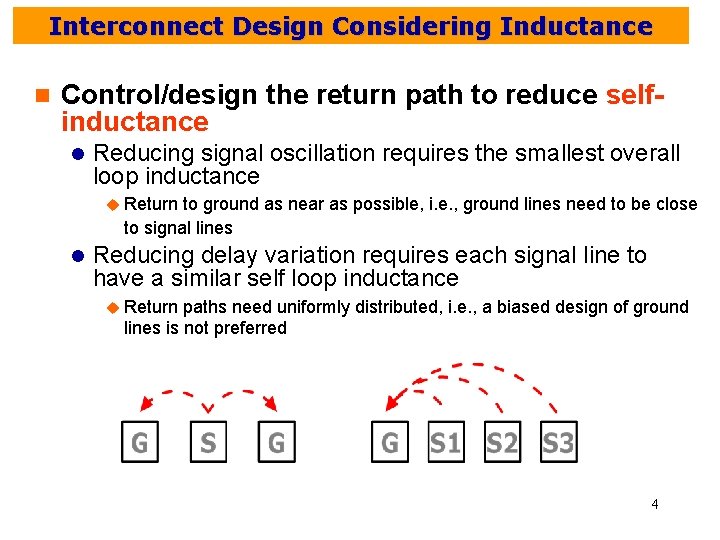

Interconnect Design Considering Inductance n Control/design the return path to reduce selfinductance l Reducing signal oscillation requires the smallest overall loop inductance u Return to ground as near as possible, i. e. , ground lines need to be close to signal lines l Reducing delay variation requires each signal line to have a similar self loop inductance u Return paths need uniformly distributed, i. e. , a biased design of ground lines is not preferred 4

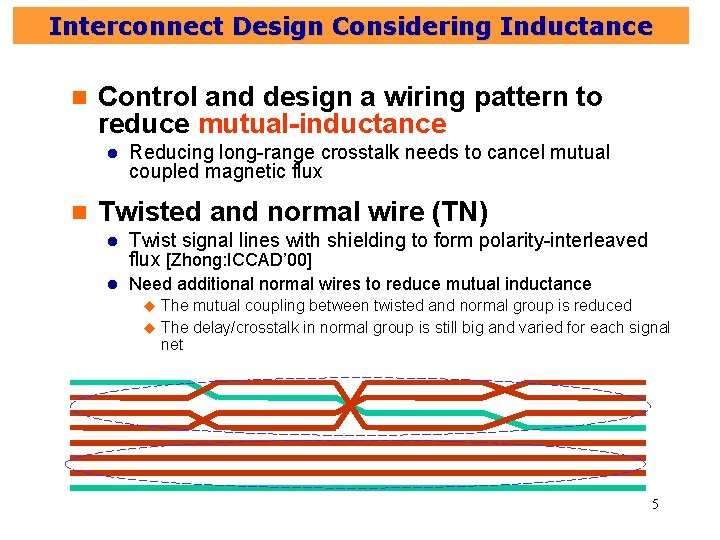

Interconnect Design Considering Inductance n Control and design a wiring pattern to reduce mutual-inductance l n Reducing long-range crosstalk needs to cancel mutual coupled magnetic flux Twisted and normal wire (TN) l Twist signal lines with shielding to form polarity-interleaved flux [Zhong: ICCAD’ 00] l Need additional normal wires to reduce mutual inductance The mutual coupling between twisted and normal group is reduced u The delay/crosstalk in normal group is still big and varied for each signal net u 5

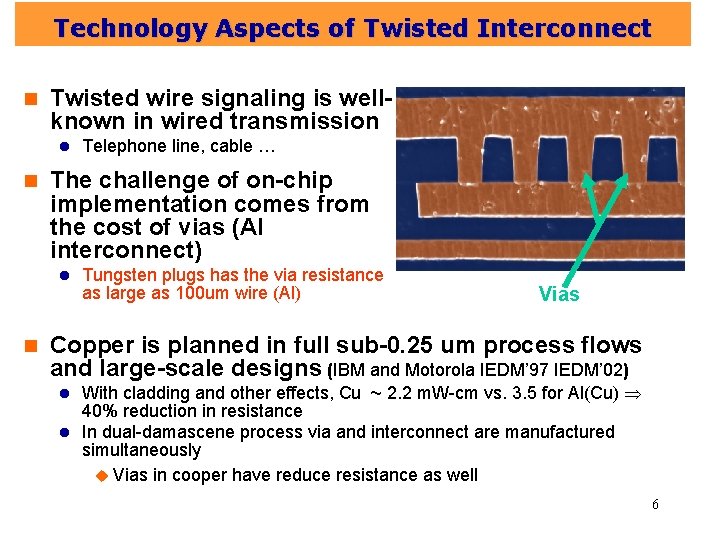

Technology Aspects of Twisted Interconnect n Twisted wire signaling is wellknown in wired transmission l n The challenge of on-chip implementation comes from the cost of vias (Al interconnect) l n Telephone line, cable … Tungsten plugs has the via resistance as large as 100 um wire (Al) Vias Copper is planned in full sub-0. 25 um process flows and large-scale designs (IBM and Motorola IEDM’ 97 IEDM’ 02) With cladding and other effects, Cu ~ 2. 2 m. W-cm vs. 3. 5 for Al(Cu) 40% reduction in resistance l In dual-damascene process via and interconnect are manufactured simultaneously u Vias in cooper have reduce resistance as well l 6

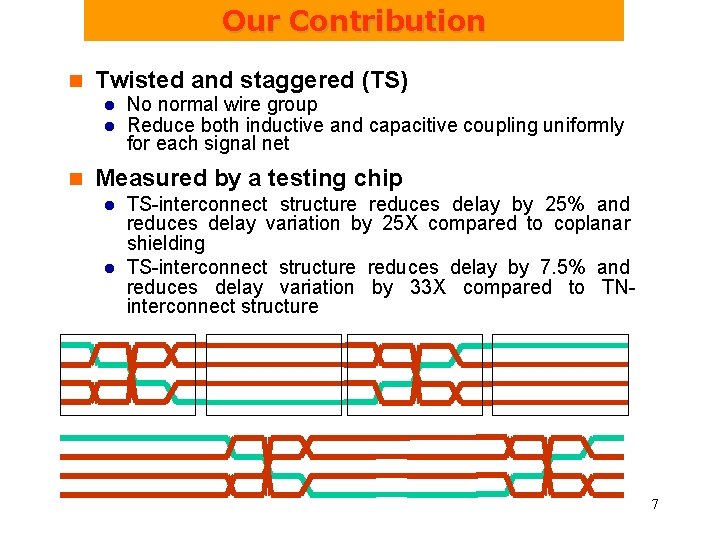

Our Contribution n Twisted and staggered (TS) l l n No normal wire group Reduce both inductive and capacitive coupling uniformly for each signal net Measured by a testing chip TS-interconnect structure reduces delay by 25% and reduces delay variation by 25 X compared to coplanar shielding l TS-interconnect structure reduces delay by 7. 5% and reduces delay variation by 33 X compared to TNinterconnect structure l 7

Outline n Motivation to design twisted wire and staggered twisted-wire n Synthesis of twisted bundle by routing matrix n Experiment results n Conclusion and future work 8

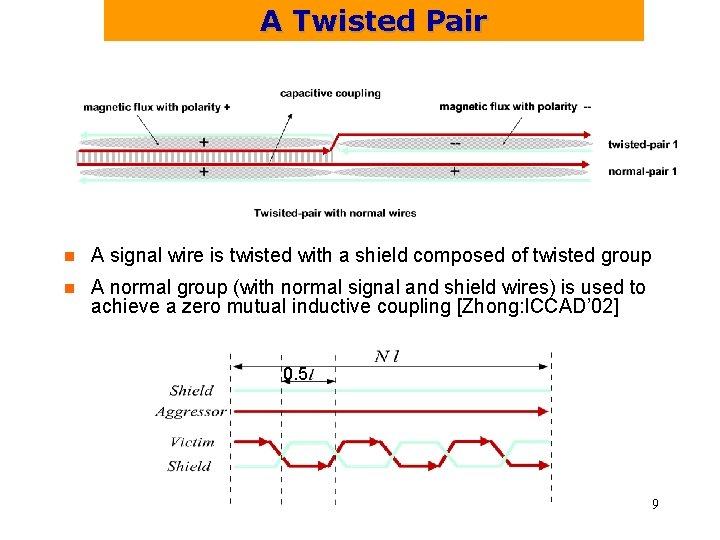

A Twisted Pair n A signal wire is twisted with a shield composed of twisted group n A normal group (with normal signal and shield wires) is used to achieve a zero mutual inductive coupling [Zhong: ICCAD’ 02] 0. 5 9

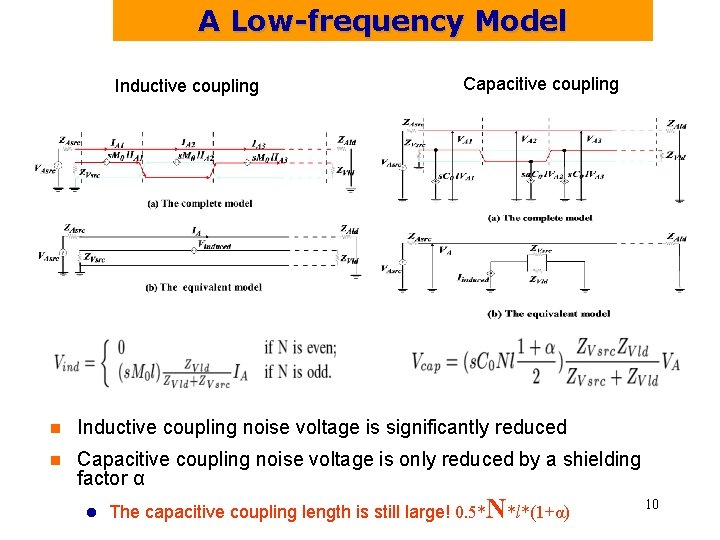

A Low-frequency Model Inductive coupling Capacitive coupling n Inductive coupling noise voltage is significantly reduced n Capacitive coupling noise voltage is only reduced by a shielding factor α l The capacitive coupling length is still large! 0. 5*N*l*(1+α) 10

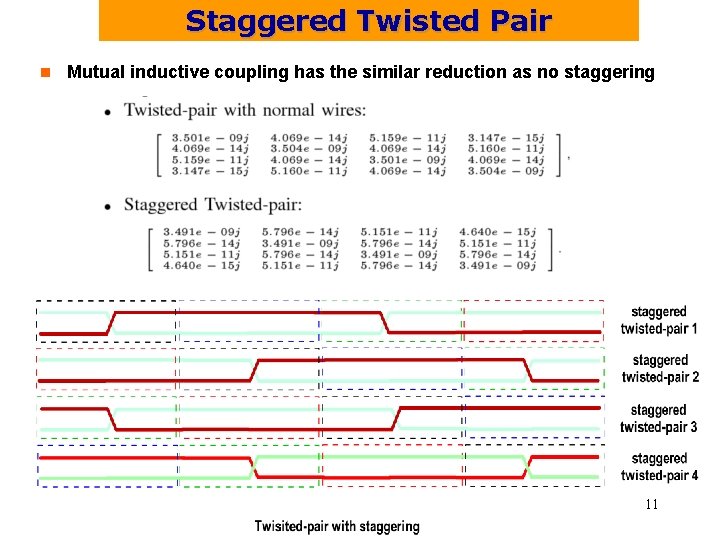

Staggered Twisted Pair n Mutual inductive coupling has the similar reduction as no staggering 11

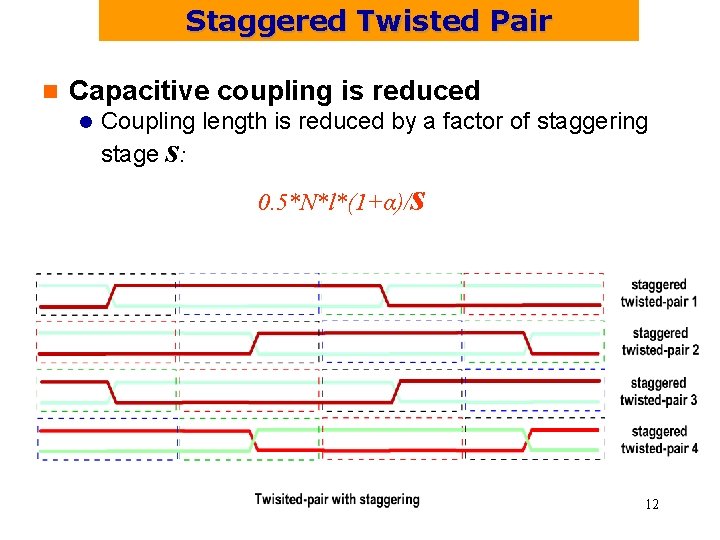

Staggered Twisted Pair n Capacitive coupling is reduced l Coupling length is reduced by a factor of staggering stage s: 0. 5*N*l*(1+α)/ s 12

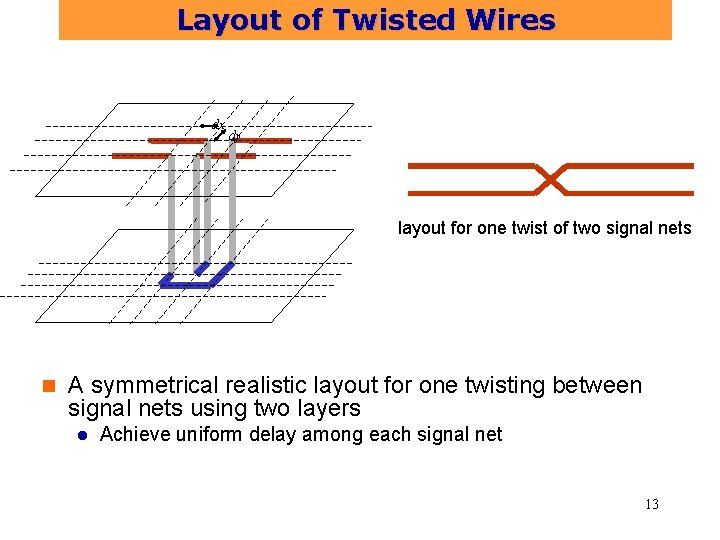

Layout of Twisted Wires dx dy layout for one twist of two signal nets n A symmetrical realistic layout for one twisting between signal nets using two layers l Achieve uniform delay among each signal net 13

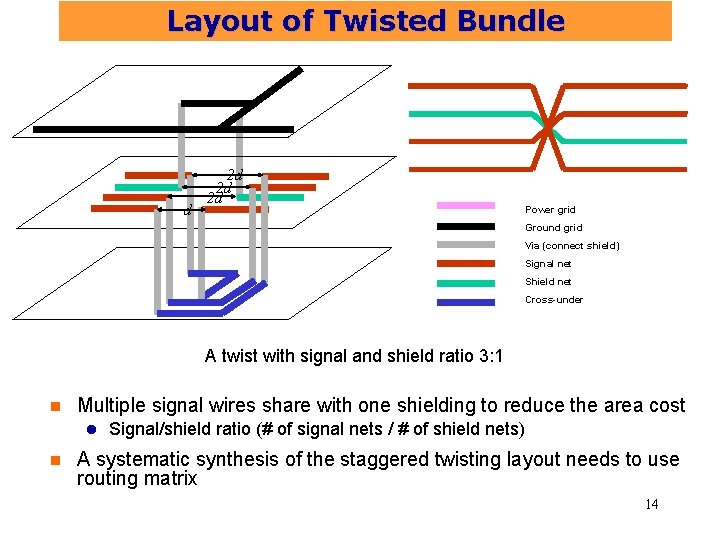

Layout of Twisted Bundle d 2 d 2 d 2 d Power grid Ground grid Via (connect shield) Signal net Shield net Cross-under A twist with signal and shield ratio 3: 1 n Multiple signal wires share with one shielding to reduce the area cost l n Signal/shield ratio (# of signal nets / # of shield nets) A systematic synthesis of the staggered twisting layout needs to use routing matrix 14

Outline n Motivation to design twisted wire and staggered twisted-wire n Synthesis of twisted bundle by routing matrix n Experiment results n Conclusion and future work 15

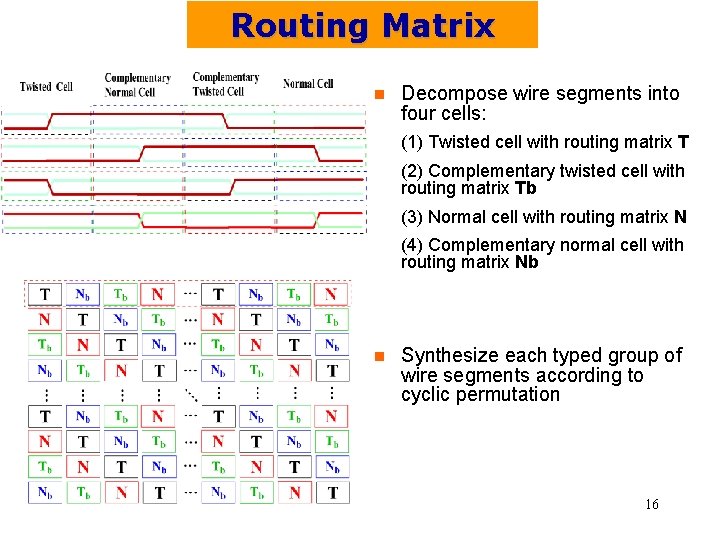

Routing Matrix n Decompose wire segments into four cells: (1) Twisted cell with routing matrix T (2) Complementary twisted cell with routing matrix Tb (3) Normal cell with routing matrix N (4) Complementary normal cell with routing matrix Nb n Synthesize each typed group of wire segments according to cyclic permutation 16

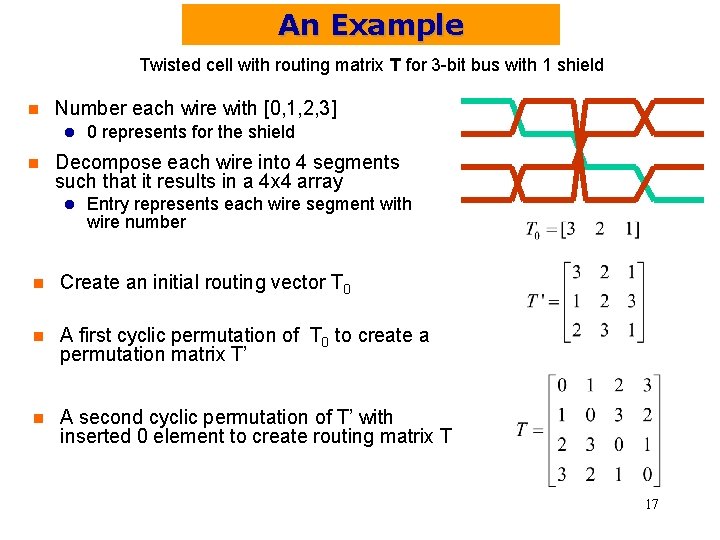

An Example Twisted cell with routing matrix T for 3 -bit bus with 1 shield n Number each wire with [0, 1, 2, 3] l n 0 represents for the shield Decompose each wire into 4 segments such that it results in a 4 x 4 array l Entry represents each wire segment with wire number n Create an initial routing vector T 0 n A first cyclic permutation of T 0 to create a permutation matrix T’ n A second cyclic permutation of T’ with inserted 0 element to create routing matrix T 17

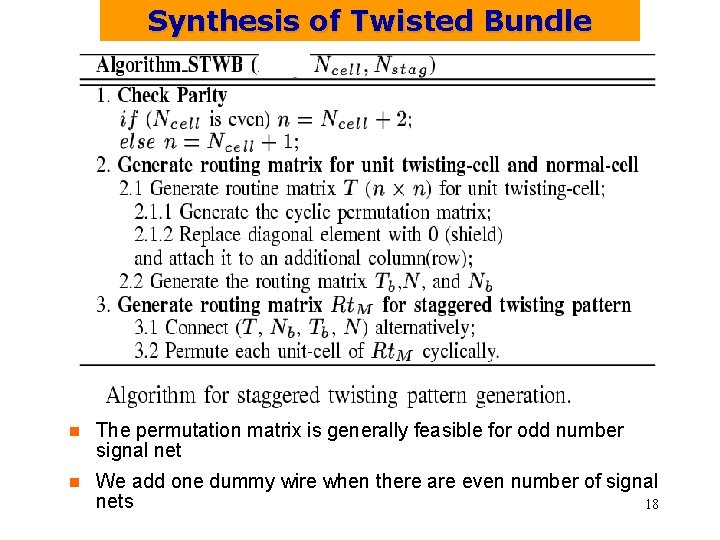

Synthesis of Twisted Bundle n The permutation matrix is generally feasible for odd number signal net n We add one dummy wire when there are even number of signal nets 18

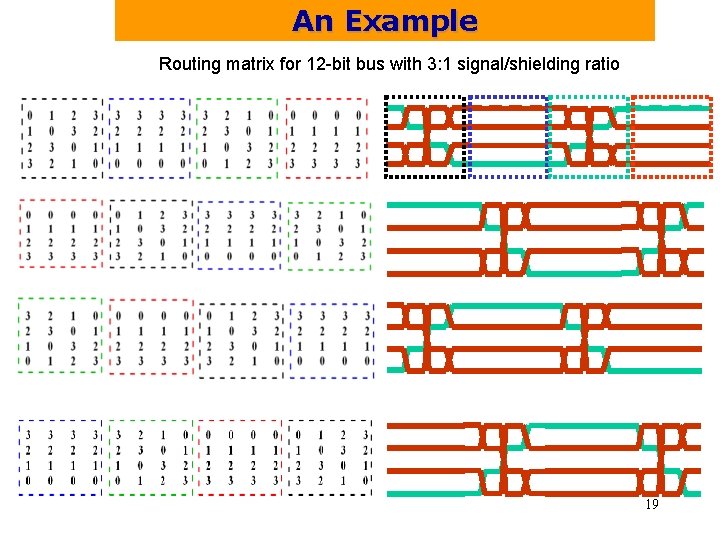

An Example Routing matrix for 12 -bit bus with 3: 1 signal/shielding ratio 19

Outline n Motivation to design twisted wire and staggered twisted-wire n Synthesis of twisted bundle by routing matrix n Experiment results n Conclusion and future work 20

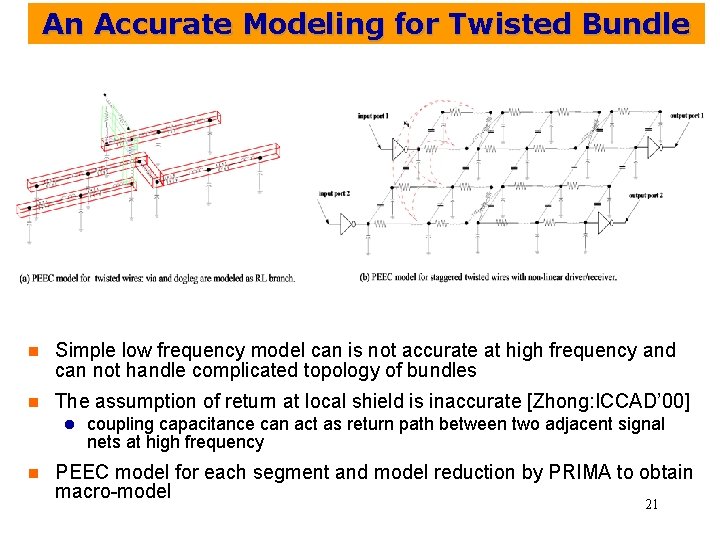

An Accurate Modeling for Twisted Bundle n Simple low frequency model can is not accurate at high frequency and can not handle complicated topology of bundles n The assumption of return at local shield is inaccurate [Zhong: ICCAD’ 00] l n coupling capacitance can act as return path between two adjacent signal nets at high frequency PEEC model for each segment and model reduction by PRIMA to obtain macro-model 21

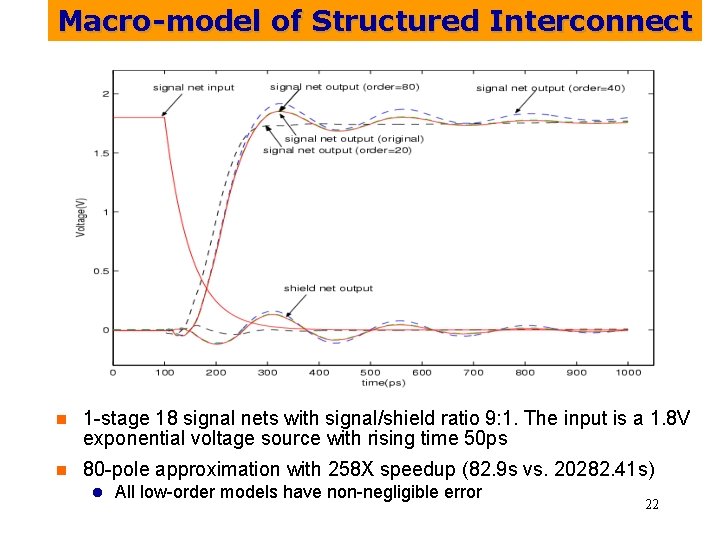

Macro-model of Structured Interconnect n 1 -stage 18 signal nets with signal/shield ratio 9: 1. The input is a 1. 8 V exponential voltage source with rising time 50 ps n 80 -pole approximation with 258 X speedup (82. 9 s vs. 20282. 41 s) l All low-order models have non-negligible error 22

Experiment Settings We use 180 nm (IBM) and 70 nm (Berkeley Predictive Model) n We assume that M 6 is used to layout the signals and shields n l The via is chosen as array of the minimum size 0. 2 um^2 The driver size is about 100 X to the minimum inverter size n RLC extracted Fast. Henry/Fast. Cap n WCD/WCN determination considering inductance [Chen and He: TCAD’ 05] n 23

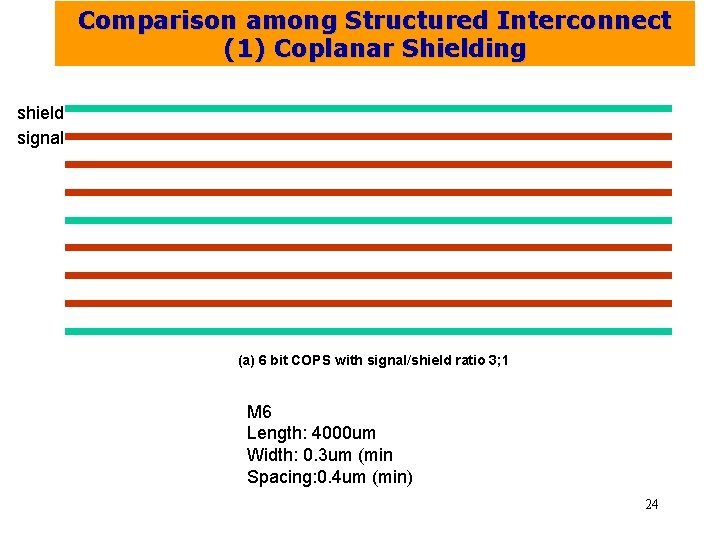

Comparison among Structured Interconnect (1) Coplanar Shielding shield signal (a) 6 bit COPS with signal/shield ratio 3; 1 M 6 Length: 4000 um Width: 0. 3 um (min Spacing: 0. 4 um (min) 24

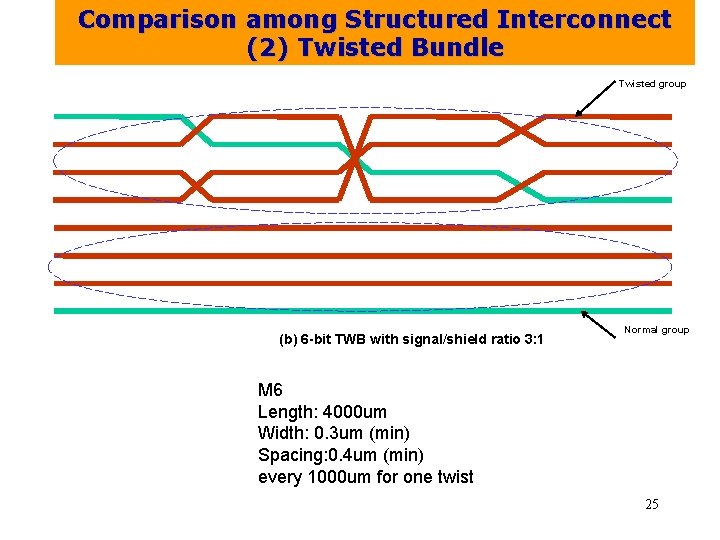

Comparison among Structured Interconnect (2) Twisted Bundle Twisted group (b) 6 -bit TWB with signal/shield ratio 3: 1 Normal group M 6 Length: 4000 um Width: 0. 3 um (min) Spacing: 0. 4 um (min) every 1000 um for one twist 25

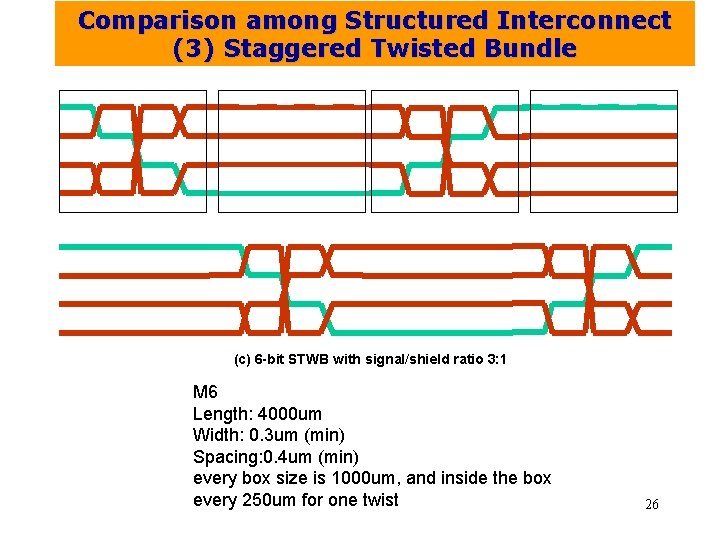

Comparison among Structured Interconnect (3) Staggered Twisted Bundle (c) 6 -bit STWB with signal/shield ratio 3: 1 M 6 Length: 4000 um Width: 0. 3 um (min) Spacing: 0. 4 um (min) every box size is 1000 um, and inside the box every 250 um for one twist 26

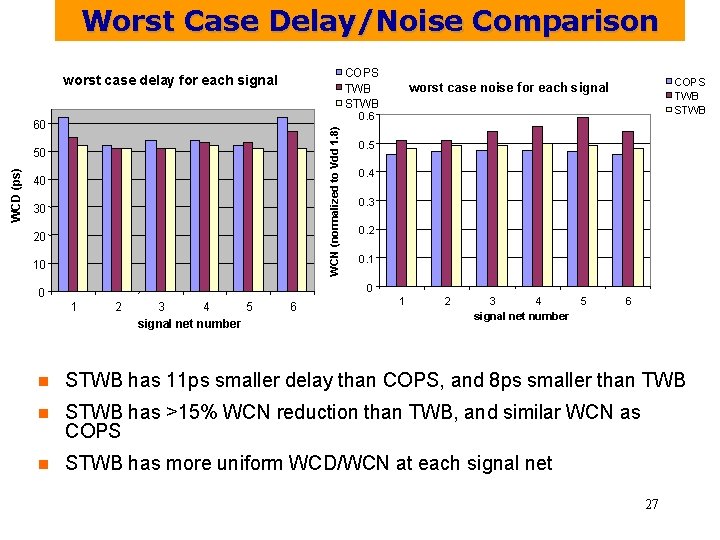

Worst Case Delay/Noise Comparison COPS TWB STWB worst case delay for each signal 0. 6 WCN (normalized to Vdd 1. 8) 60 50 WCD (ps) COPS TWB STWB worst case noise for each signal 40 30 20 10 0. 5 0. 4 0. 3 0. 2 0. 1 0 0 1 2 3 4 5 signal net number 6 1 2 3 4 signal net number 5 6 n STWB has 11 ps smaller delay than COPS, and 8 ps smaller than TWB n STWB has >15% WCN reduction than TWB, and similar WCN as COPS n STWB has more uniform WCD/WCN at each signal net 27

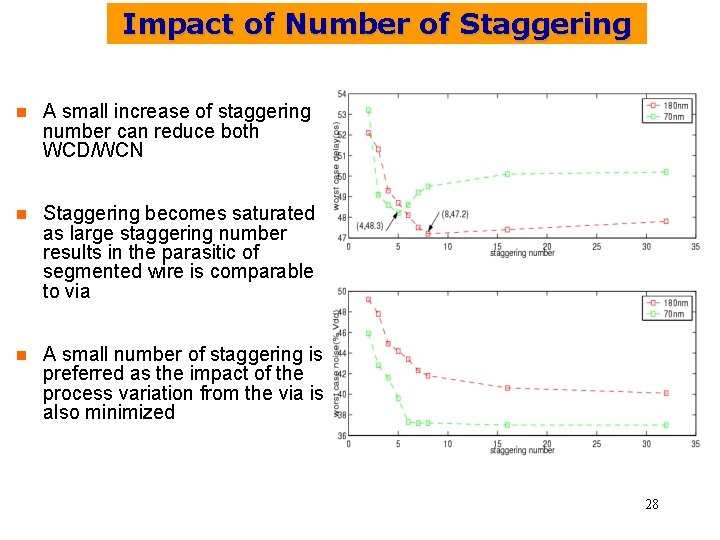

Impact of Number of Staggering n A small increase of staggering number can reduce both WCD/WCN n Staggering becomes saturated as large staggering number results in the parasitic of segmented wire is comparable to via n A small number of staggering is preferred as the impact of the process variation from the via is also minimized 28

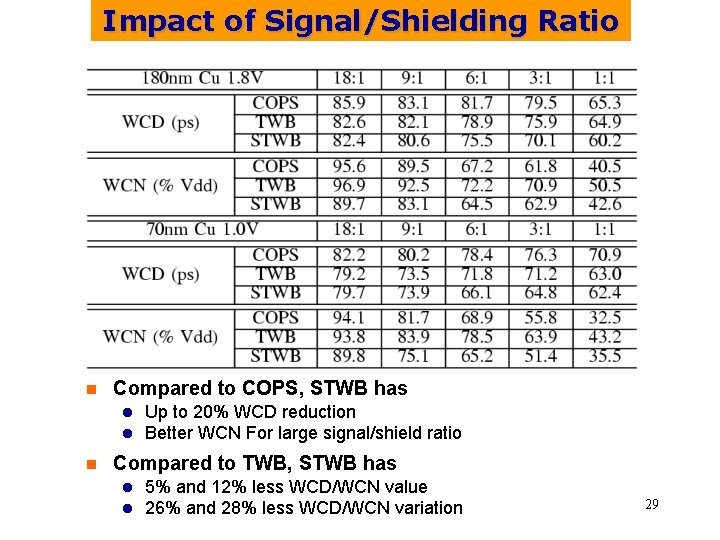

Impact of Signal/Shielding Ratio n Compared to COPS, STWB has l l n Up to 20% WCD reduction Better WCN For large signal/shield ratio Compared to TWB, STWB has l l 5% and 12% less WCD/WCN value 26% and 28% less WCD/WCN variation 29

Conclusions and Future Work n Design of structural interconnect is needed to reduce interconnect capacitance and inductance introduced delay and crosstalk n By uniformly distributing shield with twisting A staggered twisted-bundle can achieve the reduction of WCD/WCN l A staggered twisted-bundle can achieve a minimum WCD/WCN variability among each signal net l n A design of test chip is under development based on IBM 0. 13 um process 30

- Slides: 30