ST 7 Block Diagram OSC 1 OSC 2

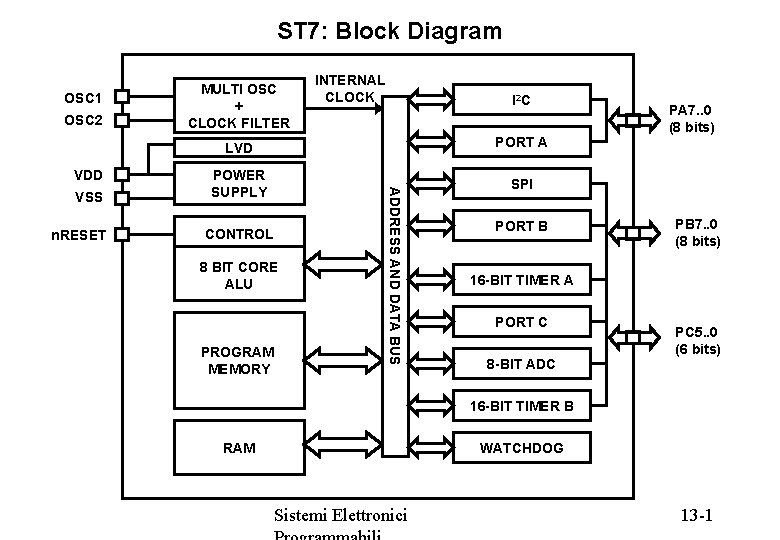

ST 7: Block Diagram OSC 1 OSC 2 VDD n. RESET INTERNAL CLOCK I 2 C LVD PORT A POWER SUPPLY SPI CONTROL 8 BIT CORE ALU PROGRAM MEMORY ADDRESS AND DATA BUS VSS MULTI OSC + CLOCK FILTER PORT B PA 7. . 0 (8 bits) PB 7. . 0 (8 bits) 16 -BIT TIMER A PORT C 8 -BIT ADC PC 5. . 0 (6 bits) 16 -BIT TIMER B RAM WATCHDOG Sistemi Elettronici 13 -1

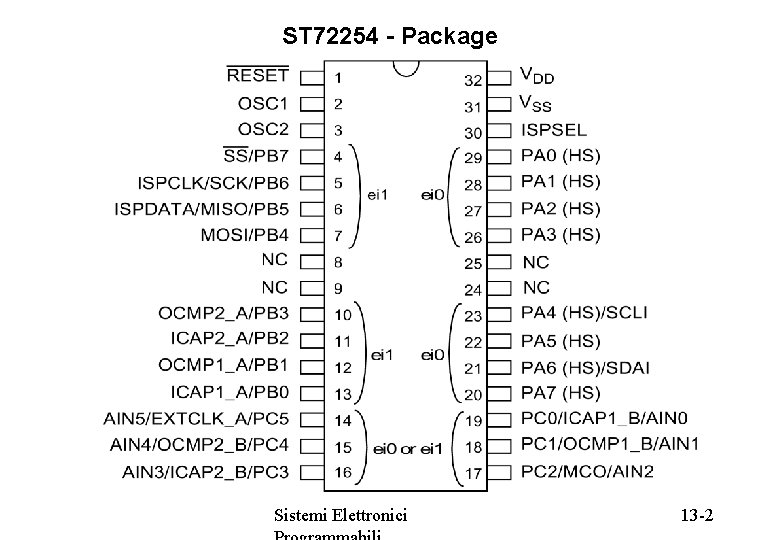

ST 72254 - Package Sistemi Elettronici 13 -2

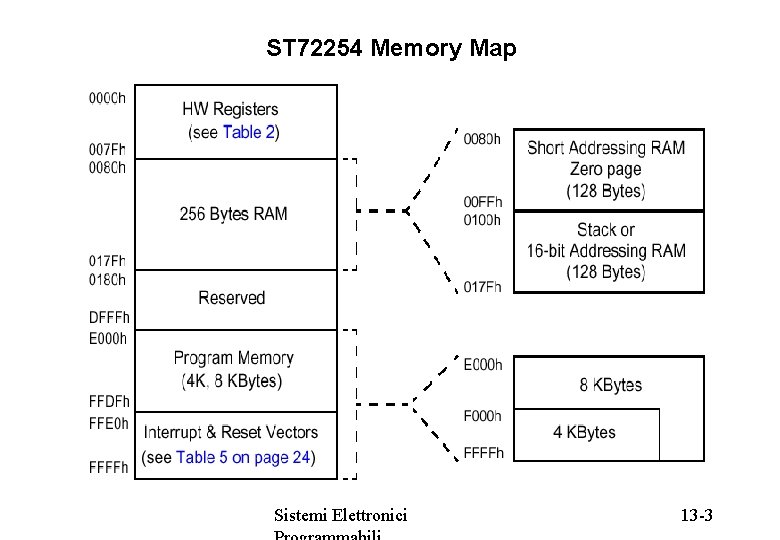

ST 72254 Memory Map Sistemi Elettronici 13 -3

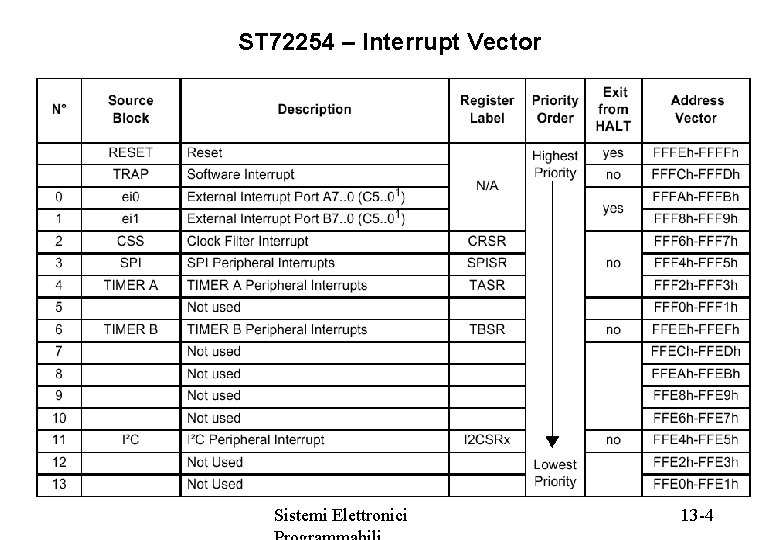

ST 72254 – Interrupt Vector Sistemi Elettronici 13 -4

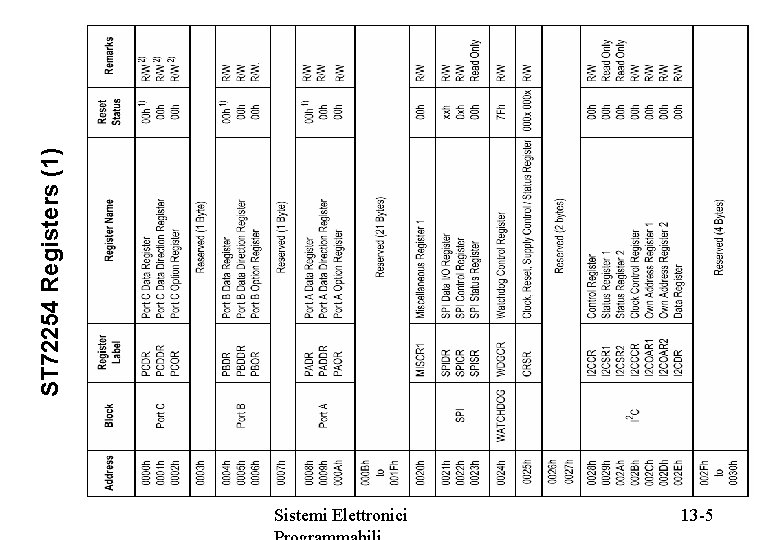

ST 72254 Registers (1) Sistemi Elettronici 13 -5

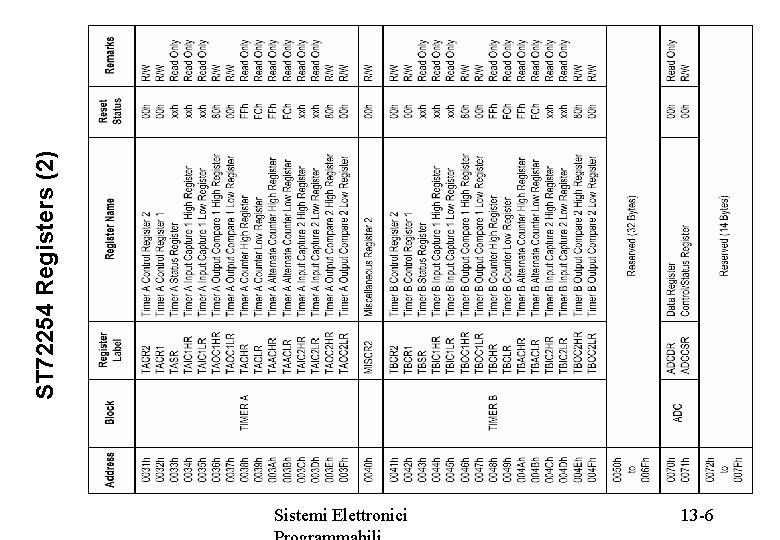

ST 72254 Registers (2) Sistemi Elettronici 13 -6

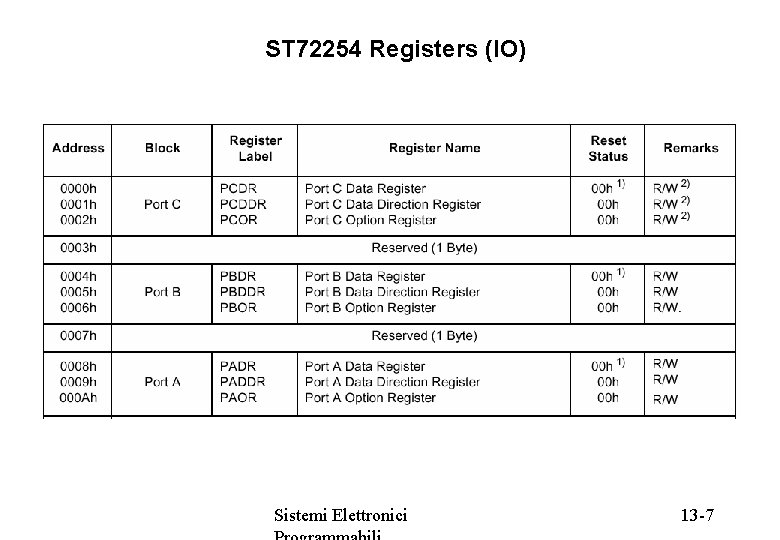

ST 72254 Registers (IO) Sistemi Elettronici 13 -7

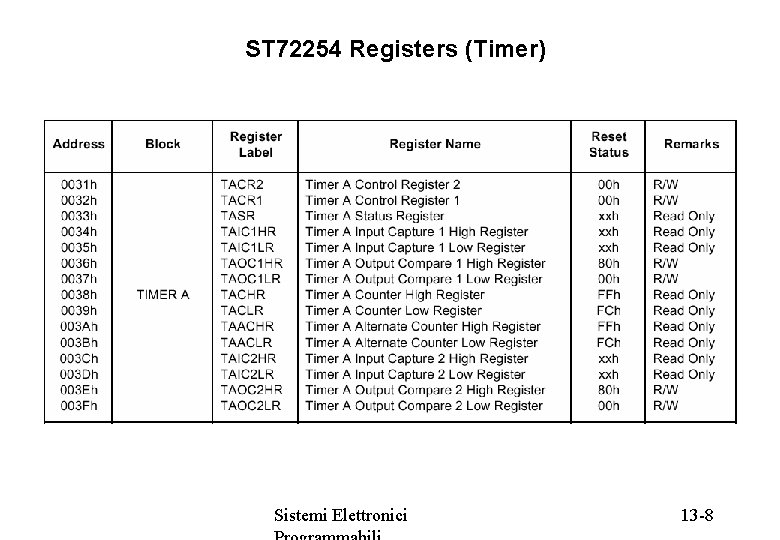

ST 72254 Registers (Timer) Sistemi Elettronici 13 -8

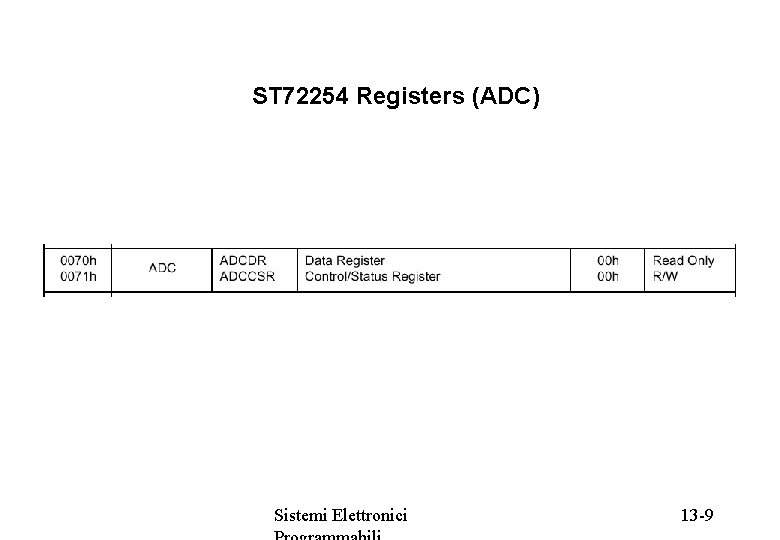

ST 72254 Registers (ADC) Sistemi Elettronici 13 -9

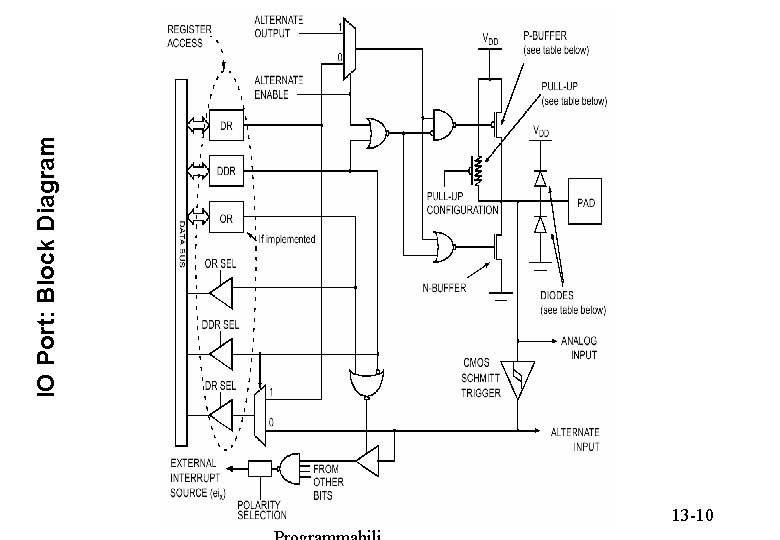

IO Port: Block Diagram Sistemi Elettronici 13 -10

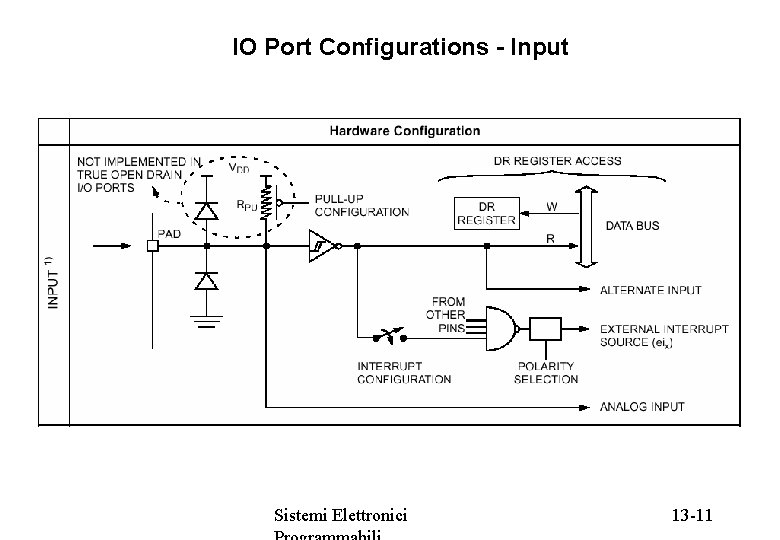

IO Port Configurations - Input Sistemi Elettronici 13 -11

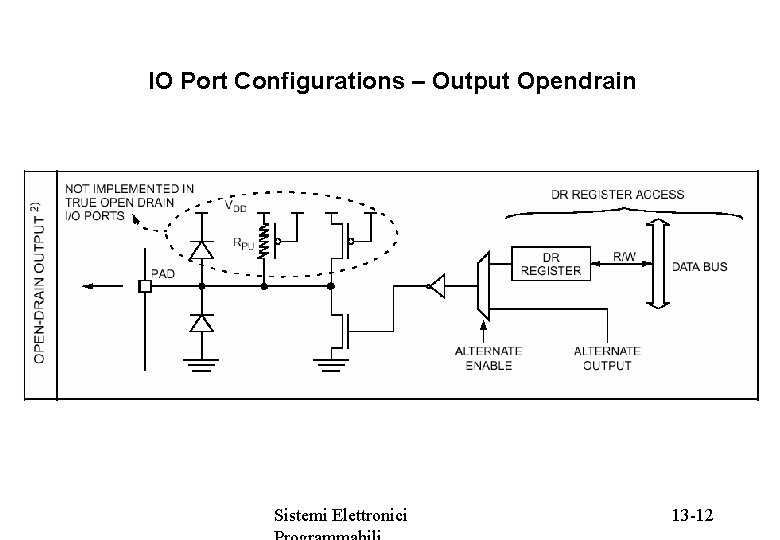

IO Port Configurations – Output Opendrain Sistemi Elettronici 13 -12

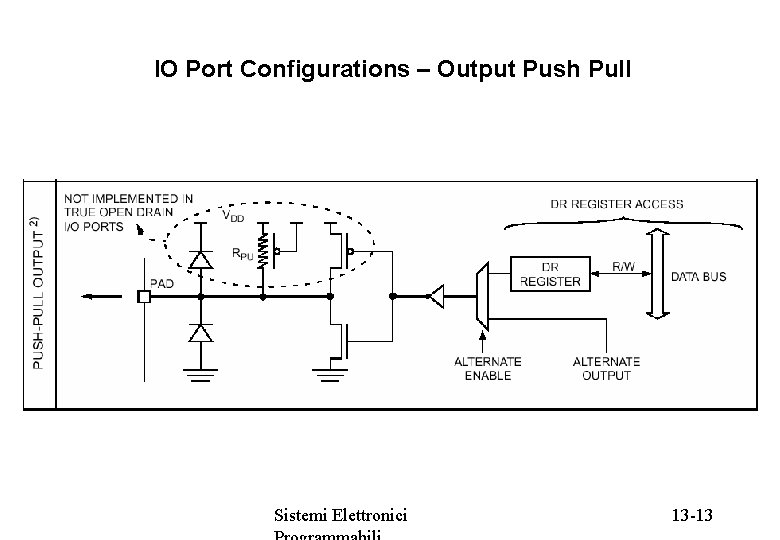

IO Port Configurations – Output Push Pull Sistemi Elettronici 13 -13

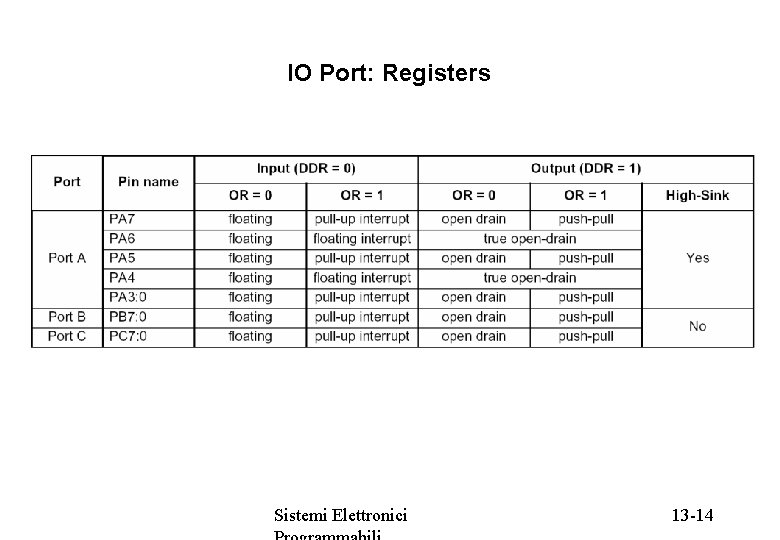

IO Port: Registers Sistemi Elettronici 13 -14

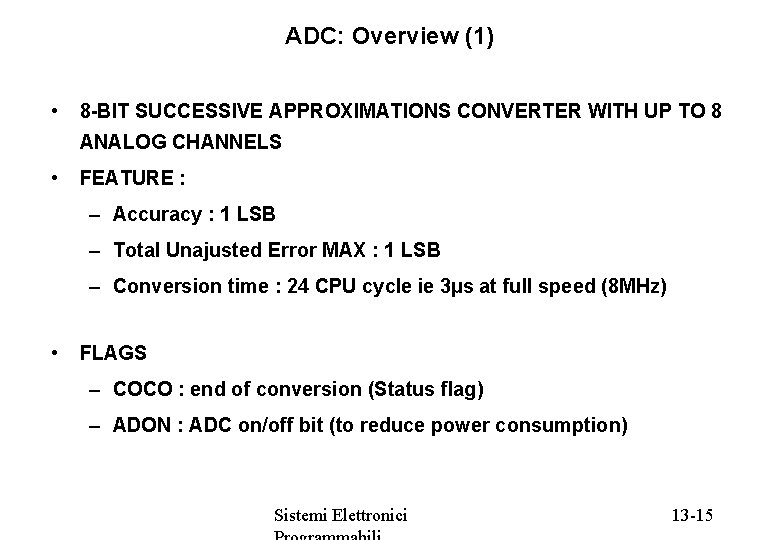

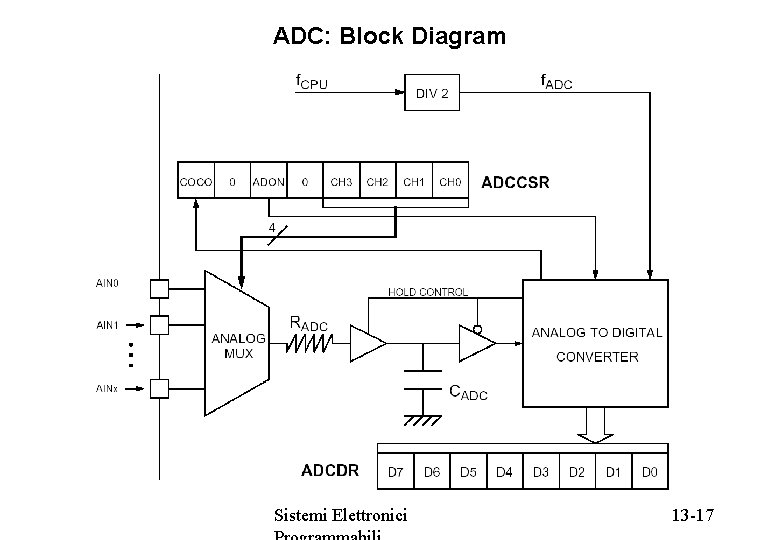

ADC: Overview (1) • 8 -BIT SUCCESSIVE APPROXIMATIONS CONVERTER WITH UP TO 8 ANALOG CHANNELS • FEATURE : – Accuracy : 1 LSB – Total Unajusted Error MAX : 1 LSB – Conversion time : 24 CPU cycle ie 3µs at full speed (8 MHz) • FLAGS – COCO : end of conversion (Status flag) – ADON : ADC on/off bit (to reduce power consumption) Sistemi Elettronici 13 -15

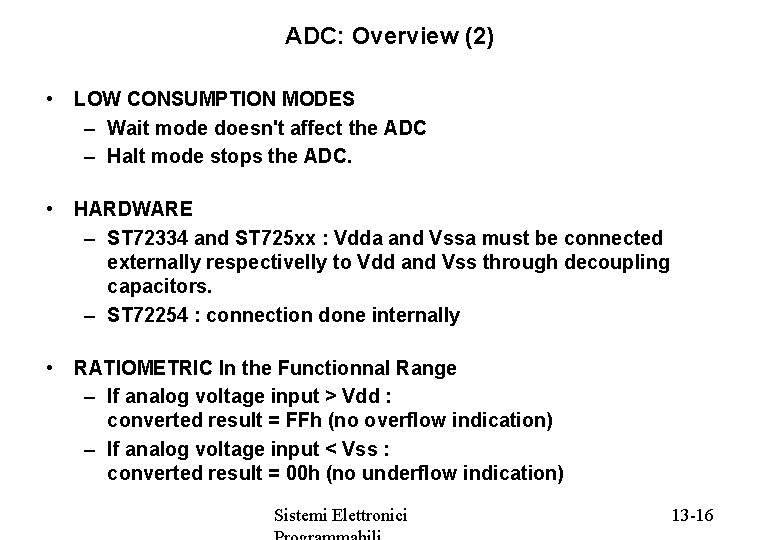

ADC: Overview (2) • LOW CONSUMPTION MODES – Wait mode doesn't affect the ADC – Halt mode stops the ADC. • HARDWARE – ST 72334 and ST 725 xx : Vdda and Vssa must be connected externally respectivelly to Vdd and Vss through decoupling capacitors. – ST 72254 : connection done internally • RATIOMETRIC In the Functionnal Range – If analog voltage input > Vdd : converted result = FFh (no overflow indication) – If analog voltage input < Vss : converted result = 00 h (no underflow indication) Sistemi Elettronici 13 -16

ADC: Block Diagram Sistemi Elettronici 13 -17

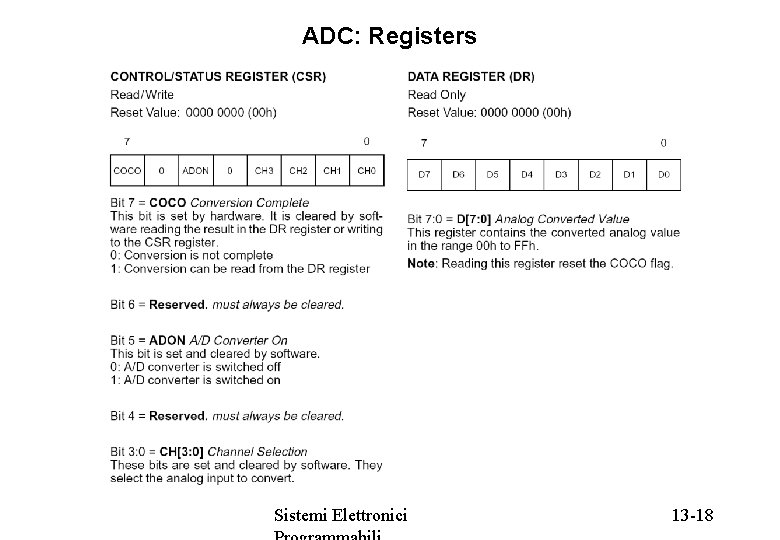

ADC: Registers Sistemi Elettronici 13 -18

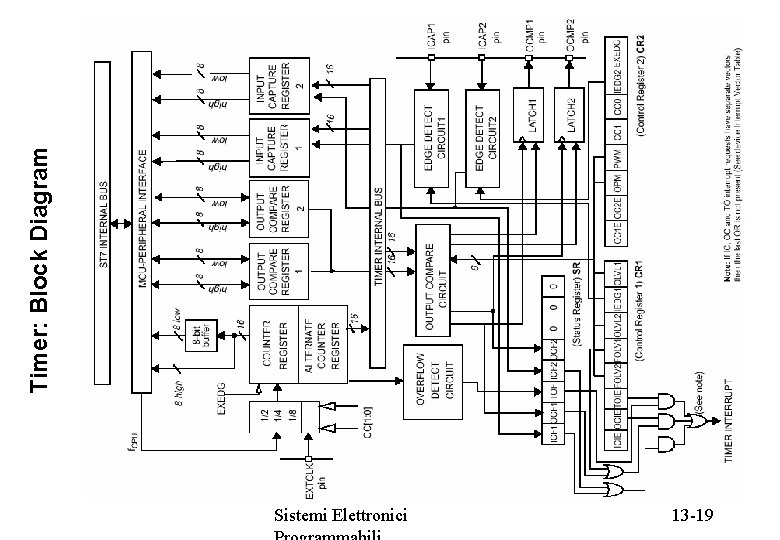

Timer: Block Diagram Sistemi Elettronici 13 -19

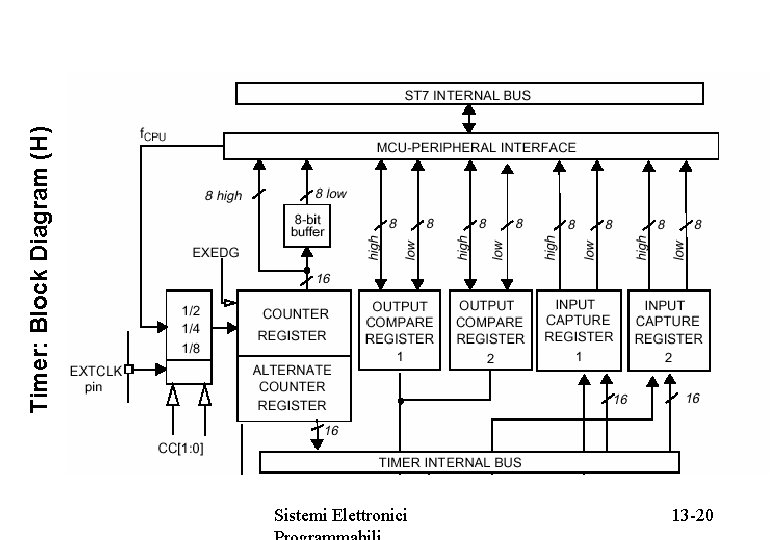

Timer: Block Diagram (H) Sistemi Elettronici 13 -20

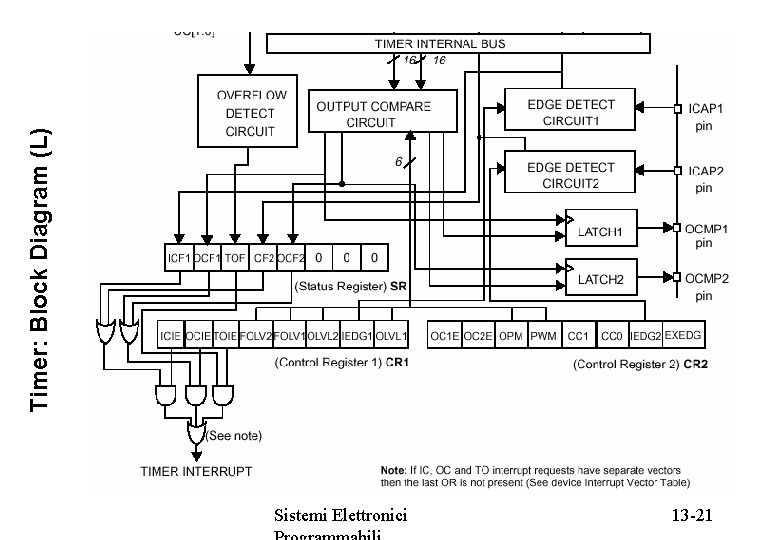

Timer: Block Diagram (L) Sistemi Elettronici 13 -21

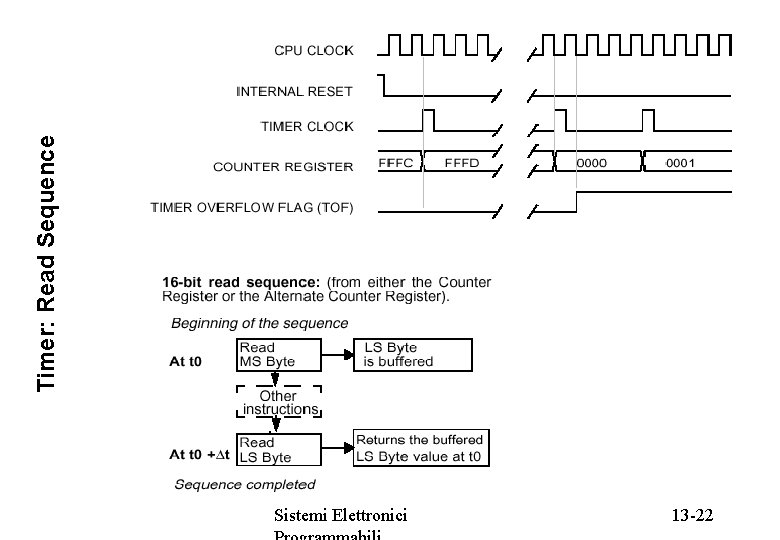

Timer: Read Sequence Sistemi Elettronici 13 -22

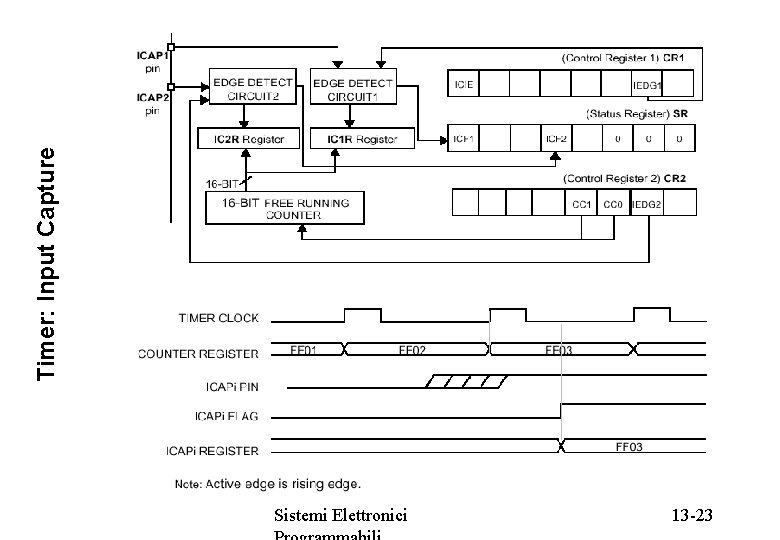

Timer: Input Capture Sistemi Elettronici 13 -23

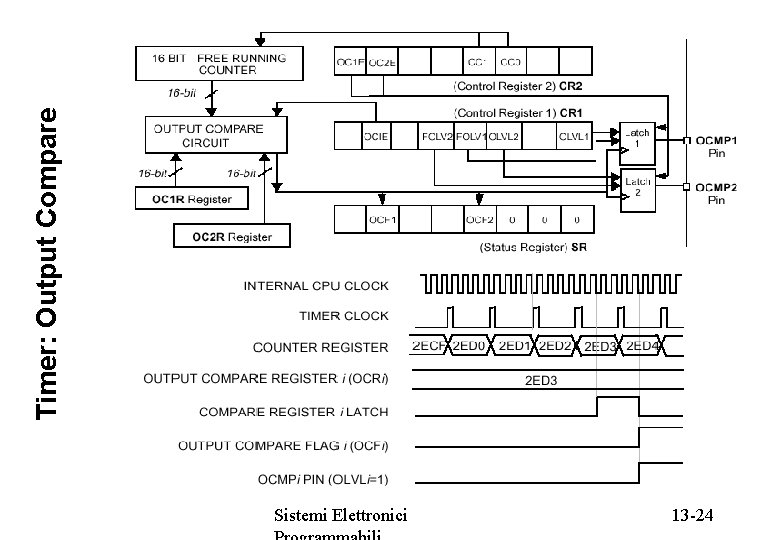

Timer: Output Compare Sistemi Elettronici 13 -24

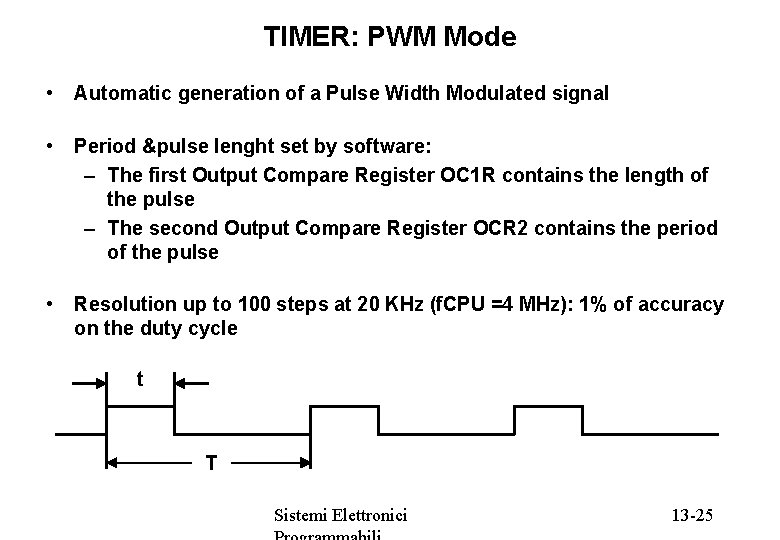

TIMER: PWM Mode • Automatic generation of a Pulse Width Modulated signal • Period &pulse lenght set by software: – The first Output Compare Register OC 1 R contains the length of the pulse – The second Output Compare Register OCR 2 contains the period of the pulse • Resolution up to 100 steps at 20 KHz (f. CPU =4 MHz): 1% of accuracy on the duty cycle t T Sistemi Elettronici 13 -25

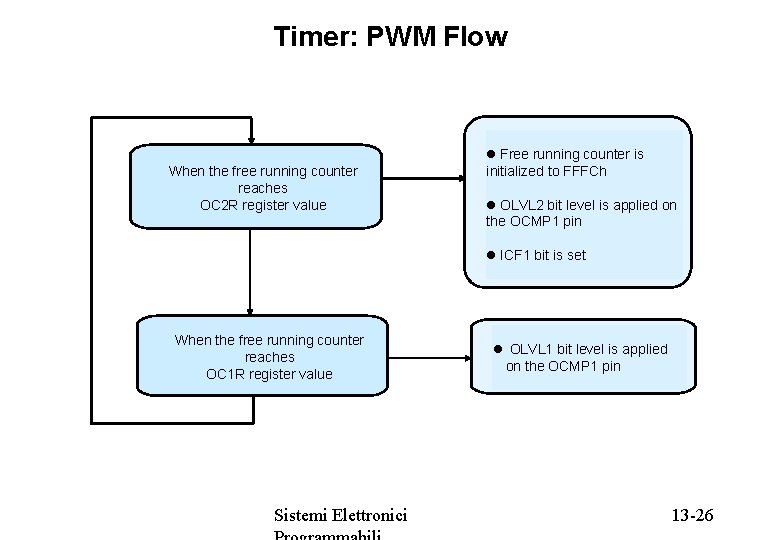

Timer: PWM Flow l Free running counter is When the free running counter reaches OC 2 R register value initialized to FFFCh l OLVL 2 bit level is applied on the OCMP 1 pin l ICF 1 bit is set When the free running counter reaches OC 1 R register value Sistemi Elettronici l OLVL 1 bit level is applied on the OCMP 1 pin 13 -26

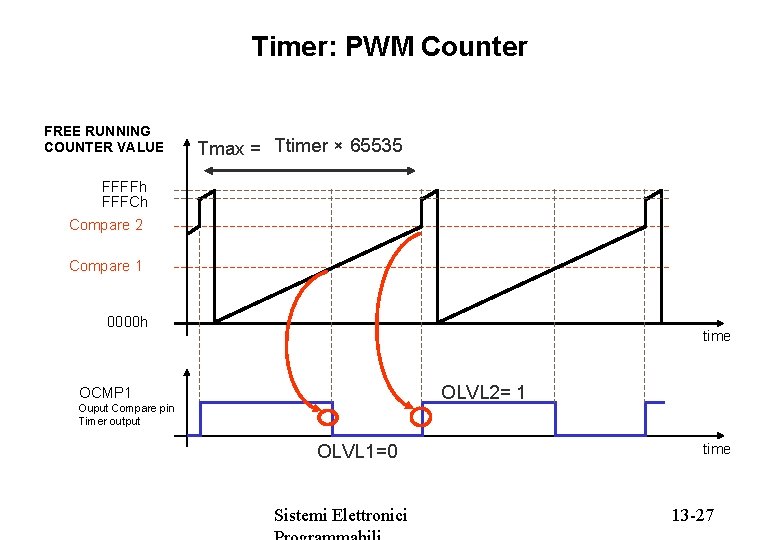

Timer: PWM Counter FREE RUNNING COUNTER VALUE Tmax = Ttimer × 65535 FFFFh FFFCh Compare 2 Compare 1 0000 h time OLVL 2= 1 OCMP 1 Ouput Compare pin Timer output OLVL 1=0 Sistemi Elettronici time 13 -27

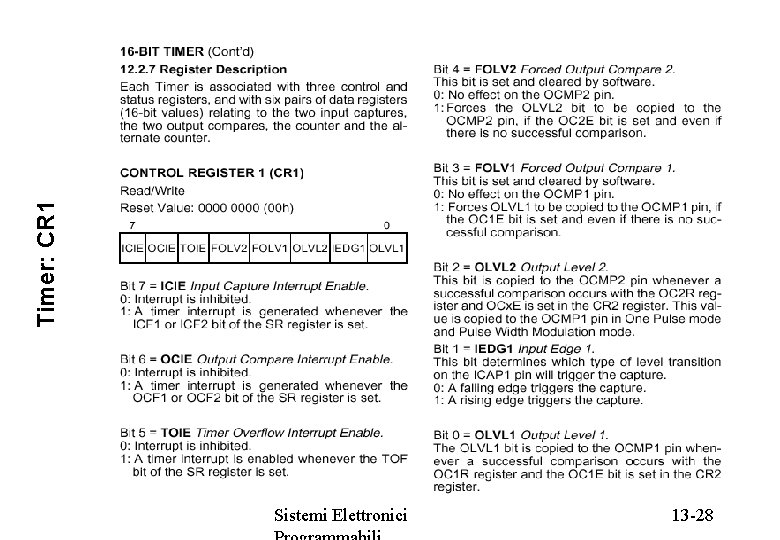

Timer: CR 1 Sistemi Elettronici 13 -28

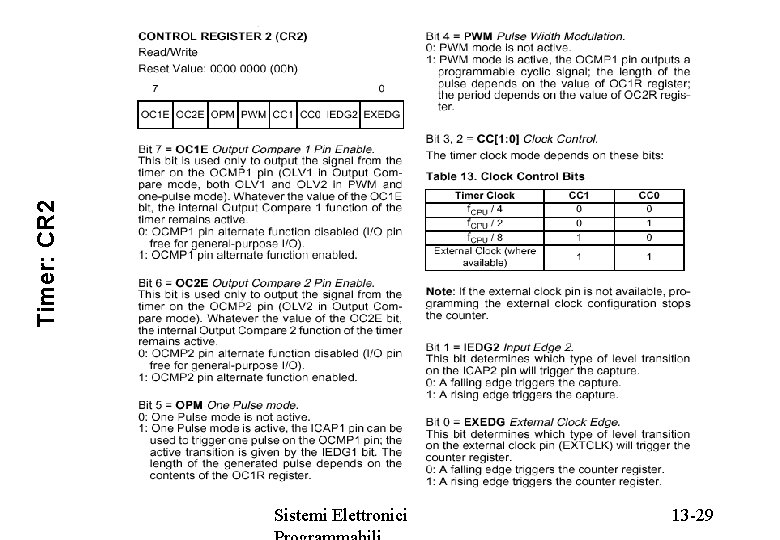

Timer: CR 2 Sistemi Elettronici 13 -29

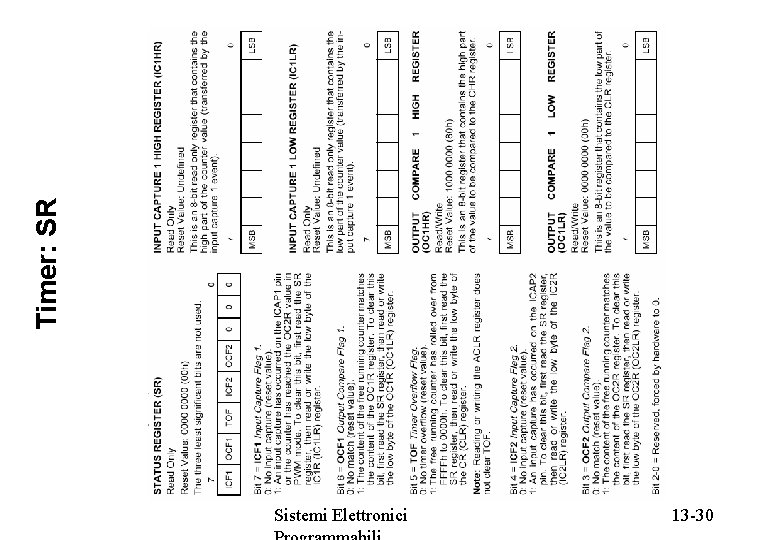

Timer: SR Sistemi Elettronici 13 -30

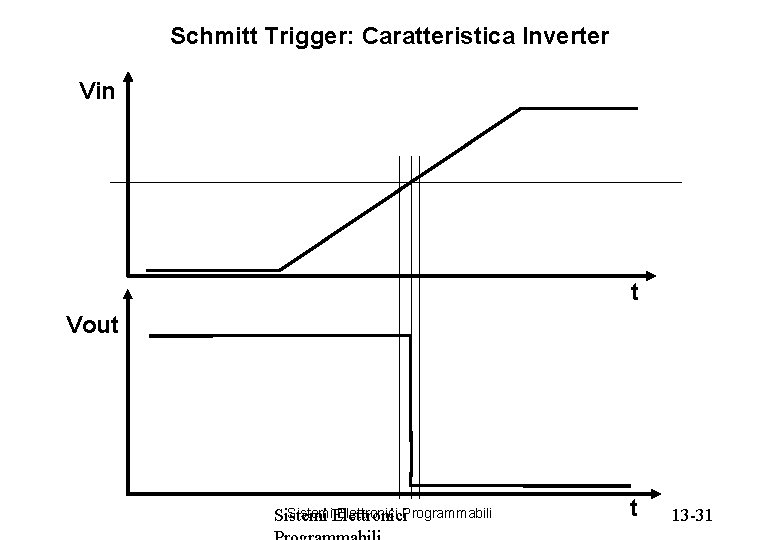

Schmitt Trigger: Caratteristica Inverter Vin t Vout Sistemi. Elettronici Programmabili Sistemi t 13 -31

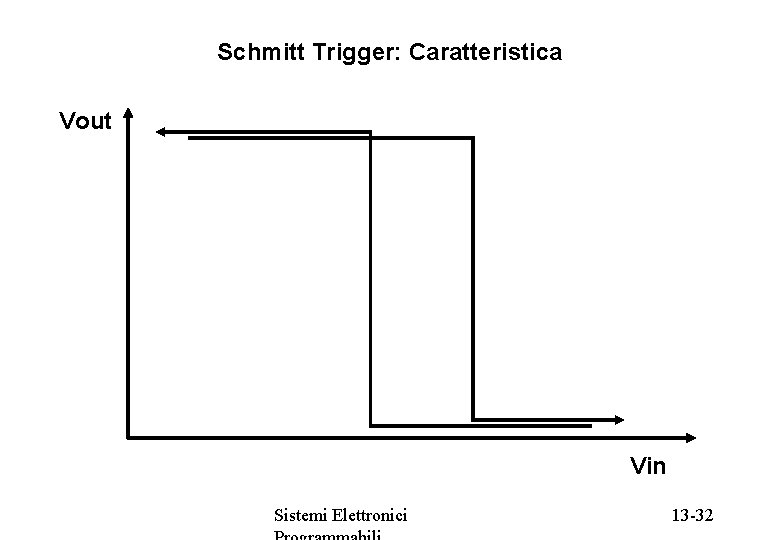

Schmitt Trigger: Caratteristica Vout Vin Sistemi Elettronici 13 -32

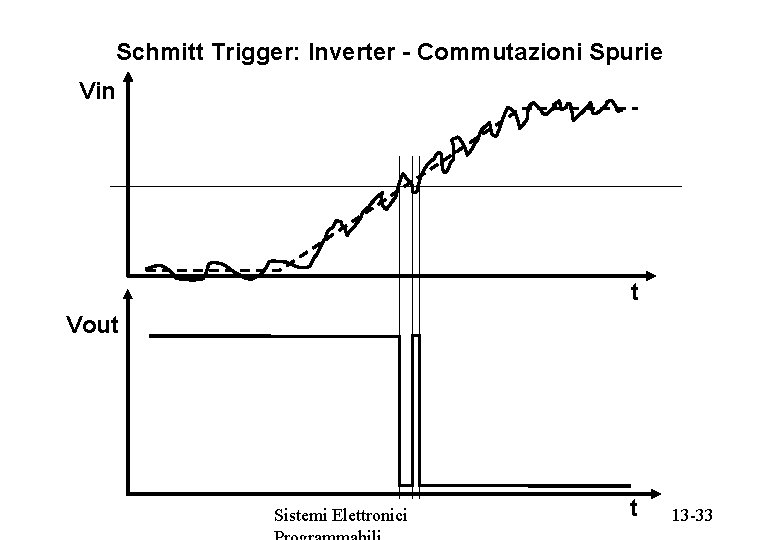

Schmitt Trigger: Inverter - Commutazioni Spurie Vin t Vout Sistemi Elettronici t 13 -33

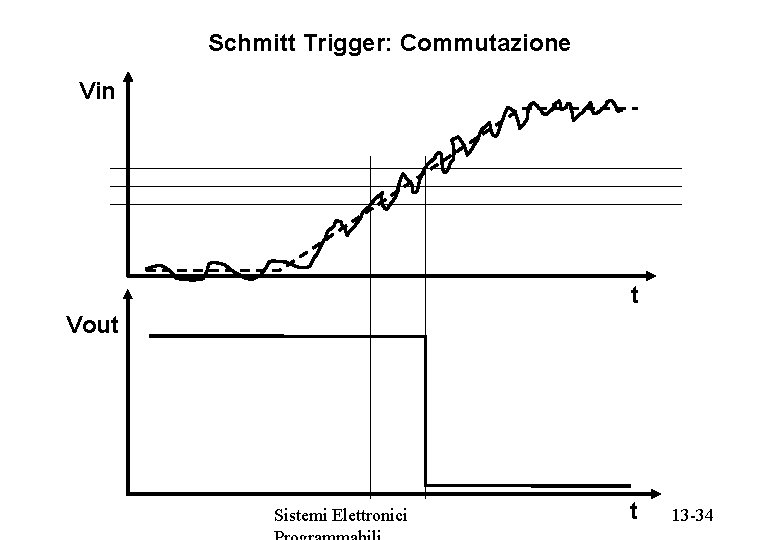

Schmitt Trigger: Commutazione Vin t Vout Sistemi Elettronici t 13 -34

- Slides: 34