SRS FrontEnd Components Sorin Martoiu CERN SRS Frontend

- Slides: 10

SRS Front-End Components Sorin Martoiu, CERN SRS Front-end Components, S. Martoiu, CERN

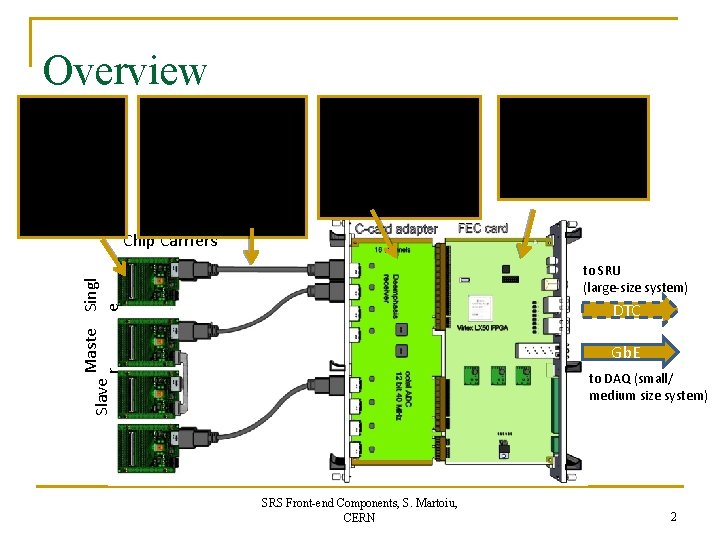

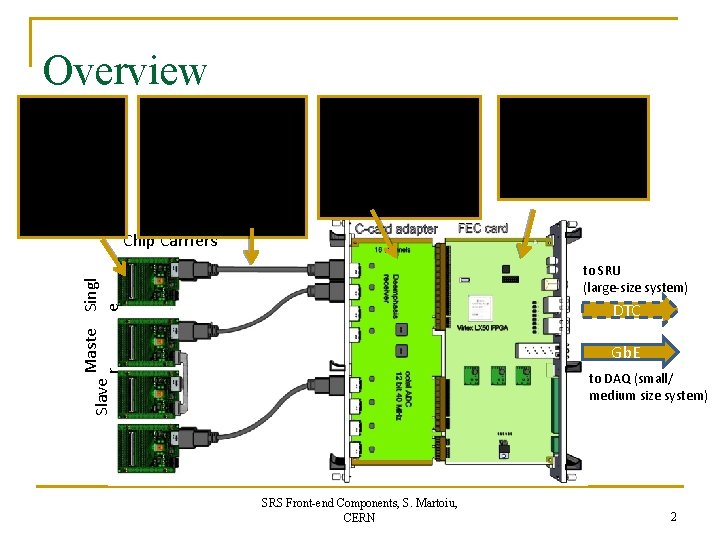

Overview Chip-links • HDMI - analog (APV/Beetle) - digital (VFAT/Beetle) • high-speed serial (VMM 1*) • … Front-end adapter (FE-specific) • ADC card • digital FE card (VFAT) • GBT receiver • … Front-end FPGA card (SRS standard) modular firmware: • SRS control • application specific Chip Carriers to SRU (large-size system) Maste Singl e r On-detector front-end hybrids • APV 25 • VFAT • BEETLE • … DTC Gb. E Slave to DAQ (small/ medium size system) SRS Front-end Components, S. Martoiu, CERN 2

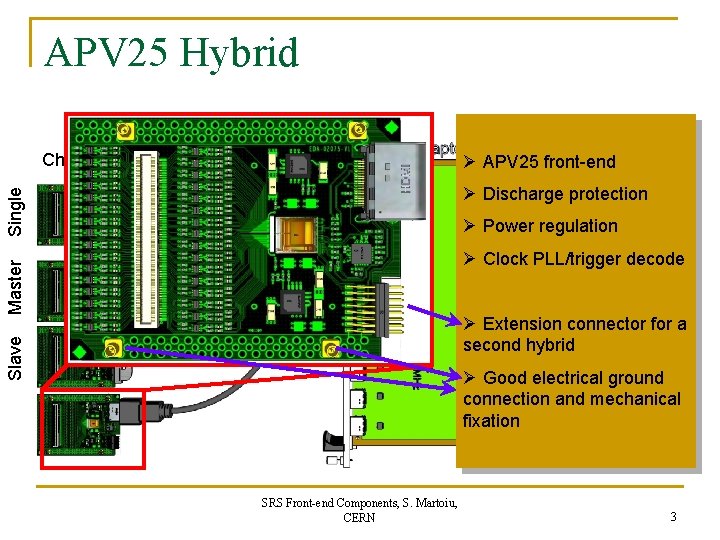

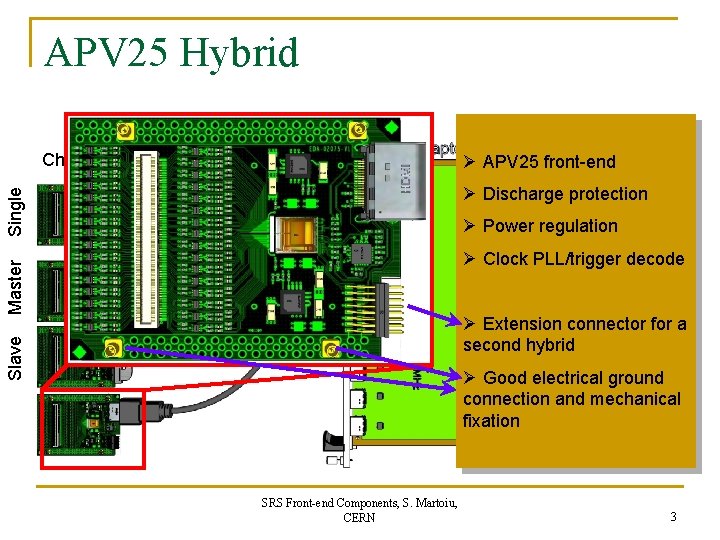

APV 25 Hybrid Chip Carriers Ø APV 25 front-end Single Ø Discharge protection Ø Power regulation Master Ø Clock PLL/trigger decode Slave Ø Extension connector for a second hybrid Ø Good electrical ground connection and mechanical fixation SRS Front-end Components, S. Martoiu, CERN 3

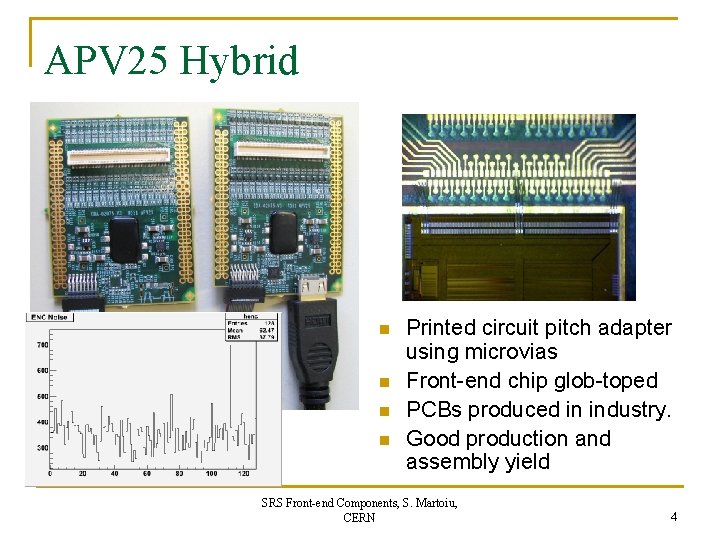

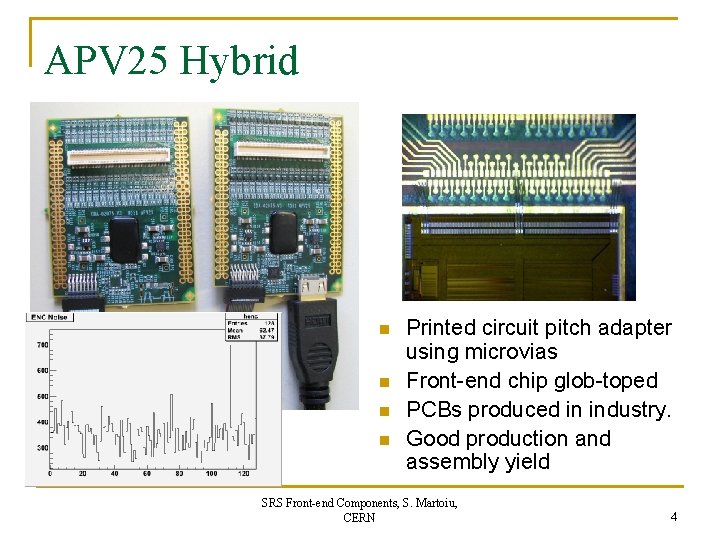

APV 25 Hybrid n n Printed circuit pitch adapter using microvias Front-end chip glob-toped PCBs produced in industry. Good production and assembly yield SRS Front-end Components, S. Martoiu, CERN 4

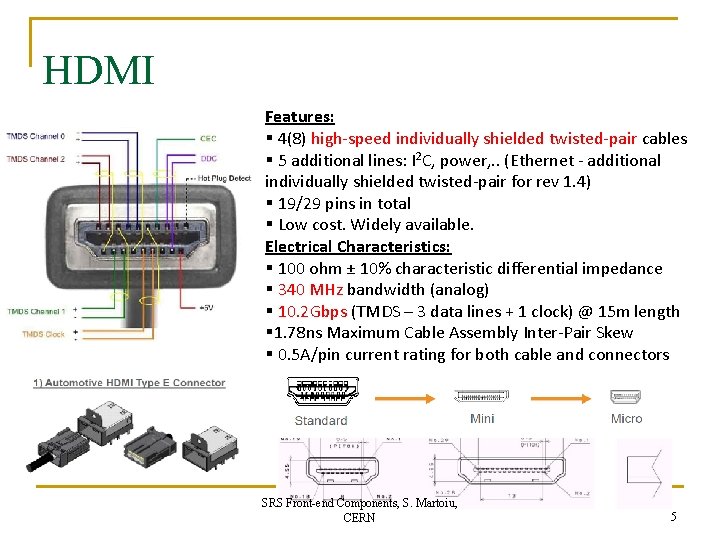

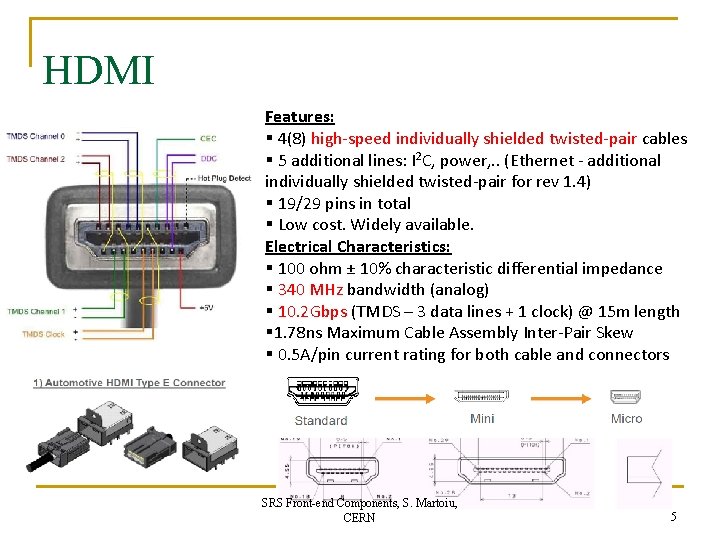

HDMI Features: § 4(8) high-speed individually shielded twisted-pair cables § 5 additional lines: I 2 C, power, . . (Ethernet - additional individually shielded twisted-pair for rev 1. 4) § 19/29 pins in total § Low cost. Widely available. Electrical Characteristics: § 100 ohm ± 10% characteristic differential impedance § 340 MHz bandwidth (analog) § 10. 2 Gbps (TMDS – 3 data lines + 1 clock) @ 15 m length § 1. 78 ns Maximum Cable Assembly Inter-Pair Skew § 0. 5 A/pin current rating for both cable and connectors SRS Front-end Components, S. Martoiu, CERN 5

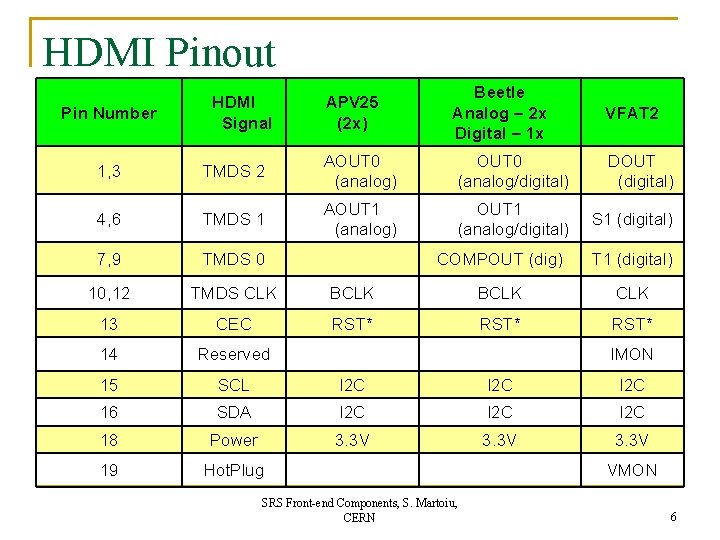

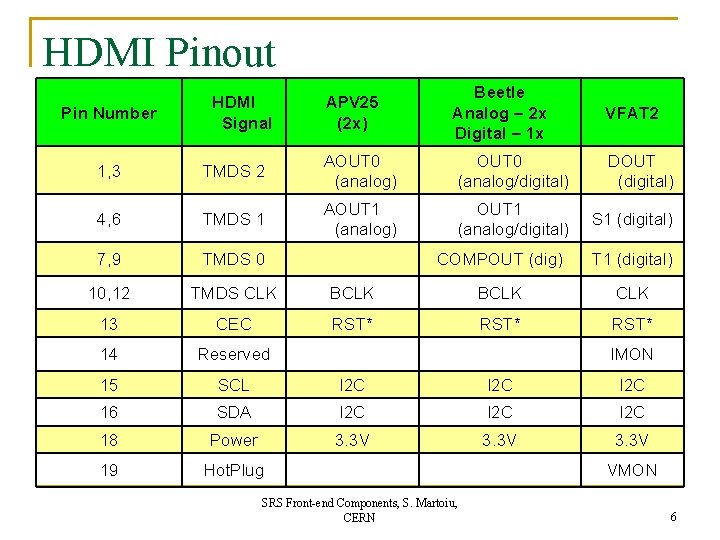

HDMI Pinout Pin Number HDMI Signal APV 25 (2 x) Beetle Analog – 2 x Digital – 1 x VFAT 2 1, 3 TMDS 2 AOUT 0 (analog) OUT 0 (analog/digital) DOUT (digital) 4, 6 TMDS 1 AOUT 1 (analog) OUT 1 (analog/digital) S 1 (digital) 7, 9 TMDS 0 10, 12 TMDS CLK 13 CEC 14 Reserved 15 SCL I 2 C 16 SDA I 2 C 18 Power 3. 3 V 19 Hot. Plug COMPOUT (dig) T 1 (digital) BCLK CLK RST* IMON SRS Front-end Components, S. Martoiu, CERN VMON 6

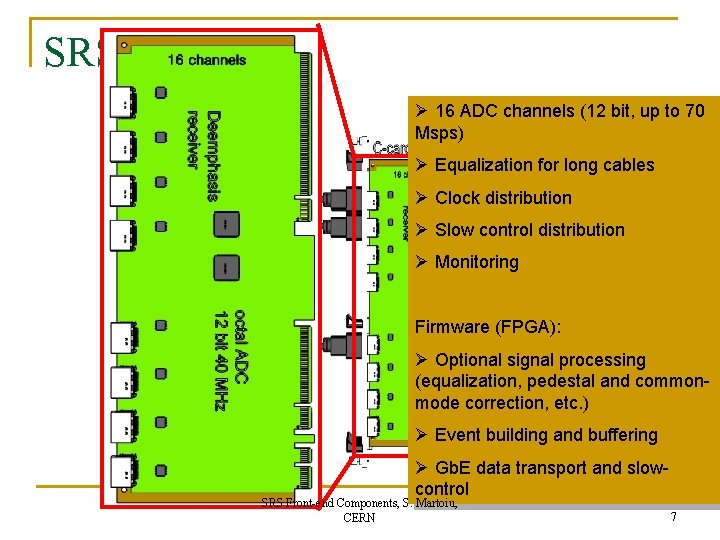

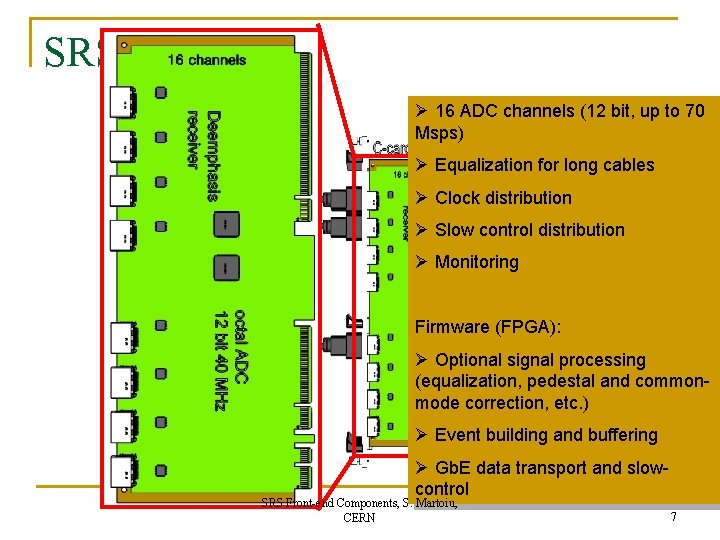

SRS APV DAQ Ø 16 ADC channels (12 bit, up to 70 Msps) Ø Clock distribution Ø Monitoring Slave Single Ø Equalization for long cables Master Chip Carriers Ø Slow control distribution Firmware (FPGA): Ø Optional signal processing (equalization, pedestal and commonmode correction, etc. ) Ø Event building and buffering Ø Gb. E data transport and slowcontrol SRS Front-end Components, S. Martoiu, CERN 7

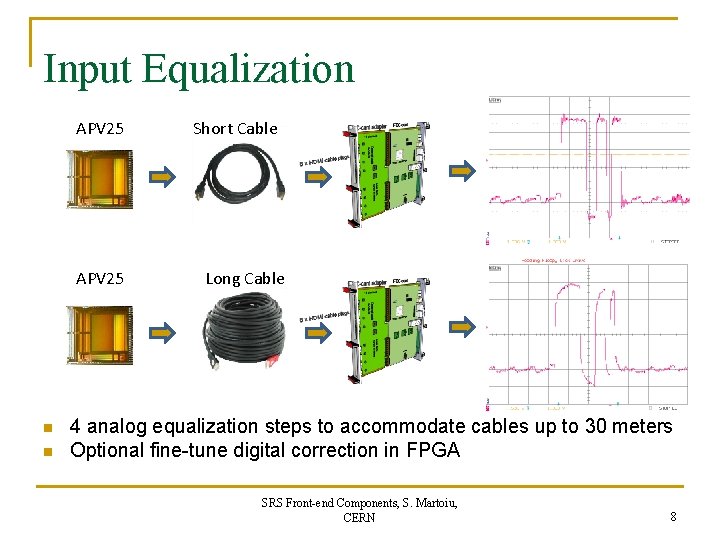

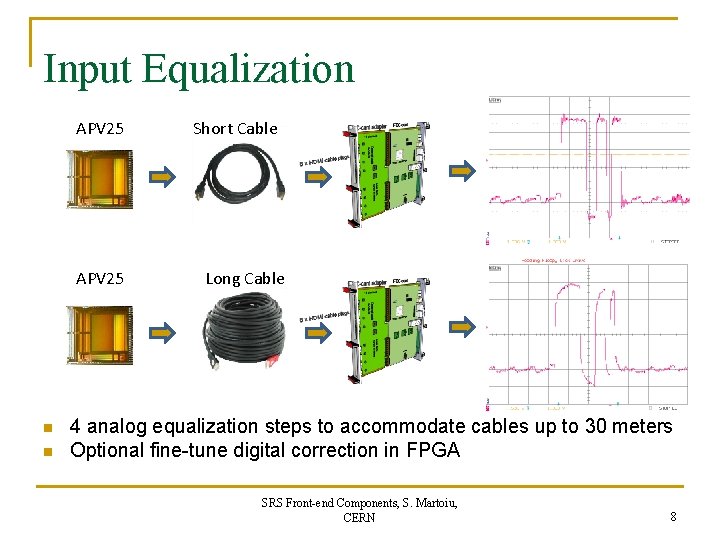

Input Equalization APV 25 n n Short Cable Long Cable 4 analog equalization steps to accommodate cables up to 30 meters Optional fine-tune digital correction in FPGA SRS Front-end Components, S. Martoiu, CERN 8

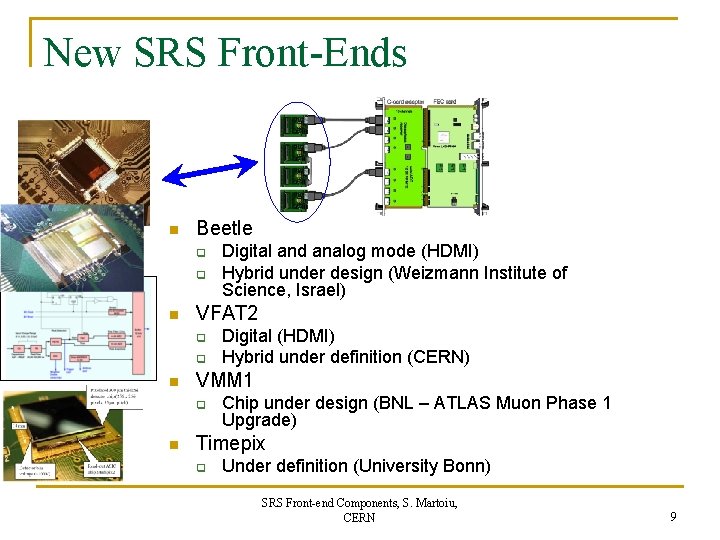

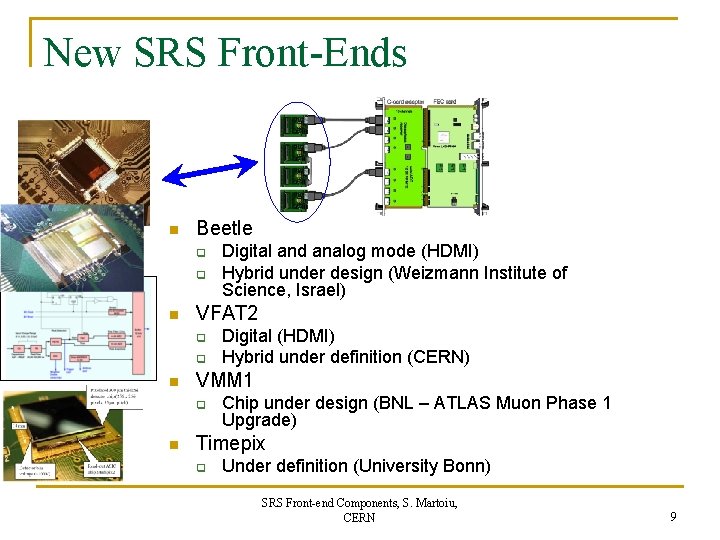

New SRS Front-Ends n Beetle q q n VFAT 2 q q n Digital (HDMI) Hybrid under definition (CERN) VMM 1 q n Digital and analog mode (HDMI) Hybrid under design (Weizmann Institute of Science, Israel) Chip under design (BNL – ATLAS Muon Phase 1 Upgrade) Timepix q Under definition (University Bonn) SRS Front-end Components, S. Martoiu, CERN 9

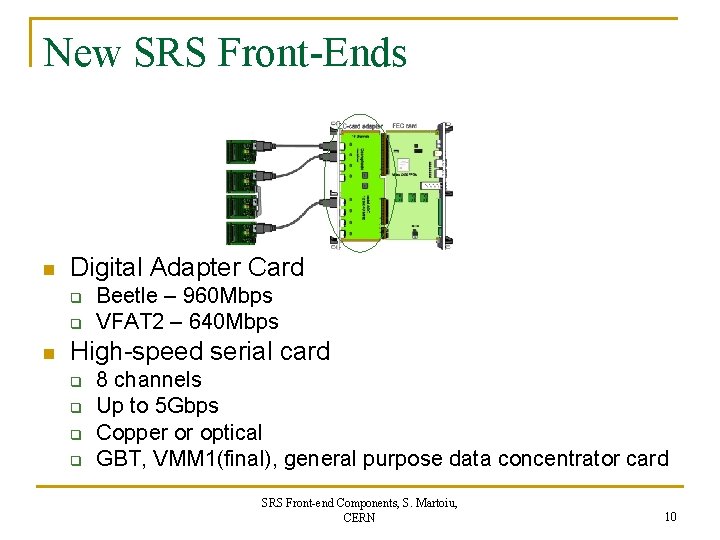

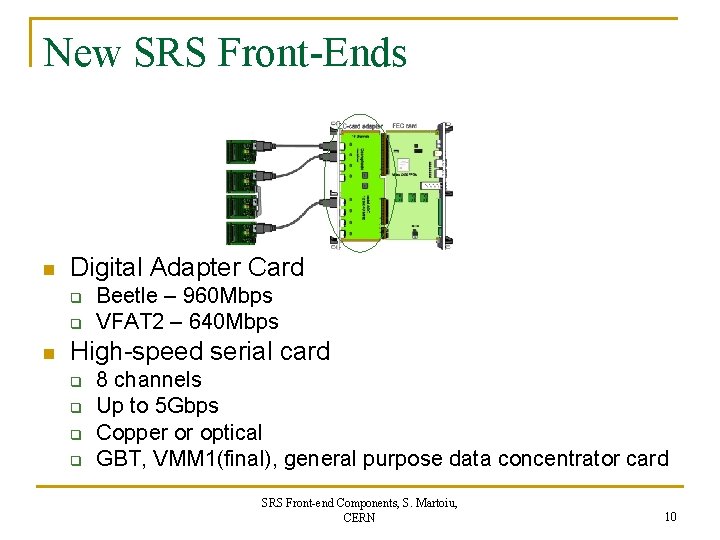

New SRS Front-Ends n Digital Adapter Card q q n Beetle – 960 Mbps VFAT 2 – 640 Mbps High-speed serial card q q 8 channels Up to 5 Gbps Copper or optical GBT, VMM 1(final), general purpose data concentrator card SRS Front-end Components, S. Martoiu, CERN 10