SRS Activities at IFINHH VMM 2 Hybrid FECv

SRS Activities at IFIN-HH: VMM 2 Hybrid, FECv 6 Firmware, High-Density Optical ATCA-SRS Mezzanine Sorin Martoiu, Michele Renda, Paul Vartolomei (IFIN-HH Bucharest)

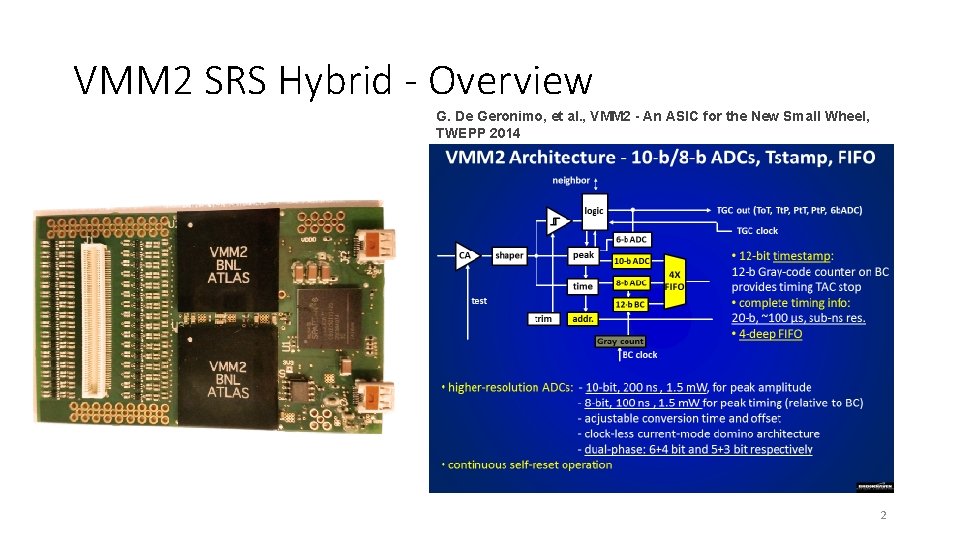

VMM 2 SRS Hybrid - Overview G. De Geronimo, et al. , VMM 2 - An ASIC for the New Small Wheel, TWEPP 2014 2

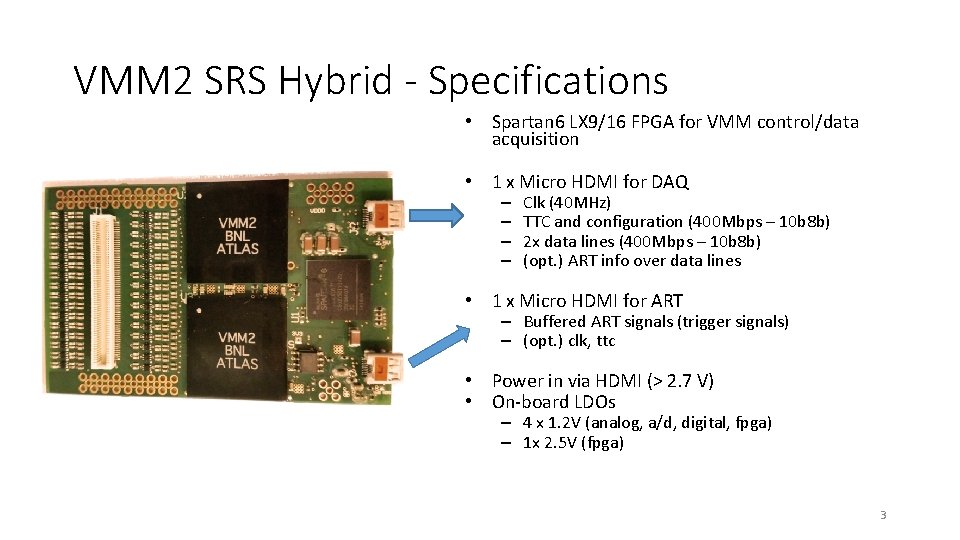

VMM 2 SRS Hybrid - Specifications • Spartan 6 LX 9/16 FPGA for VMM control/data acquisition • 1 x Micro HDMI for DAQ – – Clk (40 MHz) TTC and configuration (400 Mbps – 10 b 8 b) 2 x data lines (400 Mbps – 10 b 8 b) (opt. ) ART info over data lines • 1 x Micro HDMI for ART – Buffered ART signals (trigger signals) – (opt. ) clk, ttc • Power in via HDMI (> 2. 7 V) • On-board LDOs – 4 x 1. 2 V (analog, a/d, digital, fpga) – 1 x 2. 5 V (fpga) 3

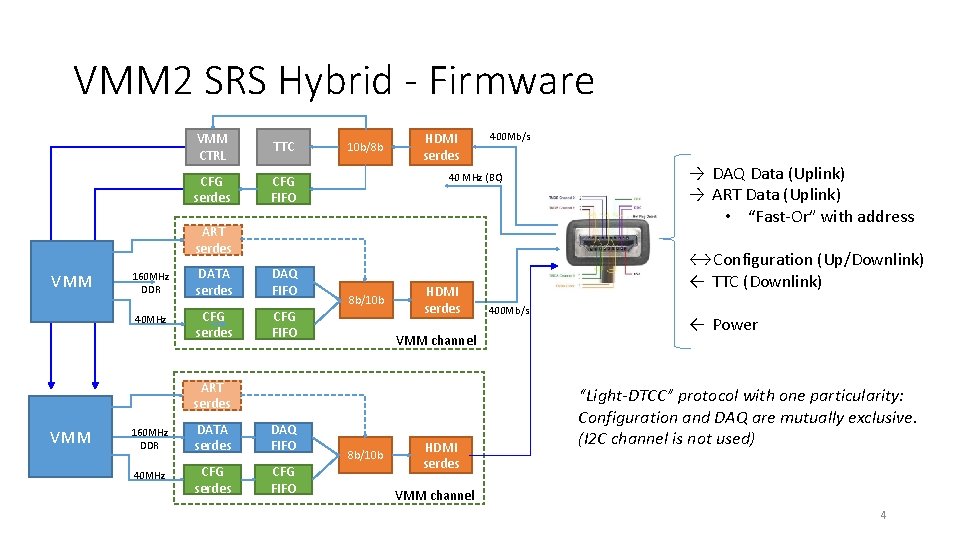

VMM 2 SRS Hybrid - Firmware VMM CTRL TTC CFG serdes CFG FIFO 10 b/8 b HDMI serdes 400 Mb/s 40 MHz (BC) ART serdes VMM 160 MHz DDR DATA serdes DAQ FIFO 40 MHz CFG serdes CFG FIFO 8 b/10 b HDMI serdes VMM channel ART serdes VMM 160 MHz DDR DATA serdes DAQ FIFO 40 MHz CFG serdes CFG FIFO 8 b/10 b HDMI serdes → DAQ Data (Uplink) → ART Data (Uplink) • “Fast-Or” with address ↔Configuration (Up/Downlink) ← TTC (Downlink) 400 Mb/s ← Power “Light-DTCC” protocol with one particularity: Configuration and DAQ are mutually exclusive. (I 2 C channel is not used) VMM channel 4

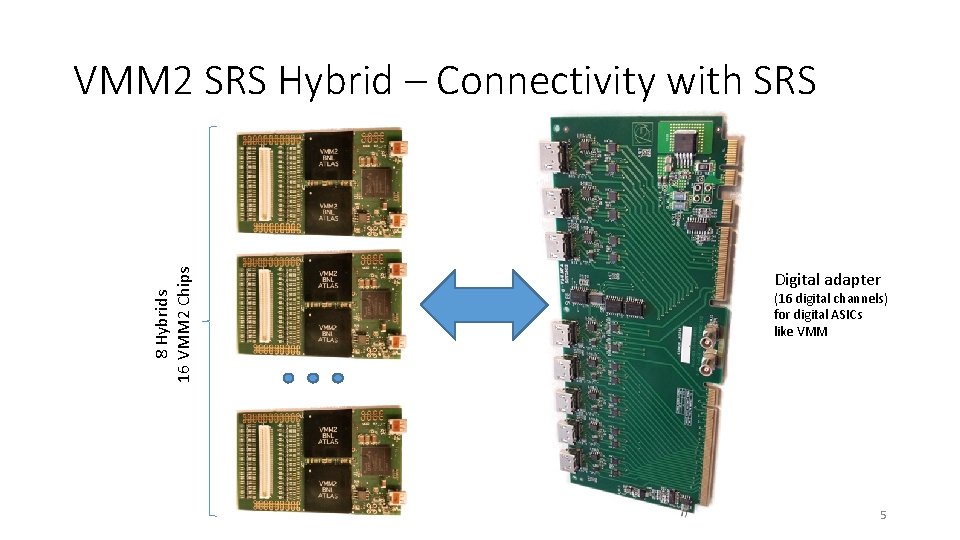

8 Hybrids 16 VMM 2 Chips VMM 2 SRS Hybrid – Connectivity with SRS Digital adapter (16 digital channels) for digital ASICs like VMM 5

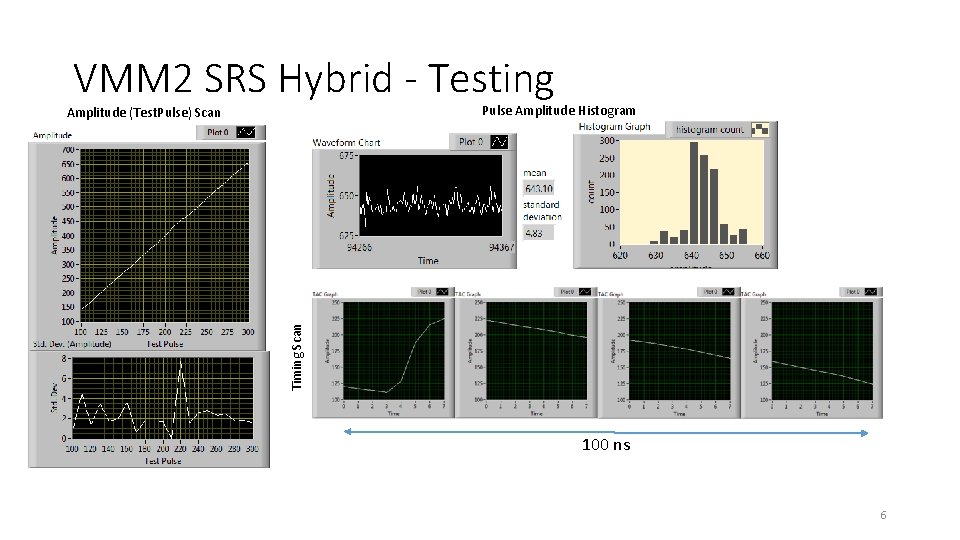

VMM 2 SRS Hybrid - Testing Pulse Amplitude Histogram Timing Scan Amplitude (Test. Pulse) Scan 100 ns 6

VMM 2 SRS Hybrid – Status A few modifications under way: • Access to analog monitor outputs for calibration and debug • Layout changes to improve power distribution and decoupling • Separate power option • Also, digital DCARD is being modified to provide the needed power to the VMM Hybrid (1. 5 A/hybrid) 7

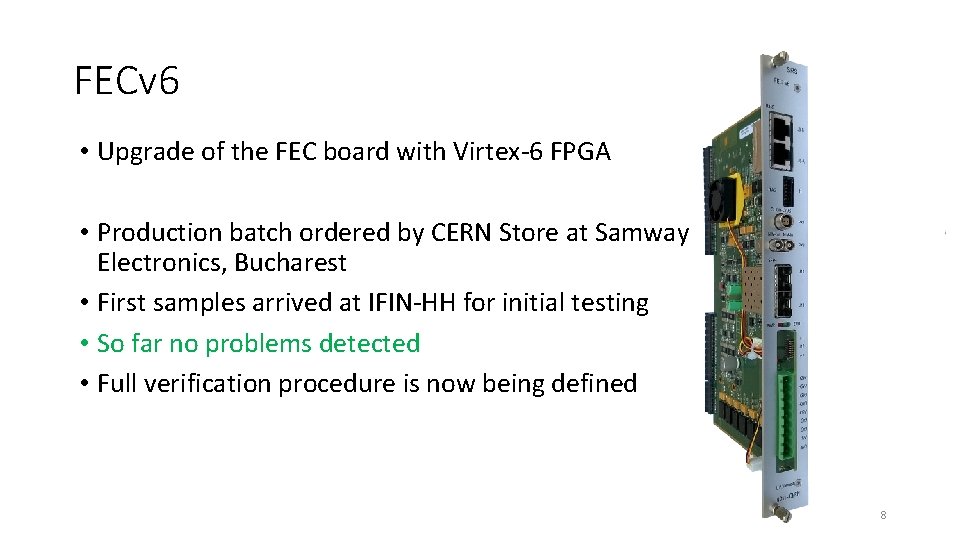

FECv 6 • Upgrade of the FEC board with Virtex-6 FPGA • Production batch ordered by CERN Store at Samway Electronics, Bucharest • First samples arrived at IFIN-HH for initial testing • So far no problems detected • Full verification procedure is now being defined 8

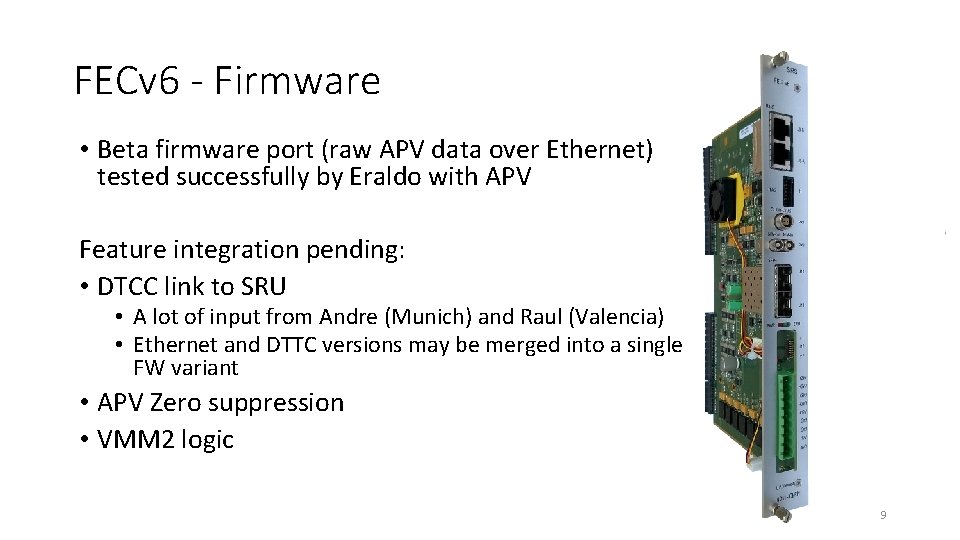

FECv 6 - Firmware • Beta firmware port (raw APV data over Ethernet) tested successfully by Eraldo with APV Feature integration pending: • DTCC link to SRU • A lot of input from Andre (Munich) and Raul (Valencia) • Ethernet and DTTC versions may be merged into a single FW variant • APV Zero suppression • VMM 2 logic 9

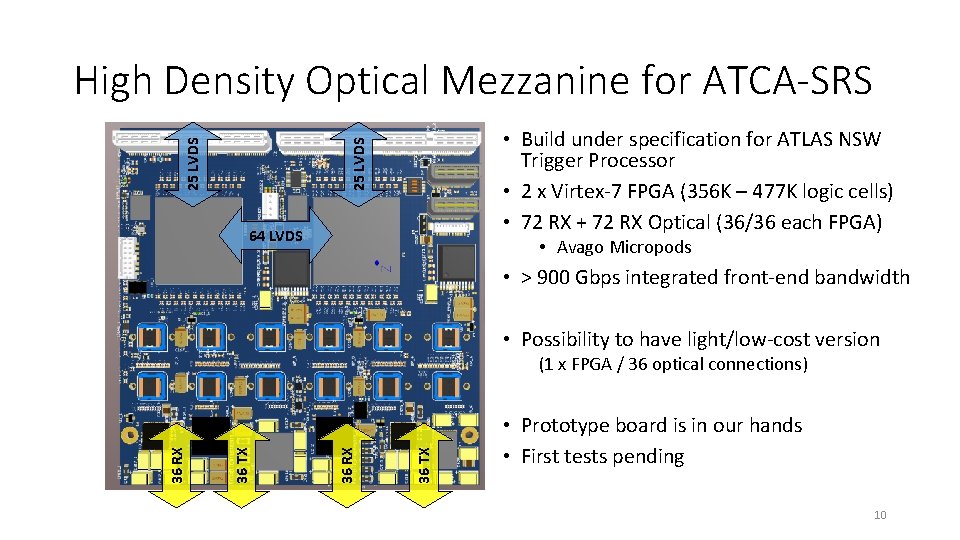

High Density Optical Mezzanine for ATCA-SRS 25 LVDS • Build under specification for ATLAS NSW Trigger Processor • 2 x Virtex-7 FPGA (356 K – 477 K logic cells) • 72 RX + 72 RX Optical (36/36 each FPGA) 64 LVDS • Avago Micropods • > 900 Gbps integrated front-end bandwidth • Possibility to have light/low-cost version 36 TX 36 RX (1 x FPGA / 36 optical connections) • Prototype board is in our hands • First tests pending 10

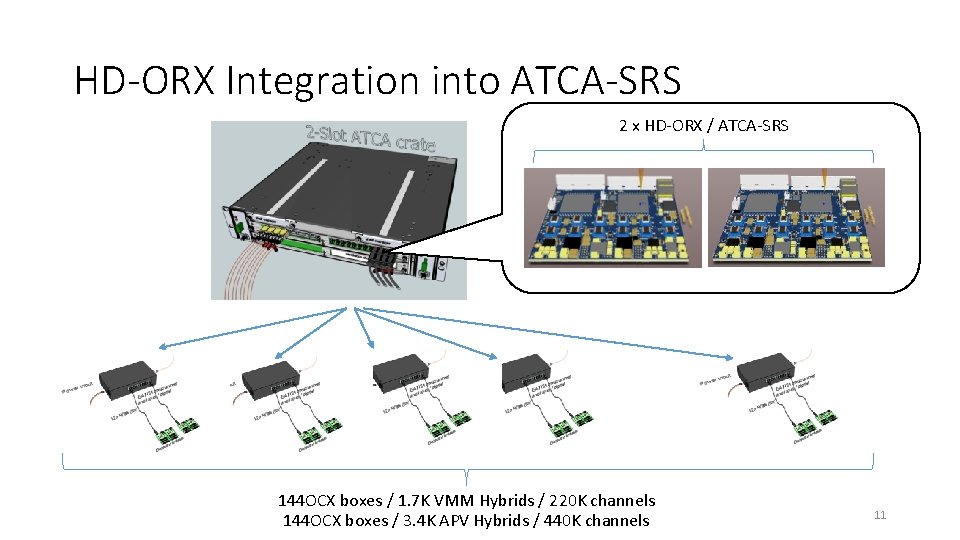

HD-ORX Integration into ATCA-SRS 2 x HD-ORX / ATCA-SRS 144 OCX boxes / 1. 7 K VMM Hybrids / 220 K channels 144 OCX boxes / 3. 4 K APV Hybrids / 440 K channels 11

Thank You 12

- Slides: 12