SRCs Unified Computing Architecture Market Specialized Performance with

- Slides: 15

SRC’s Unified Computing Architecture Market Specialized Performance with Commodity Components Jon Huppenthal President and CEO SRC Computers, Inc. hupp@srccomp. com 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

SRC Architectural Goals l Tightly coupled implicitly and explicitly controlled processing devices l Support cluster and switch based interconnect l Standard programming languages and models l System is optimally configured for the applications 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

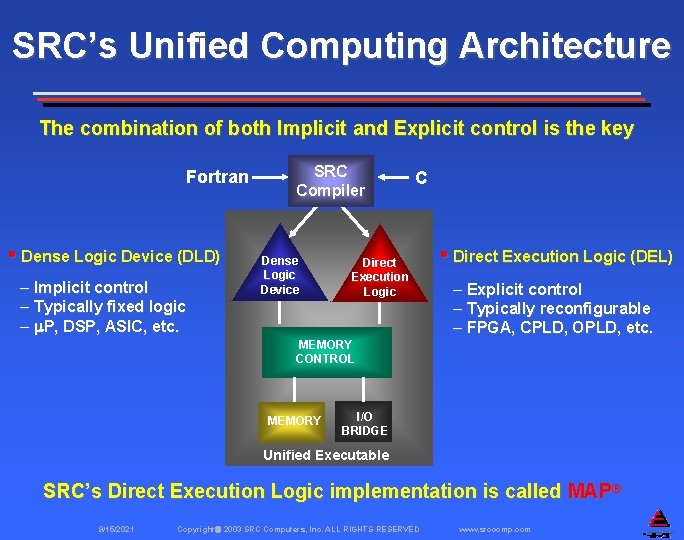

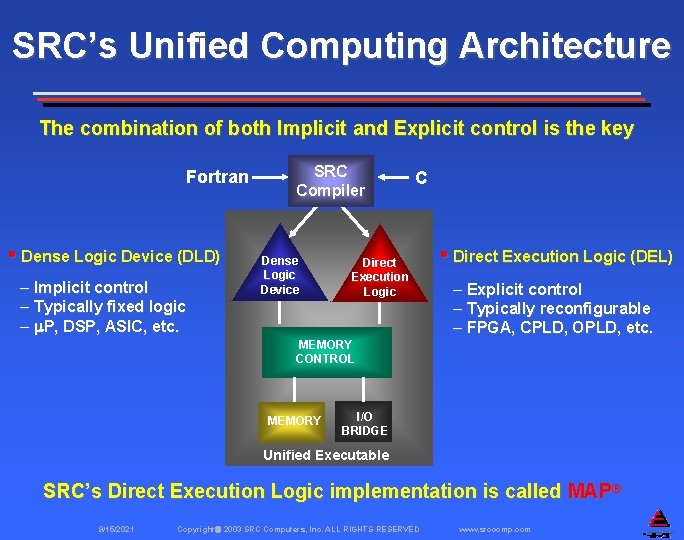

SRC’s Unified Computing Architecture The combination of both Implicit and Explicit control is the key Fortran • Dense Logic Device (DLD) – Implicit control – Typically fixed logic - P, DSP, ASIC, etc. SRC Compiler Dense Logic Device C Direct Execution Logic • Direct Execution Logic (DEL) – Explicit control – Typically reconfigurable – FPGA, CPLD, OPLD, etc. MEMORY CONTROL MEMORY I/O BRIDGE Unified Executable SRC’s Direct Execution Logic implementation is called MAP® 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

SRC Architectural Features l Explicitly controlled direct execution logic allows for – Explicit computational f(x) units – Explicit memory pre-fetch f(x) units – Explicit data access f(x) units l Standard programming models and languages – No changes required to run existing codes – A single unified executable is automatically generated l Orders of magnitude more efficient use of gates, power and bandwidth PROCESSING POWER INCREASED by ORDERS of MAGNITUDE 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

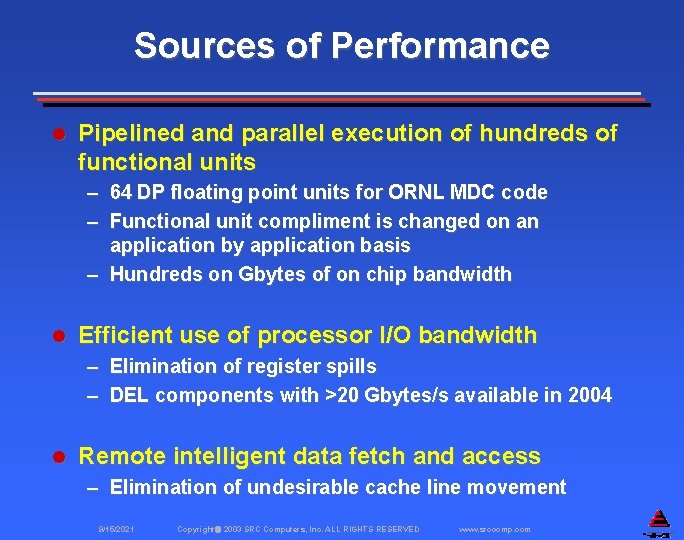

Sources of Performance l Pipelined and parallel execution of hundreds of functional units – 64 DP floating point units for ORNL MDC code – Functional unit compliment is changed on an application by application basis – Hundreds on Gbytes of on chip bandwidth l Efficient use of processor I/O bandwidth – Elimination of register spills – DEL components with >20 Gbytes/s available in 2004 l Remote intelligent data fetch and access – Elimination of undesirable cache line movement 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

Carte. TM Programming Environment l Carte. TM uses standard high level languages – C and Fortran l Merges SRC developed and third party tools l Emulation and simulation supported l Standard debug methodologies supported 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

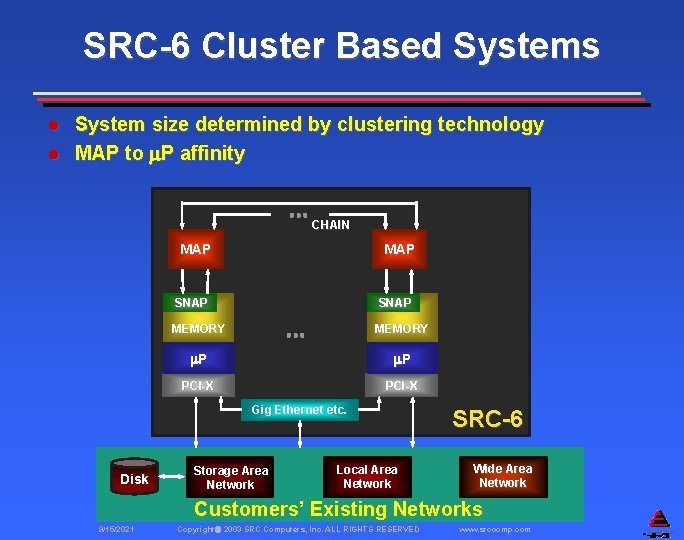

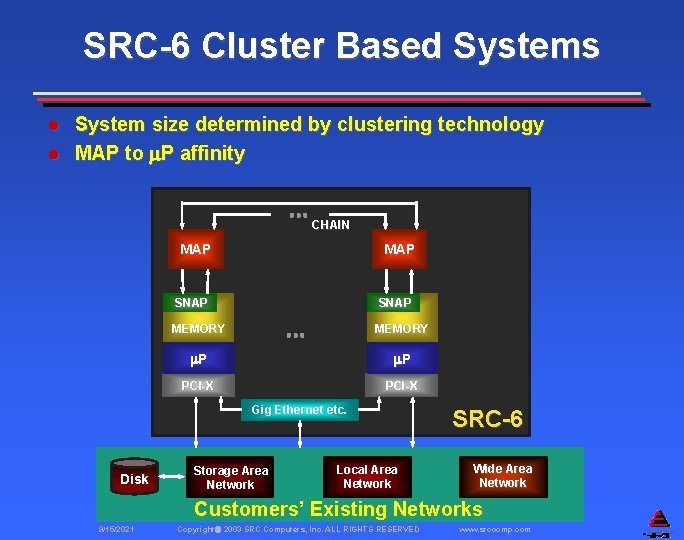

SRC-6 Cluster Based Systems System size determined by clustering technology l MAP to P affinity l CHAIN MAP SNAP MEMORY P P PCI-X Gig Ethernet etc. Disk Storage Area Network Local Area Network SRC-6 Wide Area Network Customers’ Existing Networks 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

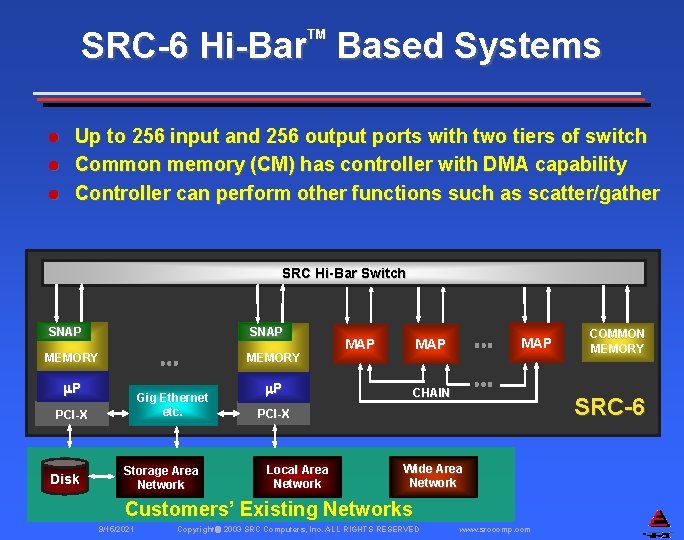

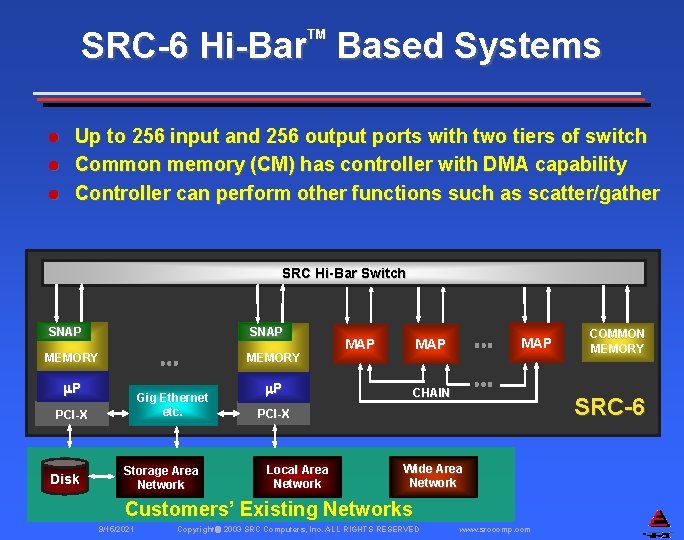

SRC-6 Hi-Bar Based Systems TM Up to 256 input and 256 output ports with two tiers of switch l Common memory (CM) has controller with DMA capability l Controller can perform other functions such as scatter/gather l SRC Hi-Bar Switch SNAP MEMORY P Gig Ethernet etc. PCI-X Disk Storage Area Network P MAP MAP CHAIN SRC-6 PCI-X Local Area Network Wide Area Network Customers’ Existing Networks 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED COMMON MEMORY www. srccomp. com

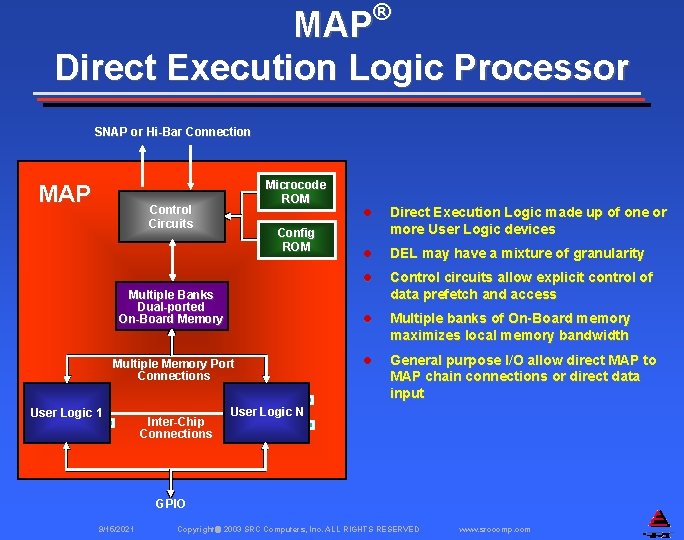

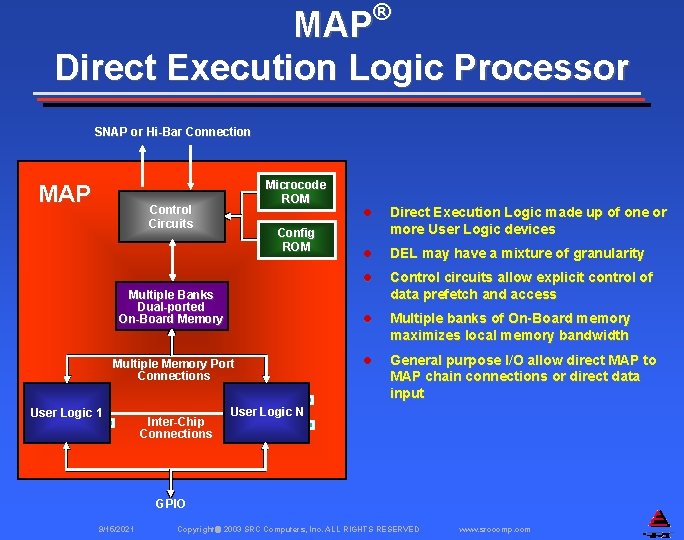

® MAP Direct Execution Logic Processor SNAP or Hi-Bar Connection MAP Microcode ROM Control Circuits Config ROM Multiple Banks Dual-ported On-Board Memory Multiple Memory Port Connections User Logic 1 Inter-Chip Connections l Direct Execution Logic made up of one or more User Logic devices l DEL may have a mixture of granularity l Control circuits allow explicit control of data prefetch and access l Multiple banks of On-Board memory maximizes local memory bandwidth l General purpose I/O allow direct MAP to MAP chain connections or direct data input User Logic N GPIO 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

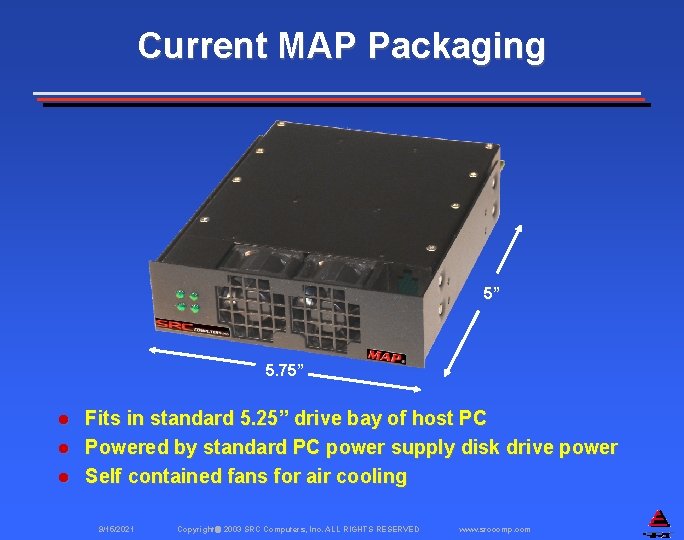

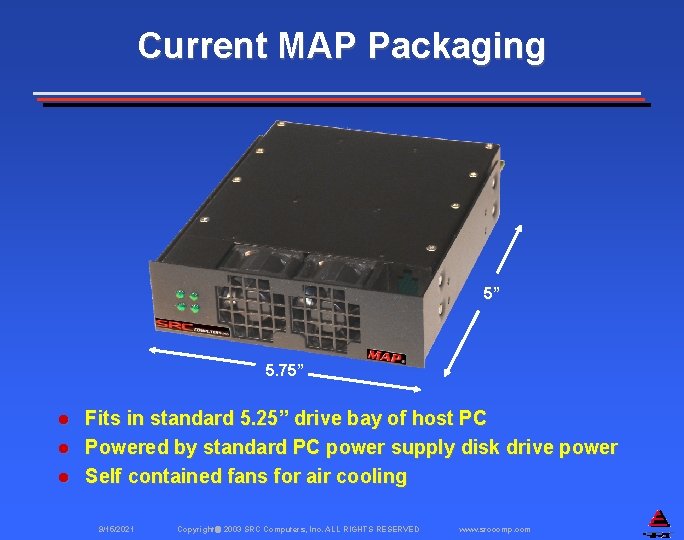

Current MAP Packaging 5” 5. 75” Fits in standard 5. 25” drive bay of host PC l Powered by standard PC power supply disk drive power l Self contained fans for air cooling l 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

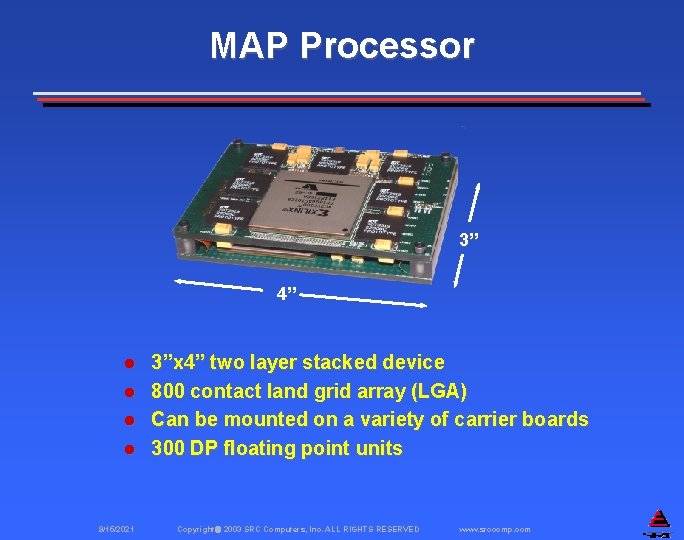

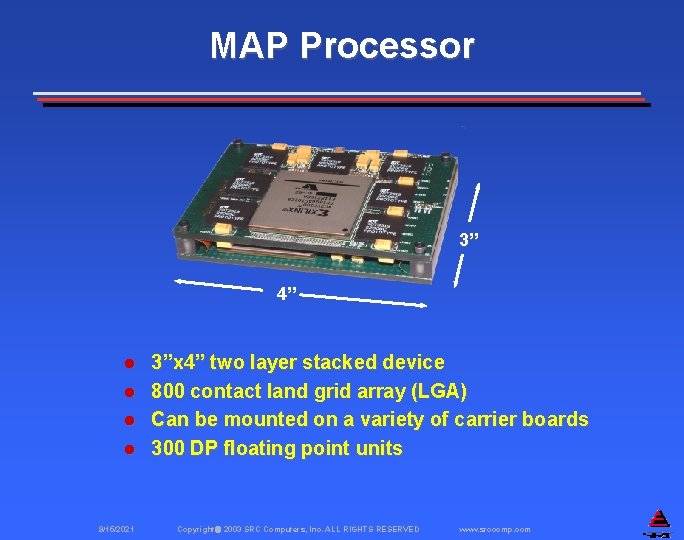

MAP Processor 3” 4” 3”x 4” two layer stacked device l 800 contact land grid array (LGA) l Can be mounted on a variety of carrier boards l 300 DP floating point units l 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

Marketplace Optimization l System component mix varies with market – MAP, P, common memory and I/O l System interconnect varies with market – Hi-Bar, cluster l Variety of communications models supported – MPI over cluster or Hi-Bar, shared memory Functional unit and application library varies with market l Tuned DEL applications l The Unified Computing Architecture is easily optimized to serve many diverse markets 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

Status l Unified Computing Architecture fielded in 1998 – Proved viability for general purpose computing – Limited capacity and not programmer friendly l Current systems in operation at customer sites since 2002 – Hardware and software very stable – Programmer friendly software environment – Capacity for over 100 DP floating point units per MAP l Customer upgrades underway – Hi-Bar switch for higher interconnect bandwidth – Shared common memory TM 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

Near Term Roadmap l Compiler Enhancements – “Compiler does it all” goal l MAP densification – Allows for small, high MAP count systems – Positions MAP to use advanced high capacity components l Peta-Scale System – – Three year program Based on densification efforts that are underway Small number of MAPs required Total system requires approximately 8 racks 9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com

9/15/2021 Copyright 2003 SRC Computers, Inc. ALL RIGHTS RESERVED www. srccomp. com