Speculation Problems of Tomasulo algorithm out of order

Speculation 윤진훈

Problems of Tomasulo algorithm • 명령어 완료 = out of order – Exception – Branch misprediction • 명령어 완료는 in order 여야 한다. • Reorder buffer (ROB) – Write result된 명령어의 순서를 재조정 – Ready/finished 비트로 구분

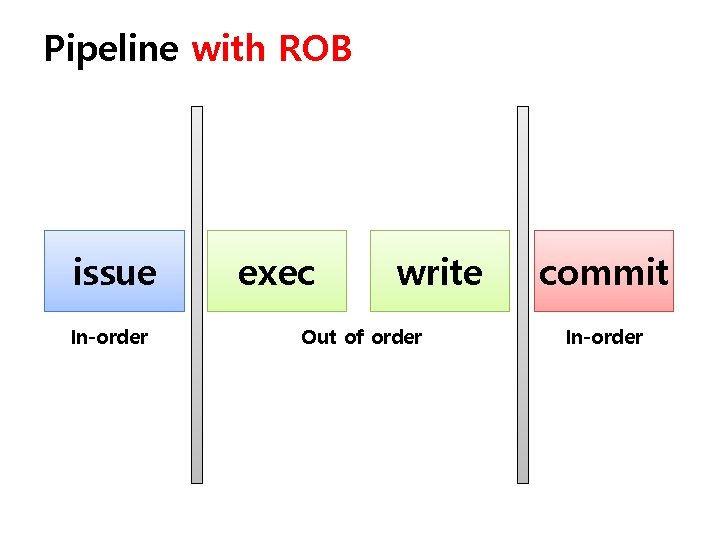

Pipeline with ROB issue In-order exec write Out of order commit In-order

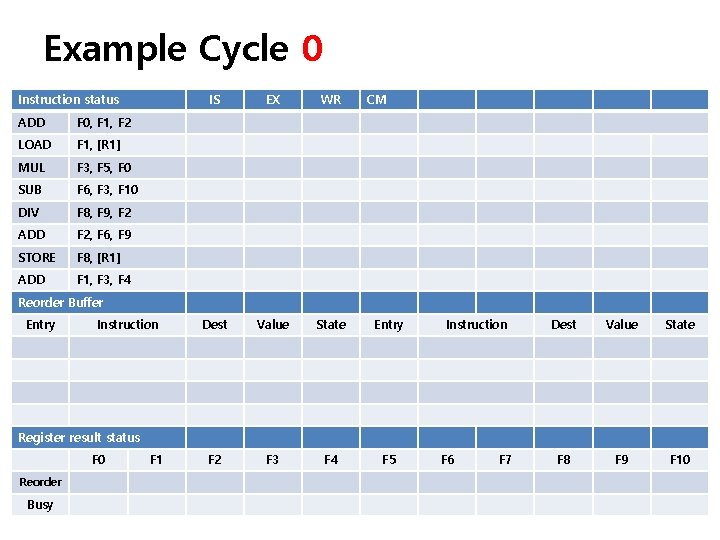

Example Cycle 0 Instruction status ADD F 0, F 1, F 2 LOAD F 1, [R 1] MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 IS EX WR CM Dest Value State Entry F 2 F 3 F 4 F 5 Reorder Buffer Entry Instruction Dest Value State F 8 F 9 F 10 Register result status F 0 Reorder Busy F 1 F 6 F 7

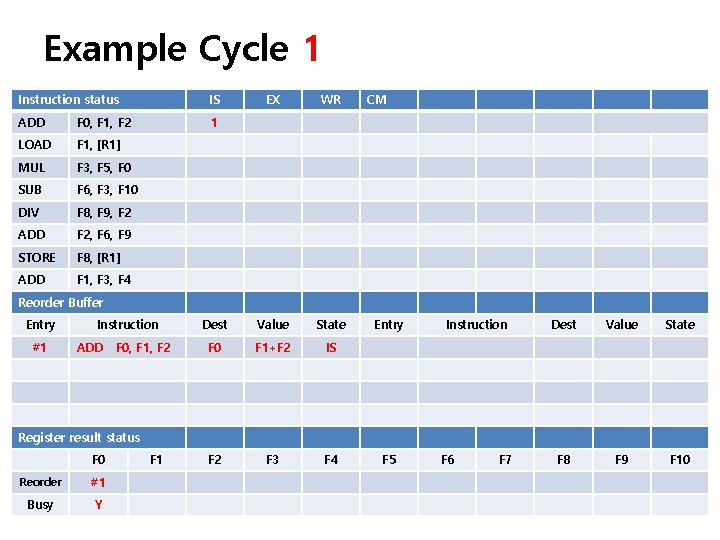

Example Cycle 1 Instruction status IS EX WR ADD F 0, F 1, F 2 1 LOAD F 1, [R 1] MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 Dest Value State F 0 F 1+F 2 IS F 2 F 3 F 4 CM Reorder Buffer Entry #1 Instruction ADD F 0, F 1, F 2 Entry Instruction Dest Value State F 8 F 9 F 10 Register result status F 0 Reorder #1 Busy Y F 1 F 5 F 6 F 7

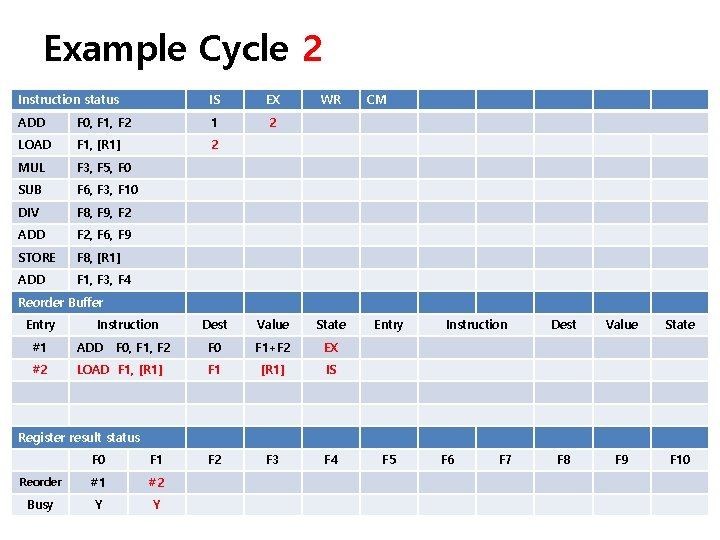

Example Cycle 2 Instruction status IS EX ADD F 0, F 1, F 2 1 2 LOAD F 1, [R 1] 2 MUL F 3, F 5, F 0 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 WR CM Reorder Buffer Entry Instruction #1 ADD F 0, F 1, F 2 #2 LOAD F 1, [R 1] Dest Value State F 0 F 1+F 2 EX F 1 [R 1] IS F 2 F 3 F 4 Entry Instruction Dest Value State F 8 F 9 F 10 Register result status F 0 F 1 Reorder #1 #2 Busy Y Y F 5 F 6 F 7

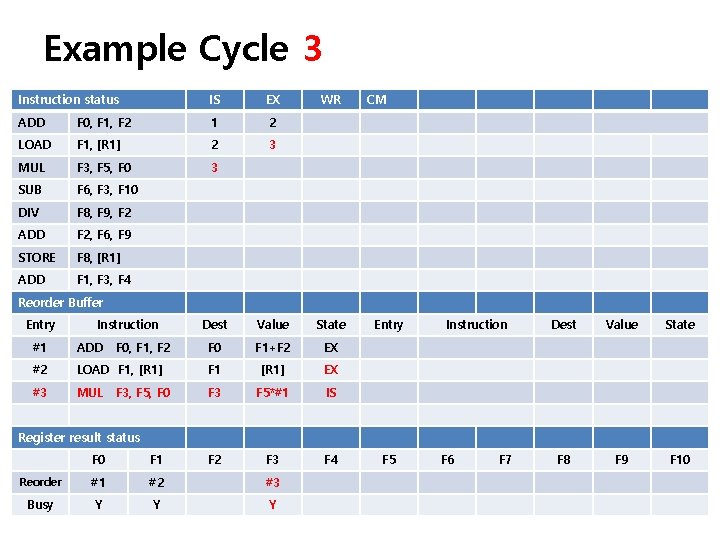

Example Cycle 3 Instruction status IS EX ADD F 0, F 1, F 2 1 2 LOAD F 1, [R 1] 2 3 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 WR CM Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State F 0 F 1+F 2 EX #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] EX #3 MUL F 3 F 5*#1 IS F 2 F 3 F 4 F 3, F 5, F 0 Entry Instruction Dest Value State F 8 F 9 F 10 Register result status F 0 F 1 Reorder #1 #2 #3 Busy Y Y Y F 5 F 6 F 7

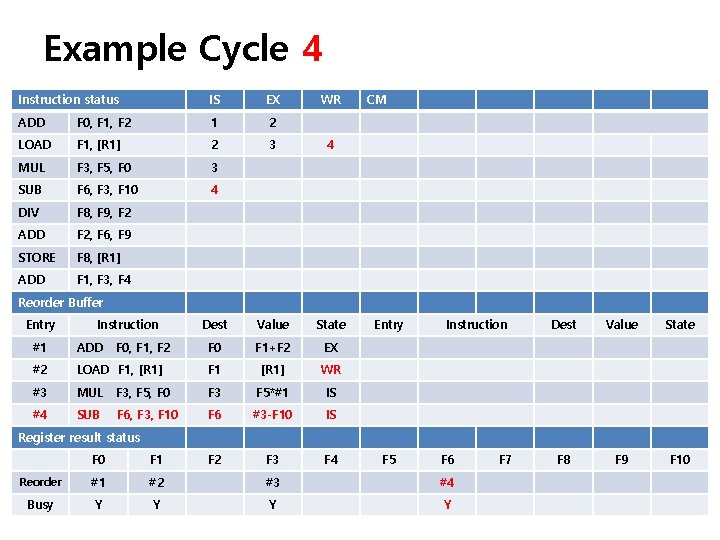

Example Cycle 4 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 Dest Value State F 0 F 1+F 2 EX CM Reorder Buffer Entry Instruction #1 ADD F 0, F 1, F 2 #2 LOAD F 1, [R 1] F 1 [R 1] WR #3 MUL F 3, F 5, F 0 F 3 F 5*#1 IS #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 2 F 3 F 4 Entry Instruction Dest Value State F 8 F 9 F 10 Register result status F 0 F 1 F 5 F 6 Reorder #1 #2 #3 #4 Busy Y Y F 7

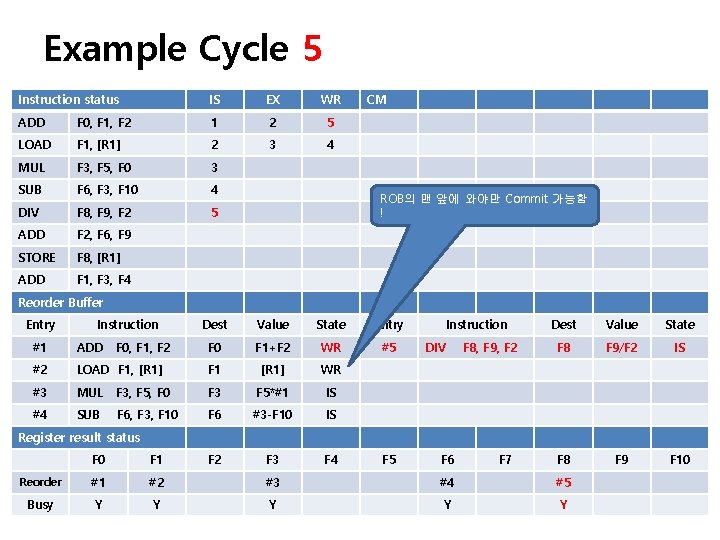

Example Cycle 5 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 STORE F 8, [R 1] ADD F 1, F 3, F 4 CM ROB의 맨 앞에 와야만 Commit 가능함 ! Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry F 0 F 1+F 2 WR #5 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] WR #3 MUL F 3, F 5, F 0 F 3 F 5*#1 IS #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 2 F 3 F 4 Instruction DIV F 8, F 9, F 2 Dest Value State F 8 F 9/F 2 IS F 8 F 9 F 10 Register result status F 0 F 1 F 5 F 6 F 7 Reorder #1 #2 #3 #4 #5 Busy Y Y Y

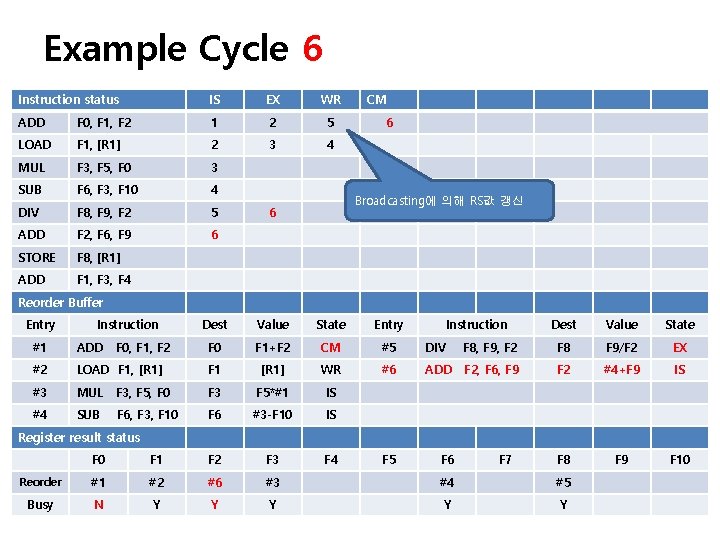

Example Cycle 6 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 LOAD F 1, [R 1] 2 3 4 MUL F 3, F 5, F 0 3 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] ADD F 1, F 3, F 4 CM 6 Broadcasting에 의해 RS값 갱신 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV #6 ADD F 5 F 6 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] WR #3 MUL F 3, F 5, F 0 F 3 F 5*#1 IS #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS F 8 F 9 F 10 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N Y Y Y

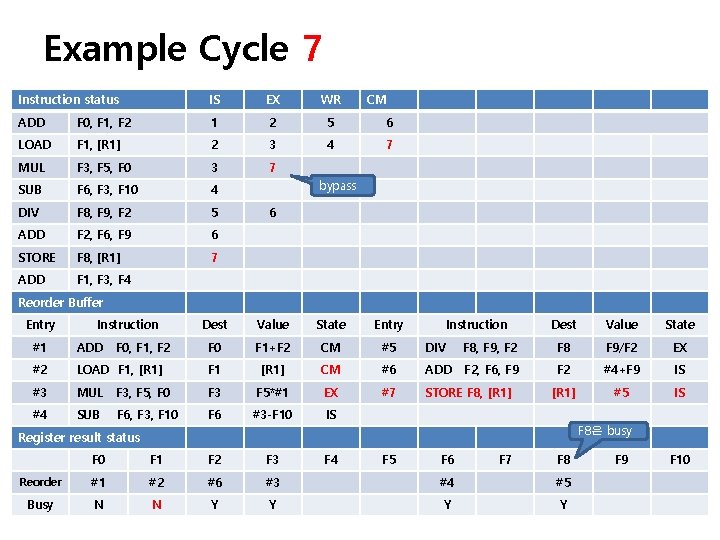

Example Cycle 7 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 bypass 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 EX #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 8은 busy Register result status F 0 F 1 F 2 F 3 F 4 F 5 F 6 F 7 F 8 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y F 9 F 10

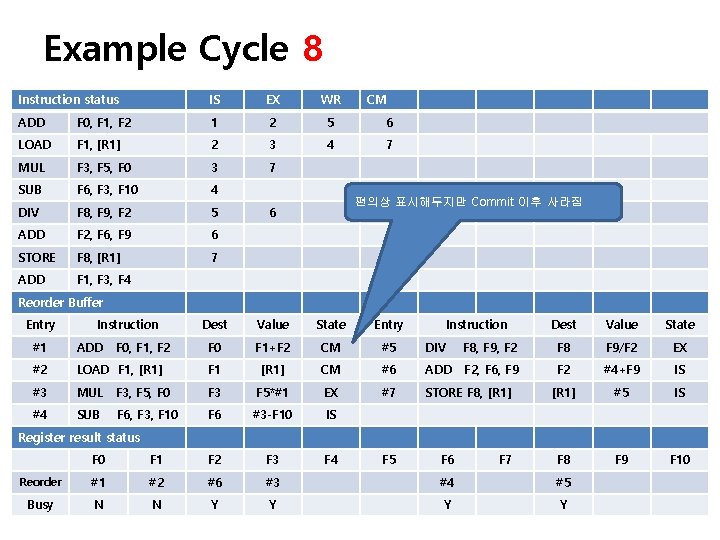

Example Cycle 8 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 편의상 표시해두지만 Commit 이후 사라짐 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 EX #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

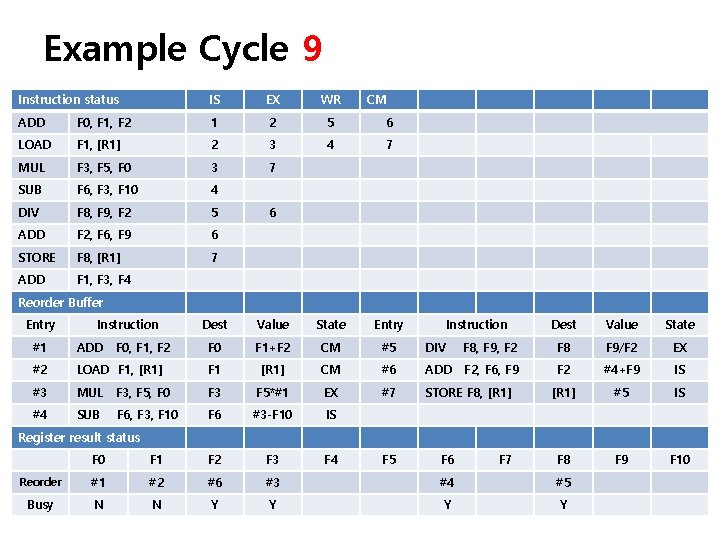

Example Cycle 9 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 EX #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

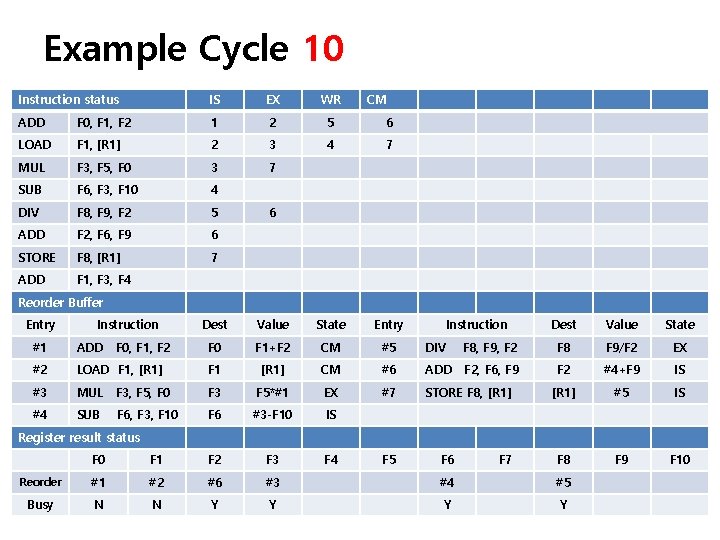

Example Cycle 10 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 EX #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

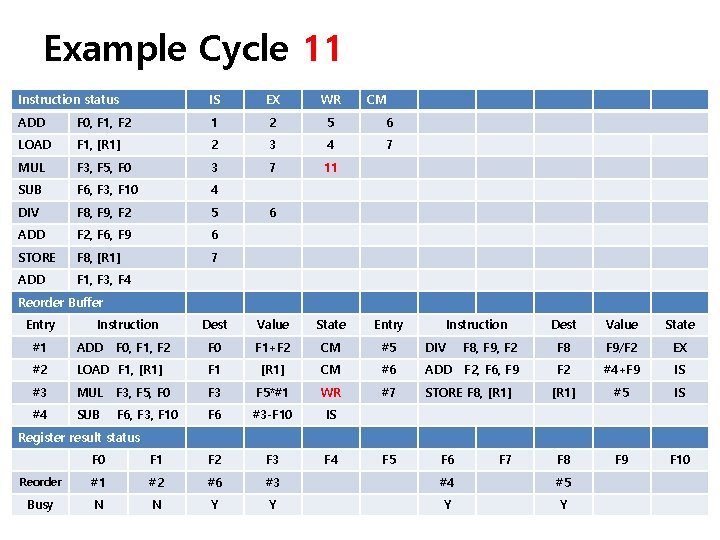

Example Cycle 11 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 WR #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

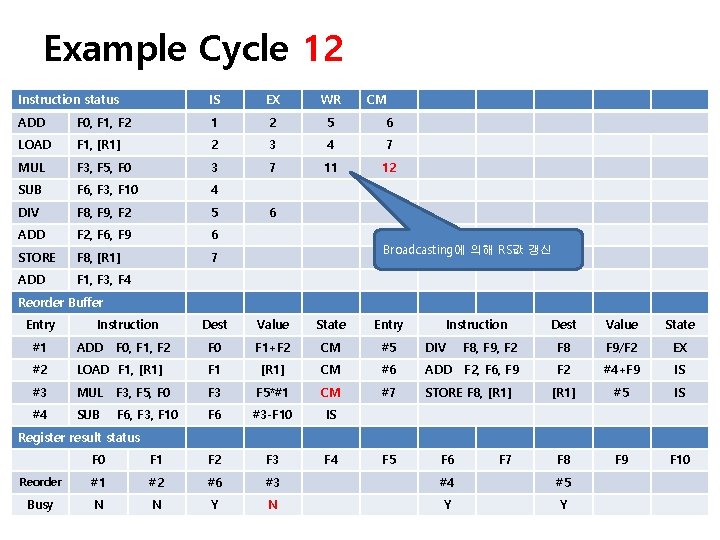

Example Cycle 12 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 DIV F 8, F 9, F 2 5 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 6 Broadcasting에 의해 RS값 갱신 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 IS F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

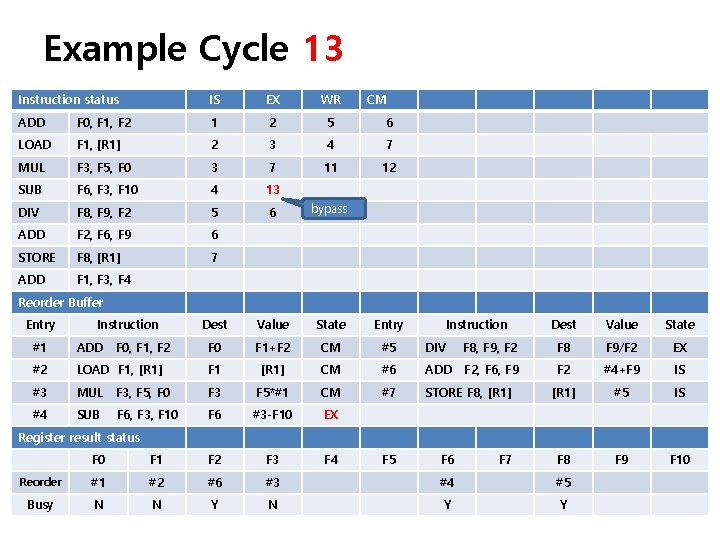

Example Cycle 13 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 DIV F 8, F 9, F 2 5 6 bypass ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 EX F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

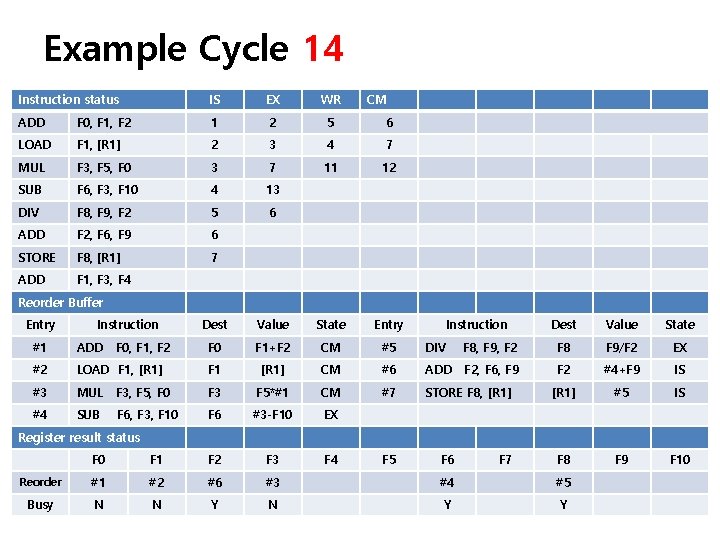

Example Cycle 14 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 DIV F 8, F 9, F 2 5 6 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 EX F 4 Register result status F 0 F 1 F 2 F 3 F 5 F 6 F 7 Reorder #1 #2 #6 #3 #4 #5 Busy N N Y Y

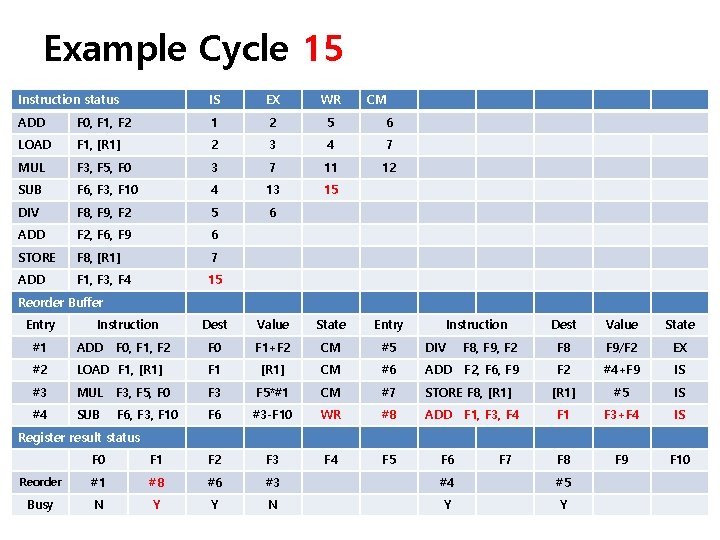

Example Cycle 15 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 DIV F 8, F 9, F 2 5 6 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 Reorder Buffer Entry Instruction F 0, F 1, F 2 Dest Value State Entry Instruction F 0 F 1+F 2 CM #5 DIV Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 EX F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 1 F 3+F 4 IS F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 WR #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y

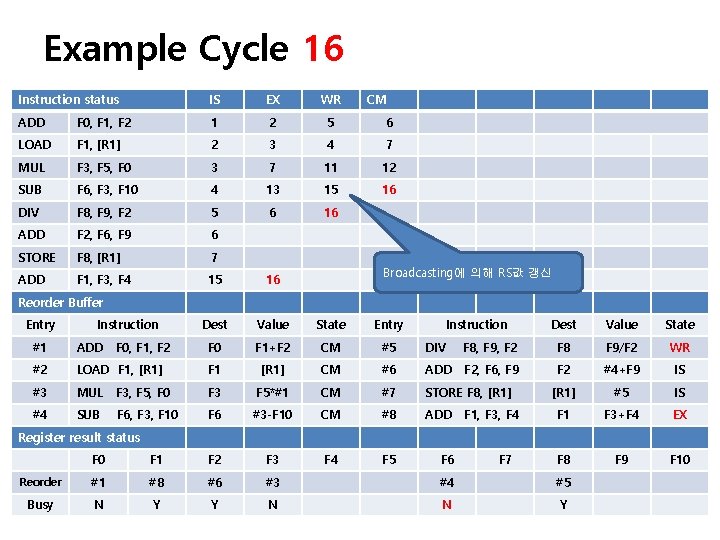

Example Cycle 16 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 ADD F 2, F 6, F 9 6 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 16 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Broadcasting에 의해 RS값 갱신 Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 WR F 2, F 6, F 9 F 2 #4+F 9 IS [R 1] #5 IS F 1 F 3+F 4 EX F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y N N Y

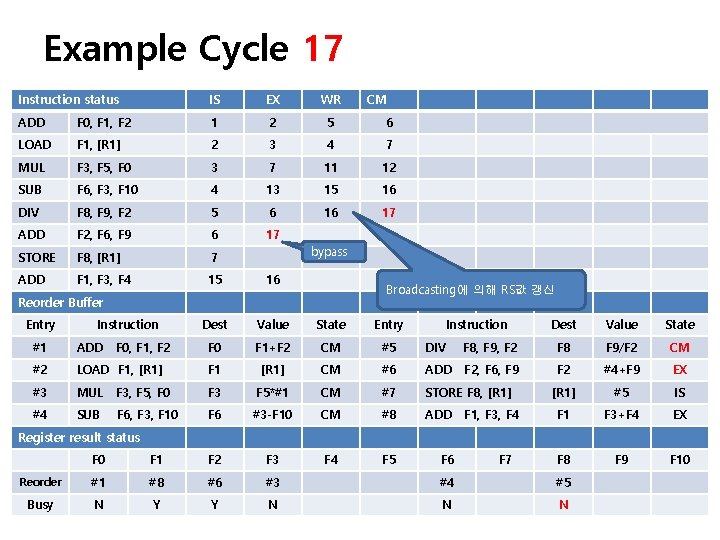

Example Cycle 17 Instruction status IS EX WR ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 15 16 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV bypass Broadcasting에 의해 RS값 갱신 Reorder Buffer Entry Instruction F 0, F 1, F 2 CM Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 EX [R 1] #5 IS F 1 F 3+F 4 EX F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y N N N

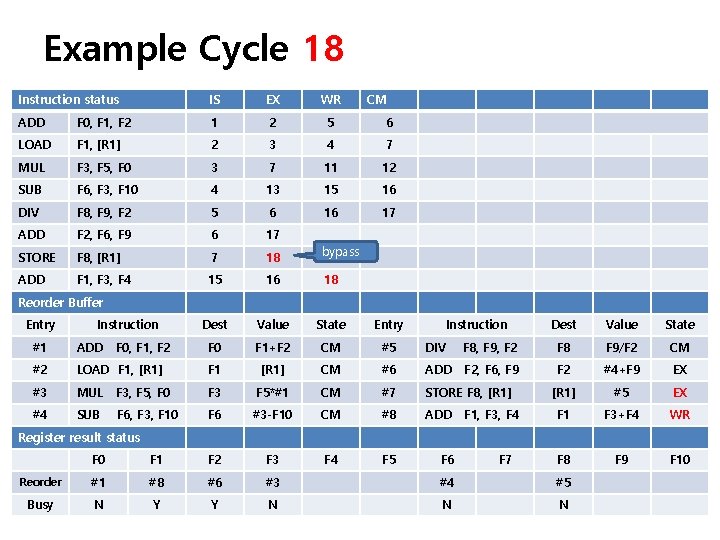

Example Cycle 18 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 STORE F 8, [R 1] 7 18 bypass ADD F 1, F 3, F 4 15 16 18 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 EX [R 1] #5 EX F 1 F 3+F 4 WR F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y N N N

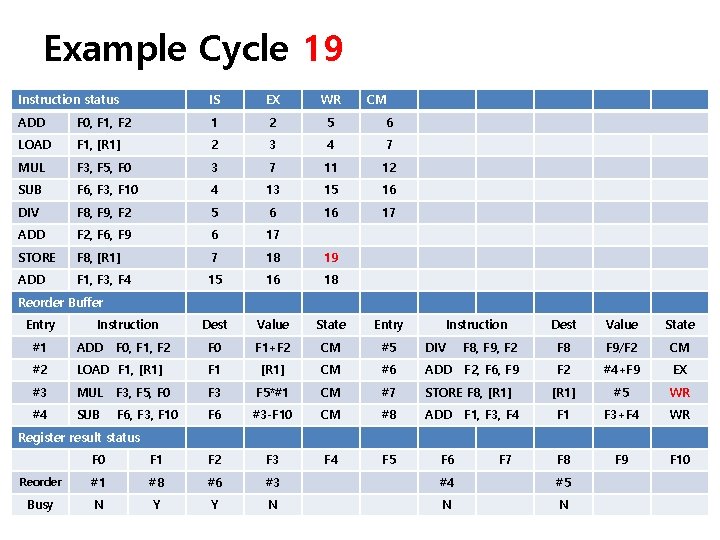

Example Cycle 19 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 STORE F 8, [R 1] 7 18 19 ADD F 1, F 3, F 4 15 16 18 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 EX [R 1] #5 WR F 1 F 3+F 4 WR F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y N N N

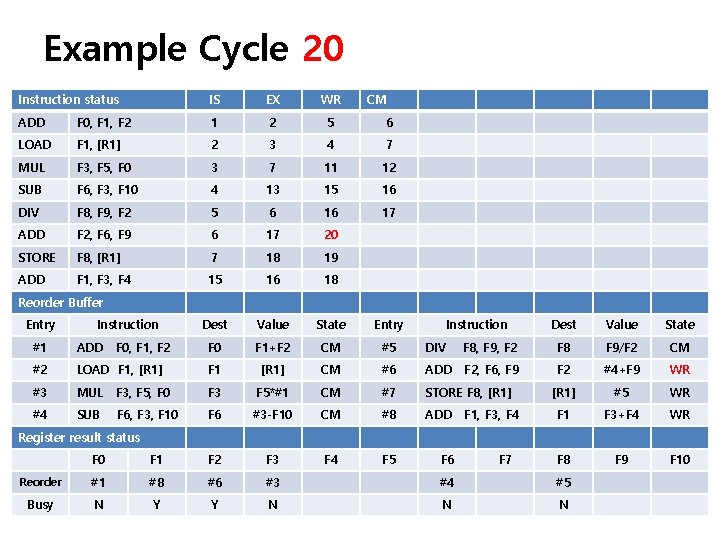

Example Cycle 20 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 20 STORE F 8, [R 1] 7 18 19 ADD F 1, F 3, F 4 15 16 18 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 WR [R 1] #5 WR F 1 F 3+F 4 WR F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y Y N N N

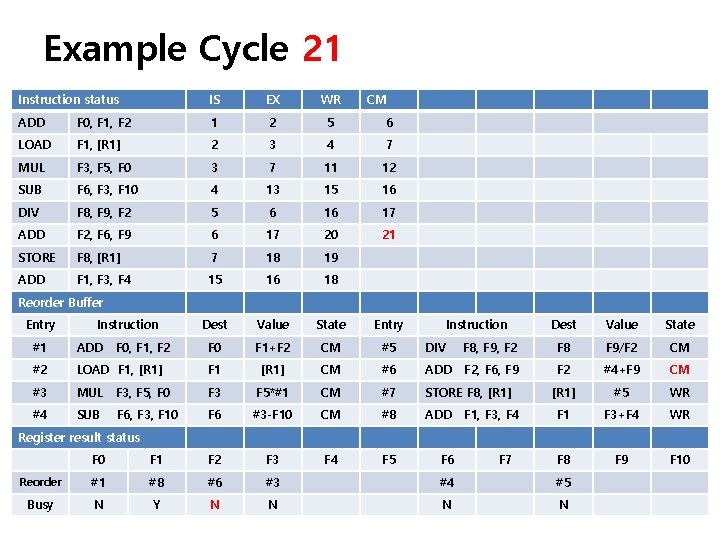

Example Cycle 21 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 20 21 STORE F 8, [R 1] 7 18 19 ADD F 1, F 3, F 4 15 16 18 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 CM [R 1] #5 WR F 1 F 3+F 4 WR F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y N N

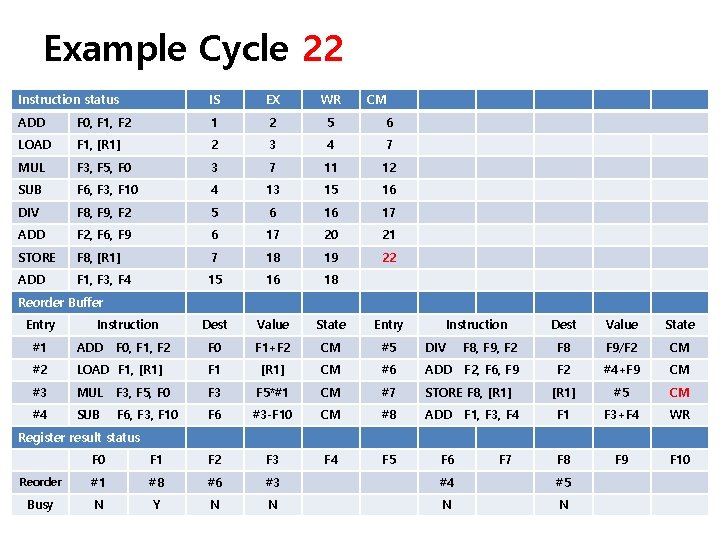

Example Cycle 22 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 20 21 STORE F 8, [R 1] 7 18 19 22 ADD F 1, F 3, F 4 15 16 18 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 CM [R 1] #5 CM F 1 F 3+F 4 WR F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N Y N N

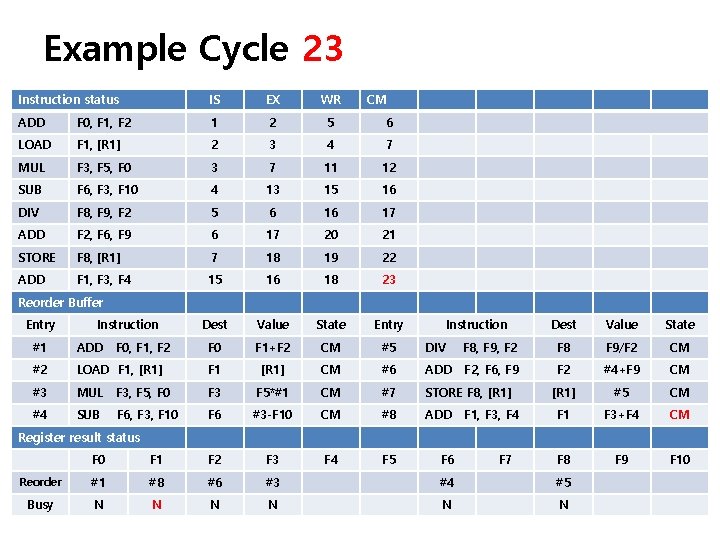

Example Cycle 23 Instruction status IS EX WR CM ADD F 0, F 1, F 2 1 2 5 6 LOAD F 1, [R 1] 2 3 4 7 MUL F 3, F 5, F 0 3 7 11 12 SUB F 6, F 3, F 10 4 13 15 16 DIV F 8, F 9, F 2 5 6 16 17 ADD F 2, F 6, F 9 6 17 20 21 STORE F 8, [R 1] 7 18 19 22 ADD F 1, F 3, F 4 15 16 18 23 Dest Value State Entry F 0 F 1+F 2 CM #5 DIV Reorder Buffer Entry Instruction F 0, F 1, F 2 Instruction Dest Value State F 8, F 9, F 2 F 8 F 9/F 2 CM F 2, F 6, F 9 F 2 #4+F 9 CM [R 1] #5 CM F 1 F 3+F 4 CM F 8 F 9 F 10 #1 ADD #2 LOAD F 1, [R 1] F 1 [R 1] CM #6 ADD #3 MUL F 3, F 5, F 0 F 3 F 5*#1 CM #7 STORE F 8, [R 1] #4 SUB F 6, F 3, F 10 F 6 #3 -F 10 CM #8 ADD F 4 F 5 F 6 F 1, F 3, F 4 Register result status F 0 F 1 F 2 F 3 F 7 Reorder #1 #8 #6 #3 #4 #5 Busy N N N

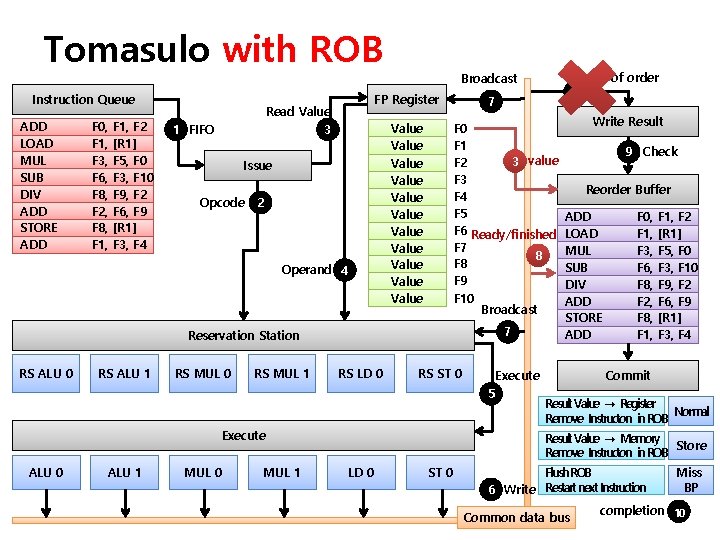

Tomasulo with ROB Instruction Queue ADD LOAD MUL SUB DIV ADD STORE ADD F 0, F 1, F 3, F 6, F 8, F 2, F 8, F 1, F 2 [R 1] F 5, F 0 F 3, F 10 F 9, F 2 F 6, F 9 [R 1] F 3, F 4 FP Register Read Value 1 FIFO 3 Issue Opcode Broadcast 2 Operand 4 Write Result F 0 F 1 9 Check 3 value F 2 F 3 Reorder Buffer F 4 F 5 ADD F 0, F 1, F 2 F 6 Ready/finished LOAD F 1, [R 1] F 7 MUL F 3, F 5, F 0 8 F 8 SUB F 6, F 3, F 10 F 9 DIV F 8, F 9, F 2 F 10 ADD F 2, F 6, F 9 Broadcast STORE F 8, [R 1] 7 ADD F 1, F 3, F 4 Value Value Value Reservation Station RS ALU 0 RS ALU 1 RS MUL 0 RS MUL 1 RS LD 0 RS ST 0 Execute ALU 1 MUL 0 MUL 1 Commit Execute 5 ALU 0 8 7 Out of order Result Value → Register Normal Remove Instructon in ROB Result Value → Memory Store Remove Instructon in ROB LD 0 ST 0 Flush ROB Restart next Instruction 6 Write CDB Common data bus Miss BP completion 10

- Slides: 28