Specificationbased Compaction of Directed Tests for Functional Validation

Specification-based Compaction of Directed Tests for Functional Validation of Pipelined Processors Heon-Mo Koo and Prabhat Mishra Embedded Systems Lab, CISE University of Florida

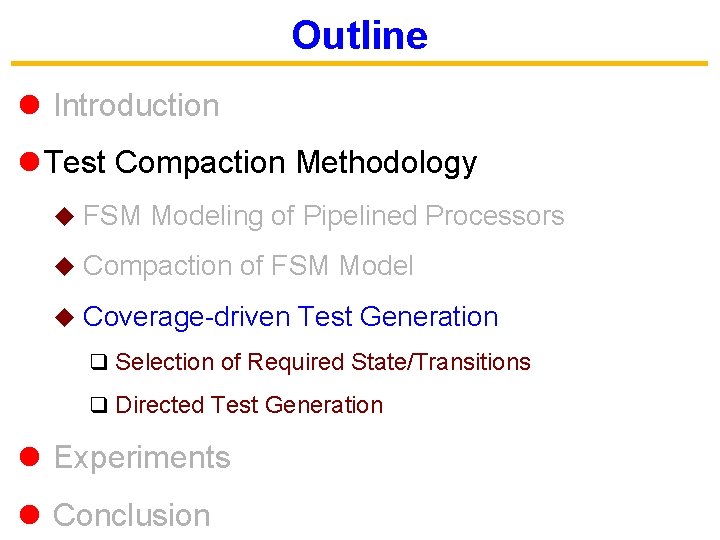

Outline l Introduction l Related Work l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model u Coverage-driven Test Generation l Experiments l Conclusion

Introduction l Exponential growth in verification complexity Verification complexity design complexity u How to reduce overall validation effort? u l Simulation-based validation is widely used u Billions of random and directed-random tests l Directed tests are promising Drastically less number of tests are required to obtain the same coverage goal. u The number can still be extremely large u l We propose a test compaction technique u Reduces the required number of directed tests. 3

Outline l Introduction l Related Work l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model u Coverage-driven Test Generation l Experiments l Conclusion

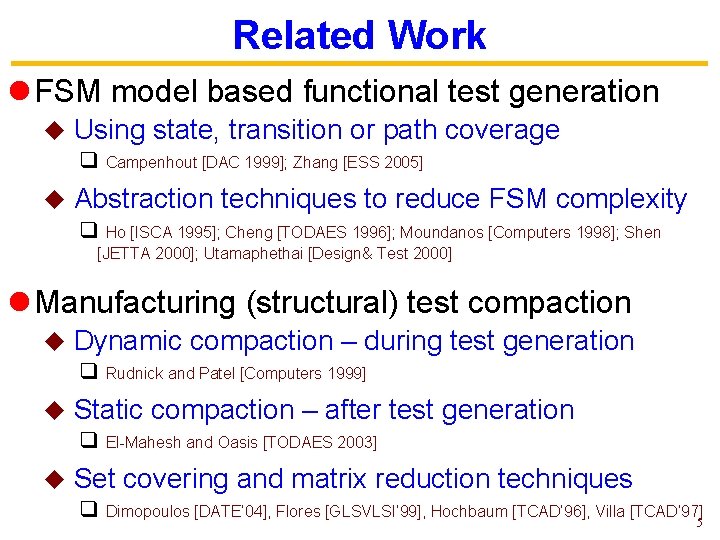

Related Work l FSM model based functional test generation u Using state, transition or path coverage q u Campenhout [DAC 1999]; Zhang [ESS 2005] Abstraction techniques to reduce FSM complexity q Ho [ISCA 1995]; Cheng [TODAES 1996]; Moundanos [Computers 1998]; Shen [JETTA 2000]; Utamaphethai [Design& Test 2000] l Manufacturing (structural) test compaction u Dynamic compaction – during test generation q u Static compaction – after test generation q u Rudnick and Patel [Computers 1999] El-Mahesh and Oasis [TODAES 2003] Set covering and matrix reduction techniques q Dimopoulos [DATE’ 04], Flores [GLSVLSI’ 99], Hochbaum [TCAD’ 96], Villa [TCAD’ 97] 5

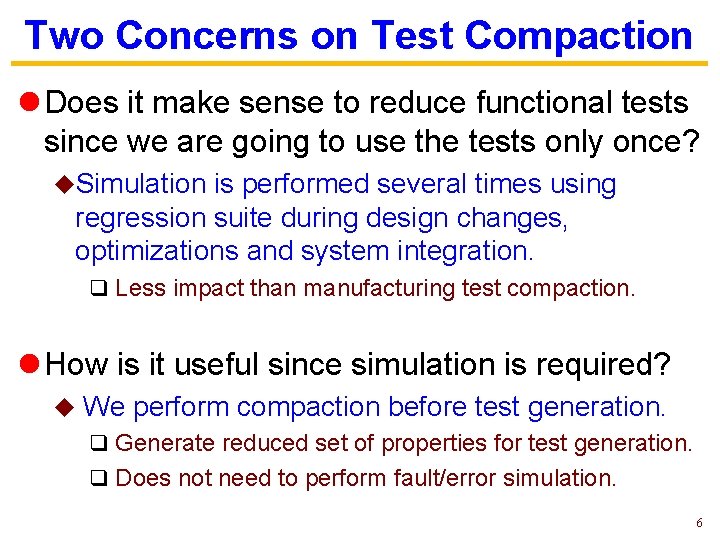

Two Concerns on Test Compaction l Does it make sense to reduce functional tests since we are going to use the tests only once? u. Simulation is performed several times using regression suite during design changes, optimizations and system integration. q Less impact than manufacturing test compaction. l How is it useful since simulation is required? u We perform compaction before test generation. q Generate reduced set of properties for test generation. q Does not need to perform fault/error simulation. 6

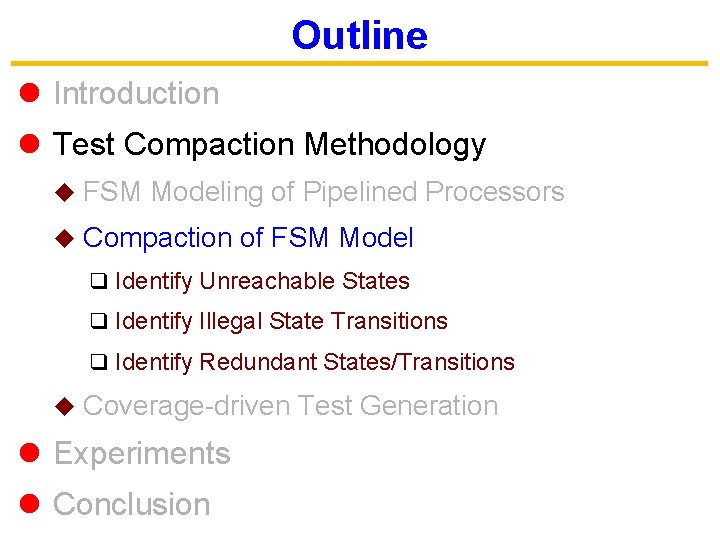

Outline l Introduction l Related Work l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model u Coverage-driven Test Generation l Experiments l Conclusion

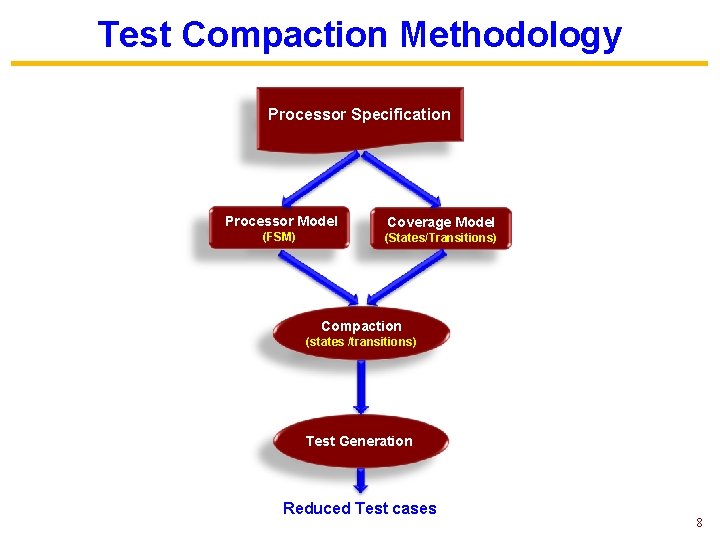

Test Compaction Methodology Processor Specification Processor Model Coverage Model (FSM) (States/Transitions) Compaction (states /transitions) Test Generation Reduced Test cases 8

Outline l Introduction l Test Compaction Methodology u FSM Modeling of Pipelined Processors q Modeling of FSM States q Modeling of FSM Transitions q Functional Coverage u Compaction of FSM Model u Coverage-driven Test Generation l Experiments l Conclusion

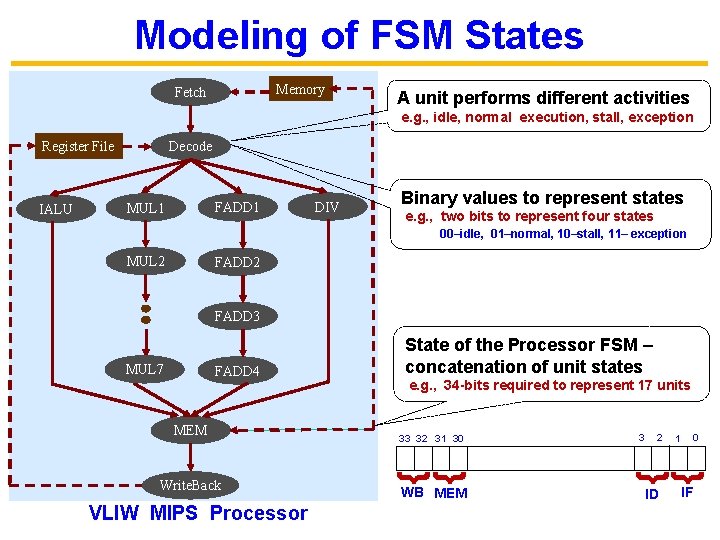

Modeling of FSM States Memory Fetch A unit performs different activities e. g. , idle, normal execution, stall, exception Register File FADD 1 MUL 1 DIV Binary values to represent states e. g. , two bits to represent four states 00–idle, 01–normal, 10–stall, 11– exception MUL 2 FADD 3 FADD 4 MEM Write. Back VLIW MIPS Processor e. g. , 34 -bits required to represent 17 units 33 32 31 30 WB MEM 3 2 0 1 { { MUL 7 State of the Processor FSM – concatenation of unit states { { IALU Decode ID IF

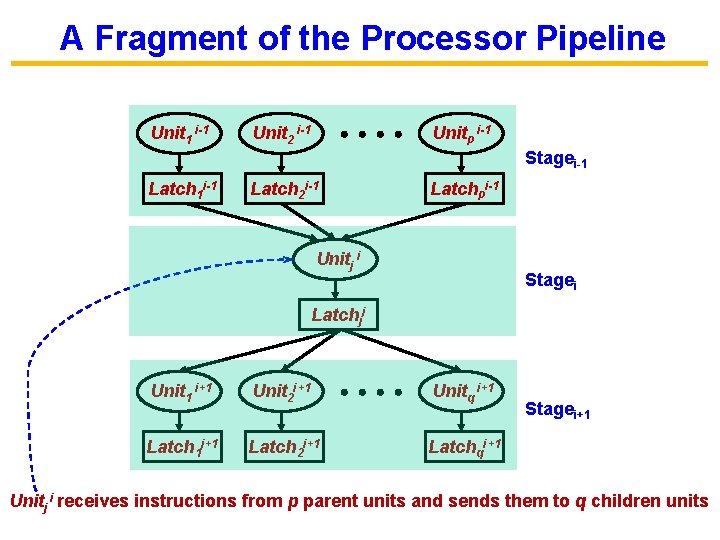

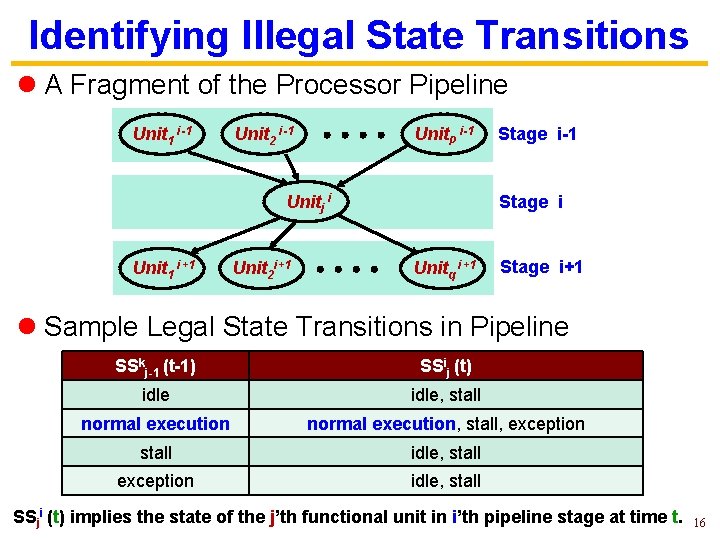

A Fragment of the Processor Pipeline Unit 1 i-1 Unit 2 i-1 Unitp i-1 Stagei-1 Latch 1 i-1 Latch 2 i-1 Latchpi-1 Unitj i Stagei Latchji Unit 1 i+1 Unit 2 i+1 Unitq i+1 Latch 1 i+1 Latch 2 i+1 Latchqi+1 Stagei+1 Unitj i receives instructions from p parent units and sends them to q children units

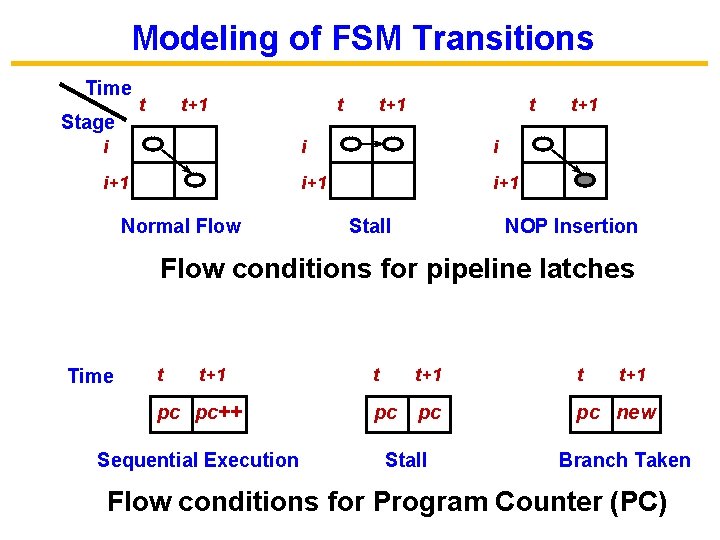

Modeling of FSM Transitions Time Stage t t+1 t i i+1 i+1 Normal Flow Stall t+1 NOP Insertion Flow conditions for pipeline latches Time t t+1 pc pc++ Sequential Execution t t+1 t pc pc pc new Stall t+1 Branch Taken Flow conditions for Program Counter (PC)

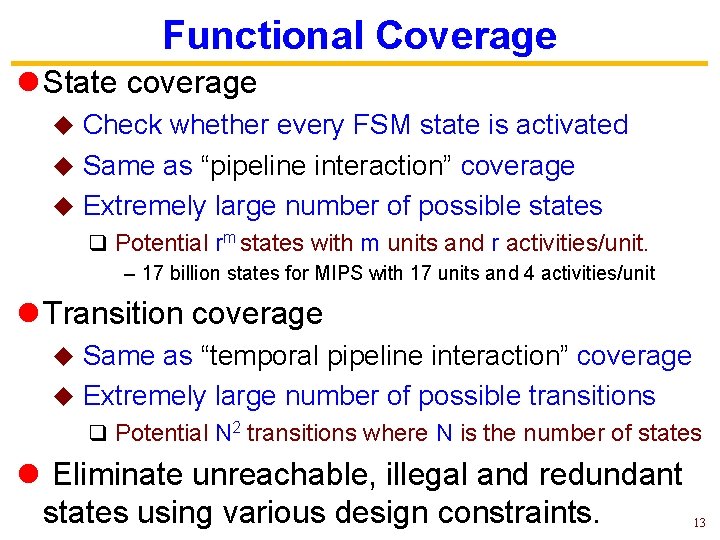

Functional Coverage l State coverage Check whether every FSM state is activated u Same as “pipeline interaction” coverage u Extremely large number of possible states u q Potential rm states with m units and r activities/unit. – 17 billion states for MIPS with 17 units and 4 activities/unit l Transition coverage Same as “temporal pipeline interaction” coverage u Extremely large number of possible transitions u q Potential N 2 transitions where N is the number of states l Eliminate unreachable, illegal and redundant states using various design constraints. 13

Outline l Introduction l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model q Identify Unreachable States q Identify Illegal State Transitions q Identify Redundant States/Transitions u Coverage-driven Test Generation l Experiments l Conclusion

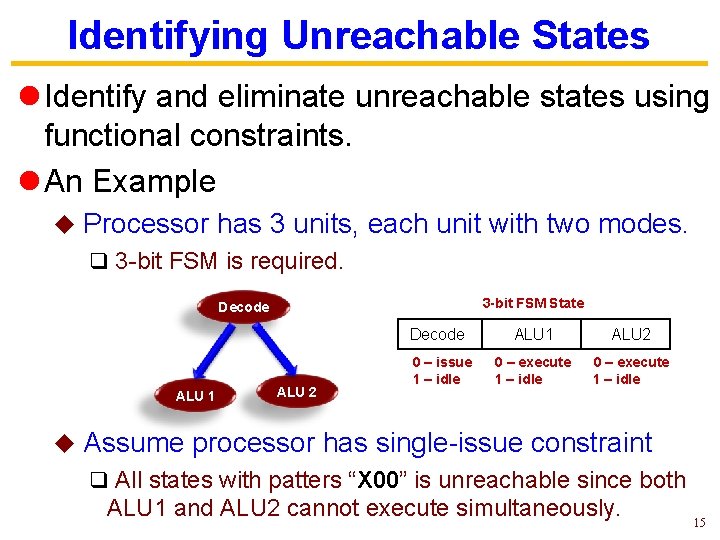

Identifying Unreachable States l Identify and eliminate unreachable states using functional constraints. l An Example u Processor has 3 units, each unit with two modes. q 3 -bit FSM is required. 3 -bit FSM State Decode ALU 1 u ALU 2 0 – issue 1 – idle ALU 1 ALU 2 0 – execute 1 – idle Assume processor has single-issue constraint q All states with patters “X 00” is unreachable since both ALU 1 and ALU 2 cannot execute simultaneously. 15

Identifying Illegal State Transitions l A Fragment of the Processor Pipeline Unit 1 i-1 Unit 2 i-1 Unitp i-1 Unitj i Unit 1 i+1 Unit 2 i+1 Stage i-1 Stage i Unitq i+1 Stage i+1 l Sample Legal State Transitions in Pipeline SSkj-1 (t-1) SSij (t) idle, stall normal execution, stall, exception stall idle, stall exception idle, stall SSji (t) implies the state of the j’th functional unit in i’th pipeline stage at time t. 16

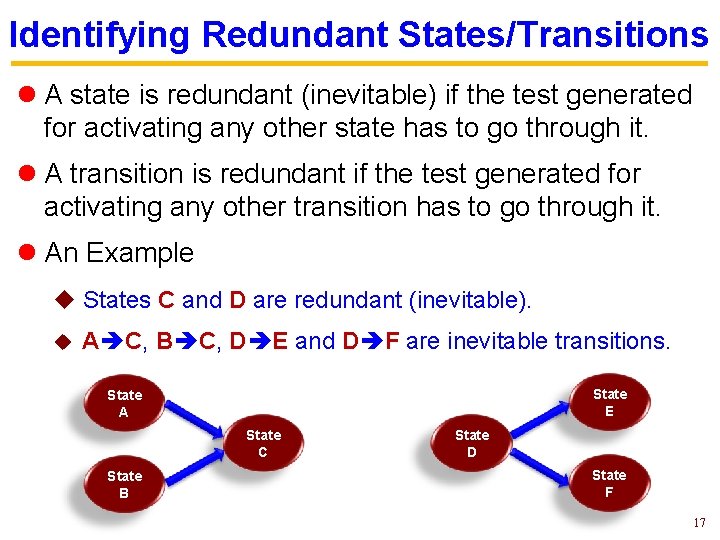

Identifying Redundant States/Transitions l A state is redundant (inevitable) if the test generated for activating any other state has to go through it. l A transition is redundant if the test generated for activating any other transition has to go through it. l An Example u States C and D are redundant (inevitable). u A C, B C, D E and D F are inevitable transitions. State E State A State C State B State D State F 17

Outline l Introduction l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model u Coverage-driven Test Generation q Selection of Required State/Transitions q Directed Test Generation l Experiments l Conclusion

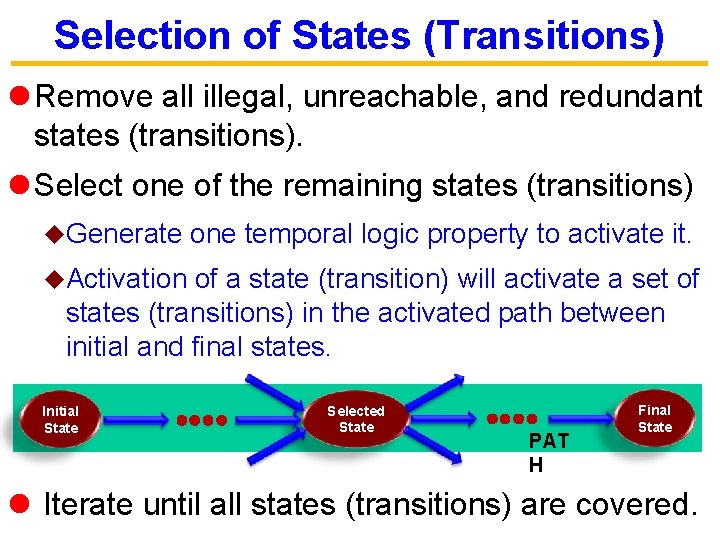

Selection of States (Transitions) l Remove all illegal, unreachable, and redundant states (transitions). l Select one of the remaining states (transitions) u. Generate one temporal logic property to activate it. u. Activation of a state (transition) will activate a set of states (transitions) in the activated path between initial and final states. Initial State Selected State PAT H Final State l Iterate until all states (transitions) are covered.

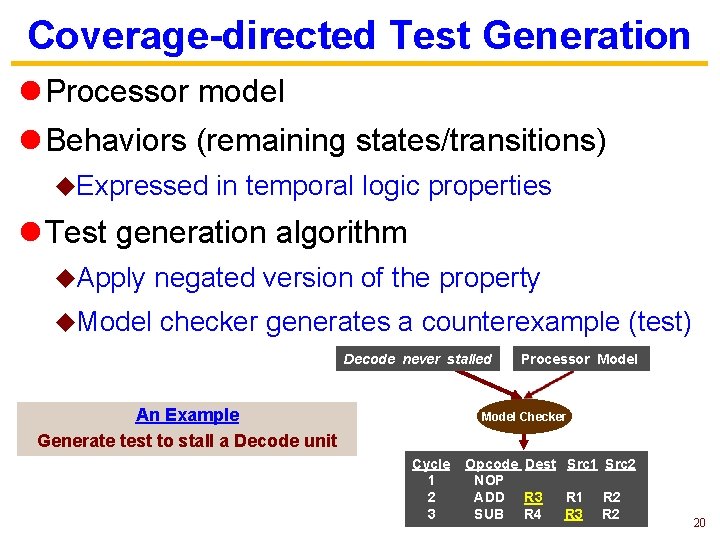

Coverage-directed Test Generation l Processor model l Behaviors (remaining states/transitions) u. Expressed in temporal logic properties l Test generation algorithm u. Apply negated version of the property u. Model checker generates a counterexample (test) Decode never stalled An Example Generate test to stall a Decode unit Processor Model Checker Cycle 1 2 3 Opcode Dest Src 1 Src 2 NOP ADD R 3 R 1 R 2 SUB R 4 R 3 R 2 20

Outline l Introduction l Test Compaction Methodology u FSM Modeling of Pipelined Processors u Compaction of FSM Model u Coverage-driven Test Generation l Experiments u. Test Compaction for Two Pipelined Processors q Single-issue MIPS Processor q Superscalar e 500 (dual-issue) Processor l Conclusion

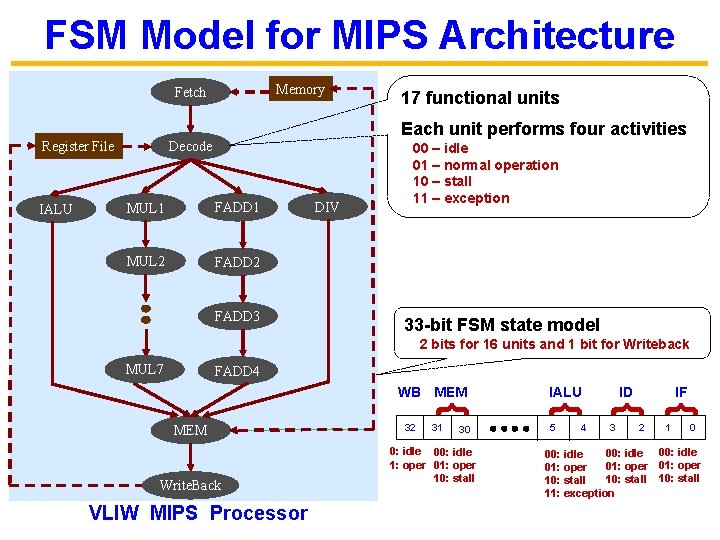

FSM Model for MIPS Architecture Memory Fetch Register File IALU 17 functional units Each unit performs four activities Decode MUL 1 FADD 1 MUL 2 FADD 3 DIV 00 – idle 01 – normal operation 10 – stall 11 – exception 33 -bit FSM state model 2 bits for 16 units and 1 bit for Writeback MUL 7 FADD 4 WB MEM VLIW MIPS Processor 31 30 0: idle 00: idle 1: oper 01: oper 10: stall { { Write. Back 32 IF { { MEM ID IALU 5 3 4 2 1 0 00: idle 01: oper 10: stall 11: exception

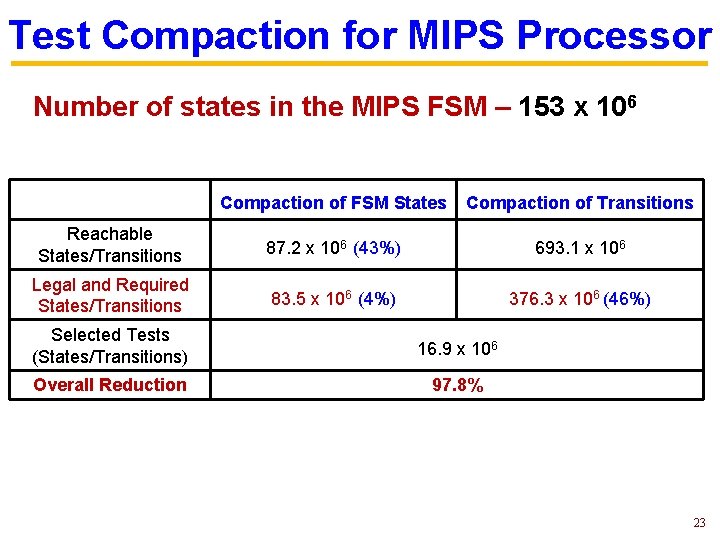

Test Compaction for MIPS Processor Number of states in the MIPS FSM – 153 x 106 Compaction of FSM States Compaction of Transitions Reachable States/Transitions 87. 2 x 106 (43%) 693. 1 x 106 Legal and Required States/Transitions 83. 5 x 106 (4%) 376. 3 x 106 (46%) Selected Tests (States/Transitions) 16. 9 x 106 Overall Reduction 97. 8% 23

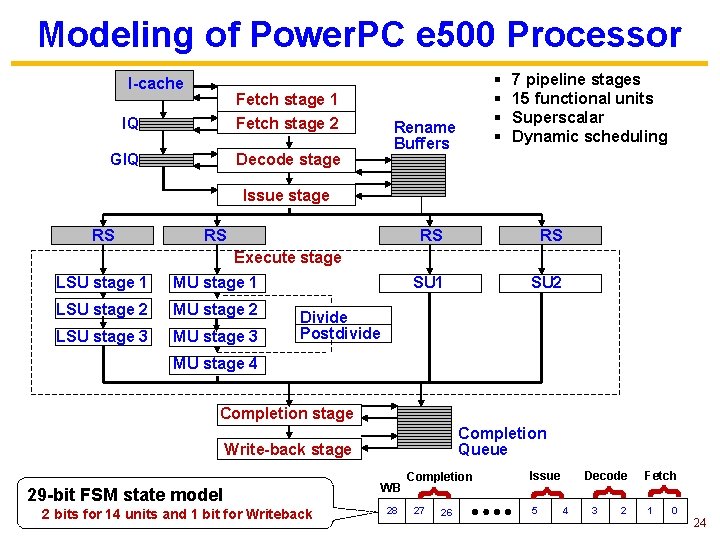

Modeling of Power. PC e 500 Processor I-cache IQ Fetch stage 1 Fetch stage 2 GIQ Decode stage § § Rename Buffers 7 pipeline stages 15 functional units Superscalar Dynamic scheduling Issue stage RS RS SU 1 SU 2 Execute stage LSU stage 1 MU stage 1 LSU stage 2 MU stage 2 LSU stage 3 MU stage 3 Divide Postdivide MU stage 4 Completion stage Completion Queue Write-back stage 26 Fetch { 27 Decode { 28 Issue { 2 bits for 14 units and 1 bit for Writeback Completion { 29 -bit FSM state model WB 5 3 1 4 2 0 24

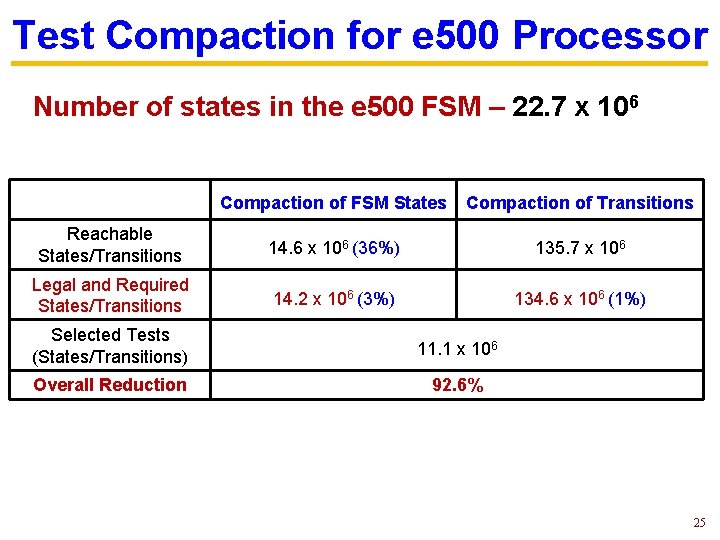

Test Compaction for e 500 Processor Number of states in the e 500 FSM – 22. 7 x 106 Compaction of FSM States Compaction of Transitions Reachable States/Transitions 14. 6 x 106 (36%) 135. 7 x 106 Legal and Required States/Transitions 14. 2 x 106 (3%) 134. 6 x 106 (1%) Selected Tests (States/Transitions) 11. 1 x 106 Overall Reduction 92. 6% 25

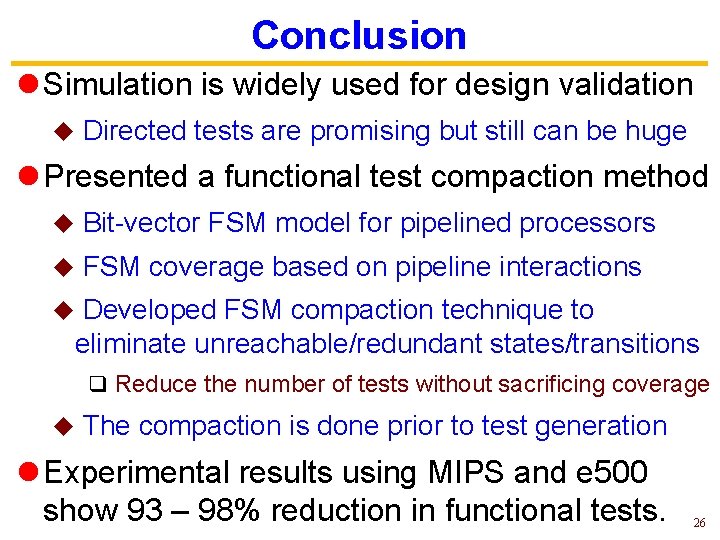

Conclusion l Simulation is widely used for design validation u Directed tests are promising but still can be huge l Presented a functional test compaction method u Bit-vector FSM model for pipelined processors u FSM coverage based on pipeline interactions Developed FSM compaction technique to eliminate unreachable/redundant states/transitions u q Reduce the number of tests without sacrificing coverage u The compaction is done prior to test generation l Experimental results using MIPS and e 500 show 93 – 98% reduction in functional tests. 26

Thank you

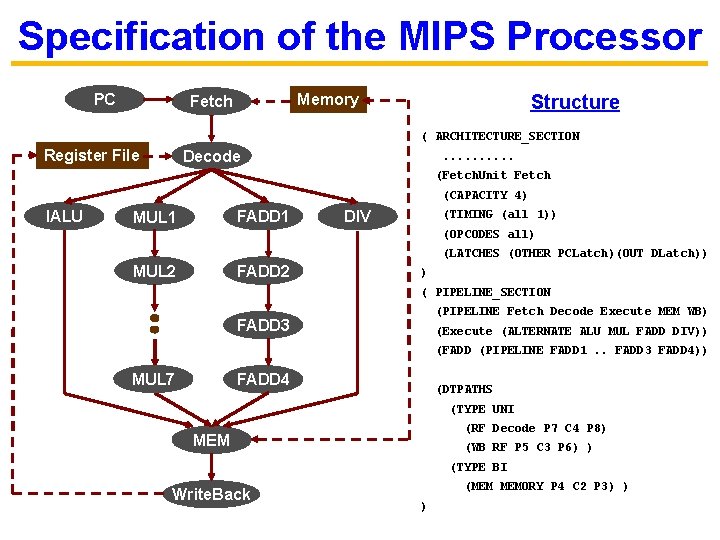

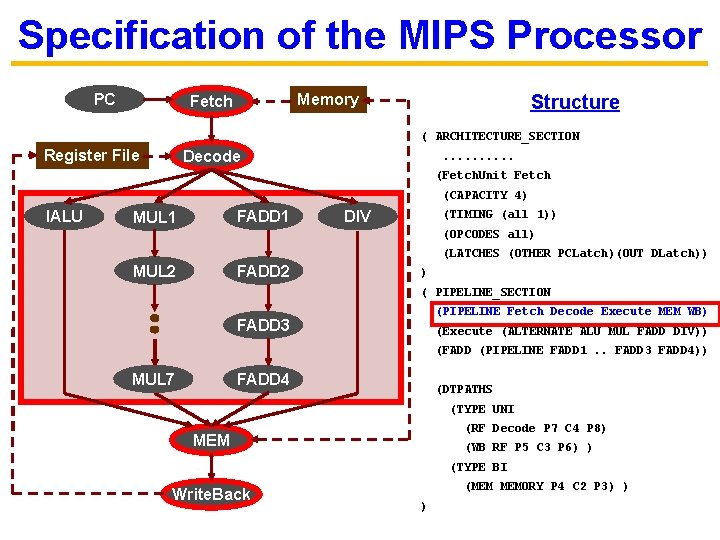

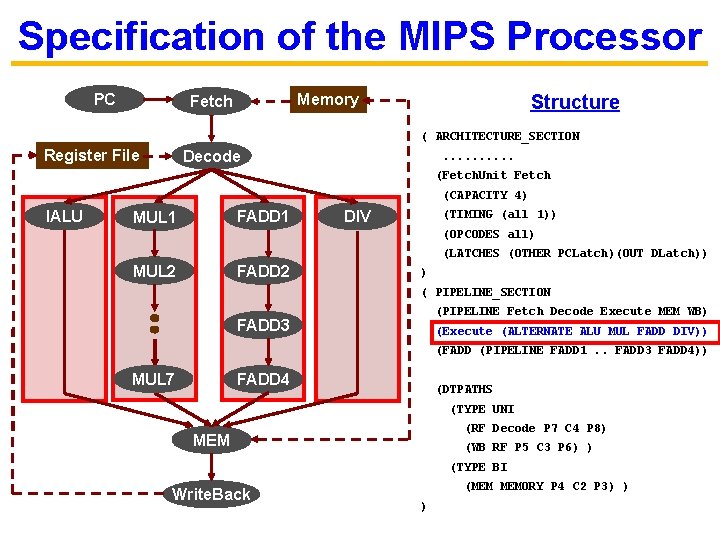

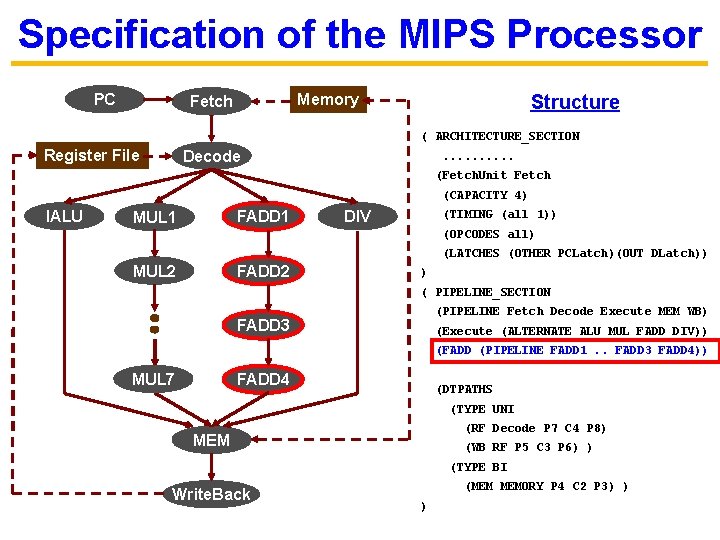

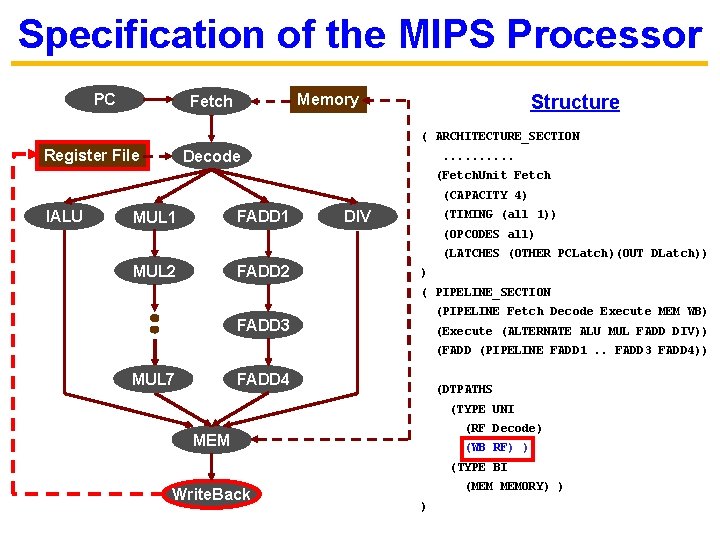

Specification of the MIPS Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode P 7 C 4 P 8) MEM (WB RF P 5 C 3 P 6) ) (TYPE BI Write. Back (MEM MEMORY P 4 C 2 P 3) ) )

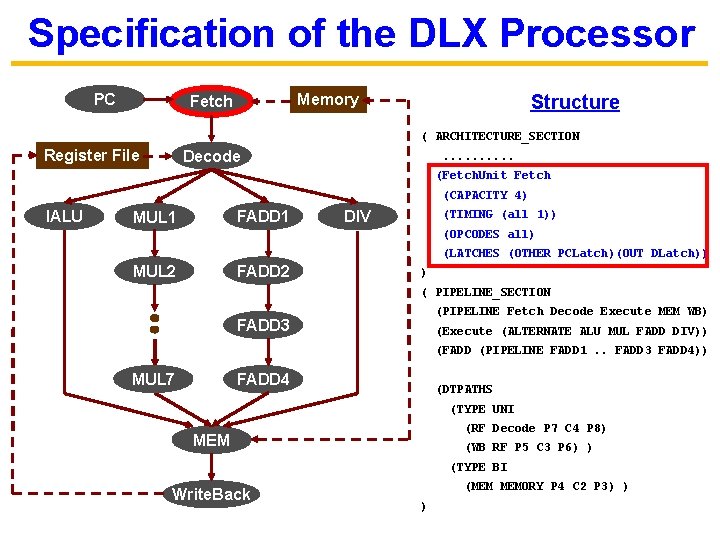

Specification of the DLX Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode P 7 C 4 P 8) MEM (WB RF P 5 C 3 P 6) ) (TYPE BI Write. Back (MEM MEMORY P 4 C 2 P 3) ) )

Specification of the MIPS Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode P 7 C 4 P 8) MEM (WB RF P 5 C 3 P 6) ) (TYPE BI Write. Back (MEM MEMORY P 4 C 2 P 3) ) )

Specification of the MIPS Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode P 7 C 4 P 8) MEM (WB RF P 5 C 3 P 6) ) (TYPE BI Write. Back (MEM MEMORY P 4 C 2 P 3) ) )

Specification of the MIPS Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode P 7 C 4 P 8) MEM (WB RF P 5 C 3 P 6) ) (TYPE BI Write. Back (MEM MEMORY P 4 C 2 P 3) ) )

Specification of the MIPS Processor PC Structure Memory Fetch ( ARCHITECTURE_SECTION Register File Decode . . (Fetch. Unit Fetch (CAPACITY 4) IALU FADD 1 MUL 1 DIV (TIMING (all 1)) (OPCODES all) (LATCHES (OTHER PCLatch)(OUT DLatch)) MUL 2 FADD 2 ) ( PIPELINE_SECTION (PIPELINE Fetch Decode Execute MEM WB) FADD 3 (Execute (ALTERNATE ALU MUL FADD DIV)) (FADD (PIPELINE FADD 1. . FADD 3 FADD 4)) MUL 7 FADD 4 (DTPATHS (TYPE UNI (RF Decode) MEM (WB RF) ) (TYPE BI Write. Back (MEM MEMORY) ) )

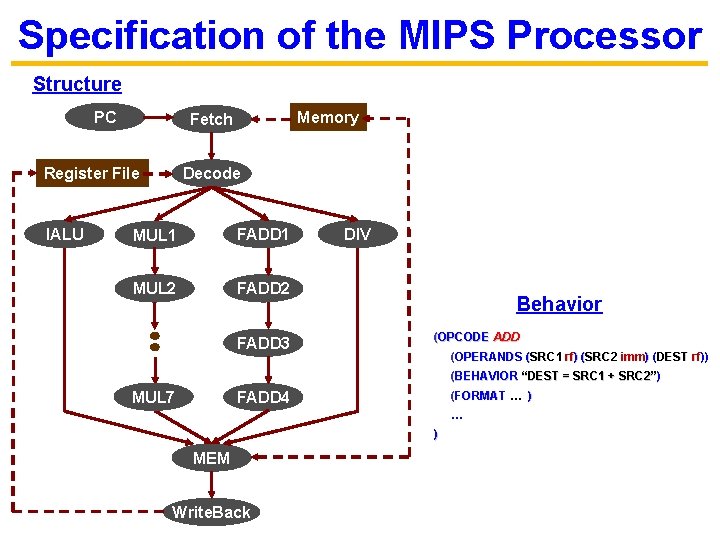

Specification of the MIPS Processor Structure PC Register File IALU Memory Fetch Decode MUL 1 FADD 1 MUL 2 FADD 3 DIV Behavior (OPCODE ADD (OPERANDS (SRC 1 rf) (SRC 2 imm) (DEST rf)) (BEHAVIOR “DEST = SRC 1 + SRC 2”) MUL 7 FADD 4 (FORMAT … ) MEM Write. Back

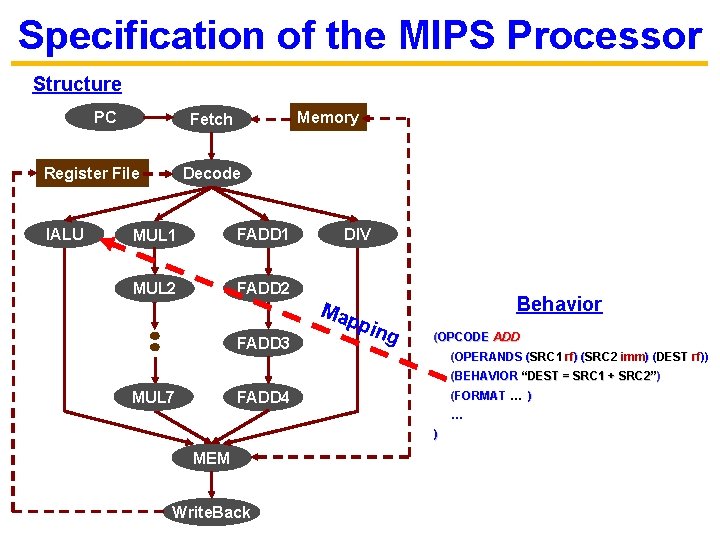

Specification of the MIPS Processor Structure PC Register File IALU Memory Fetch Decode MUL 1 FADD 1 MUL 2 FADD 3 DIV Map pin g Behavior (OPCODE ADD (OPERANDS (SRC 1 rf) (SRC 2 imm) (DEST rf)) (BEHAVIOR “DEST = SRC 1 + SRC 2”) MUL 7 FADD 4 (FORMAT … ) MEM Write. Back

- Slides: 35