SOURCING AND SINKING INPUTS Dc input modules can

- Slides: 23

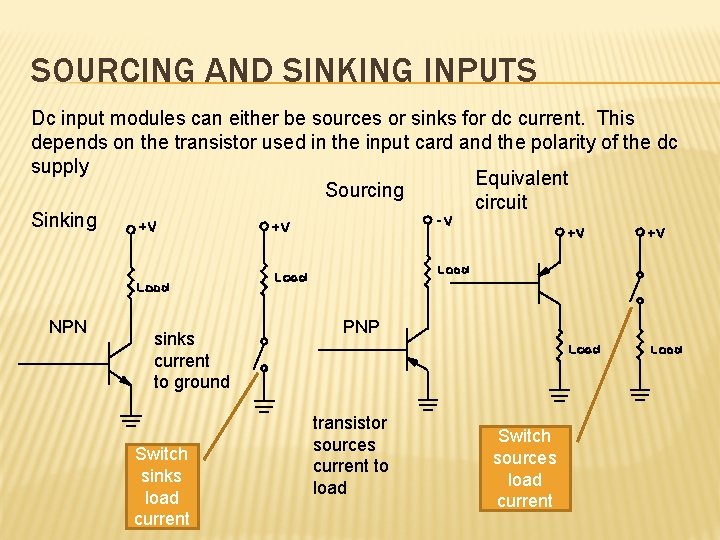

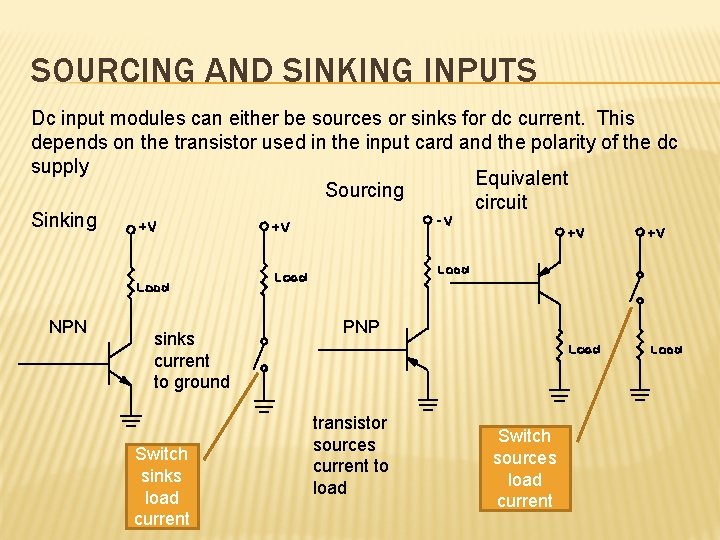

SOURCING AND SINKING INPUTS Dc input modules can either be sources or sinks for dc current. This depends on the transistor used in the input card and the polarity of the dc supply Equivalent Sourcing circuit Sinking NPN sinks current to ground Switch sinks load current PNP transistor sources current to load Switch sources load current

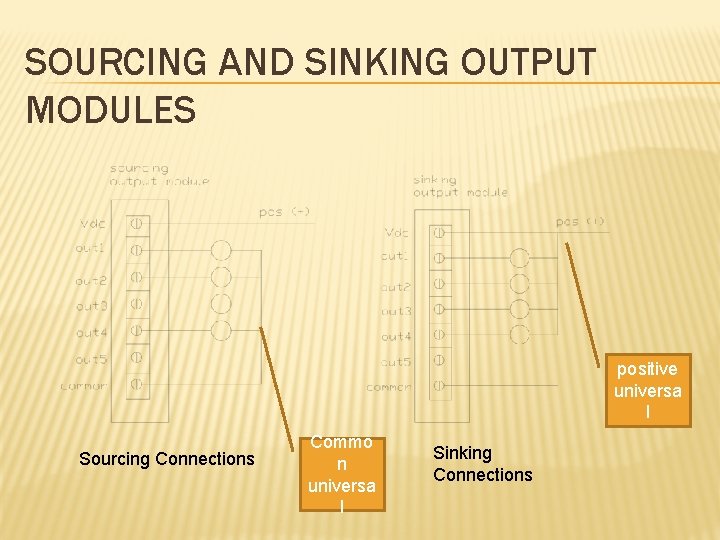

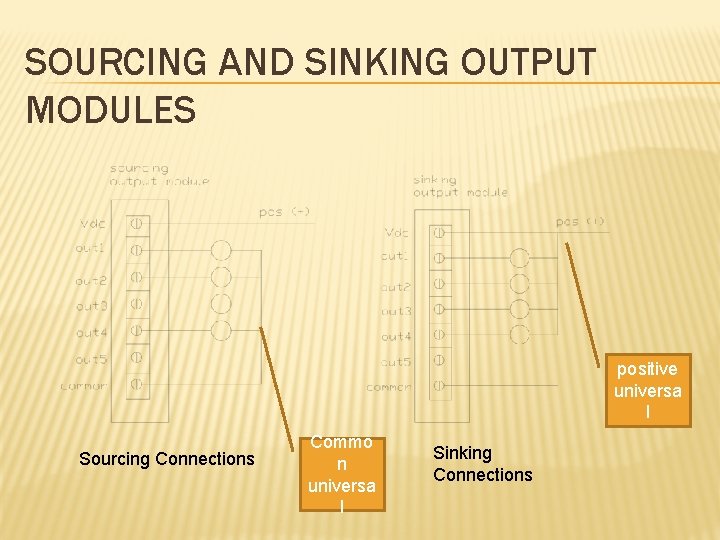

SOURCING AND SINKING OUTPUT MODULES positive universa l Sourcing Connections Commo n universa l Sinking Connections

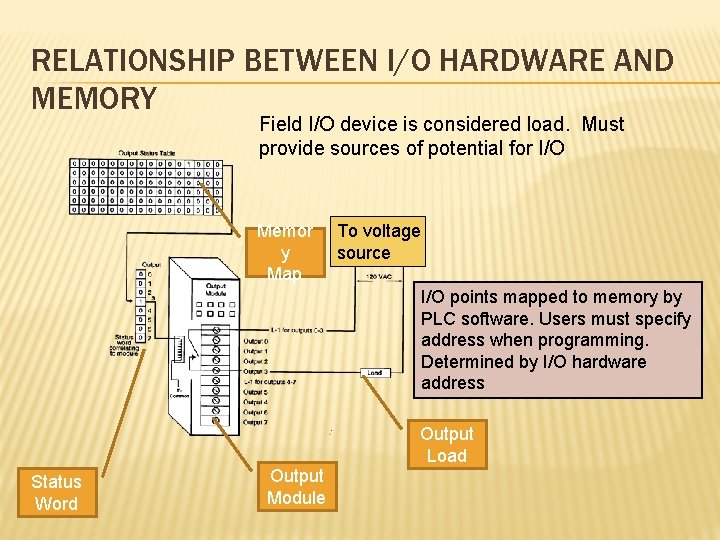

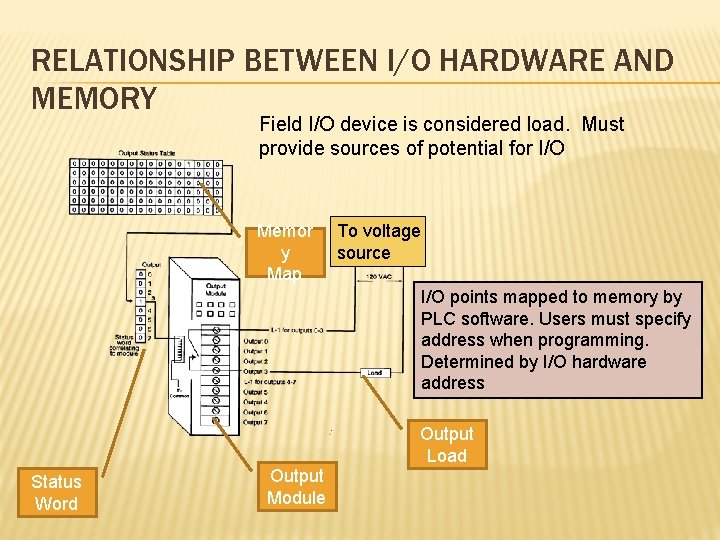

RELATIONSHIP BETWEEN I/O HARDWARE AND MEMORY Field I/O device is considered load. Must provide sources of potential for I/O Memor y Map To voltage source I/O points mapped to memory by PLC software. Users must specify address when programming. Determined by I/O hardware address Output Load Status Word Output Module

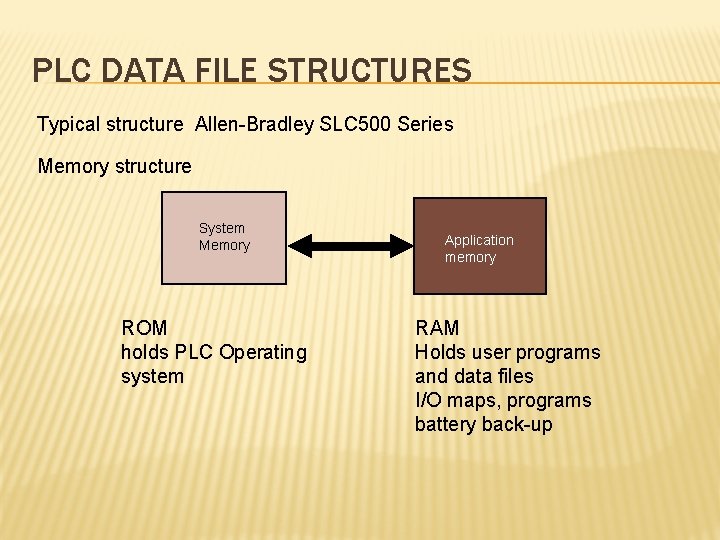

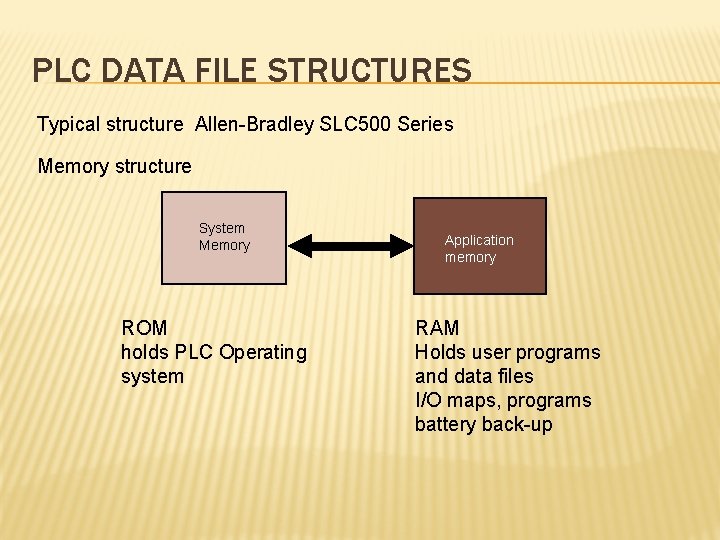

PLC DATA FILE STRUCTURES Typical structure Allen-Bradley SLC 500 Series Memory structure System Memory ROM holds PLC Operating system Application memory RAM Holds user programs and data files I/O maps, programs battery back-up

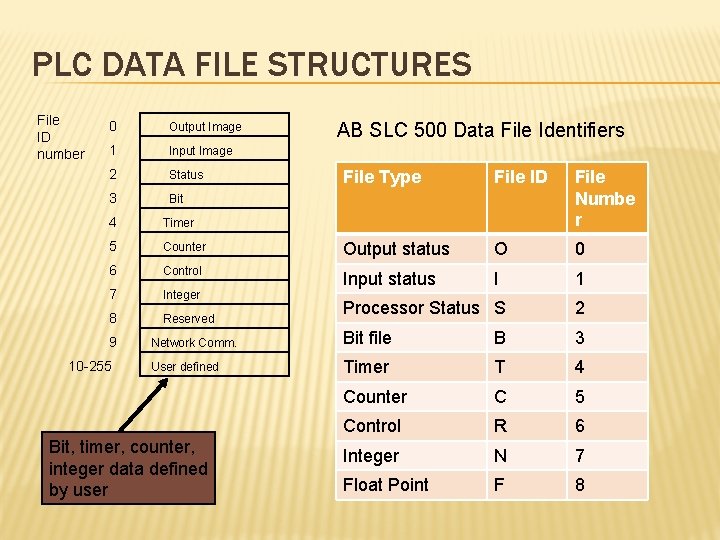

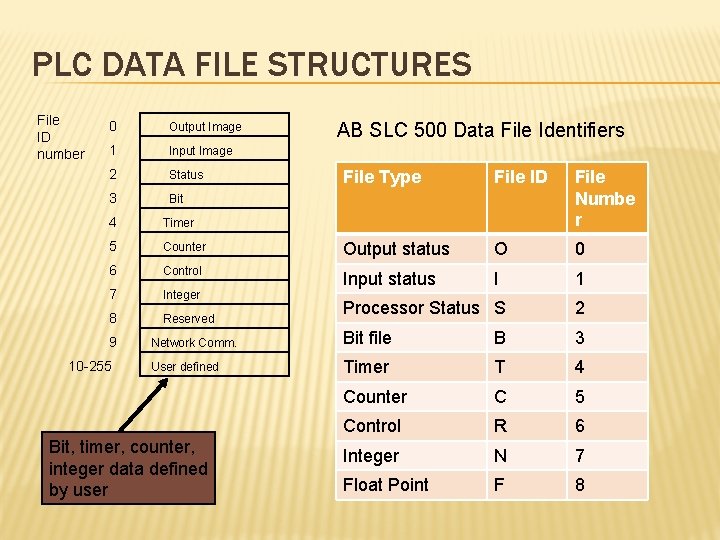

PLC DATA FILE STRUCTURES File ID number 0 Output Image 1 Input Image 2 Status 3 Bit 4 Timer 5 AB SLC 500 Data File Identifiers File Type File ID File Numbe r Counter Output status O 0 6 Control 7 Integer Input status I 1 8 Reserved 9 10 -255 Processor Status S 2 Network Comm. Bit file B 3 User defined Timer T 4 Counter C 5 Control R 6 Integer N 7 Float Point F 8 Bit, timer, counter, integer data defined by user

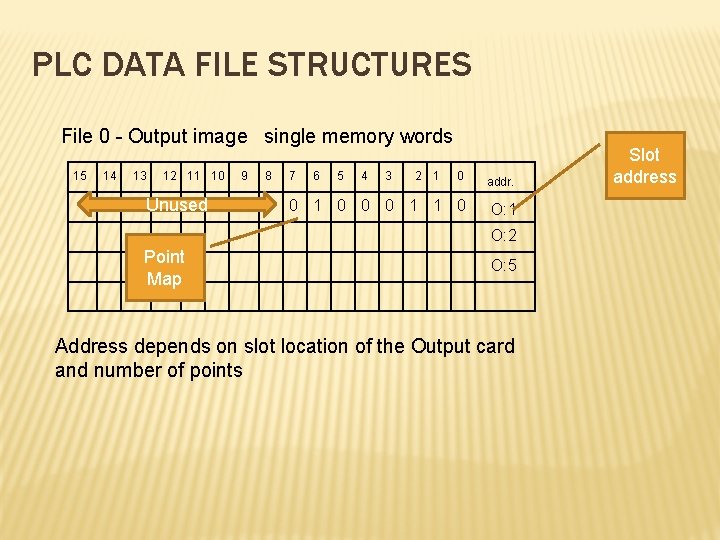

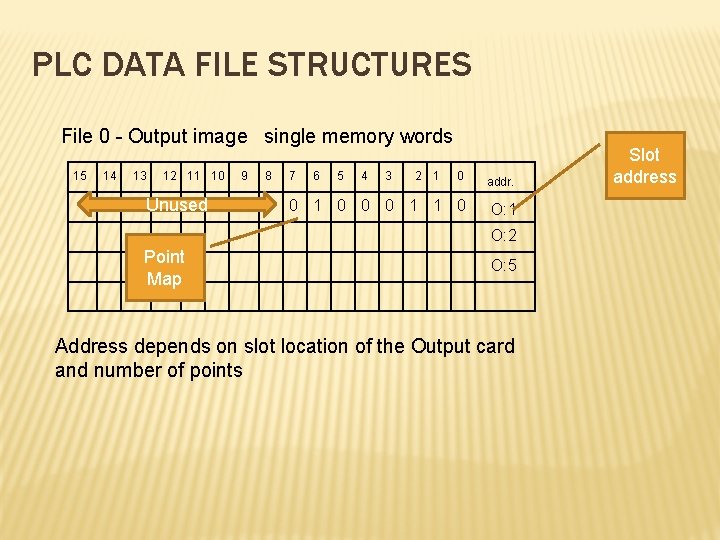

PLC DATA FILE STRUCTURES File 0 - Output image single memory words 15 14 13 12 11 10 Unused 9 8 7 6 5 4 3 2 1 0 addr. 0 1 0 0 0 1 1 0 O: 1 O: 2 Point Map O: 5 Address depends on slot location of the Output card and number of points Slot address

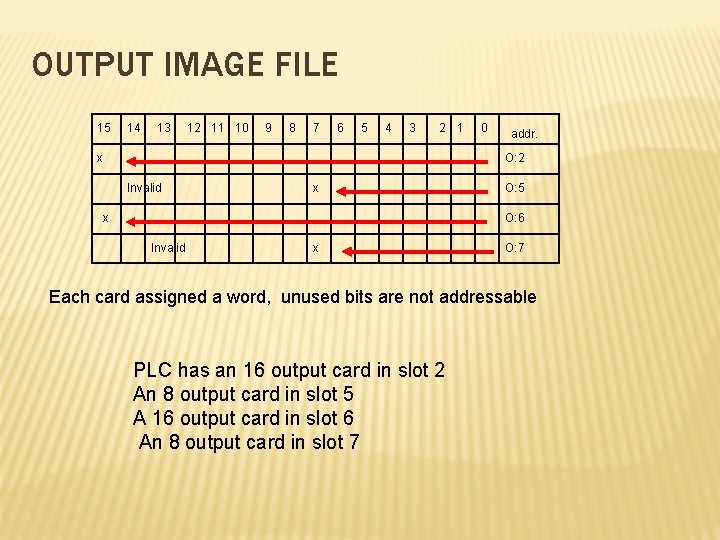

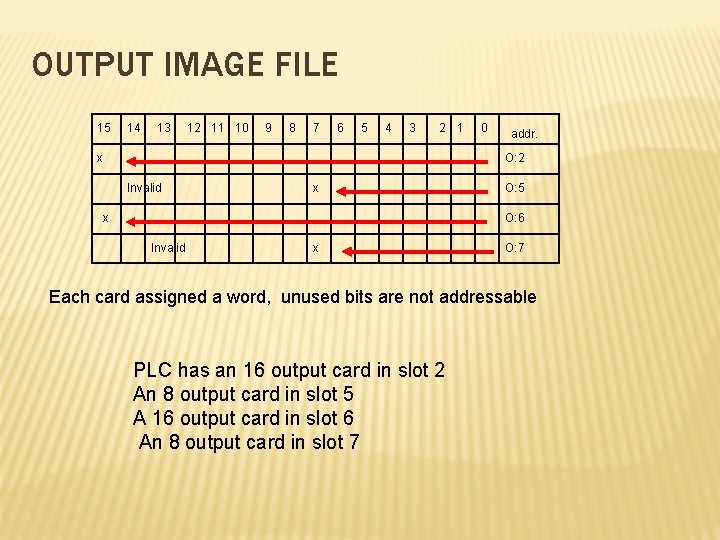

OUTPUT IMAGE FILE 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 x 0 addr. O: 2 Invalid x x O: 5 O: 6 Invalid x O: 7 Each card assigned a word, unused bits are not addressable PLC has an 16 output card in slot 2 An 8 output card in slot 5 A 16 output card in slot 6 An 8 output card in slot 7

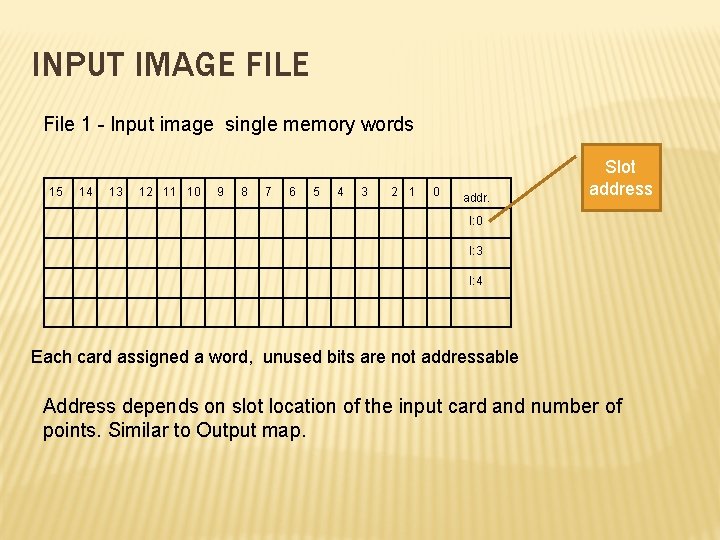

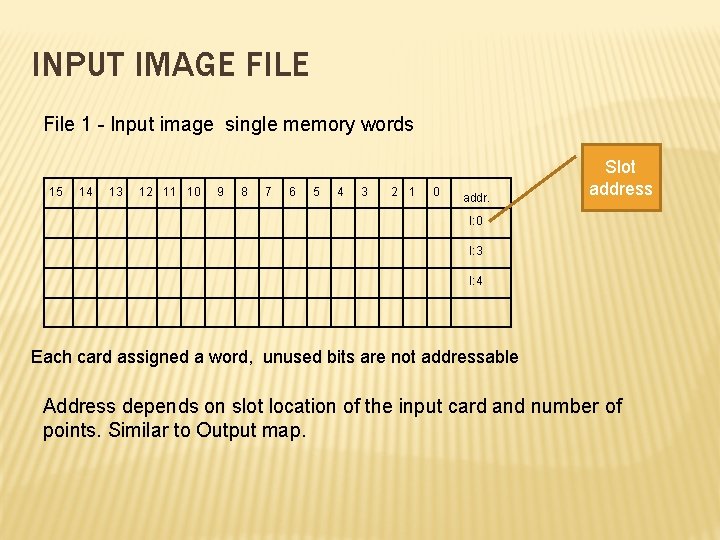

INPUT IMAGE FILE File 1 - Input image single memory words 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 addr. Slot address I: 0 I: 3 I: 4 Each card assigned a word, unused bits are not addressable Address depends on slot location of the input card and number of points. Similar to Output map.

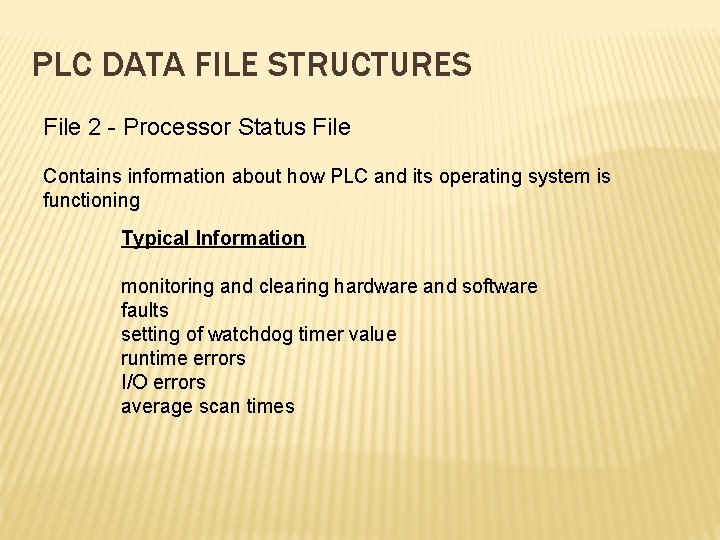

PLC DATA FILE STRUCTURES File 2 - Processor Status File Contains information about how PLC and its operating system is functioning Typical Information monitoring and clearing hardware and software faults setting of watchdog timer value runtime errors I/O errors average scan times

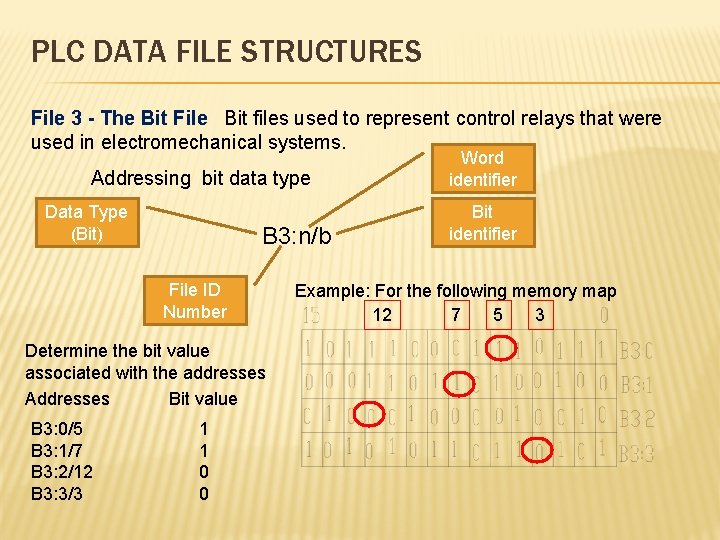

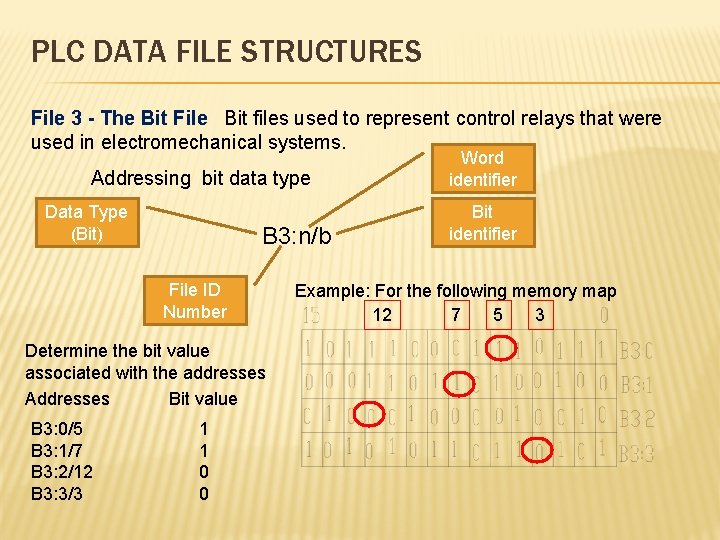

PLC DATA FILE STRUCTURES File 3 - The Bit File Bit files used to represent control relays that were used in electromechanical systems. Addressing bit data type Data Type (Bit) B 3: n/b File ID Number Determine the bit value associated with the addresses Addresses Bit value B 3: 0/5 B 3: 1/7 B 3: 2/12 B 3: 3/3 1 1 0 0 Word identifier Bit identifier Example: For the following memory map 12 7 5 3

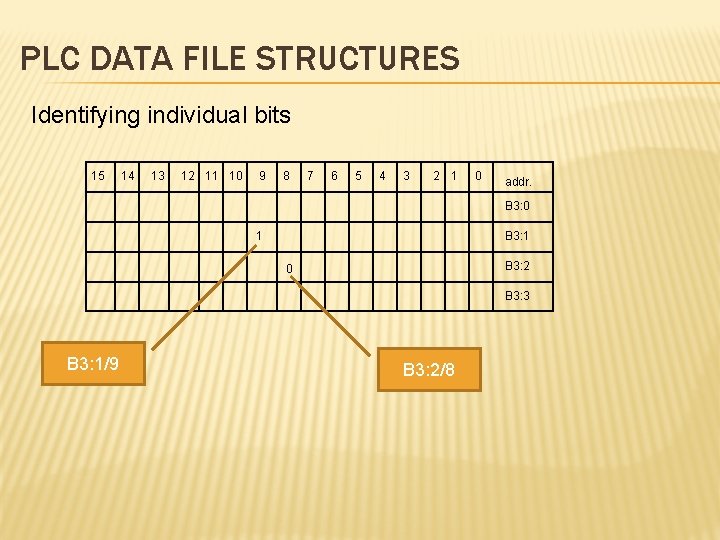

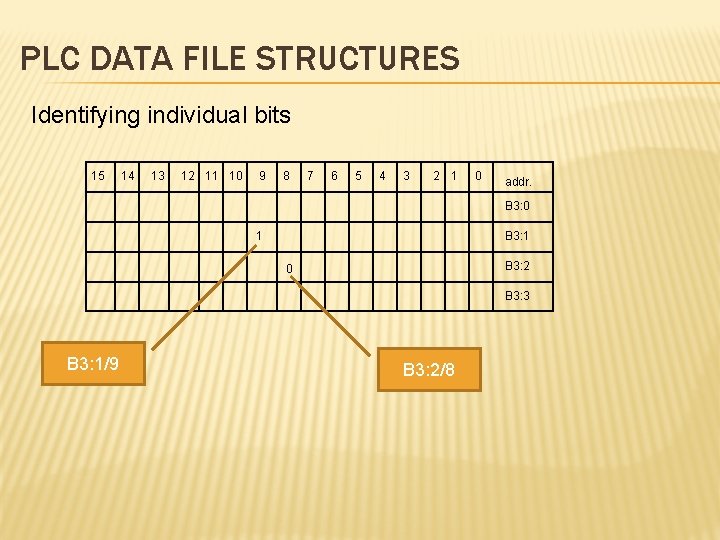

PLC DATA FILE STRUCTURES Identifying individual bits 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 addr. B 3: 0 1 B 3: 2 0 B 3: 3 B 3: 1/9 B 3: 2/8

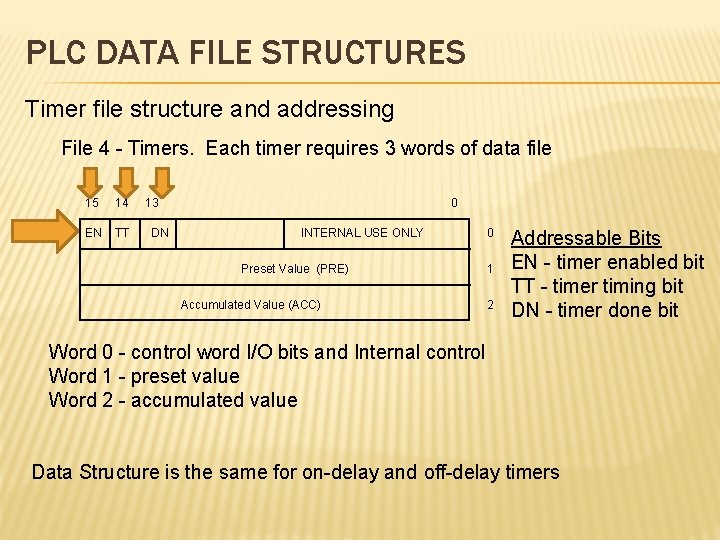

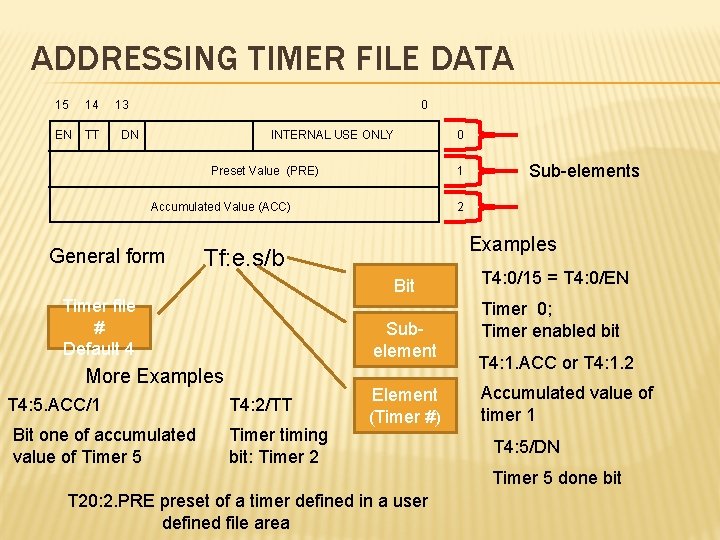

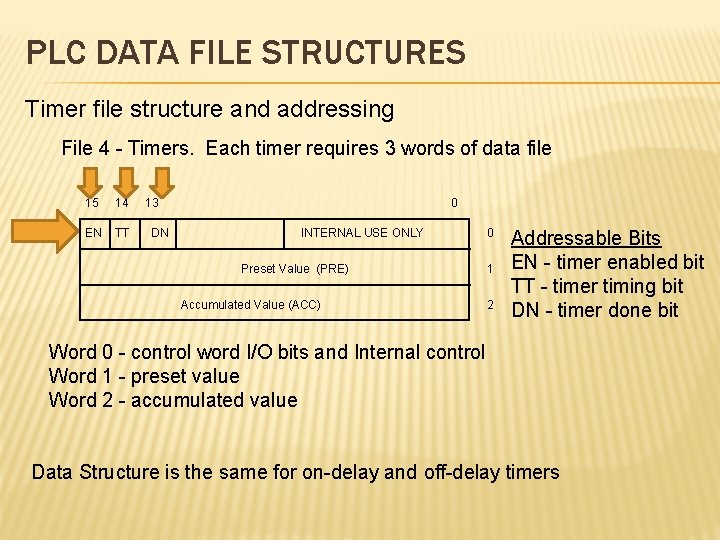

PLC DATA FILE STRUCTURES Timer file structure and addressing File 4 - Timers. Each timer requires 3 words of data file 15 14 EN TT 13 DN 0 INTERNAL USE ONLY Preset Value (PRE) Accumulated Value (ACC) 0 1 2 Addressable Bits EN - timer enabled bit TT - timer timing bit DN - timer done bit Word 0 - control word I/O bits and Internal control Word 1 - preset value Word 2 - accumulated value Data Structure is the same for on-delay and off-delay timers

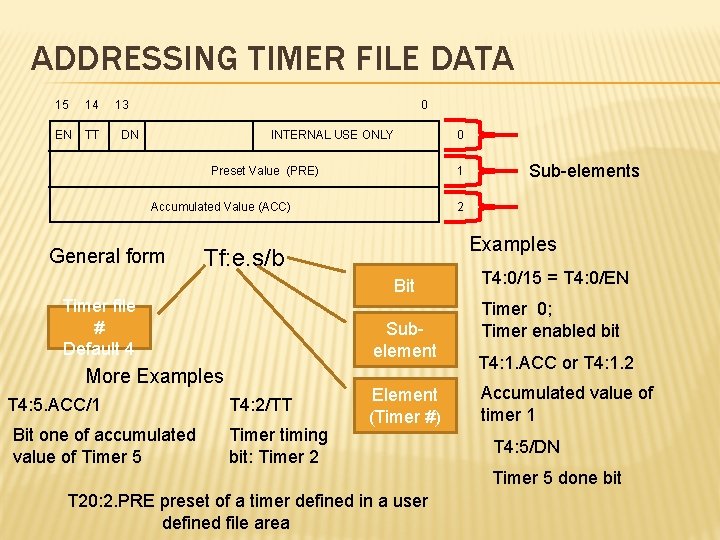

ADDRESSING TIMER FILE DATA 15 14 EN TT 13 0 DN INTERNAL USE ONLY 0 Preset Value (PRE) 1 Accumulated Value (ACC) General form 2 Examples Tf: e. s/b Bit Timer file # Default 4 Subelement More Examples T 4: 5. ACC/1 Bit one of accumulated value of Timer 5 T 4: 2/TT Timer timing bit: Timer 2 Sub-elements Element (Timer #) T 4: 0/15 = T 4: 0/EN Timer 0; Timer enabled bit T 4: 1. ACC or T 4: 1. 2 Accumulated value of timer 1 T 4: 5/DN Timer 5 done bit T 20: 2. PRE preset of a timer defined in a user defined file area

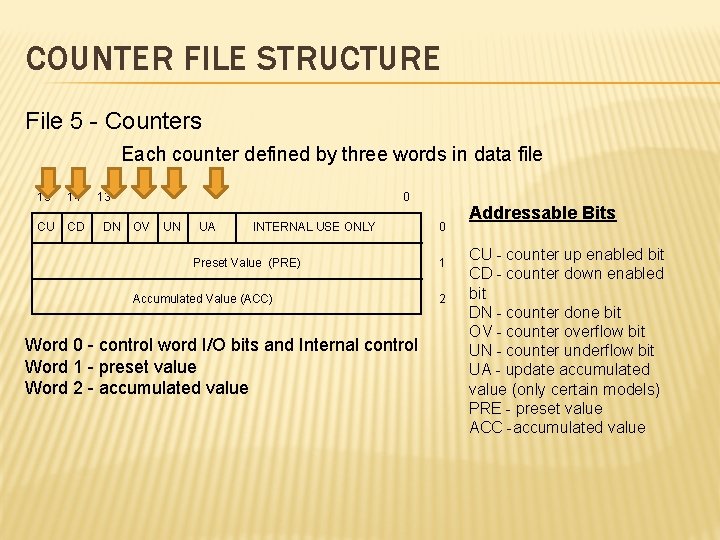

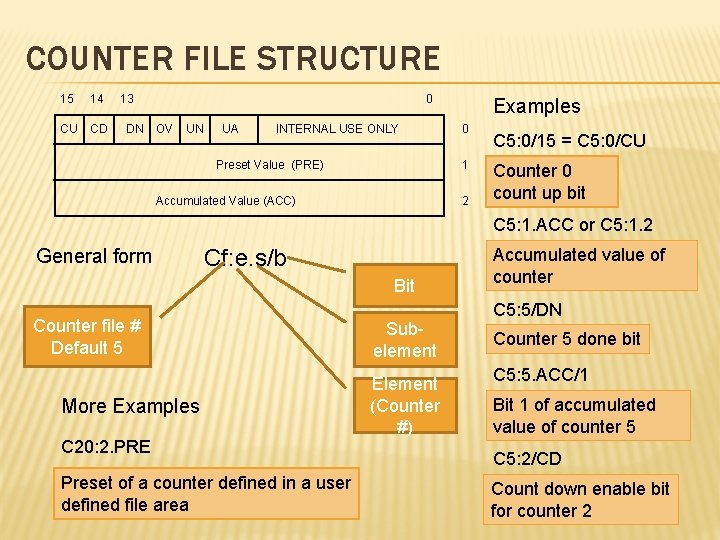

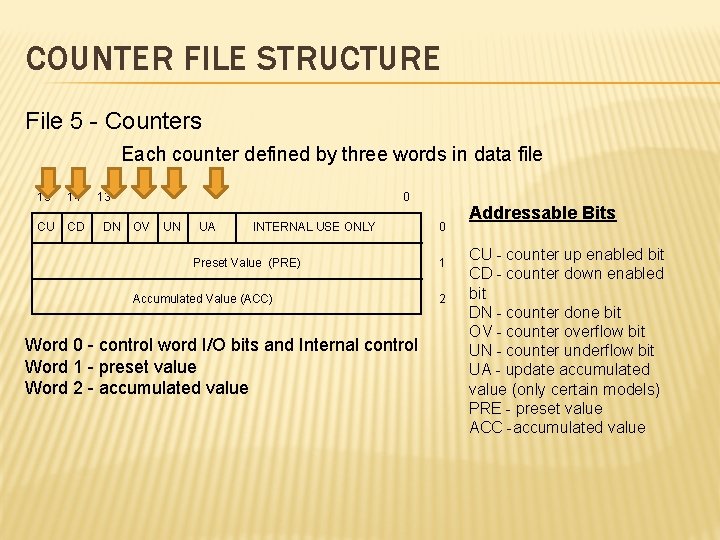

COUNTER FILE STRUCTURE File 5 - Counters Each counter defined by three words in data file 15 14 CU CD 13 DN 0 OV UN UA INTERNAL USE ONLY Preset Value (PRE) Accumulated Value (ACC) Word 0 - control word I/O bits and Internal control Word 1 - preset value Word 2 - accumulated value 0 1 2 Addressable Bits CU - counter up enabled bit CD - counter down enabled bit DN - counter done bit OV - counter overflow bit UN - counter underflow bit UA - update accumulated value (only certain models) PRE - preset value ACC -accumulated value

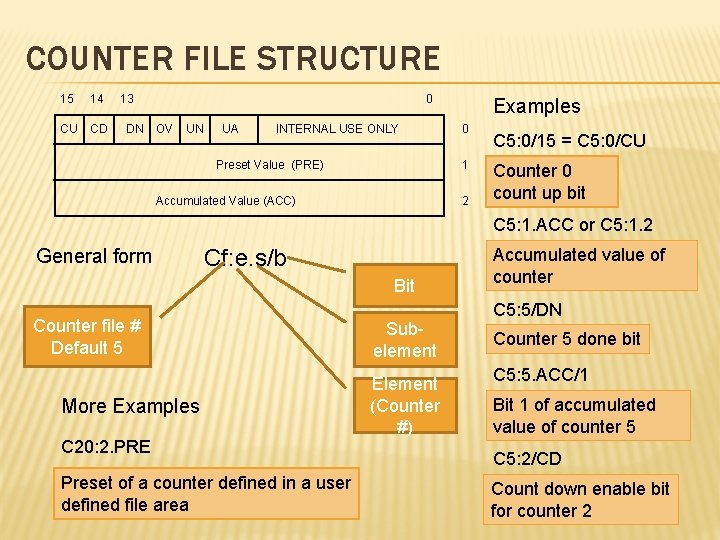

COUNTER FILE STRUCTURE 15 14 CU CD 13 DN 0 OV UN UA INTERNAL USE ONLY Preset Value (PRE) Examples 0 1 Accumulated Value (ACC) 2 C 5: 0/15 = C 5: 0/CU Counter 0 count up bit C 5: 1. ACC or C 5: 1. 2 General form Cf: e. s/b Bit Counter file # Default 5 More Examples C 20: 2. PRE Preset of a counter defined in a user defined file area Subelement Element (Counter #) Accumulated value of counter C 5: 5/DN Counter 5 done bit C 5: 5. ACC/1 Bit 1 of accumulated value of counter 5 C 5: 2/CD Count down enable bit for counter 2

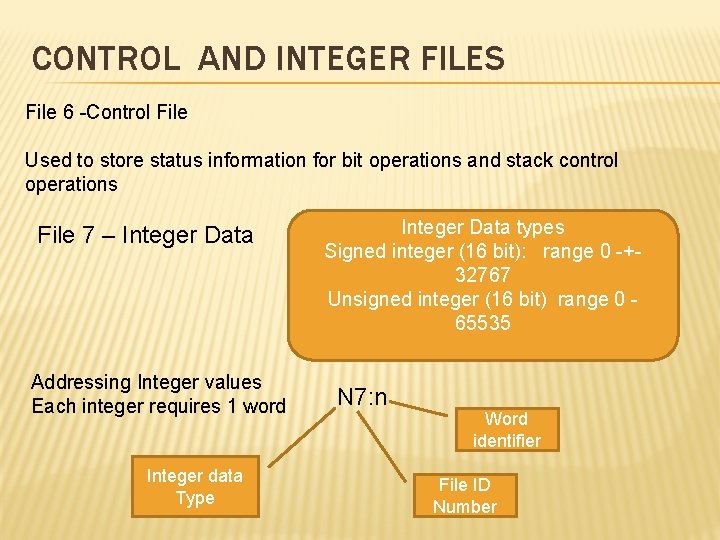

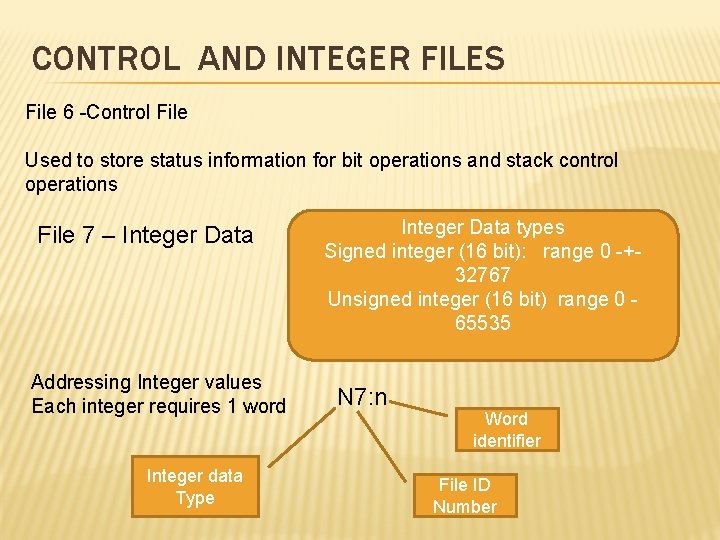

CONTROL AND INTEGER FILES File 6 -Control File Used to store status information for bit operations and stack control operations File 7 – Integer Data Addressing Integer values Each integer requires 1 word Integer data Type Integer Data types Signed integer (16 bit): range 0 -+32767 Unsigned integer (16 bit) range 0 65535 N 7: n Word identifier File ID Number

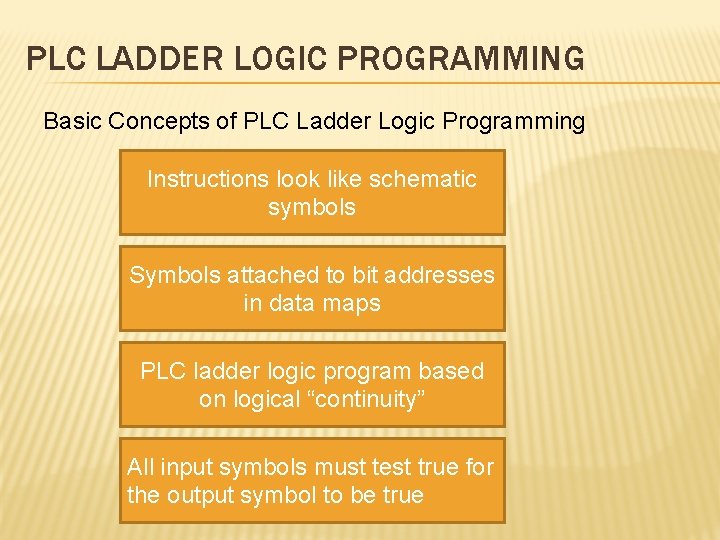

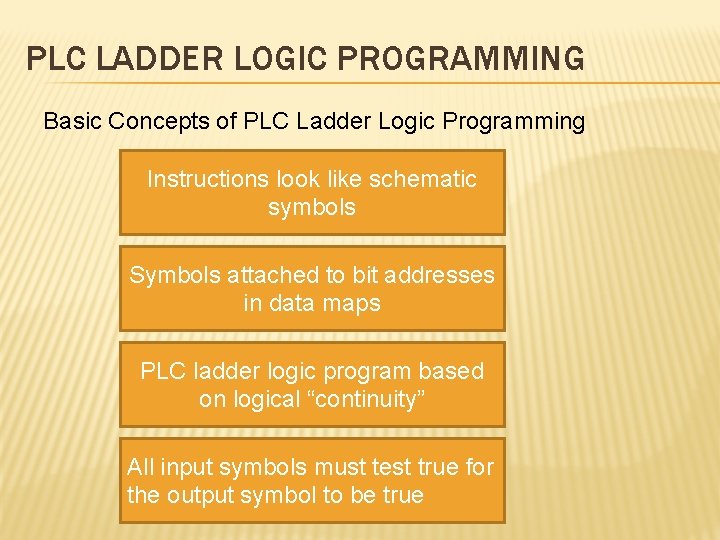

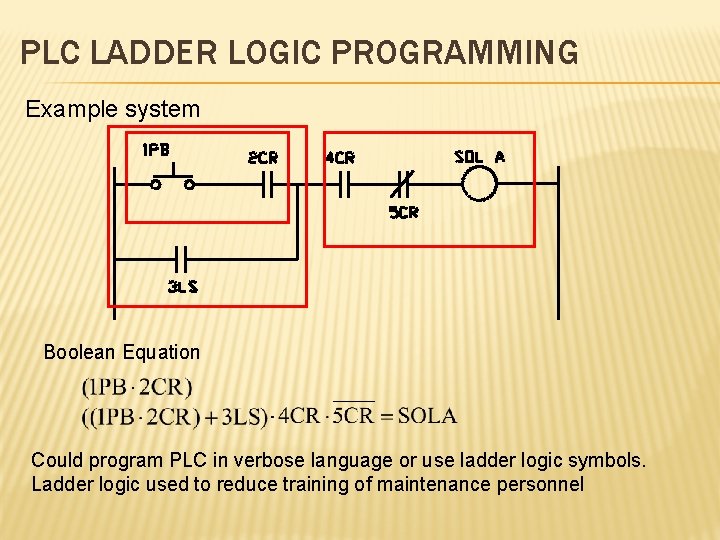

PLC LADDER LOGIC PROGRAMMING Basic Concepts of PLC Ladder Logic Programming Instructions look like schematic symbols Symbols attached to bit addresses in data maps PLC ladder logic program based on logical “continuity” All input symbols must test true for the output symbol to be true

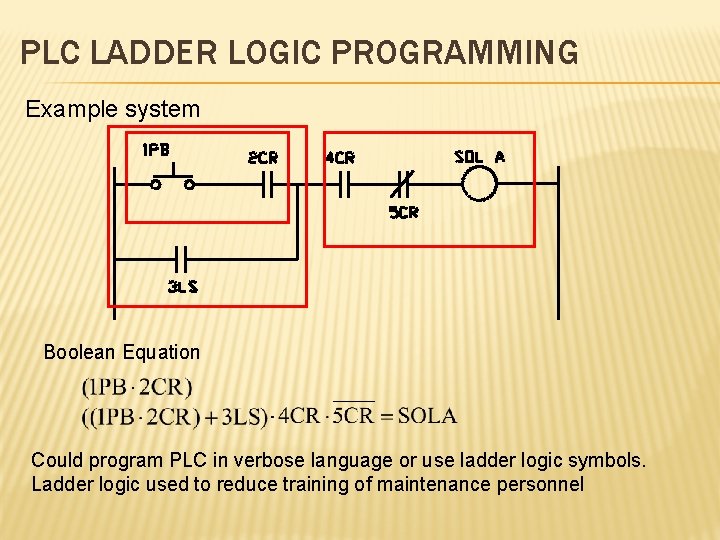

PLC LADDER LOGIC PROGRAMMING Example system Boolean Equation Could program PLC in verbose language or use ladder logic symbols. Ladder logic used to reduce training of maintenance personnel

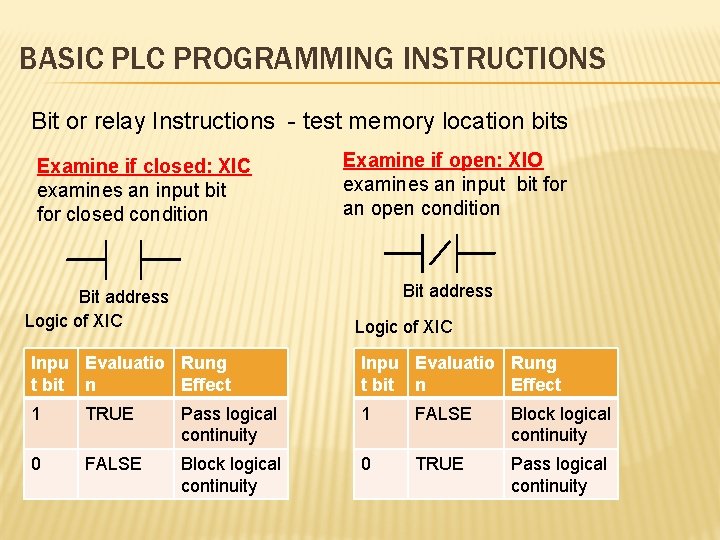

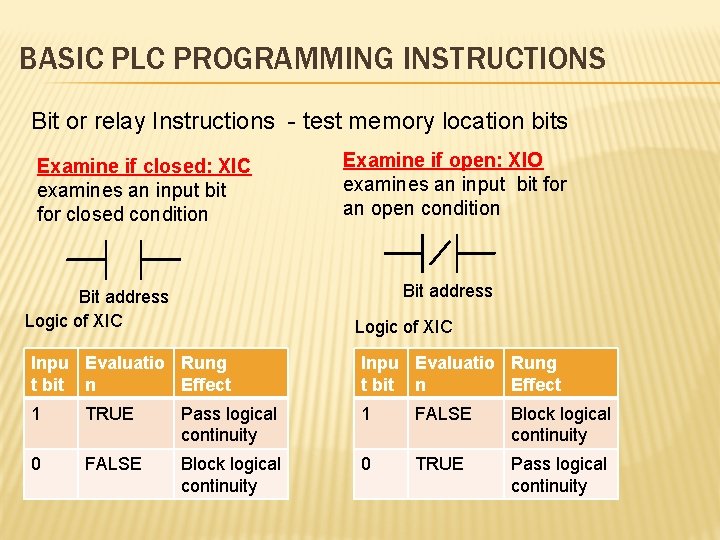

BASIC PLC PROGRAMMING INSTRUCTIONS Bit or relay Instructions - test memory location bits Examine if closed: XIC examines an input bit for closed condition Examine if open: XIO examines an input bit for an open condition Bit address Logic of XIC Inpu Evaluatio Rung t bit n Effect 1 TRUE Pass logical continuity 1 FALSE Block logical continuity 0 TRUE Pass logical continuity

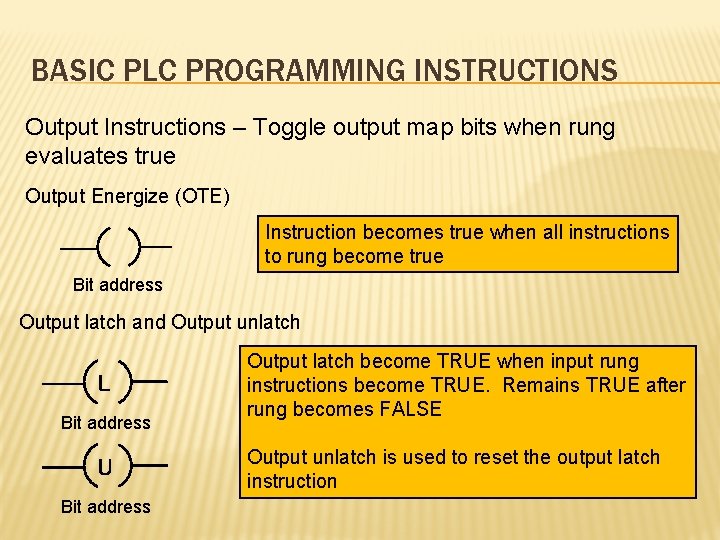

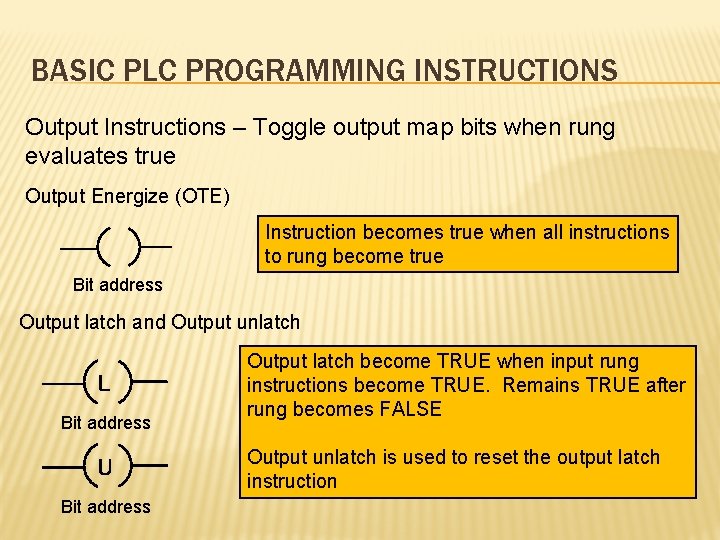

BASIC PLC PROGRAMMING INSTRUCTIONS Output Instructions – Toggle output map bits when rung evaluates true Output Energize (OTE) Instruction becomes true when all instructions to rung become true Bit address Output latch and Output unlatch Bit address Output latch become TRUE when input rung instructions become TRUE. Remains TRUE after rung becomes FALSE Output unlatch is used to reset the output latch instruction Bit address

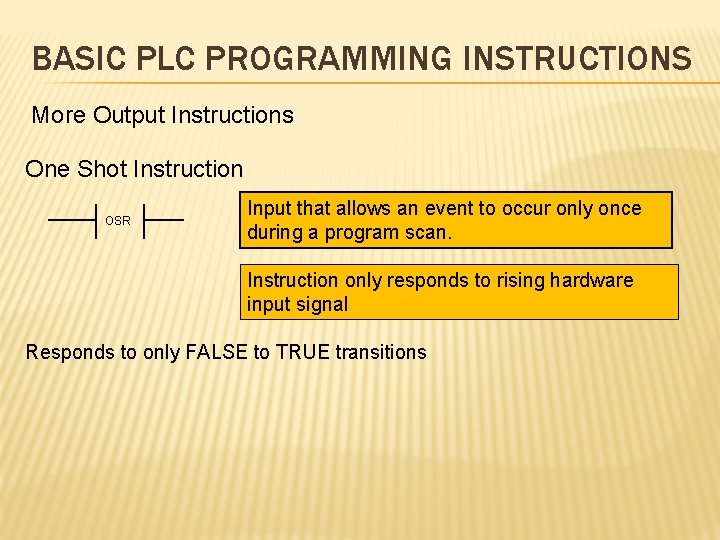

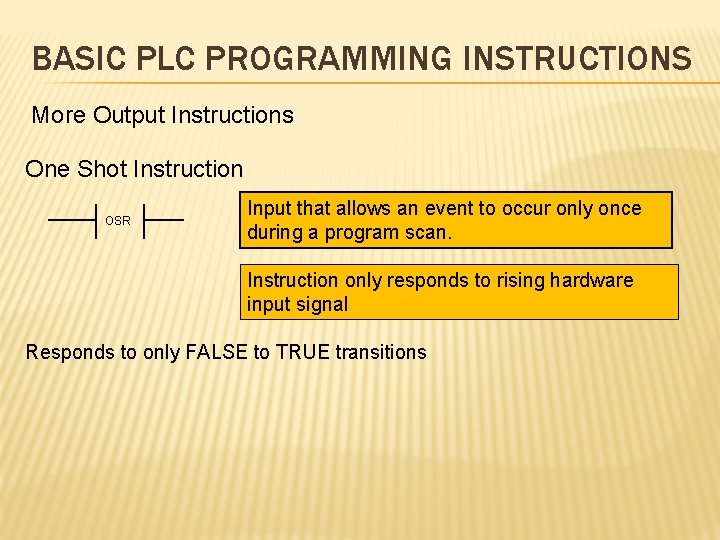

BASIC PLC PROGRAMMING INSTRUCTIONS More Output Instructions One Shot Instruction OSR Input that allows an event to occur only once during a program scan. Instruction only responds to rising hardware input signal Responds to only FALSE to TRUE transitions

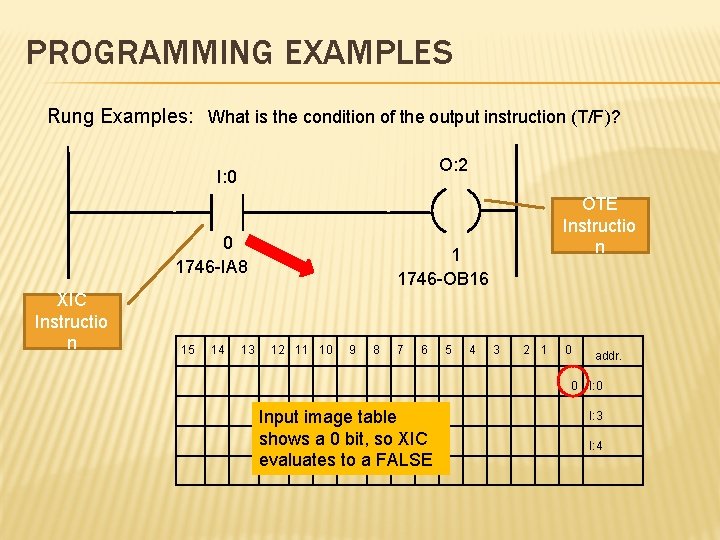

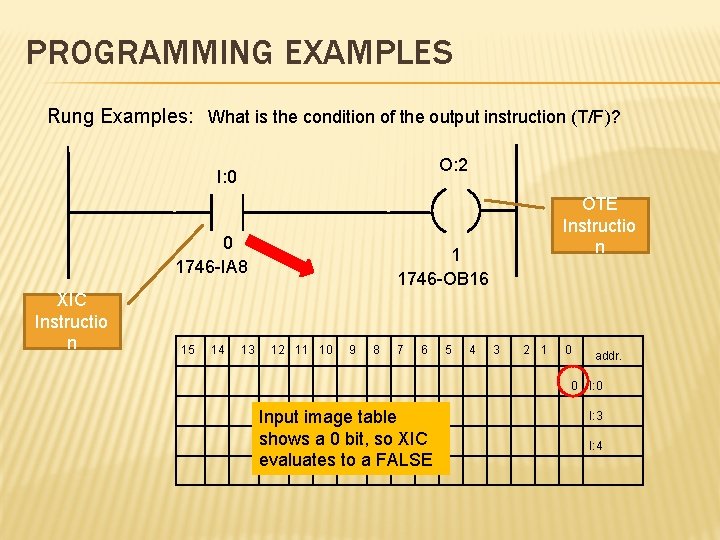

PROGRAMMING EXAMPLES Rung Examples: What is the condition of the output instruction (T/F)? O: 2 I: 0 0 1746 -IA 8 XIC Instructio n 15 14 13 OTE Instructio n 1 1746 -OB 16 12 11 10 9 8 7 6 5 4 3 2 1 0 addr. 0 I: 0 Input image table shows a 0 bit, so XIC evaluates to a FALSE I: 3 I: 4

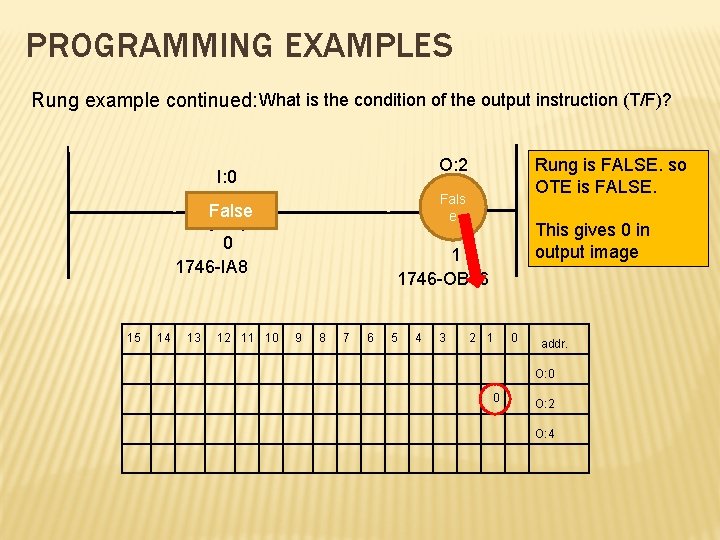

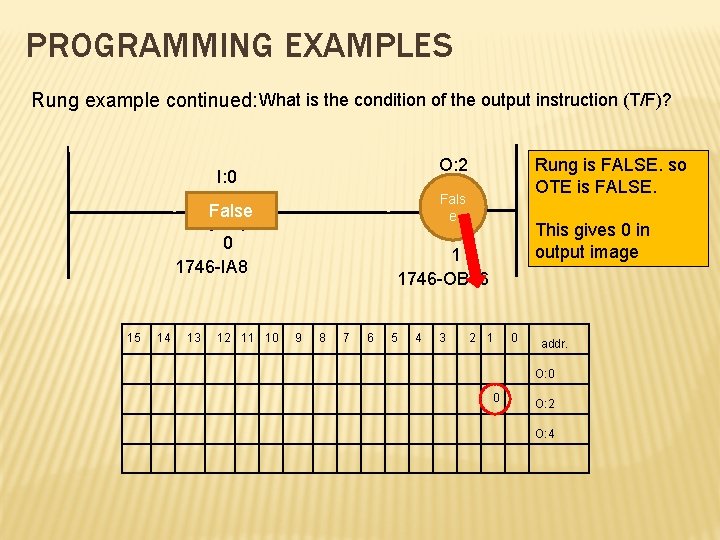

PROGRAMMING EXAMPLES Rung example continued: What is the condition of the output instruction (T/F)? O: 2 I: 0 Fals e False 0 1746 -IA 8 15 14 13 12 11 10 Rung is FALSE. so OTE is FALSE. This gives 0 in output image 1 1746 -OB 16 9 8 7 6 5 4 3 2 1 0 addr. O: 0 0 O: 2 O: 4