SOPC Builder a Design Tool for Rapid System

SOPC Builder: a Design Tool for Rapid System Prototyping on FPGAs Kerry Veenstra Workshop on Architecture Research using FPGA Platforms, 2005 © 2005 Altera Corporation

Altera’s SOPC Builder n Supports Rapid System Prototyping n Performs the Mundane Tasks of System Integration n Allows Focus on the System Architecture n Generates Verilog & VHDL Systems That Run on Model. Sim and FPGAs - Generated Interconnect is Correct by Design © 2005 Altera Corporation

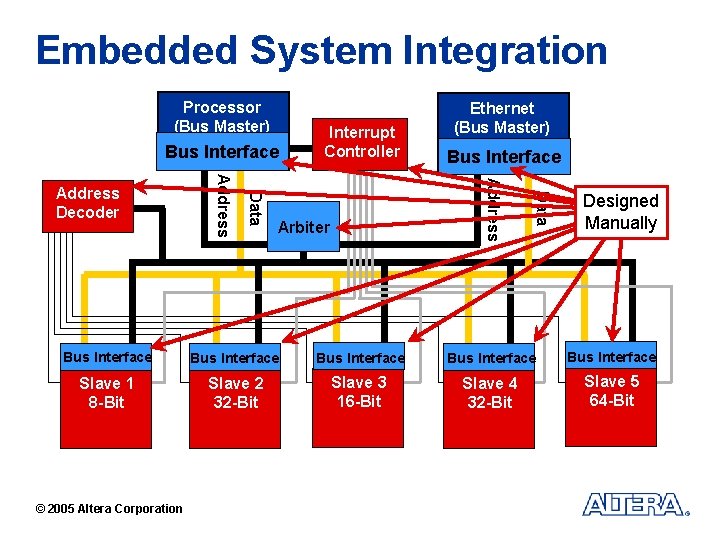

Embedded System Integration Processor (Bus Master) 32 -Bit © 2005 Altera Corporation

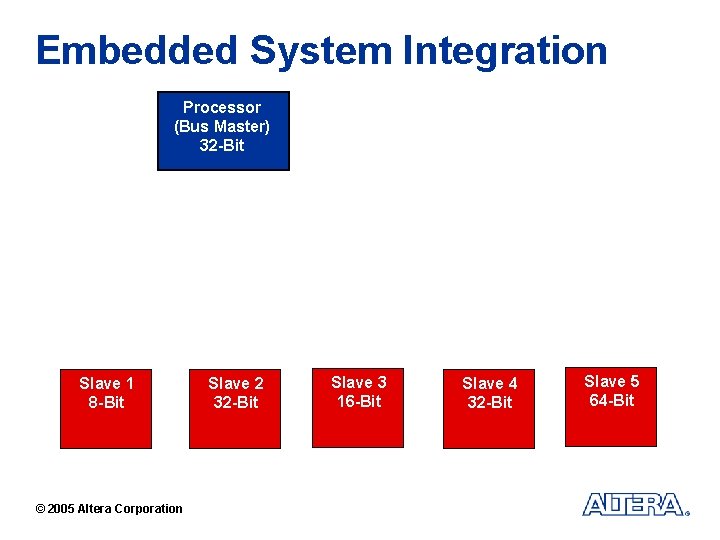

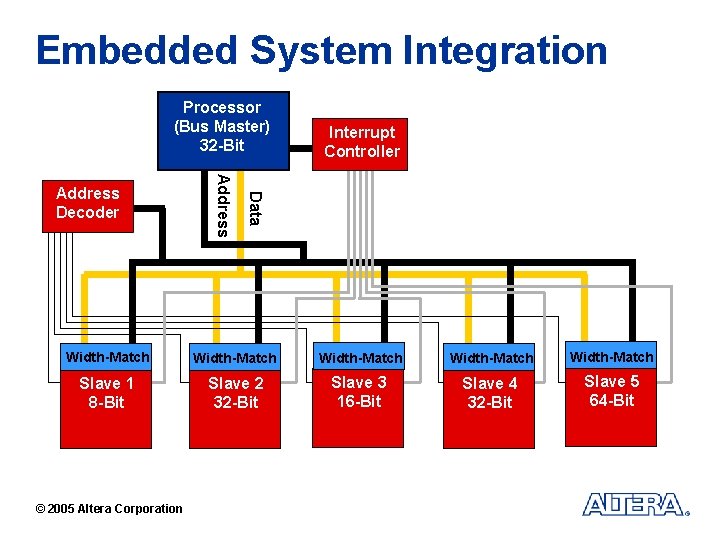

Embedded System Integration Processor (Bus Master) 32 -Bit Slave 1 8 -Bit © 2005 Altera Corporation Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit

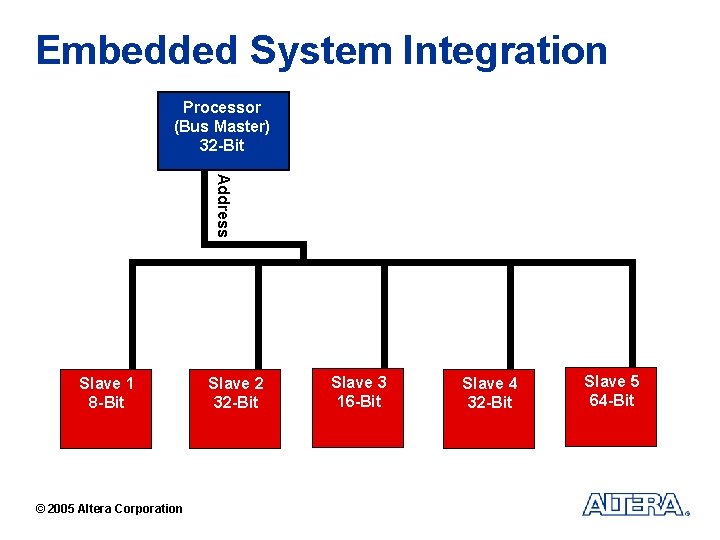

Embedded System Integration Processor (Bus Master) 32 -Bit Address Slave 1 8 -Bit © 2005 Altera Corporation Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit

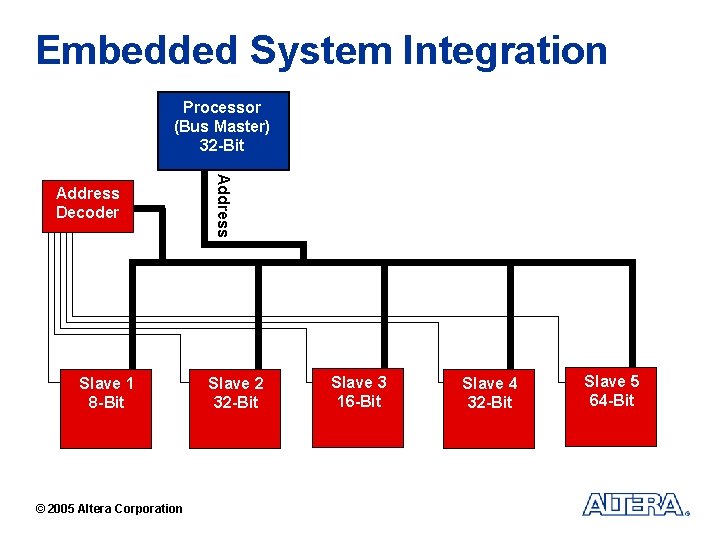

Embedded System Integration Processor (Bus Master) 32 -Bit Slave 1 8 -Bit © 2005 Altera Corporation Address Decoder Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit

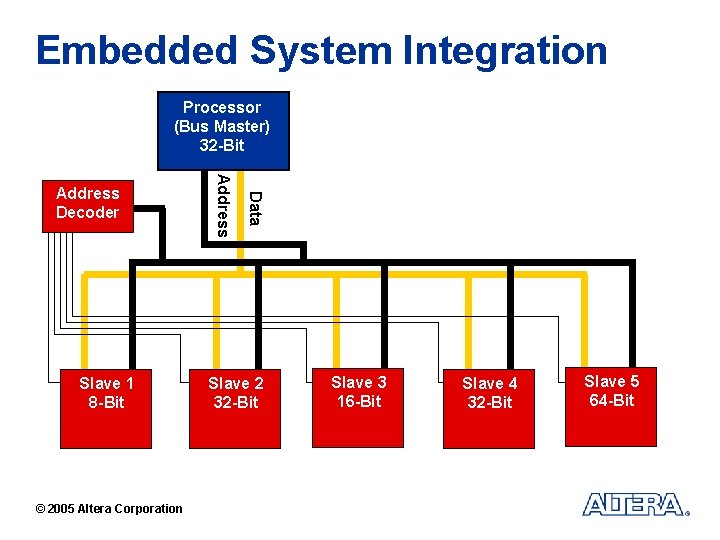

Embedded System Integration Processor (Bus Master) 32 -Bit © 2005 Altera Corporation Data Slave 1 8 -Bit Address Decoder Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit

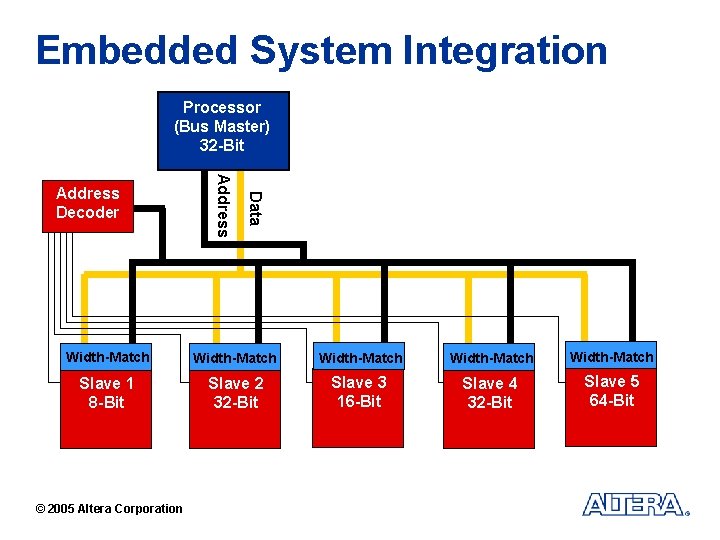

Embedded System Integration Processor (Bus Master) 32 -Bit Data Address Decoder Width-Match Width-Match Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

Embedded System Integration Processor (Bus Master) 32 -Bit Data Address Decoder Interrupt Controller Width-Match Width-Match Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

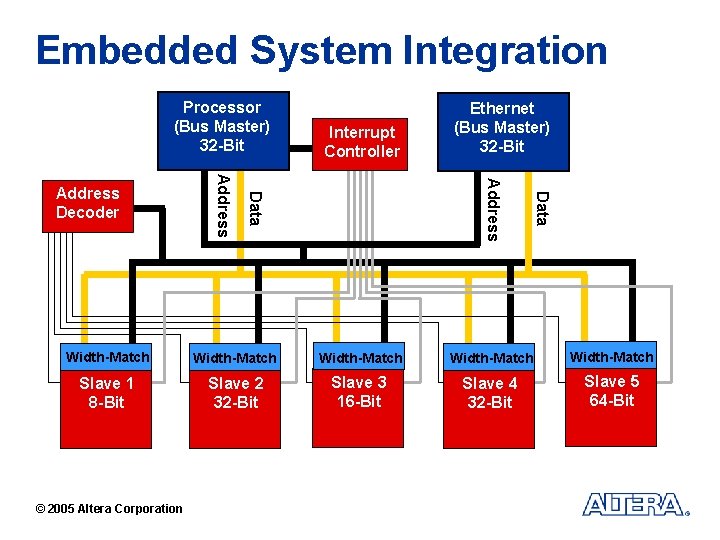

Embedded System Integration Processor (Bus Master) 32 -Bit Data Address Decoder Interrupt Controller Ethernet (Bus Master) 32 -Bit Width-Match Width-Match Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

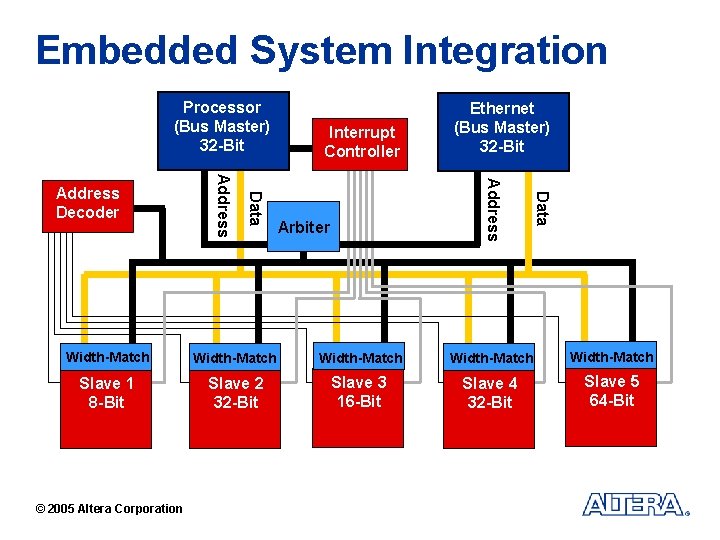

Embedded System Integration Processor (Bus Master) 32 -Bit Arbiter Data Address Decoder Interrupt Controller Ethernet (Bus Master) 32 -Bit Width-Match Width-Match Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

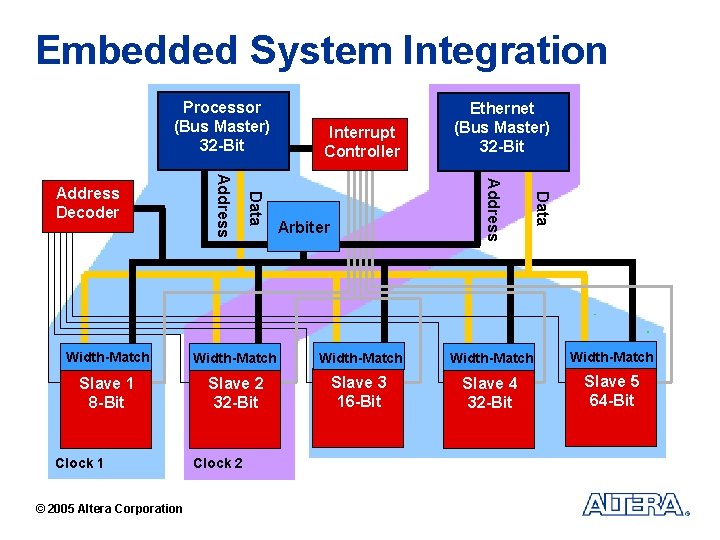

Embedded System Integration Processor (Bus Master) 32 -Bit Arbiter Data Address Decoder Interrupt Controller Ethernet (Bus Master) 32 -Bit Width-Match Width-Match Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit Clock 1 © 2005 Altera Corporation Clock 2

Embedded System Integration Processor (Bus Master) Bus 32 -Bit Interface Bus Interface Arbiter Data Address Decoder Interrupt Controller Ethernet (Bus Master) 32 -Bit Designed Manually Bus Interface Bus Interface Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

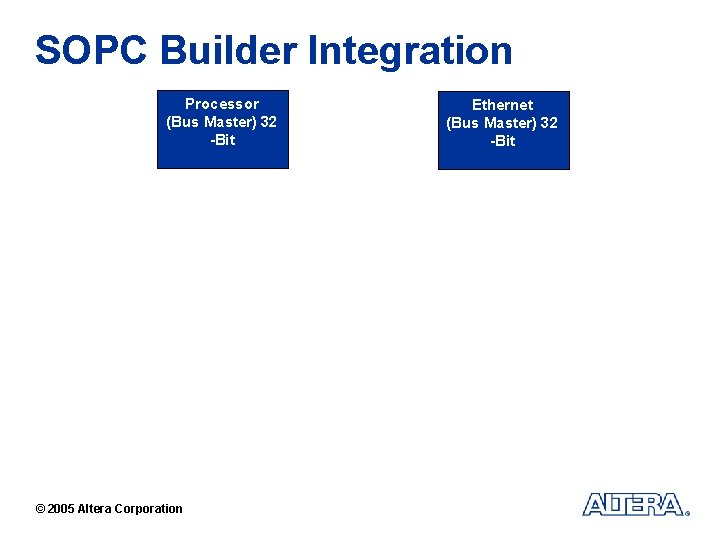

SOPC Builder Integration Processor (Bus Master) 32 -Bit © 2005 Altera Corporation Ethernet (Bus Master) 32 -Bit

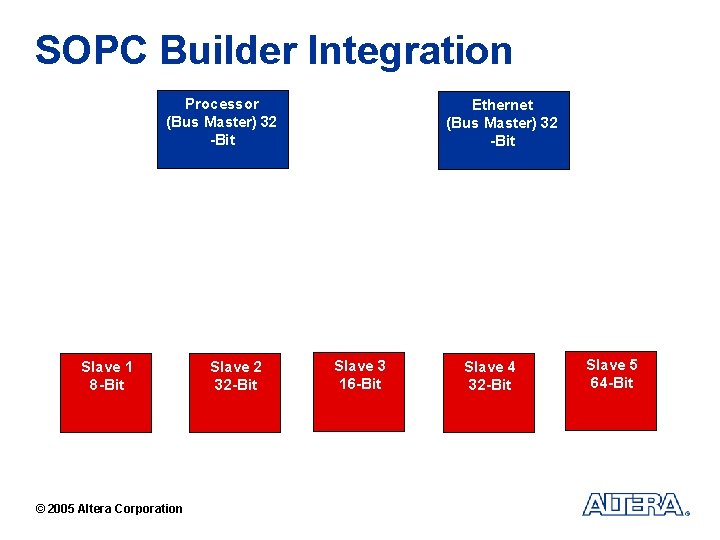

SOPC Builder Integration Processor (Bus Master) 32 -Bit Slave 1 8 -Bit © 2005 Altera Corporation Slave 2 32 -Bit Ethernet (Bus Master) 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit

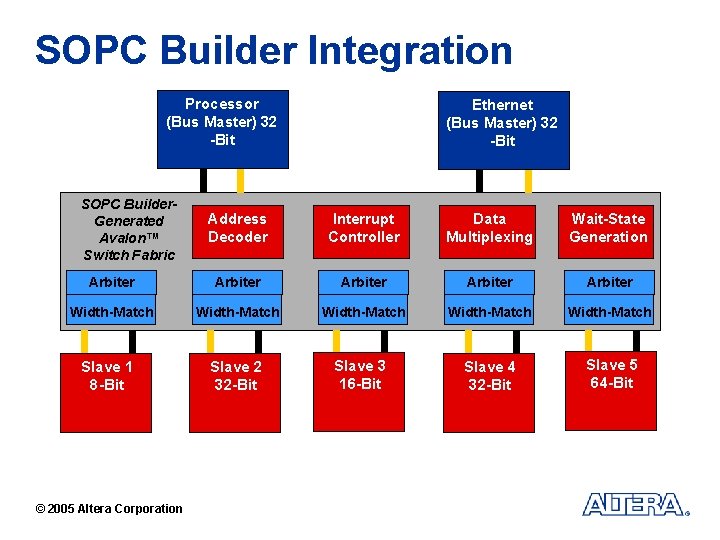

SOPC Builder Integration Processor (Bus Master) 32 -Bit SOPC Builder. Generated Avalon™ Switch Fabric Ethernet (Bus Master) 32 -Bit Address Decoder Interrupt Controller Data Multiplexing Wait-State Generation Arbiter Arbiter Width-Match Width-Match Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit Slave 1 8 -Bit © 2005 Altera Corporation

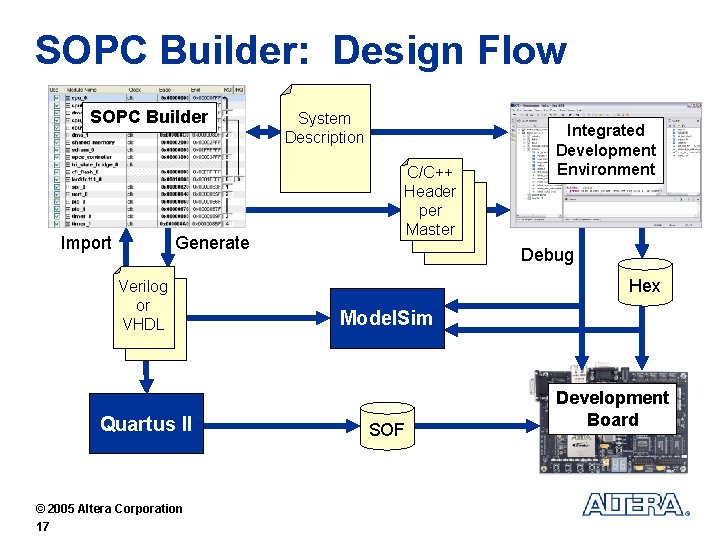

SOPC Builder: Design Flow SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 17 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

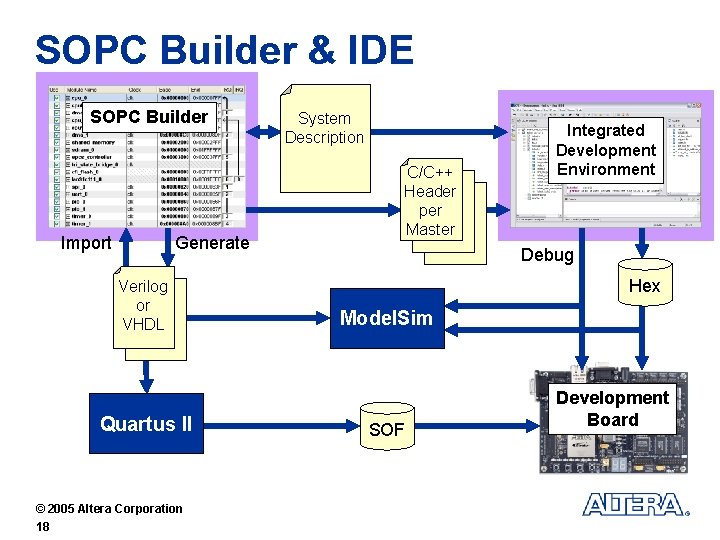

SOPC Builder & IDE SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 18 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

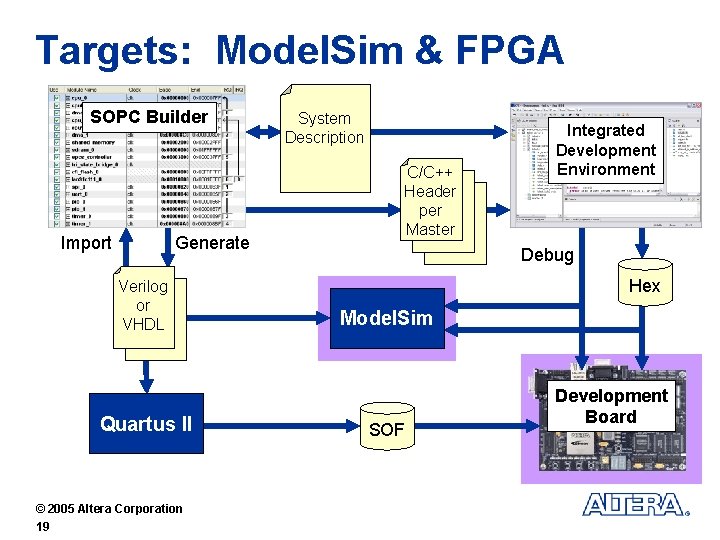

Targets: Model. Sim & FPGA SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 19 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

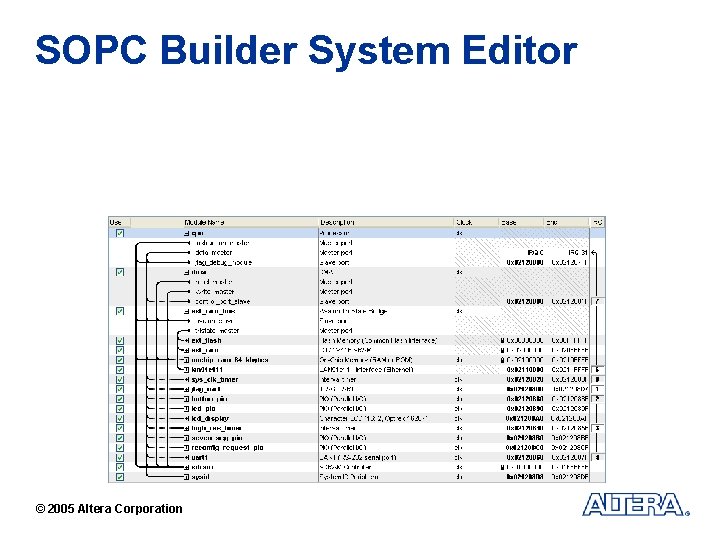

SOPC Builder System Editor SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 20 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

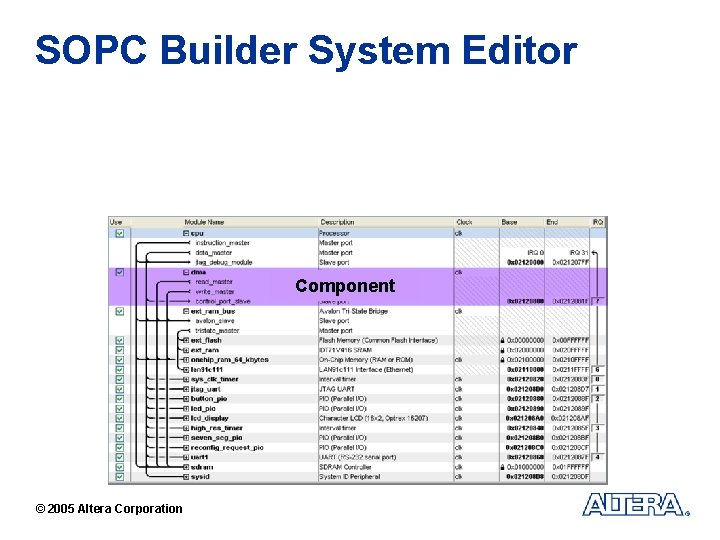

SOPC Builder System Editor © 2005 Altera Corporation

SOPC Builder System Editor Component © 2005 Altera Corporation

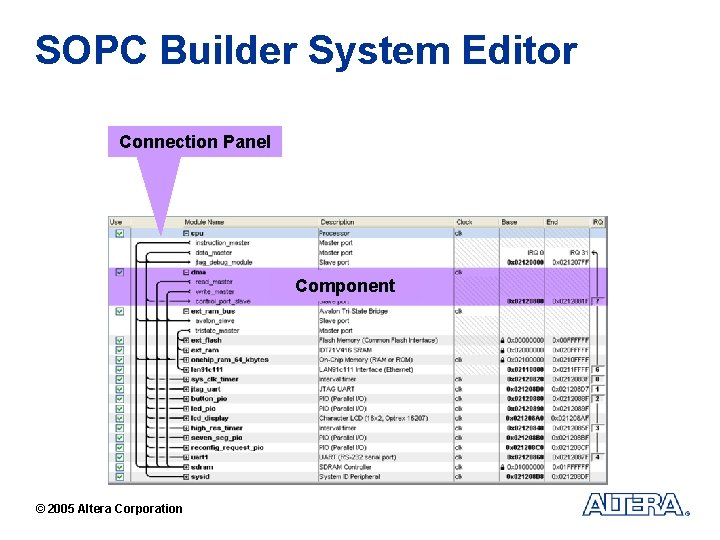

SOPC Builder System Editor Connection Panel Component © 2005 Altera Corporation

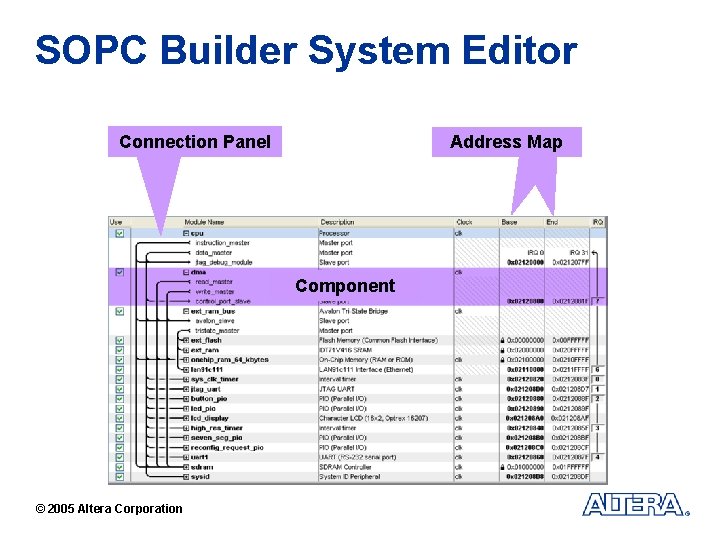

SOPC Builder System Editor Connection Panel Address Map Component © 2005 Altera Corporation

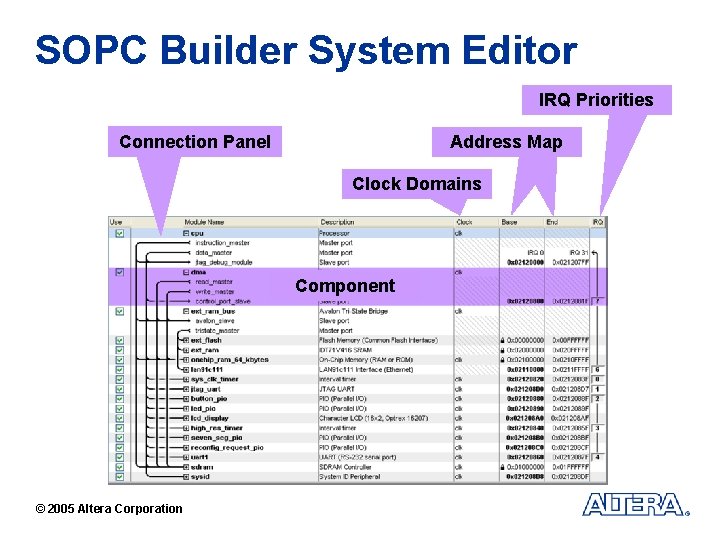

SOPC Builder System Editor IRQ Priorities Connection Panel Address Map Clock Domains Component © 2005 Altera Corporation

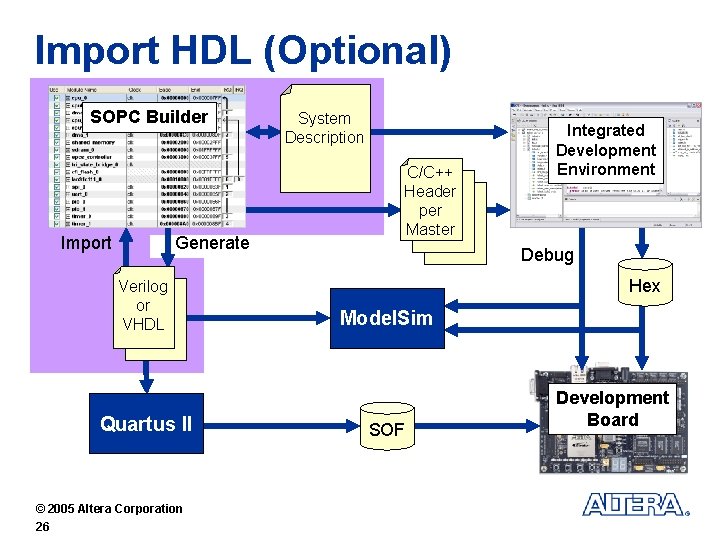

Import HDL (Optional) SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 26 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

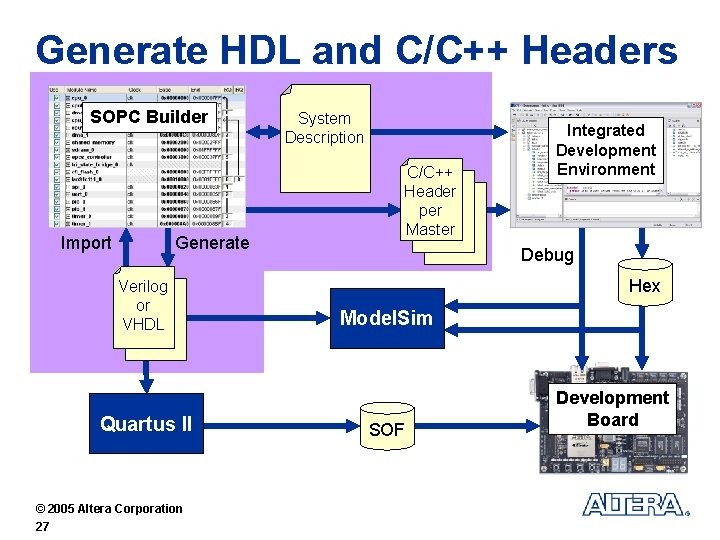

Generate HDL and C/C++ Headers SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 27 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

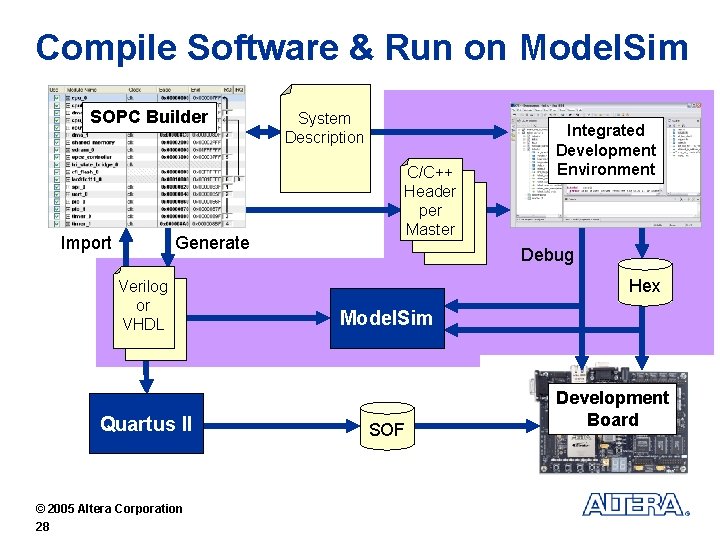

Compile Software & Run on Model. Sim SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 28 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

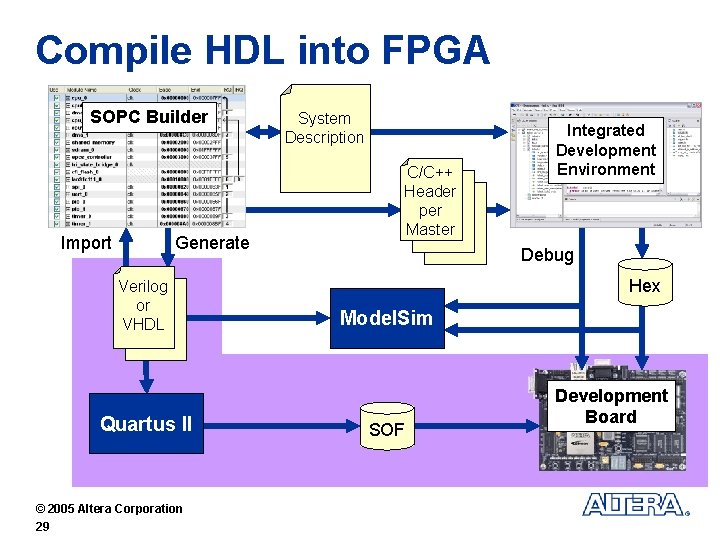

Compile HDL into FPGA SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 29 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

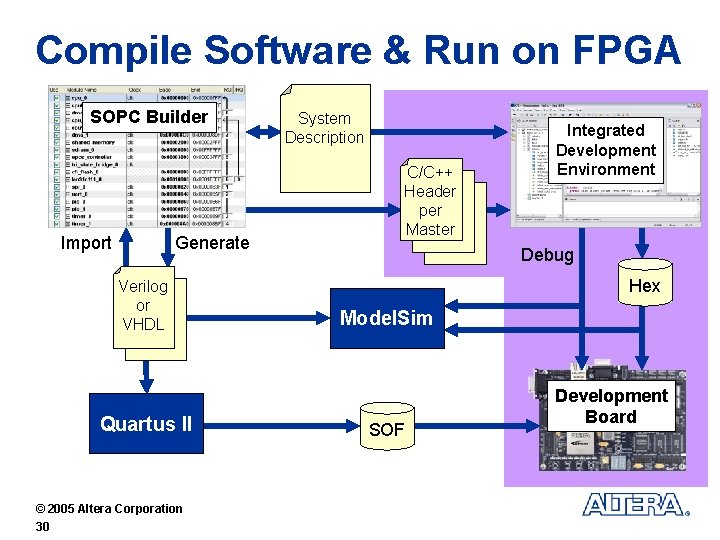

Compile Software & Run on FPGA SOPC Builder Import Generate Verilog or VHDL Quartus II © 2005 Altera Corporation 30 System Description C/C++ Header per Master Integrated Development Environment Debug Hex Model. Sim SOF Development Board

Component Interface © 2005 Altera Corporation

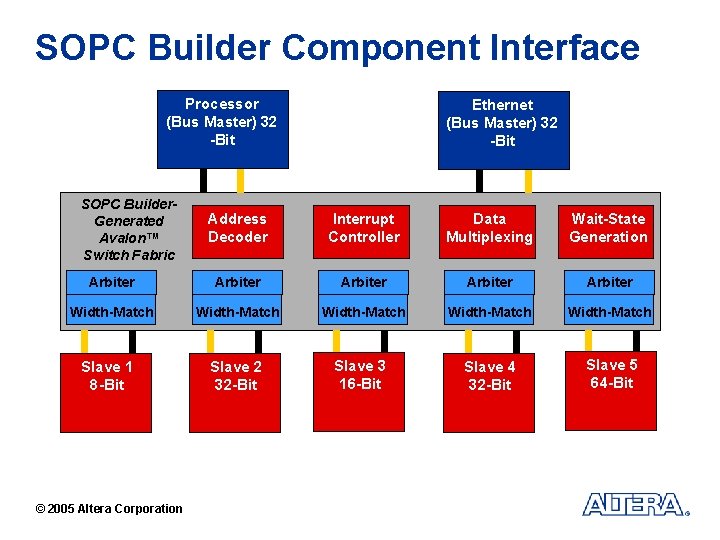

SOPC Builder Component Interface Processor (Bus Master) 32 -Bit SOPC Builder. Generated Avalon™ Switch Fabric Ethernet (Bus Master) 32 -Bit Address Decoder Interrupt Controller Data Multiplexing Wait-State Generation Arbiter Arbiter Width-Match Width-Match Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit Slave 1 8 -Bit © 2005 Altera Corporation

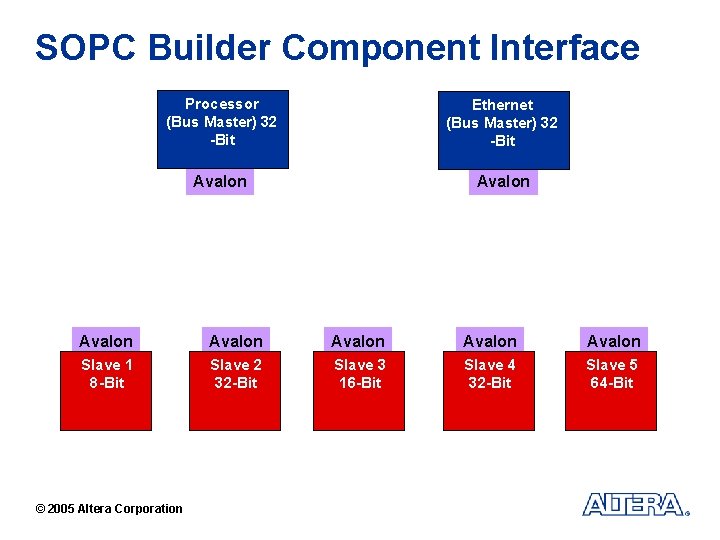

SOPC Builder Component Interface Processor (Bus Master) 32 -Bit Ethernet (Bus Master) 32 -Bit Avalon Avalon Slave 1 8 -Bit Slave 2 32 -Bit Slave 3 16 -Bit Slave 4 32 -Bit Slave 5 64 -Bit © 2005 Altera Corporation

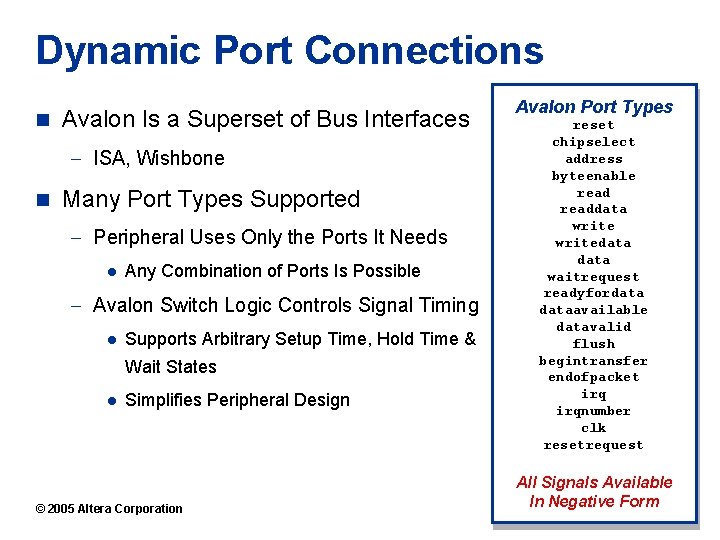

Dynamic Port Connections n Avalon Is a Superset of Bus Interfaces - ISA, Wishbone n Many Port Types Supported - Peripheral Uses Only the Ports It Needs l Any Combination of Ports Is Possible - Avalon Switch Logic Controls Signal Timing l Supports Arbitrary Setup Time, Hold Time & Wait States l Simplifies Peripheral Design © 2005 Altera Corporation Avalon Port Types reset chipselect address byteenable readdata writedata waitrequest readyfordataavailable datavalid flush begintransfer endofpacket irqnumber clk resetrequest All Signals Available In Negative Form

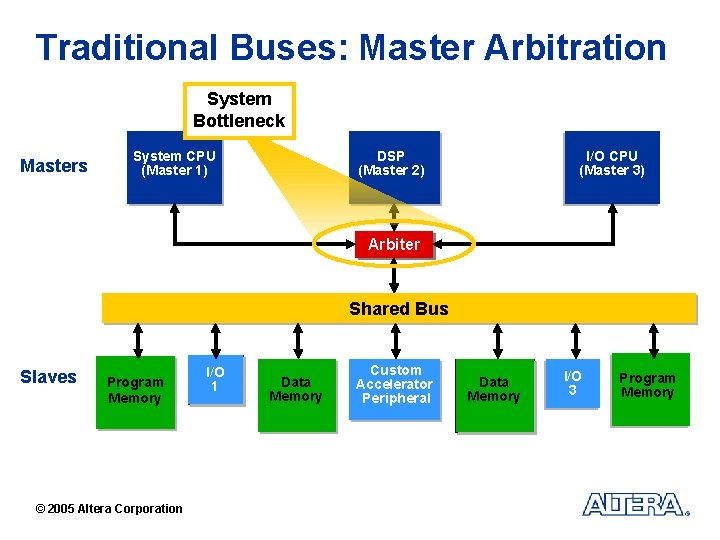

Traditional Buses: Master Arbitration System Bottleneck Masters DSP (Master 2) System CPU (Master 1) I/O CPU (Master 3) Arbiter Shared Bus Slaves Program Memory © 2005 Altera Corporation I/O 1 Data Memory Custom Accelerator Peripheral Data Memory I/O 3 Program Memory

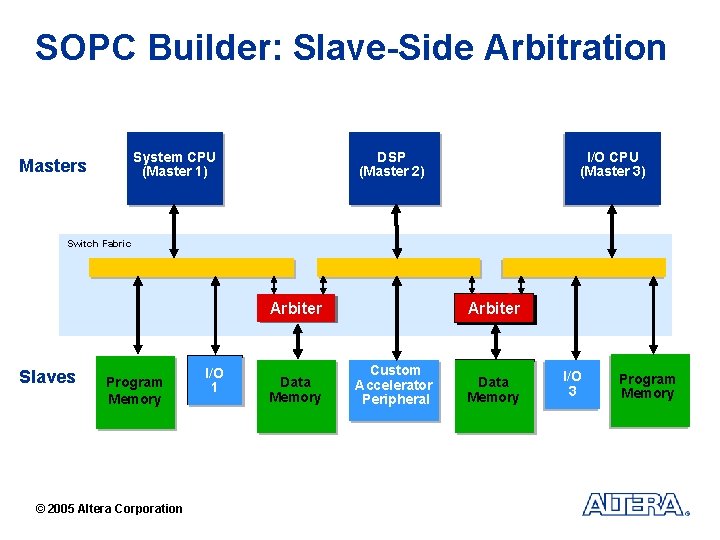

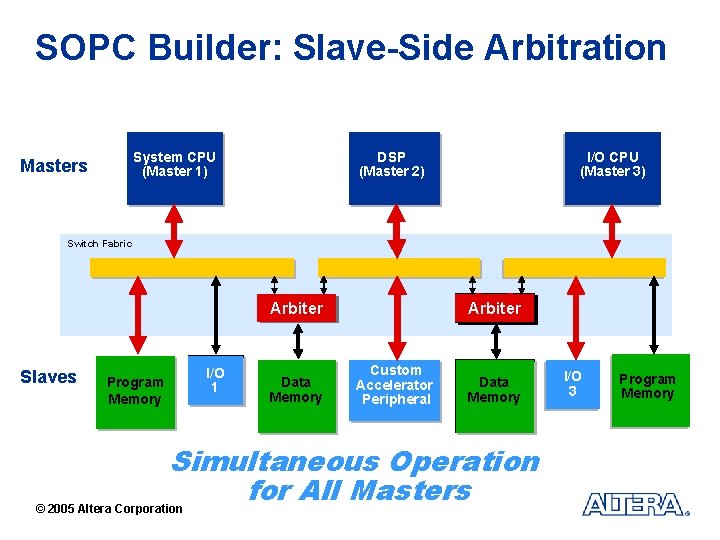

SOPC Builder: Slave-Side Arbitration DSP (Master 2) System CPU (Master 1) Masters I/O CPU (Master 3) Switch Fabric Arbiter Slaves Program Memory © 2005 Altera Corporation I/O 1 Data Memory Aribiter Arbiter Custom Accelerator Peripheral Data Memory I/O 3 Program Memory

SOPC Builder: Slave-Side Arbitration DSP (Master 2) System CPU (Master 1) Masters I/O CPU (Master 3) Switch Fabric Arbiter Slaves Program Memory I/O 1 Data Memory Aribiter Arbiter Custom Accelerator Peripheral Data Memory Simultaneous Operation for All Masters © 2005 Altera Corporation I/O 3 Program Memory

Altera’s SOPC Builder n Supports Rapid System Prototyping n Performs the Mundane Tasks of System Integration n Allows Focus on the System Architecture n Generates Verilog & VHDL Systems That Run on Model. Sim and FPGAs - Generated Interconnect is Correct by Design © 2005 Altera Corporation

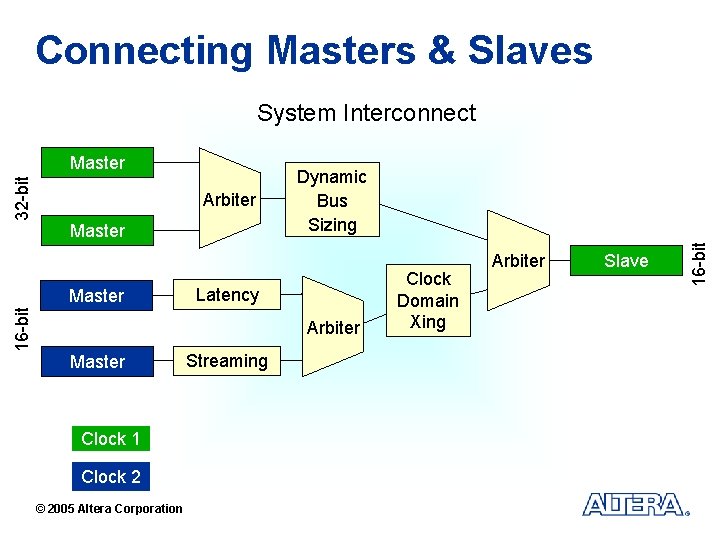

Connecting Masters & Slaves System Interconnect Arbiter Master 16 -bit Master Dynamic Bus Sizing Latency Arbiter Master Clock 1 Clock 2 © 2005 Altera Corporation Streaming Clock Domain Xing Arbiter Slave 16 -bit 32 -bit Master

- Slides: 39