Some thoughts on ART 2 GBT ASIC Sorin

Some thoughts on “ART 2 GBT” ASIC Sorin Martoiu, IFIN-HH

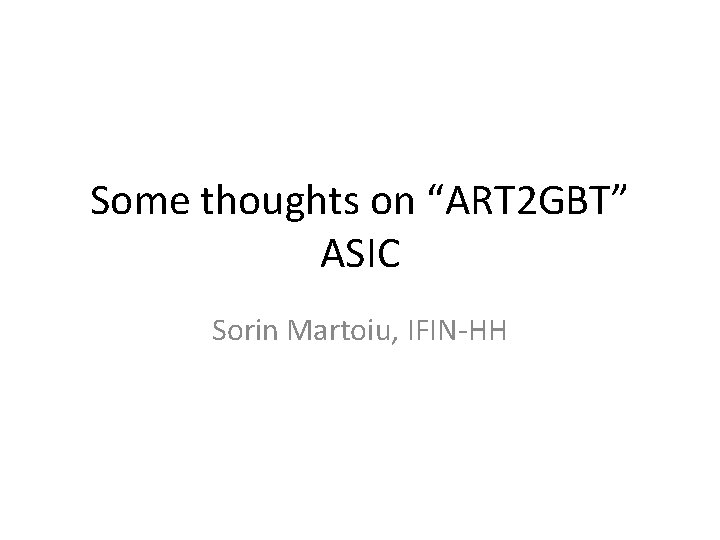

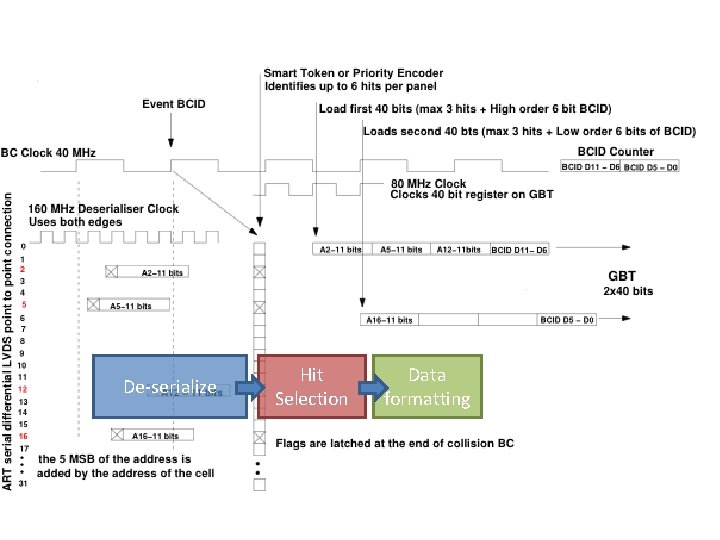

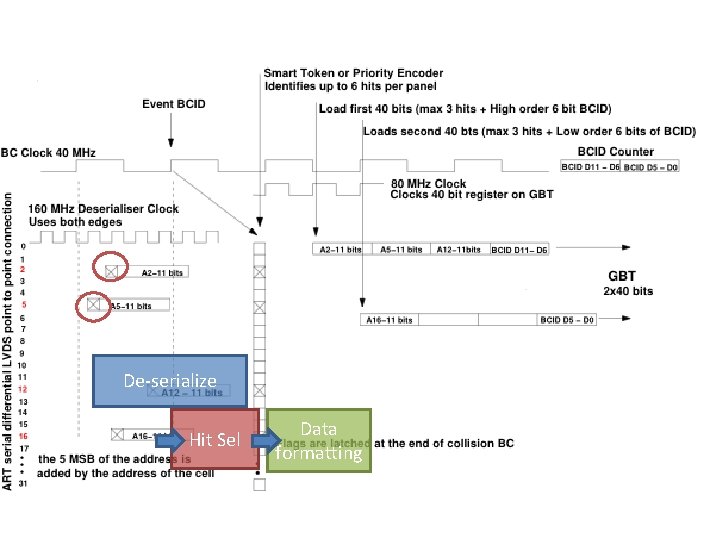

De-serialize Hit Selection Data formatting

De-serialize Hit Sel Data formatting

De-serialize Hit Sel Data formatting

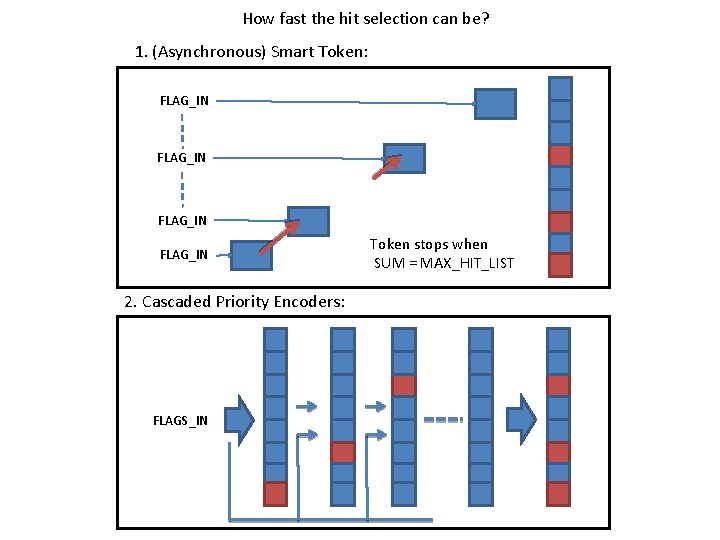

How fast the hit selection can be? 1. (Asynchronous) Smart Token: FLAG_IN 2. Cascaded Priority Encoders: FLAGS_IN Token stops when SUM = MAX_HIT_LIST

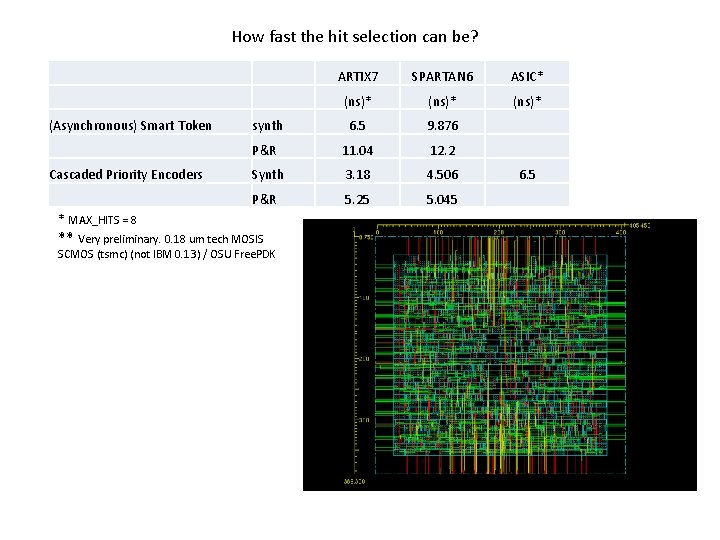

How fast the hit selection can be? (Asynchronous) Smart Token Cascaded Priority Encoders ARTIX 7 SPARTAN 6 ASIC* (ns)* synth 6. 5 9. 876 P&R 11. 04 12. 2 Synth 3. 18 4. 506 P&R 5. 25 5. 045 * MAX_HITS = 8 ** Very preliminary. 0. 18 um tech MOSIS SCMOS (tsmc) (not IBM 0. 13) / OSU Free. PDK 6. 5

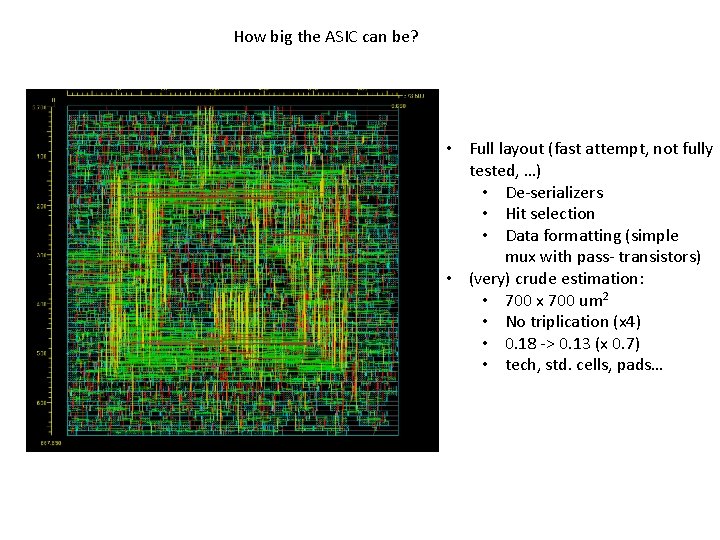

How big the ASIC can be? • Full layout (fast attempt, not fully tested, …) • De-serializers • Hit selection • Data formatting (simple mux with pass- transistors) • (very) crude estimation: • 700 x 700 um 2 • No triplication (x 4) • 0. 18 -> 0. 13 (x 0. 7) • tech, std. cells, pads…

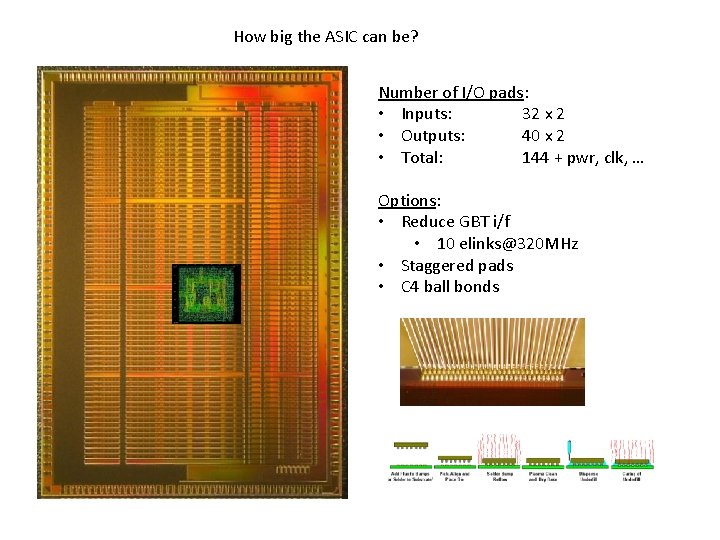

How big the ASIC can be? Number of I/O pads: • Inputs: 32 x 2 • Outputs: 40 x 2 • Total: 144 + pwr, clk, … Options: • Reduce GBT i/f • 10 elinks@320 MHz • Staggered pads • C 4 ball bonds

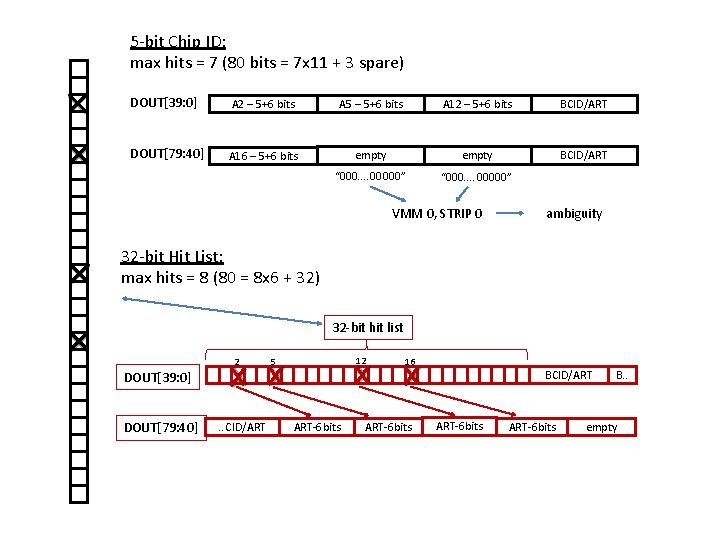

5 -bit Chip ID: max hits = 7 (80 bits = 7 x 11 + 3 spare) DOUT[39: 0] A 2 – 5+6 bits A 5 – 5+6 bits A 12 – 5+6 bits BCID/ART DOUT[79: 40] A 16 – 5+6 bits empty BCID/ART “ 000. . . . 00000” VMM 0, STRIP 0 ambiguity 32 -bit Hit List: max hits = 8 (80 = 8 x 6 + 32) 32 -bit hit list 2 12 5 16 BCID/ART DOUT[39: 0] DOUT[79: 40] . . CID/ART ART-6 bits B. . empty

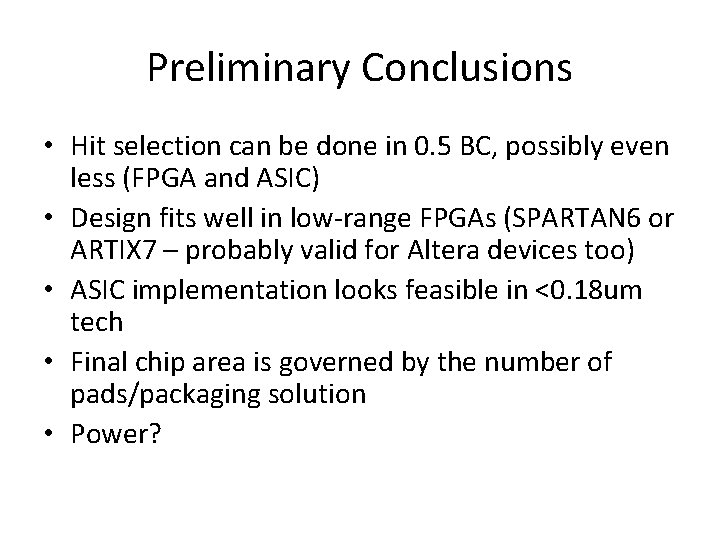

Preliminary Conclusions • Hit selection can be done in 0. 5 BC, possibly even less (FPGA and ASIC) • Design fits well in low-range FPGAs (SPARTAN 6 or ARTIX 7 – probably valid for Altera devices too) • ASIC implementation looks feasible in <0. 18 um tech • Final chip area is governed by the number of pads/packaging solution • Power?

Spare Slides

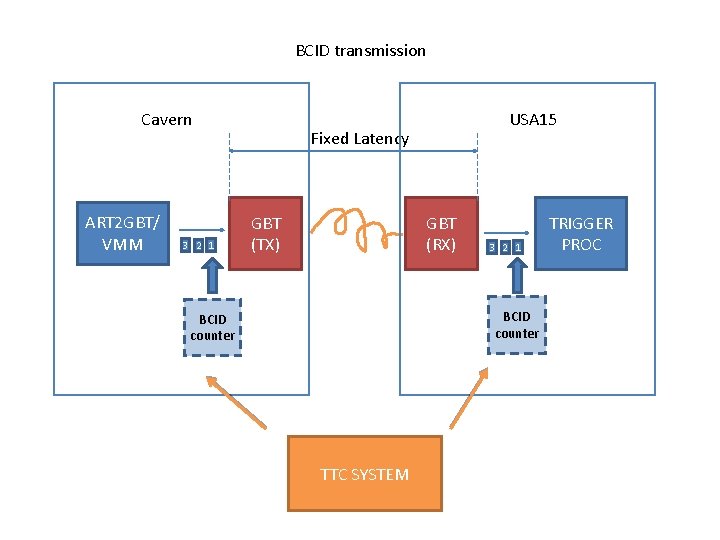

BCID transmission Cavern ART 2 GBT/ VMM 3 2 1 USA 15 Fixed Latency GBT (TX) GBT (RX) 3 2 1 BCID counter TTC SYSTEM TRIGGER PROC

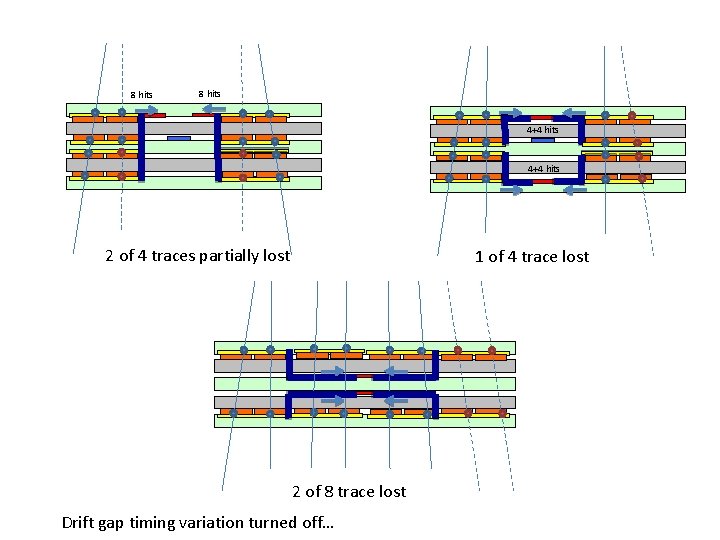

8 hits 4+4 hits 2 of 4 traces partially lost 1 of 4 trace lost 2 of 8 trace lost Drift gap timing variation turned off…

- Slides: 13