Solid State PSD related Short Activity Overview Dr

![Areas of Expertise • Digitizers w/wo DAC [100 MSPS 16 -bit] to [ 5 Areas of Expertise • Digitizers w/wo DAC [100 MSPS 16 -bit] to [ 5](https://slidetodoc.com/presentation_image/764d79878a458b995c9b713eb20d25c0/image-3.jpg)

- Slides: 15

Solid State PSD related Short Activity Overview Dr. hias Matt ch Kirs

We develop and manufacture board level electronics • VME • µTCA/MTCA. 4 • PCI/PCI Express • Custom

![Areas of Expertise Digitizers wwo DAC 100 MSPS 16 bit to 5 Areas of Expertise • Digitizers w/wo DAC [100 MSPS 16 -bit] to [ 5](https://slidetodoc.com/presentation_image/764d79878a458b995c9b713eb20d25c0/image-3.jpg)

Areas of Expertise • Digitizers w/wo DAC [100 MSPS 16 -bit] to [ 5 GSPS 10 -bit] • Interfaces • Mixed • Xilinx FPGA based

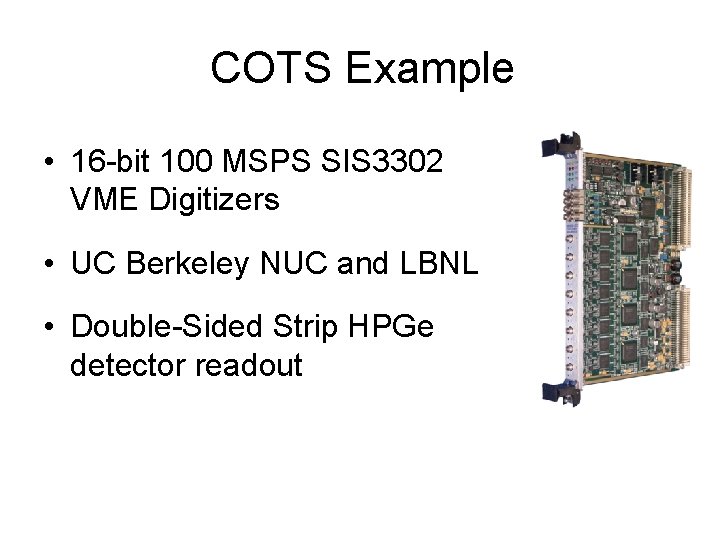

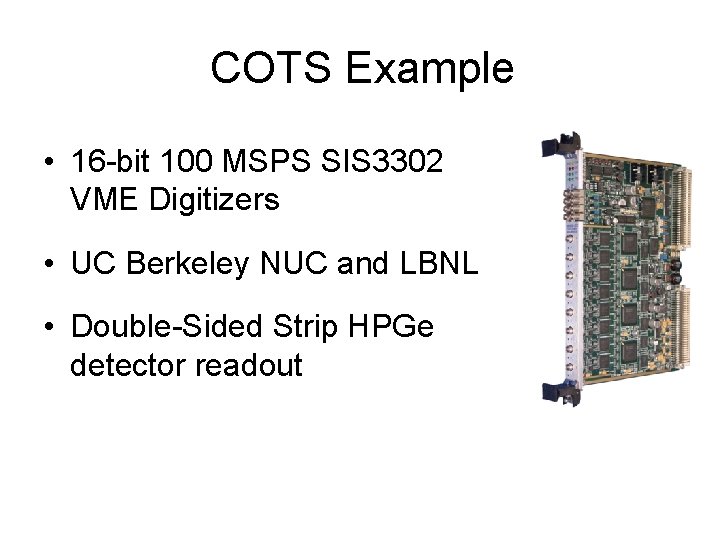

COTS Example • 16 -bit 100 MSPS SIS 3302 VME Digitizers • UC Berkeley NUC and LBNL • Double-Sided Strip HPGe detector readout

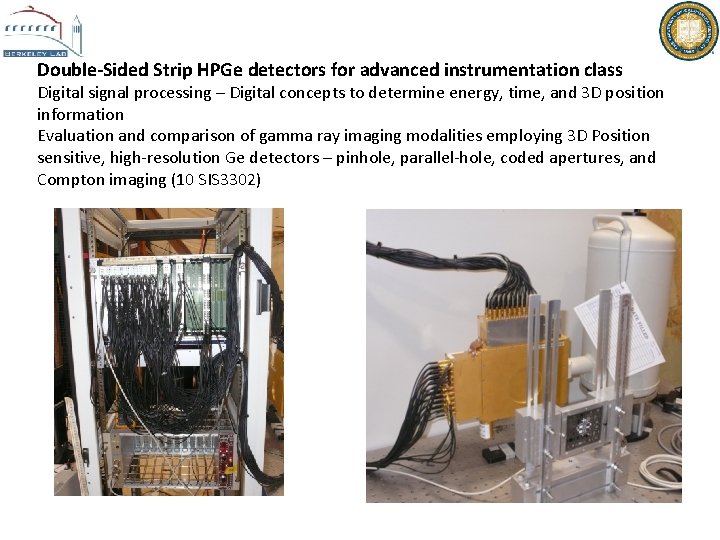

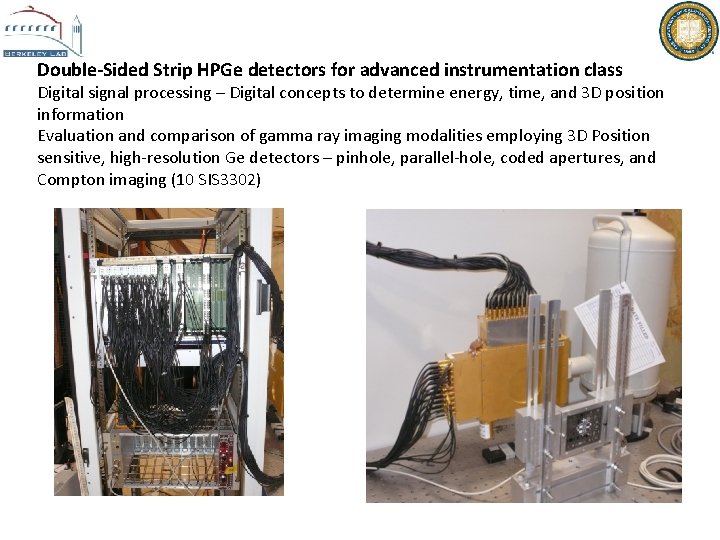

Double-Sided Strip HPGe detectors for advanced instrumentation class Digital signal processing – Digital concepts to determine energy, time, and 3 D position information Evaluation and comparison of gamma ray imaging modalities employing 3 D Position sensitive, high-resolution Ge detectors – pinhole, parallel-hole, coded apertures, and Compton imaging (10 SIS 3302)

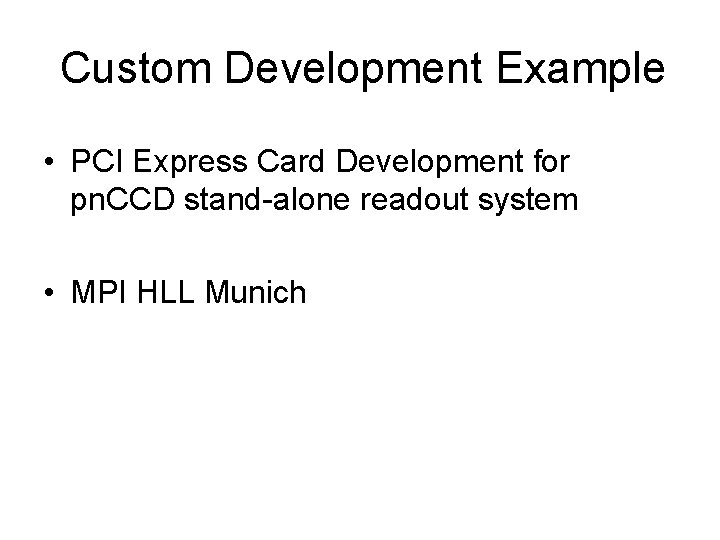

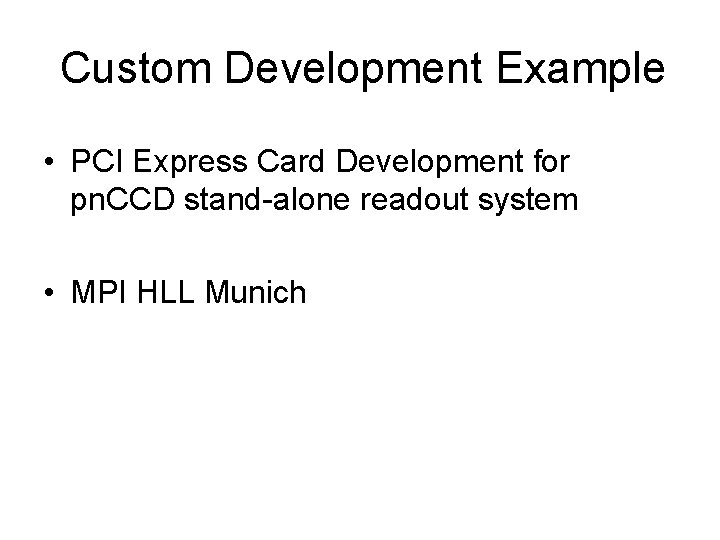

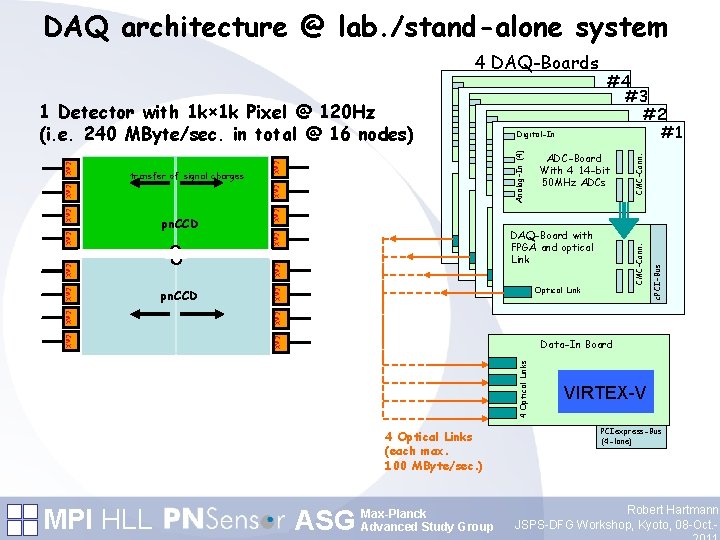

Custom Development Example • PCI Express Card Development for pn. CCD stand-alone readout system • MPI HLL Munich

pn. CCD detector module MPI HLL ASG Max-Planck Advanced Study Group Robert Hartmann JSPS-DFG Workshop, Kyoto, 08 -Oct. -

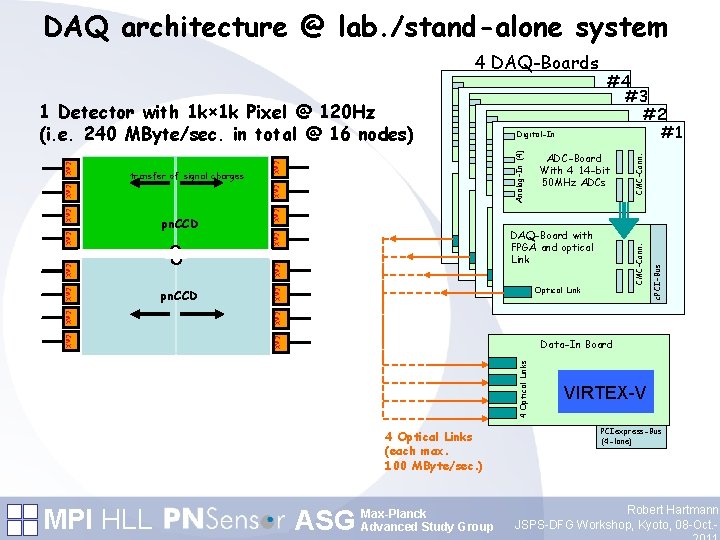

DAQ architecture @ lab. /stand-alone system CMX CMX 4 Optical Links CMX CMC-Conn. c. PCI-Bus CMC-Conn. Data-In Board 4 Optical Links (each max. 100 MByte/sec. ) MPI HLL CMC-Conn. Analog-In (4) CMX Optical Link CMC-Conn. CMX Optical Link c. PCI-Bus CMC-Conn. CMX FPGA and Memory DAQ-Board with Optical Link FPGA and Memory FPGA and optical Optical Link CMC-Conn. c. PCI-Bus CMX pn. CCD CMC-Conn. CMX 50 MHz ADCs DAQ-Board with FPGA and Memory DAQ-Board with Trigger-Out CMX pn. CCD Analog-In (4) CMX transfer of signal charges #4 #3 #2 #1 ADC-Board With. ADC-Board 4 14 -bit 100 MHz ADCs Digital-In With 4 14 -bit ADC-Board Trigger-Out 100 MHz ADCs With. ADC-Board 4 14 -bit Trigger-Out 100 MHz With ADCs 4 14 -bit Analog-In (4) 1 Detector with 1 k× 1 k Pixel @ 120 Hz (i. e. 240 MByte/sec. in total @ 16 nodes) Analog-In (4) 4 DAQ-Boards ASG Max-Planck Advanced Study Group VIRTEX-V PCIexpress-Bus (4 -lane) Robert Hartmann JSPS-DFG Workshop, Kyoto, 08 -Oct. -

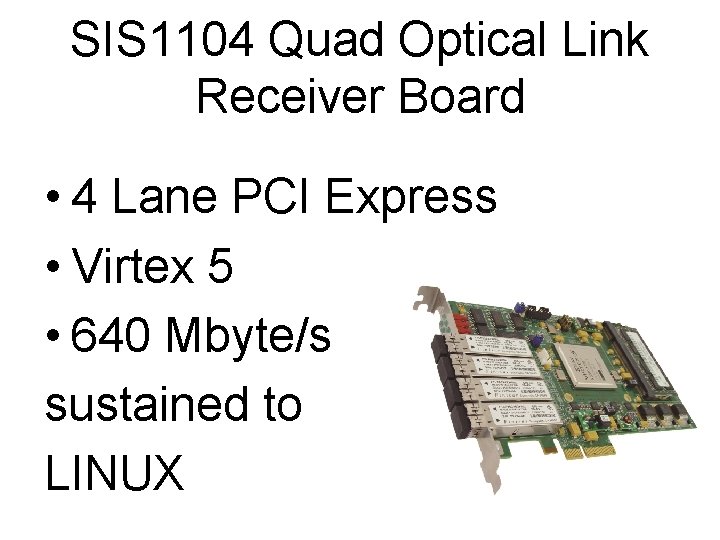

SIS 1104 Quad Optical Link Receiver Board • 4 Lane PCI Express • Virtex 5 • 640 Mbyte/s sustained to LINUX

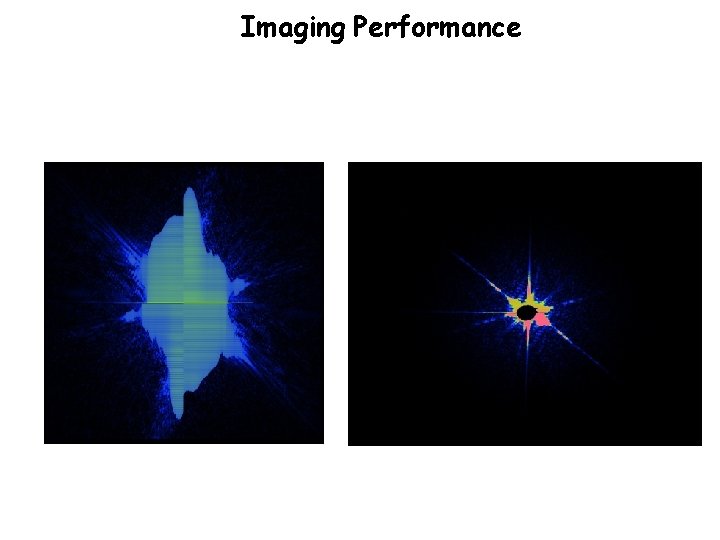

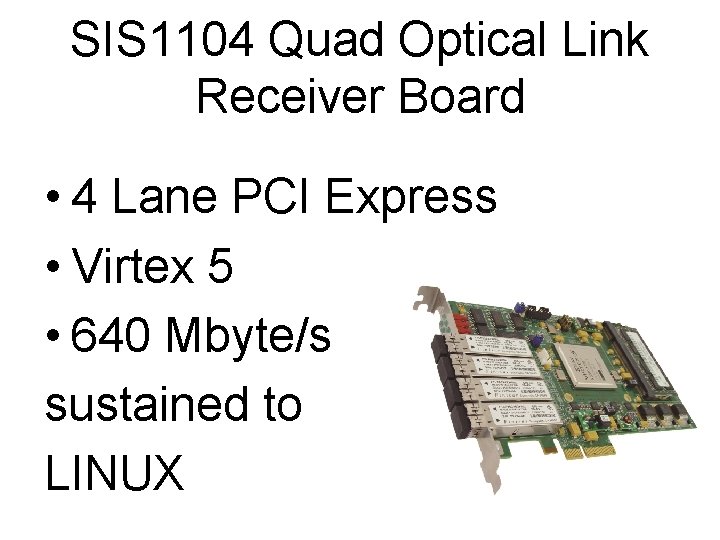

Imaging Performance

Work in Progress

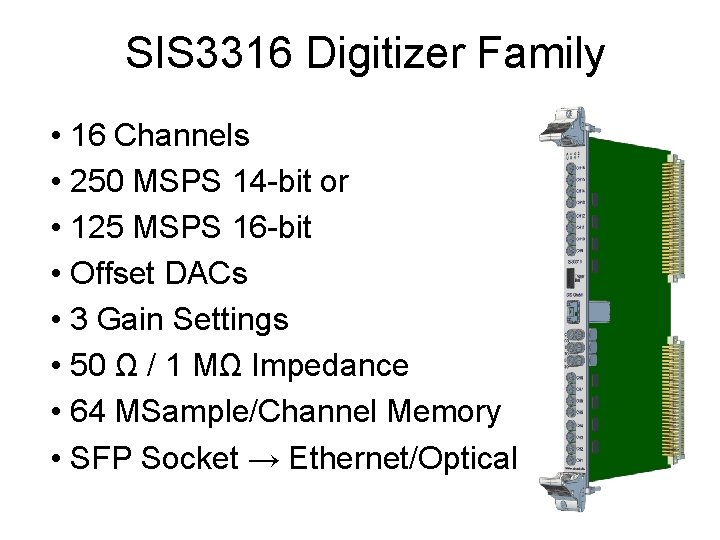

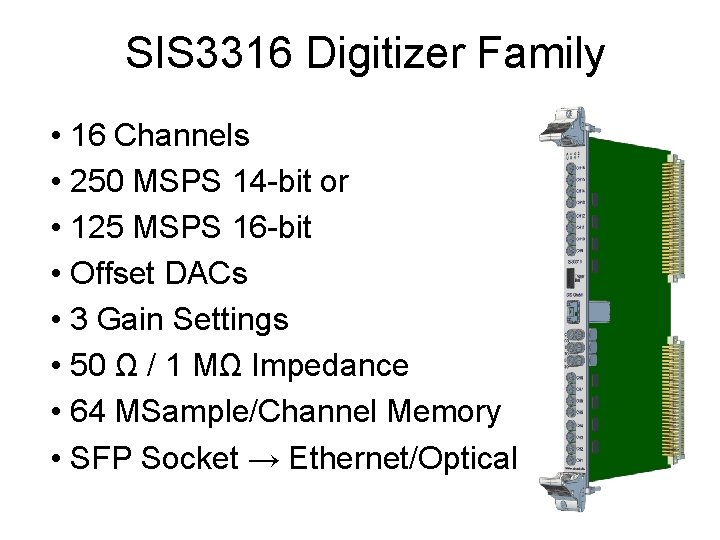

SIS 3316 Digitizer Family • 16 Channels • 250 MSPS 14 -bit or • 125 MSPS 16 -bit • Offset DACs • 3 Gain Settings • 50 Ω / 1 MΩ Impedance • 64 MSample/Channel Memory • SFP Socket → Ethernet/Optical

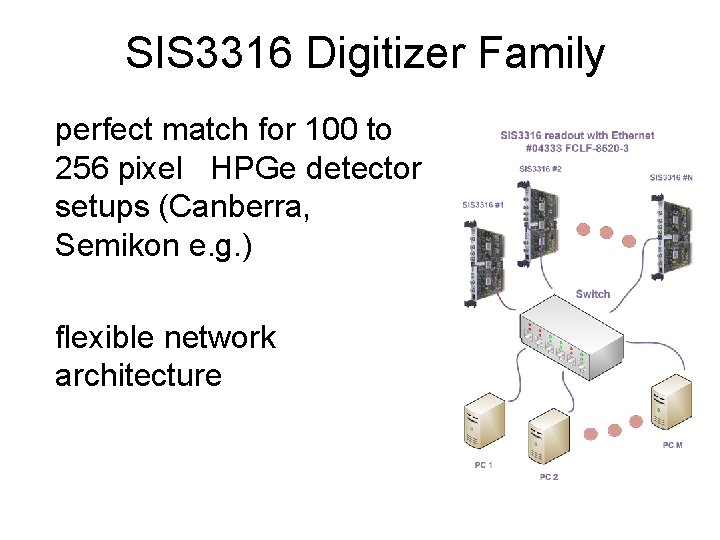

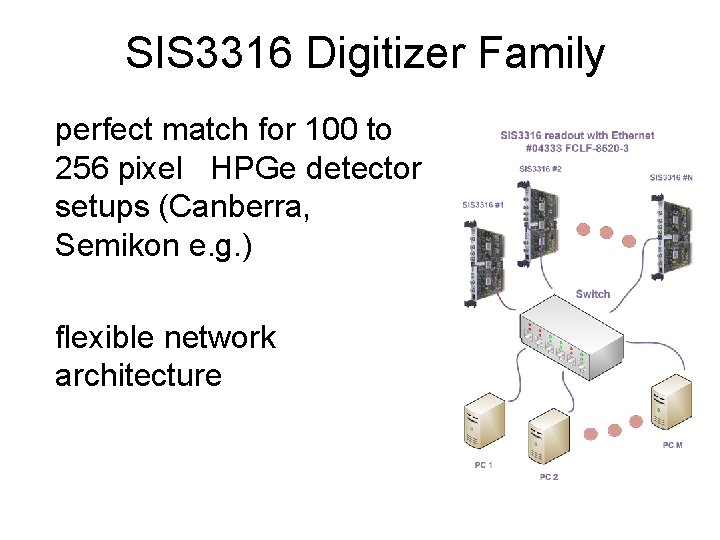

SIS 3316 Digitizer Family perfect match for 100 to 256 pixel HPGe detector setups (Canberra, Semikon e. g. ) flexible network architecture

Industry co-operation Benefits So, what‘s in it for me? • Offload part of work after specification phase • Repair/support over life cycle of equipment • Commercial availability over typical product life span on the 10 year time frame

Questions/Remarks