Solid State Detectors2 T Bowcock 1 Schedule 1

Solid State Detectors-2 T. Bowcock 1

Schedule 1 2 3 4 5 6 Position Sensors Principles of Operation of Solid State Detectors Techniques for High Performance Operation Environmental Design Measurement of time New Detector Technologies 2

Why use a Solid State Detector? • Physics requires – high rate capability • rare processes imply huge event rates – high efficiency and low dead time – good signal. /noise ratio – good resolution – electronics r/o – high speed 3

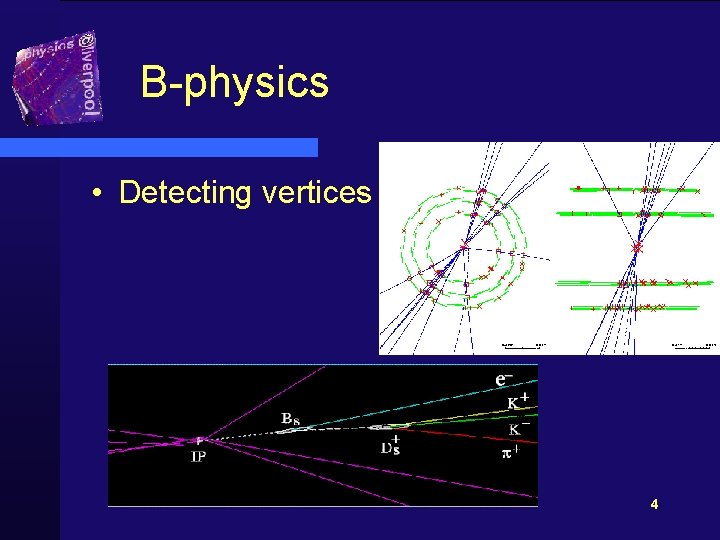

B-physics • Detecting vertices. . . 4

Silicon Properties • Electron-hole production at few e. V – compare with 30 e. V in gas • Density reduces deltas – remember bubble chamber photos(!) • 100 e-h pairs/micron • solid – easy to install close to interaction point 5

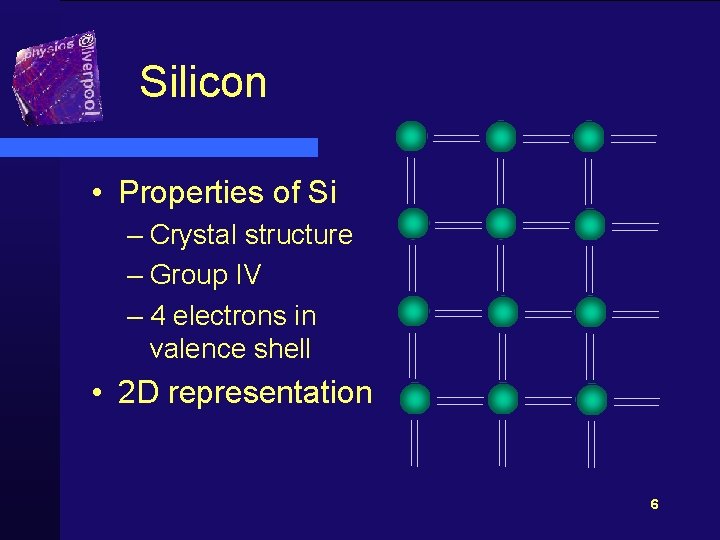

Silicon • Properties of Si – Crystal structure – Group IV – 4 electrons in valence shell • 2 D representation 6

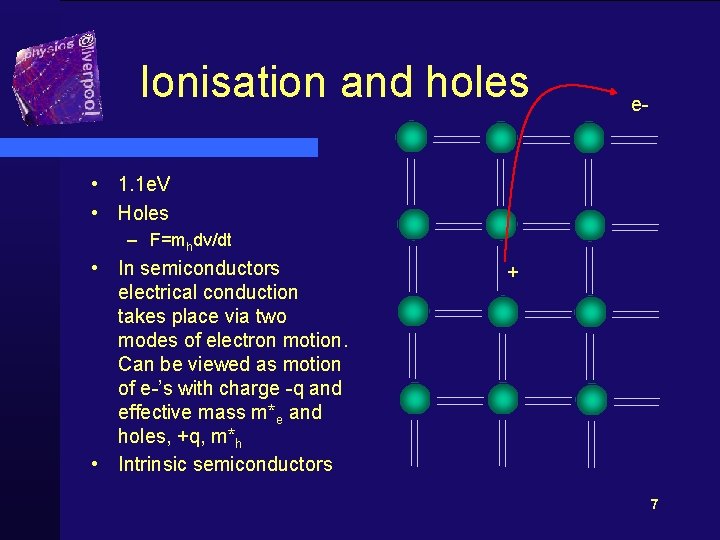

Ionisation and holes e- • 1. 1 e. V • Holes – F=mhdv/dt • In semiconductors electrical conduction takes place via two modes of electron motion. Can be viewed as motion of e-’s with charge -q and effective mass m*e and holes, +q, m*h • Intrinsic semiconductors + 7

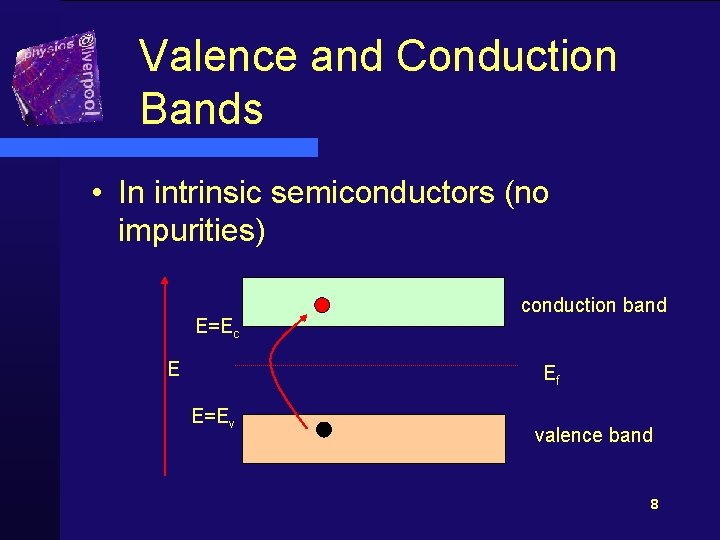

Valence and Conduction Bands • In intrinsic semiconductors (no impurities) E=Ec E conduction band Ef E=Ev valence band 8

Thermal Properties • In intrinsic semiconductor Nc=3*1019 Nv=1*1019 • Note that in intrinsic semiconductors n=p=intrinsic carrier density • For Si (at room temp) ni=1. 5*1010 9

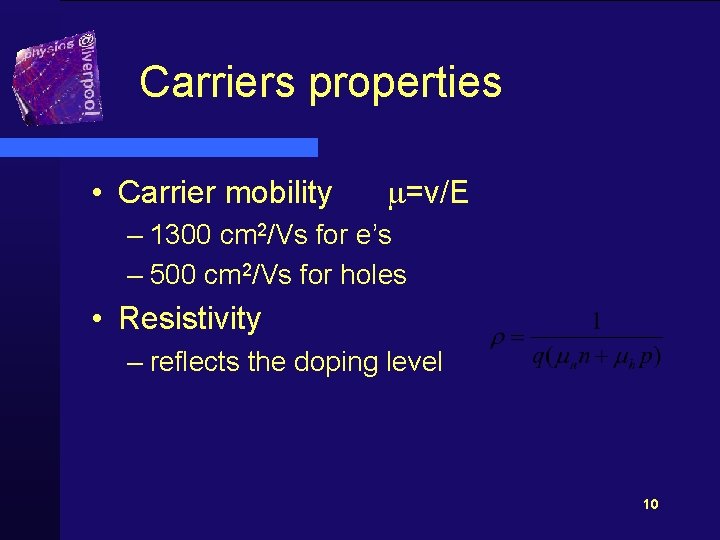

Carriers properties • Carrier mobility m=v/E – 1300 cm 2/Vs for e’s – 500 cm 2/Vs for holes • Resistivity – reflects the doping level 10

Intrinsic Silicon cont’d • At room temp in a 300 micron thick detector with an area of 1 cm 2 total free carriers would be about 109 – cool (lower T) • can be done but cryogenics are bulky and expensive – reverse biased diode operation 11

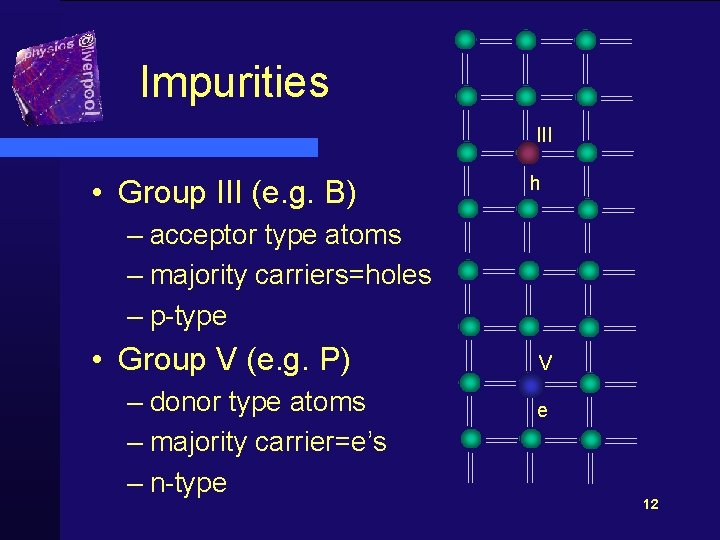

Impurities III • Group III (e. g. B) h – acceptor type atoms – majority carriers=holes – p-type • Group V (e. g. P) – donor type atoms – majority carrier=e’s – n-type V e 12

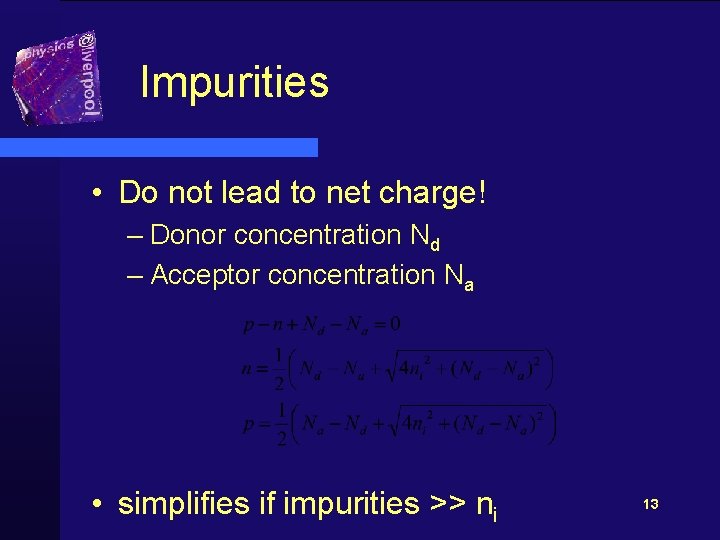

Impurities • Do not lead to net charge! – Donor concentration Nd – Acceptor concentration Na • simplifies if impurities >> ni 13

Band Structure • Doped silicon E=Ec conduction band Ed (n-type) E E=Ev Ea (p-type) valence band 14

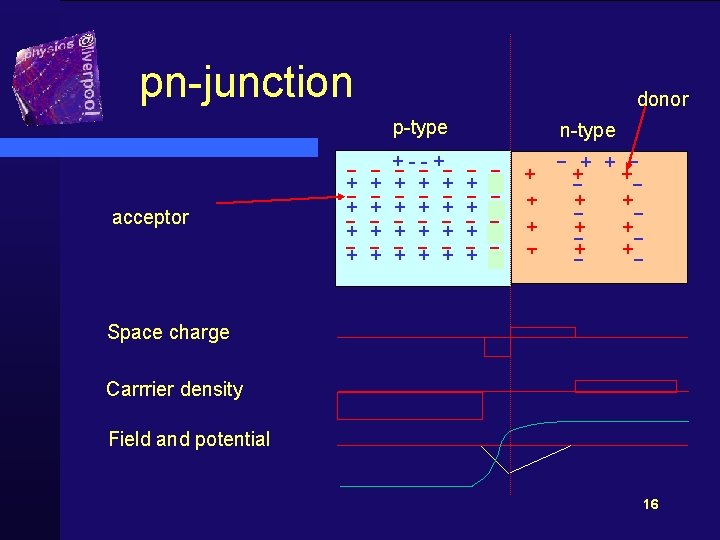

pn-junction donor p-type acceptor + + + - - +- - -- +- + + + - - + + + + n-type + + + + - - + + + + + - Space charge Carrrier density Field and potential 16

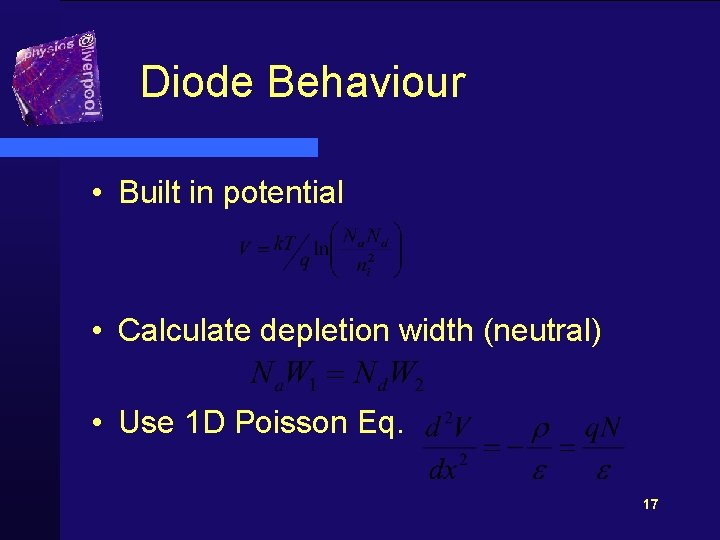

Diode Behaviour • Built in potential • Calculate depletion width (neutral) • Use 1 D Poisson Eq. 17

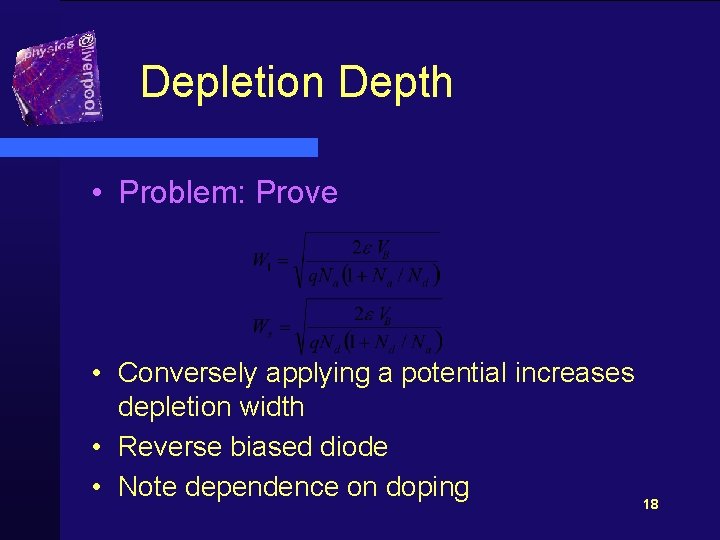

Depletion Depth • Problem: Prove • Conversely applying a potential increases depletion width • Reverse biased diode • Note dependence on doping 18

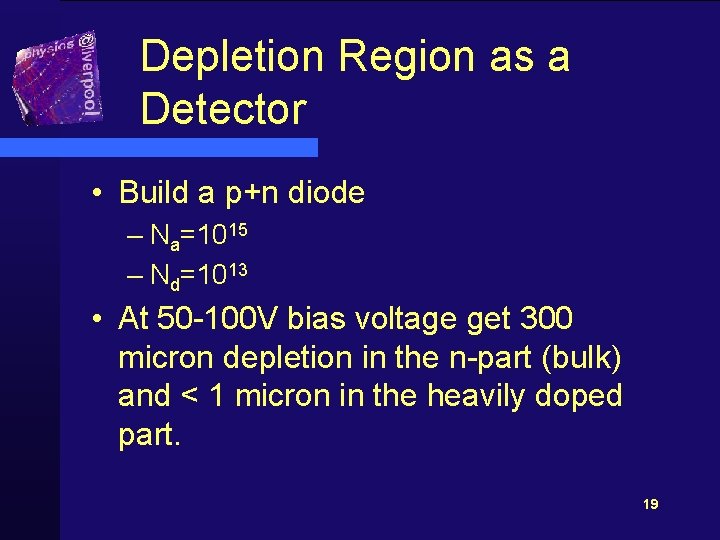

Depletion Region as a Detector • Build a p+n diode – Na=1015 – Nd=1013 • At 50 -100 V bias voltage get 300 micron depletion in the n-part (bulk) and < 1 micron in the heavily doped part. 19

Depletion region • In the depletion region continual thermal generation of eh pairs – leakage current – depends on volume • Ionisation will also create pairs that will also drift and be collected – signal/noise 20

IV and CV of diodes 21

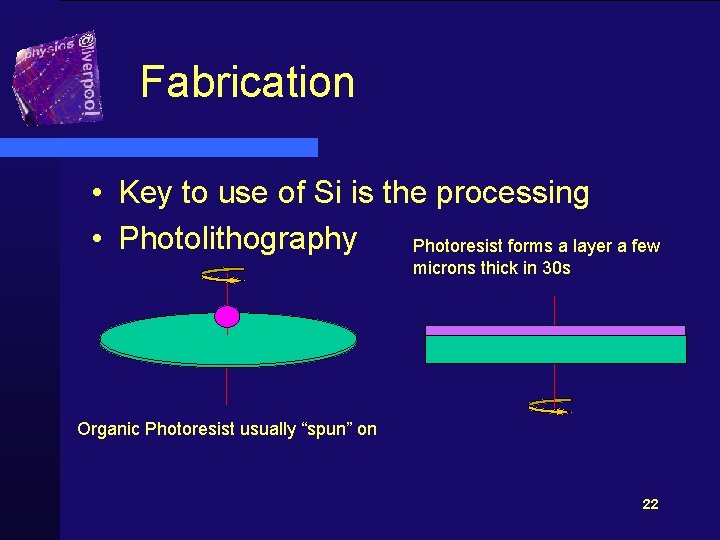

Fabrication • Key to use of Si is the processing • Photolithography Photoresist forms a layer a few microns thick in 30 s Organic Photoresist usually “spun” on 22

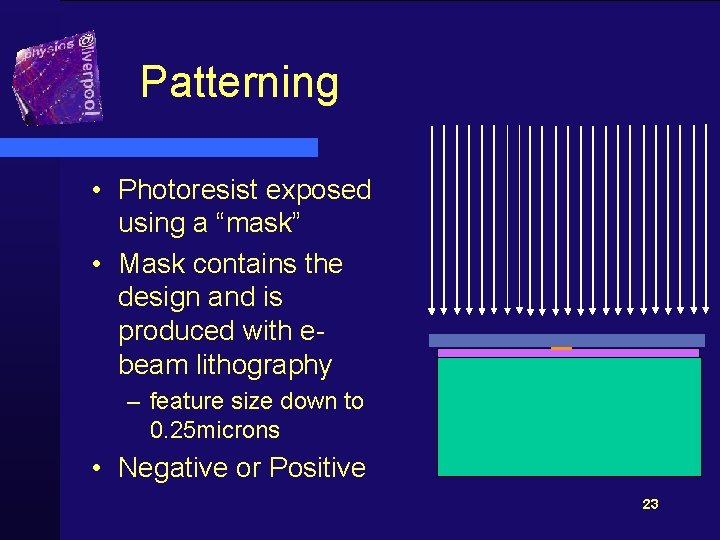

Patterning • Photoresist exposed using a “mask” • Mask contains the design and is produced with ebeam lithography – feature size down to 0. 25 microns • Negative or Positive 23

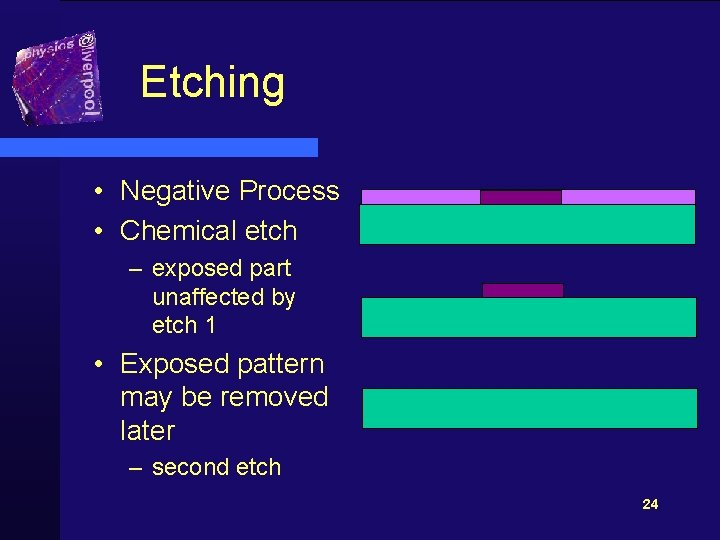

Etching • Negative Process • Chemical etch – exposed part unaffected by etch 1 • Exposed pattern may be removed later – second etch 24

Example: • Aluminium line 25

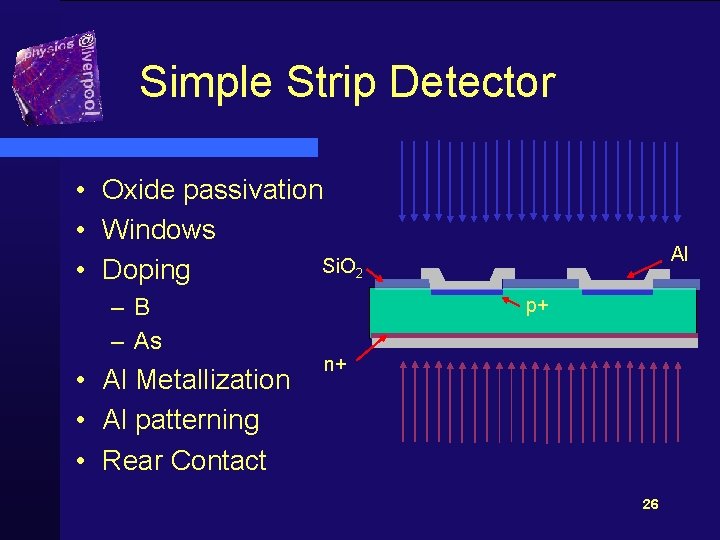

Simple Strip Detector • Oxide passivation • Windows Si. O 2 • Doping –B – As • Al Metallization • Al patterning • Rear Contact Al p+ n+ 26

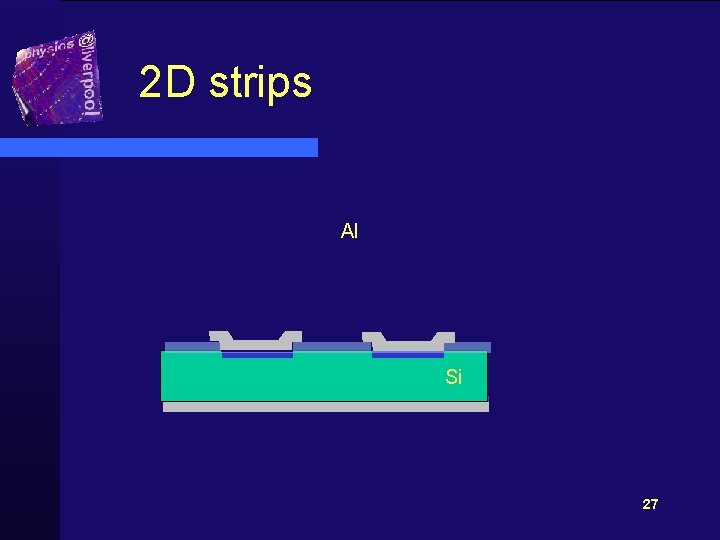

2 D strips Al Si 27

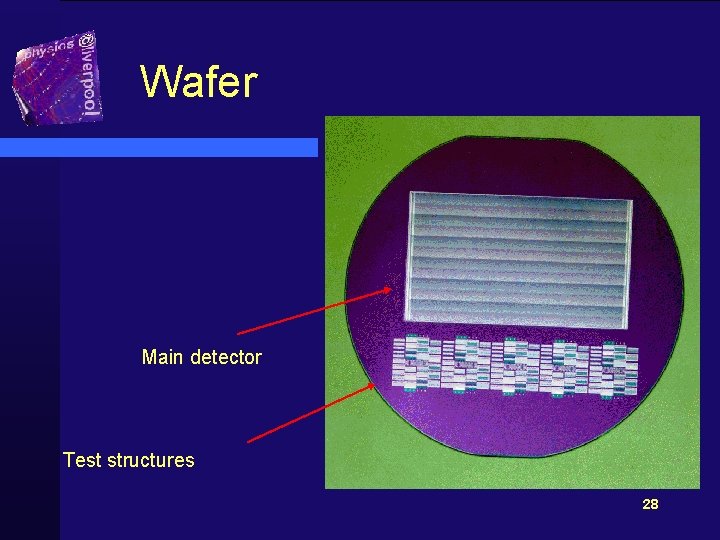

Wafer Main detector Test structures 28

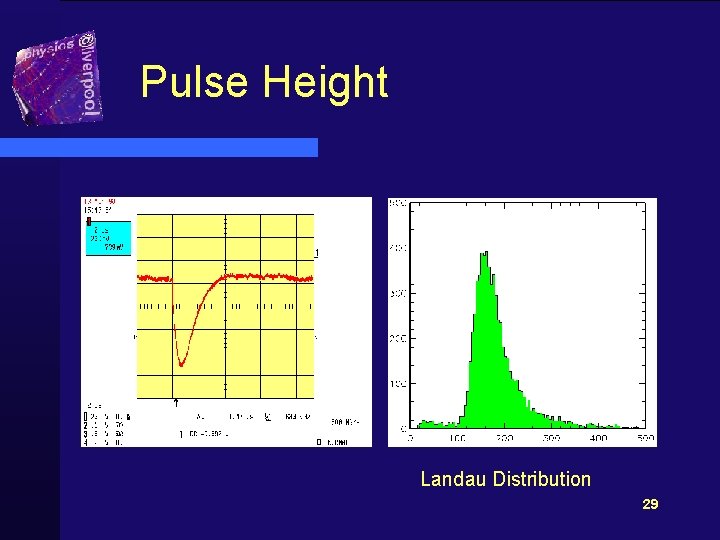

Pulse Height Landau Distribution 29

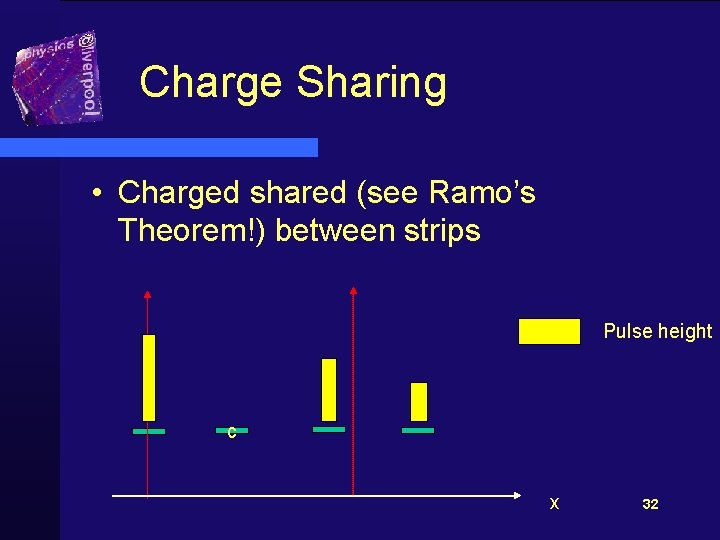

Signal Shape • Simulation – charges follow efield – Ramo’s Theorem – Finite element • Matches data 30

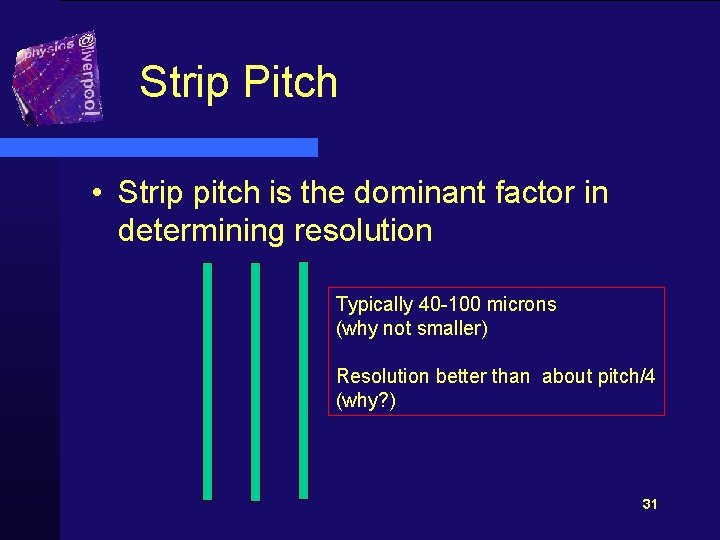

Strip Pitch • Strip pitch is the dominant factor in determining resolution Typically 40 -100 microns (why not smaller) Resolution better than about pitch/4 (why? ) 31

Charge Sharing • Charged shared (see Ramo’s Theorem!) between strips Pulse height c x 32

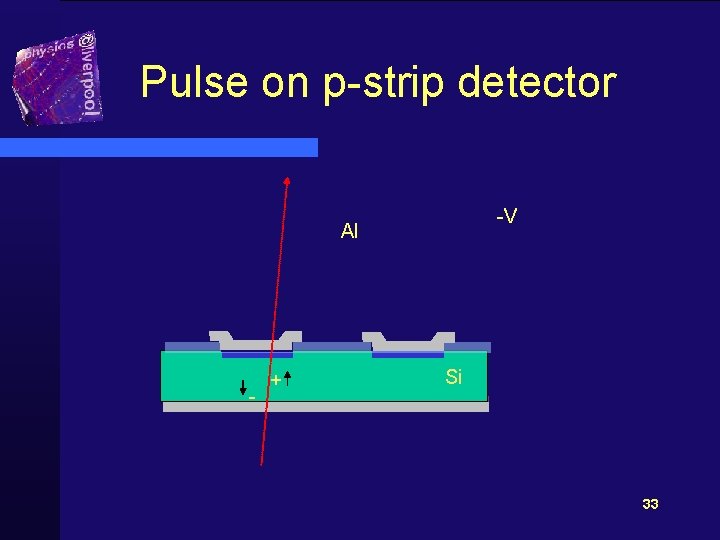

Pulse on p-strip detector -V Al - + Si 33

Electronics 34

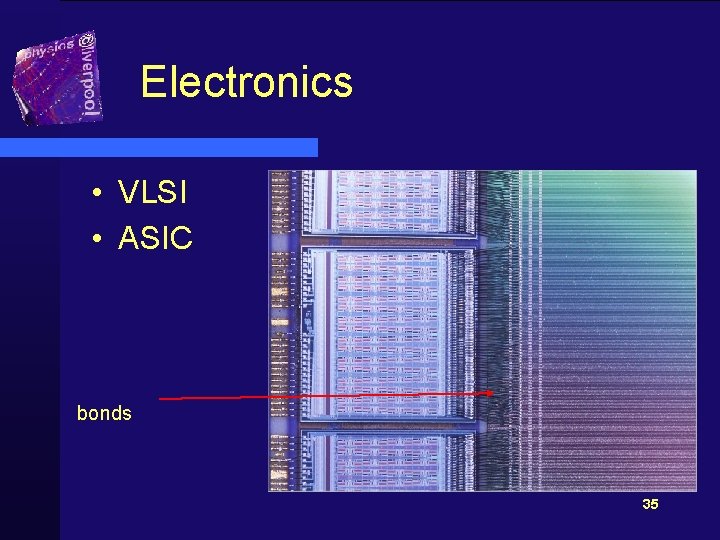

Electronics • VLSI • ASIC bonds 35

Electronic Noise • Noise sources – coupling of strips to each other an back plane (extra load and signal loss) – intrinsic to amplifier • ENC = a +b C – d may vary from 100 -1000 depending on speed – b varies from 20 to 100 depending on speed – Sources from • leakage current • load resisitor 36

Signal/Noise • Electronics – speed – intrinsic characteristics • Thickness of detector and Vbias • MIPS • Capacitance of Strips – resistors • Desire about 10/1 S/N 37

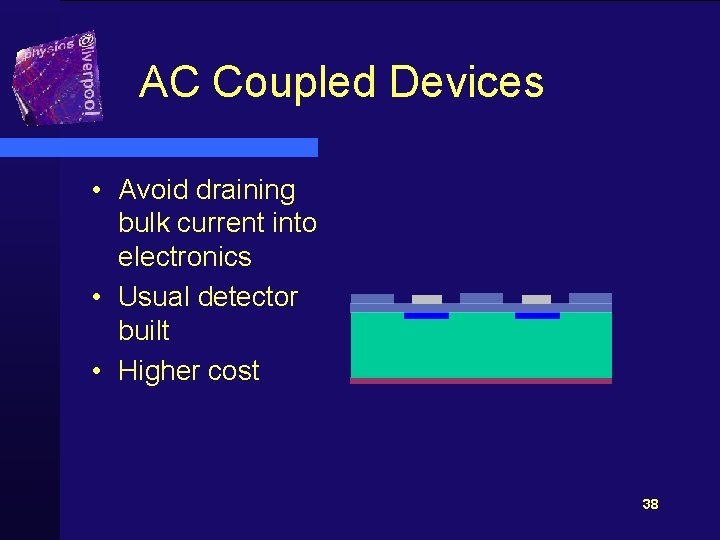

AC Coupled Devices • Avoid draining bulk current into electronics • Usual detector built • Higher cost 38

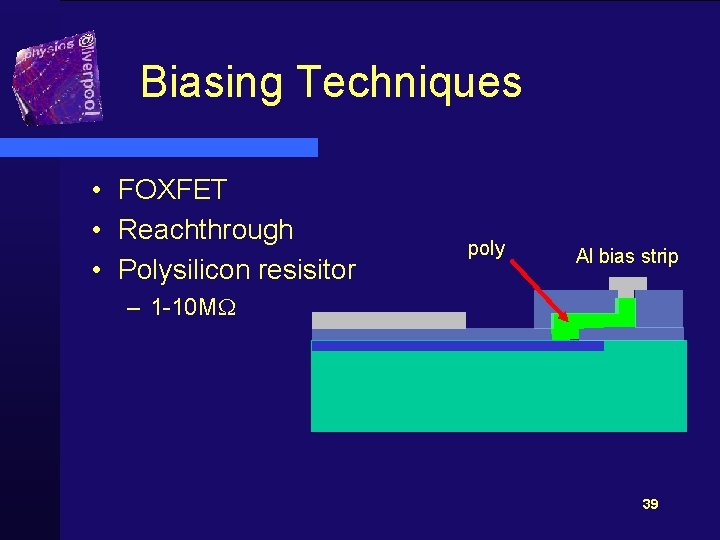

Biasing Techniques • FOXFET • Reachthrough • Polysilicon resisitor poly Al bias strip – 1 -10 M 39

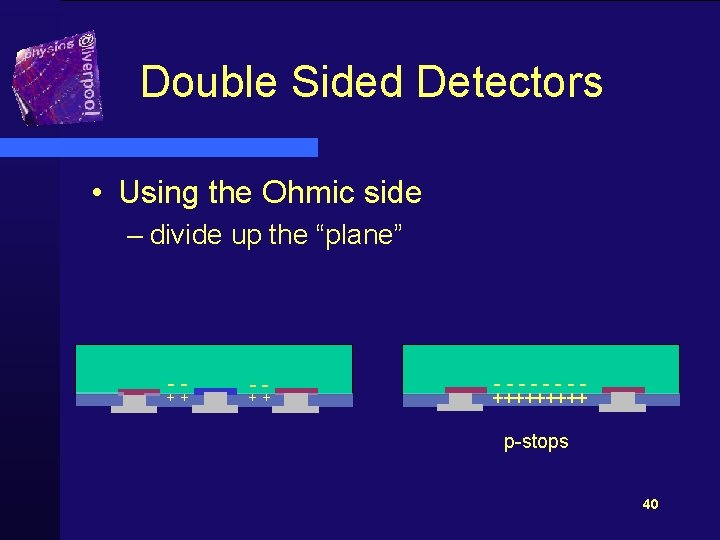

Double Sided Detectors • Using the Ohmic side – divide up the “plane” ---- +++++ p-stops 40 -- ++

Pixel Detectors • Pixel detectors are identical in principal to strip detectors – shape of pads smaller • few microns or 10’s of microns compared with strips of 6 cm or so, – more diffiucult to route out • expensive bump bonded electronics – low capacitance(noise) – intrinsically 2 D rather than 1 D 41

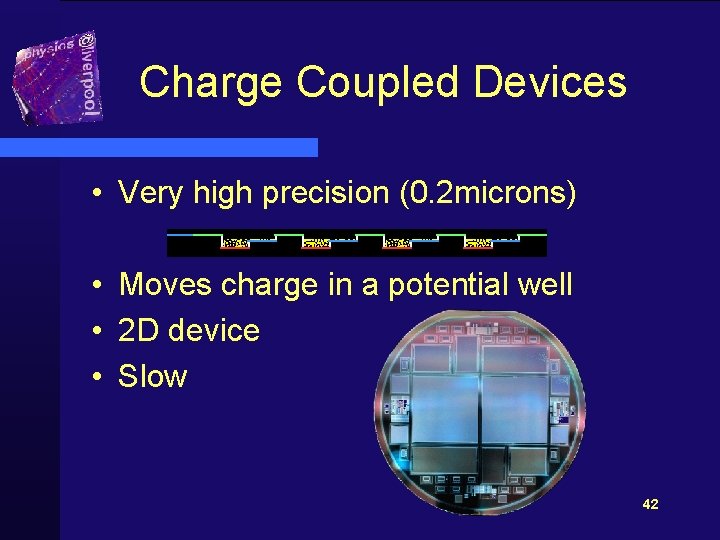

Charge Coupled Devices • Very high precision (0. 2 microns) • Moves charge in a potential well • 2 D device • Slow 42

CCD • Use small low capacity elements and exchange information <10 e noise • Matrix of potential wells created “cell” n-doping p-type 43

Summary • Have seen the basics of how a strip/pixel detector works – capable of adequate S/N – only cost effective for last 10 years with advent of second generation fabrication – easily modifiable geometry • Next: high performance operation 44

- Slides: 44