Software Transactional Memory STM Harris T and Fraser

- Slides: 18

Software Transactional Memory (STM) Harris, T. and Fraser, K. Language Support for Lightweight Transactions. In Proceedings of Object Oriented Programming, Systems, Languages & Applications. October, 2003. Ramazan Bitirgen bitirgen@csl. cornell. edu CS 612

Outline n n n n Introduction Motivation Conditional Critical Regions Software Transactions Evaluation Future Work References 10/24/2021 CS 612 2

Introduction n Software Transactional Memory (STM): q n Requires hardware support q n n A generic non-blocking synchronization construct that allows correct sequential objects to be converted automatically into correct concurrent objects. CAS in [1], LL/SC in [2] Basic requirement for an STM: linearizability Advantages of STM: q q q Applicability to today's machines Portability among machines Resiliency in the face of timing anomalies 10/24/2021 CS 612 3

Motivation n Concurrency is a concern for all the platforms q q q n Large cc-NUMA servers Modest symmetric shared-memory MPs Single processors with SMT or pre-emptive scheduling How to adjust the granularity of locking? q Protect each data structure with separate locks n q Reduces parallelism Use many smaller locks for the same data structure n 10/24/2021 Juggling the locks CS 612 4

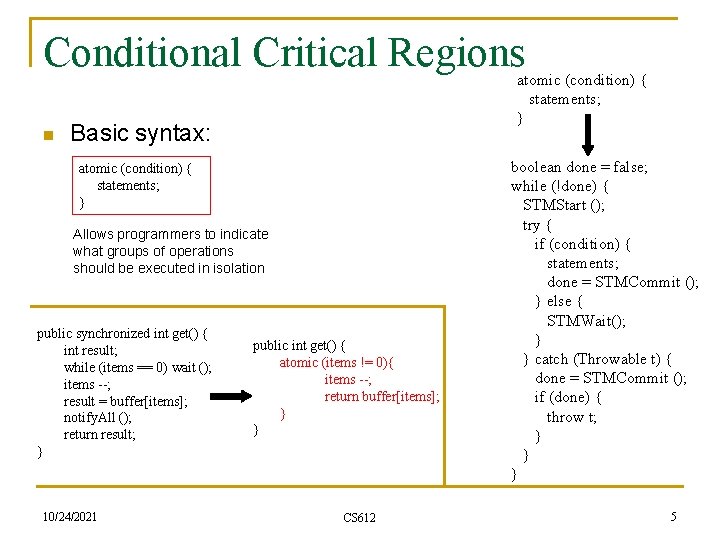

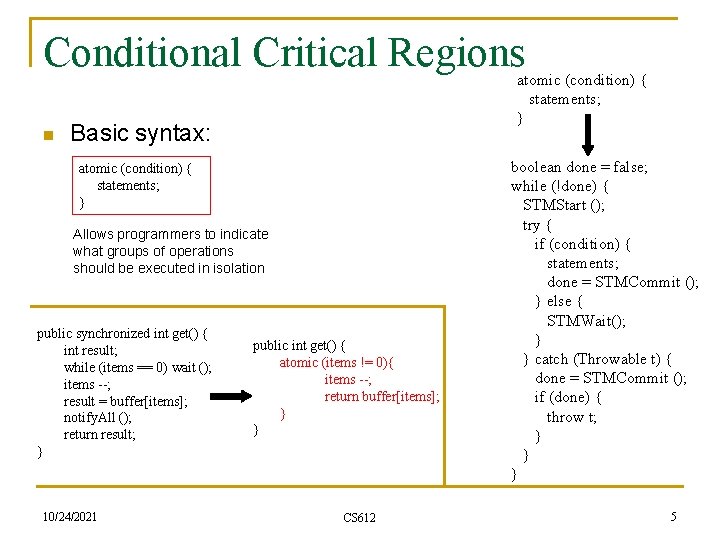

Conditional Critical Regions n atomic (condition) { statements; } Basic syntax: atomic (condition) { statements; } Allows programmers to indicate what groups of operations should be executed in isolation public synchronized int get() { int result; while (items == 0) wait (); items --; result = buffer[items]; notify. All (); return result; } 10/24/2021 public int get() { atomic (items != 0){ items --; return buffer[items]; } } CS 612 boolean done = false; while (!done) { STMStart (); try { if (condition) { statements; done = STMCommit (); } else { STMWait(); } } catch (Throwable t) { done = STMCommit (); if (done) { throw t; } } } 5

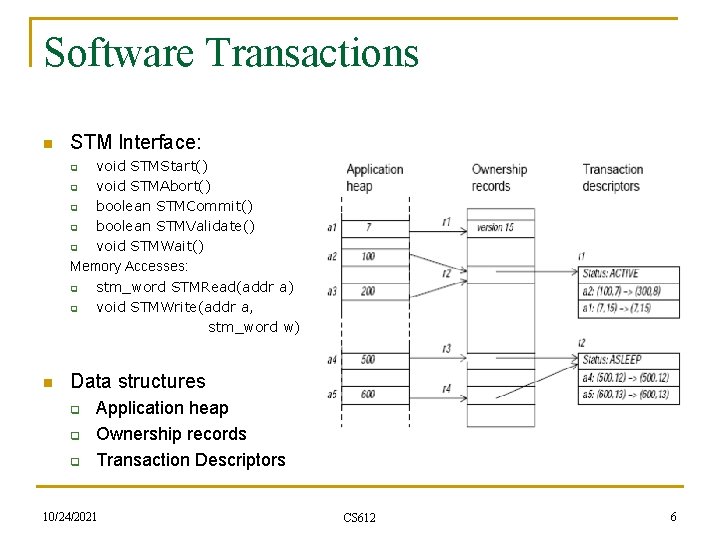

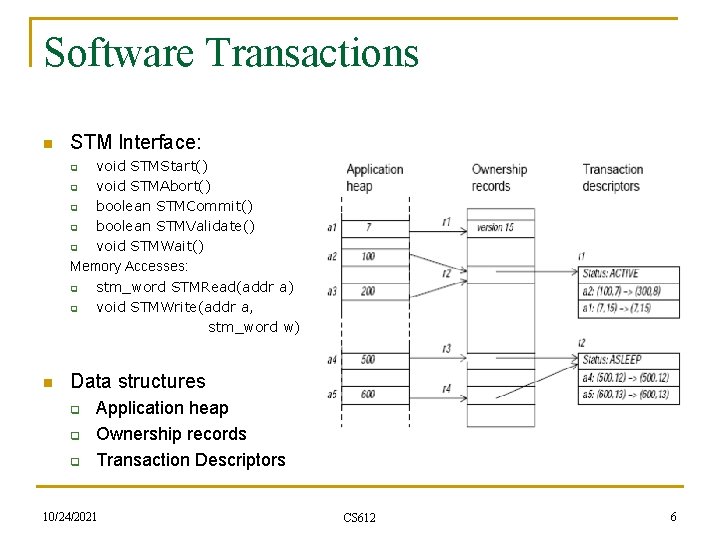

Software Transactions n STM Interface: void STMStart() q void STMAbort() q boolean STMCommit() q boolean STMValidate() q void STMWait() Memory Accesses: q stm_word STMRead(addr a) q void STMWrite(addr a, stm_word w) q n Data structures q q q Application heap Ownership records Transaction Descriptors 10/24/2021 CS 612 6

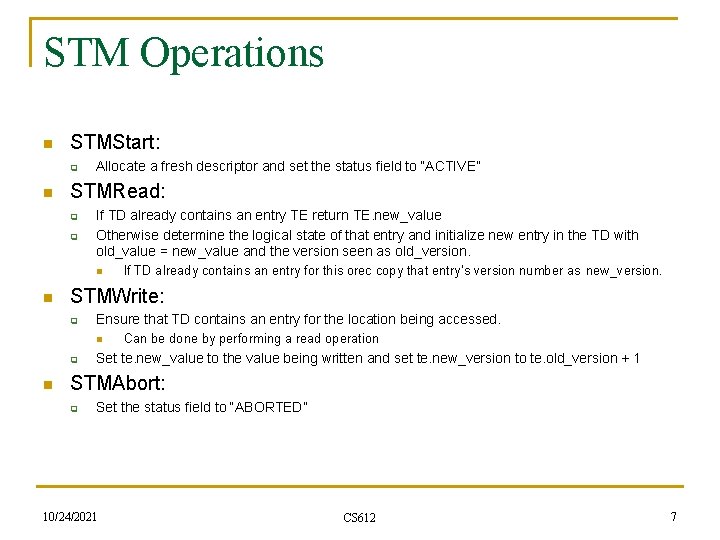

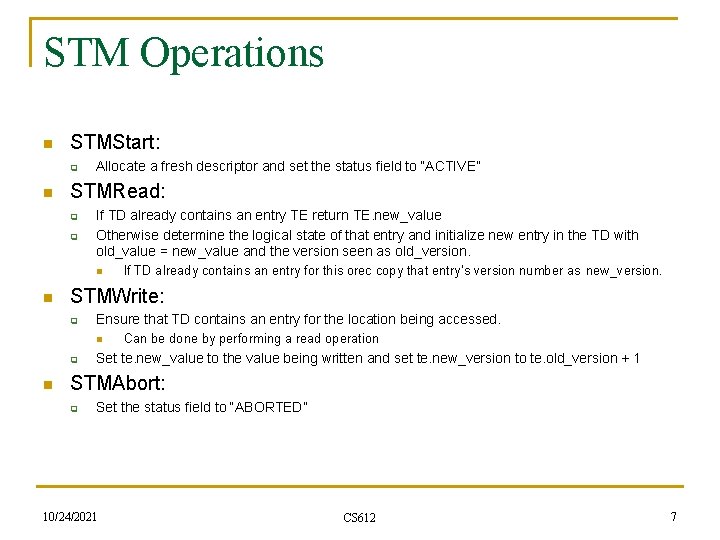

STM Operations n STMStart: q n Allocate a fresh descriptor and set the status field to “ACTIVE” STMRead: q q If TD already contains an entry TE return TE. new_value Otherwise determine the logical state of that entry and initialize new entry in the TD with old_value = new_value and the version seen as old_version. n n STMWrite: q Ensure that TD contains an entry for the location being accessed. n q n If TD already contains an entry for this orec copy that entry’s version number as new_version. Can be done by performing a read operation Set te. new_value to the value being written and set te. new_version to te. old_version + 1 STMAbort: q Set the status field to “ABORTED” 10/24/2021 CS 612 7

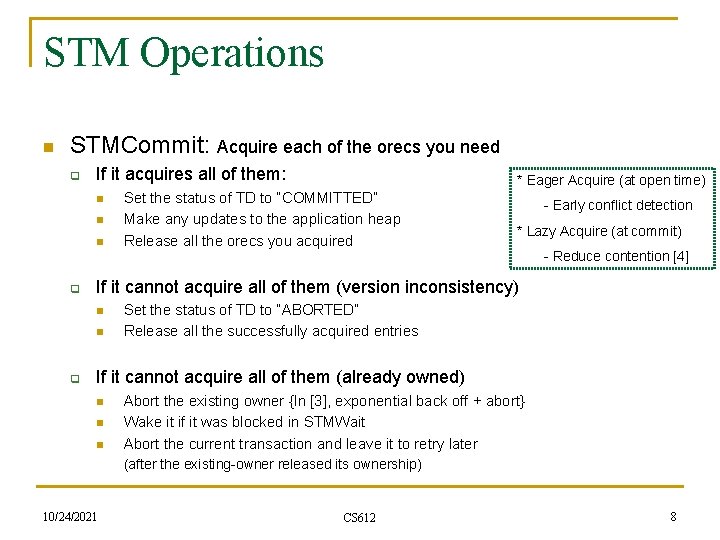

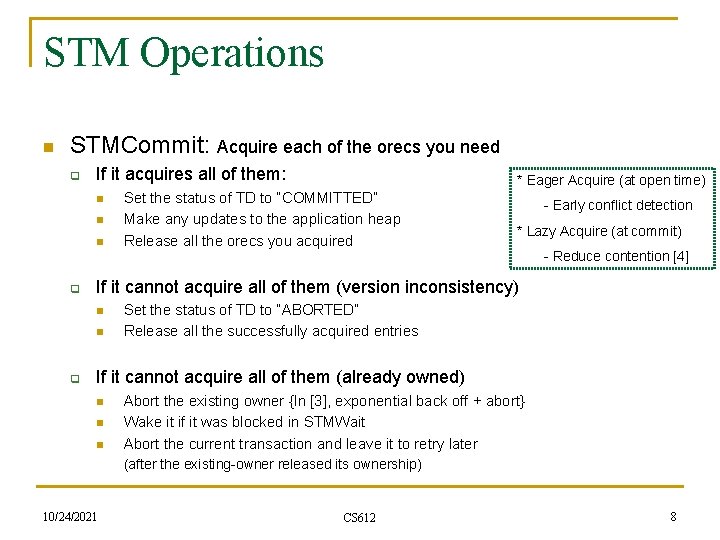

STM Operations n STMCommit: Acquire each of the orecs you need q If it acquires all of them: n n n q Set the status of TD to “COMMITTED” Make any updates to the application heap Release all the orecs you acquired - Early conflict detection * Lazy Acquire (at commit) - Reduce contention [4] If it cannot acquire all of them (version inconsistency) n n q * Eager Acquire (at open time) Set the status of TD to “ABORTED” Release all the successfully acquired entries If it cannot acquire all of them (already owned) n n n Abort the existing owner {In [3], exponential back off + abort} Wake it if it was blocked in STMWait Abort the current transaction and leave it to retry later (after the existing-owner released its ownership) 10/24/2021 CS 612 8

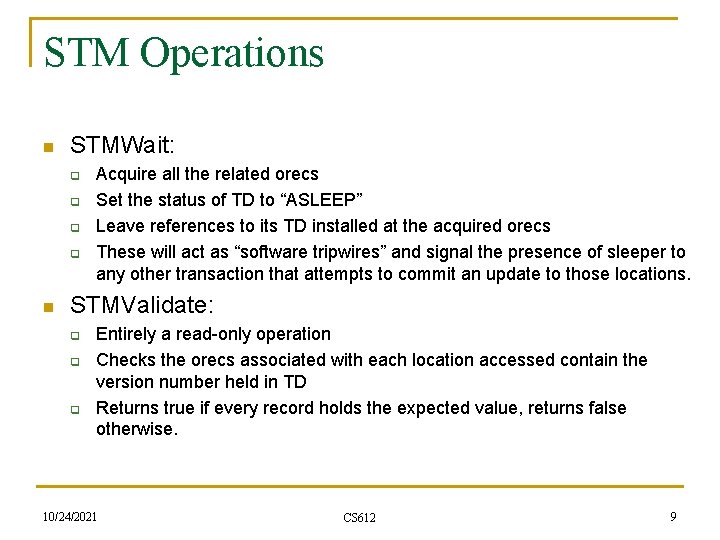

STM Operations n STMWait: q q n Acquire all the related orecs Set the status of TD to “ASLEEP” Leave references to its TD installed at the acquired orecs These will act as “software tripwires” and signal the presence of sleeper to any other transaction that attempts to commit an update to those locations. STMValidate: q q q Entirely a read-only operation Checks the orecs associated with each location accessed contain the version number held in TD Returns true if every record holds the expected value, returns false otherwise. 10/24/2021 CS 612 9

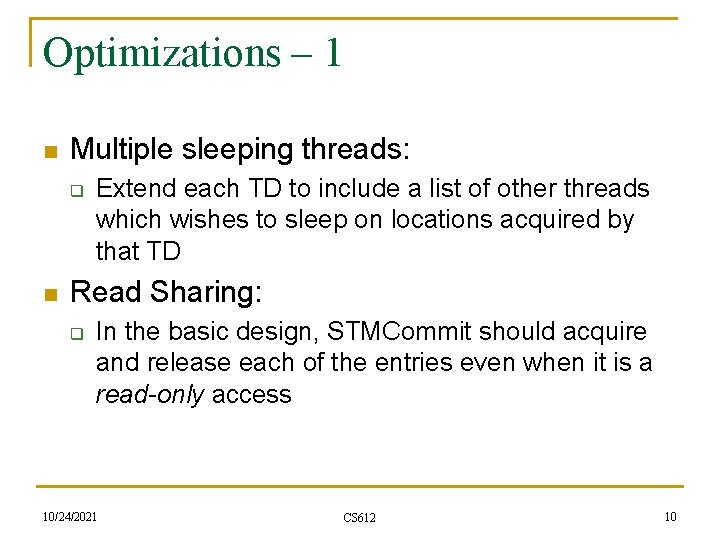

Optimizations – 1 n Multiple sleeping threads: q n Extend each TD to include a list of other threads which wishes to sleep on locations acquired by that TD Read Sharing: q In the basic design, STMCommit should acquire and release each of the entries even when it is a read-only access 10/24/2021 CS 612 10

Optimizations – 2 n Read Sharing: (cont’d) q 1 -Acquire the locations subject to an update 2 -Check the states of the read locations 3 -Attempt to update TD. state to “COMMITTED” q Add another phase: READ_PHASE q q n n 10/24/2021 1 READ_PHASE 2 3 If another transaction encounters one in READ_PHASE then it causes the one encountered to abort. CS 612 11

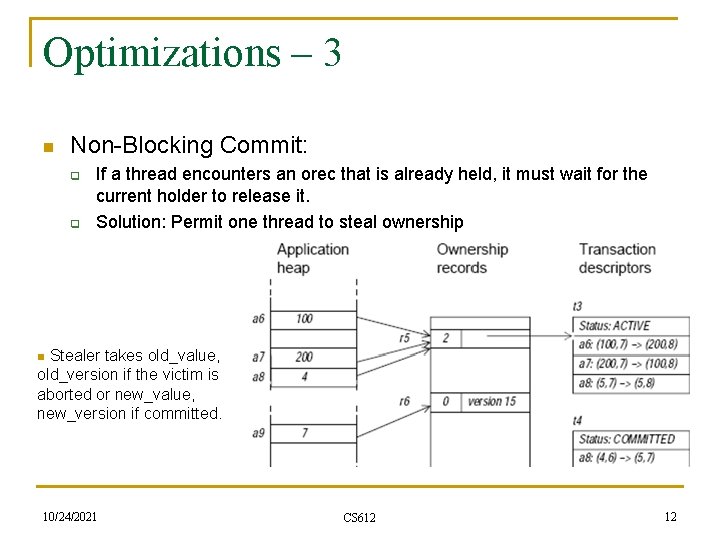

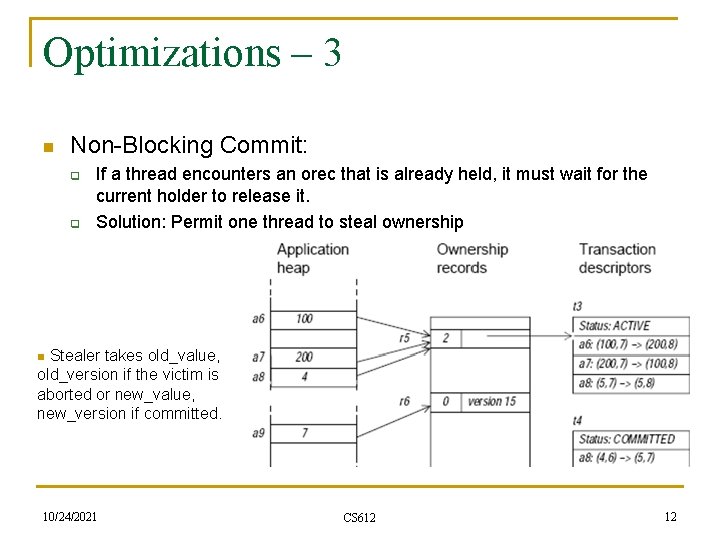

Optimizations – 3 n Non-Blocking Commit: q q If a thread encounters an orec that is already held, it must wait for the current holder to release it. Solution: Permit one thread to steal ownership Stealer takes old_value, old_version if the victim is aborted or new_value, new_version if committed. n 10/24/2021 CS 612 12

Optimizations – Ownership Stealing n Previous owner committed but not updated the heap: q q n n No control over when those updates will occur. We must ensure that writes made by new owner succeed those made by the previous owner. Use counters, increment atomically for each steal, decrement for each release. If a thread discovers that ownership has been stolen from it, it re-does the updates made by the new-owner. 10/24/2021 CS 612 13

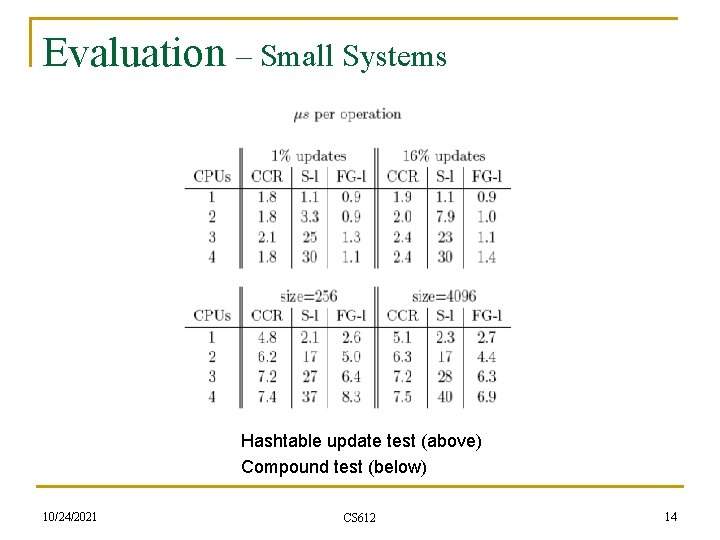

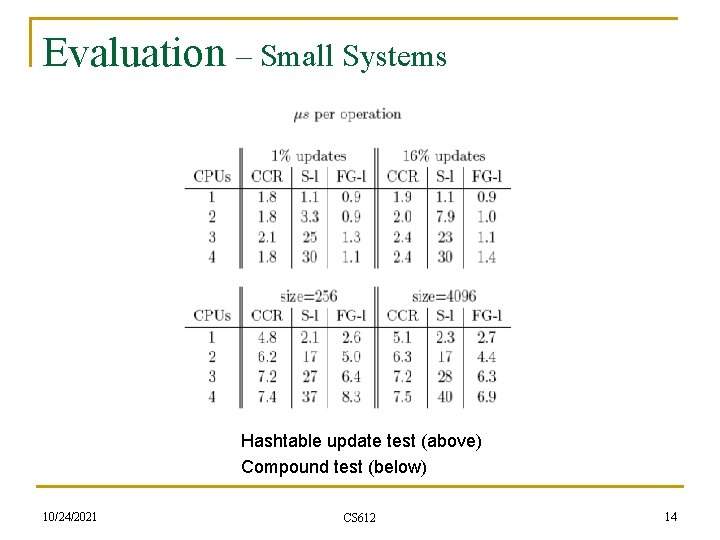

Evaluation – Small Systems Hashtable update test (above) Compound test (below) 10/24/2021 CS 612 14

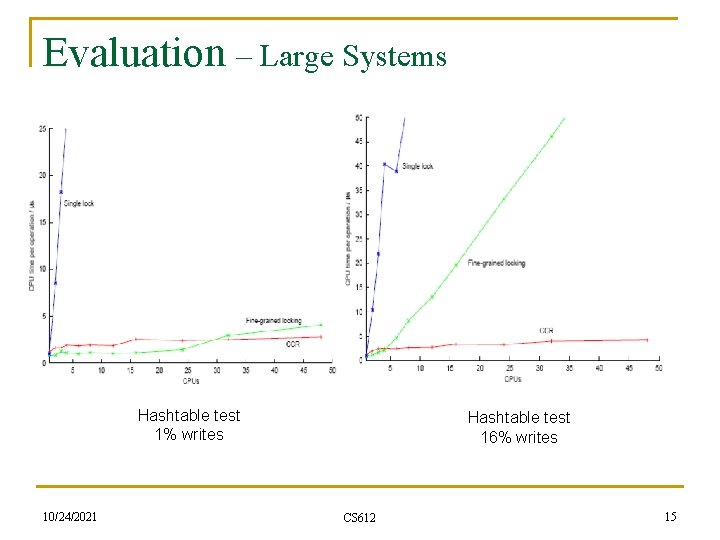

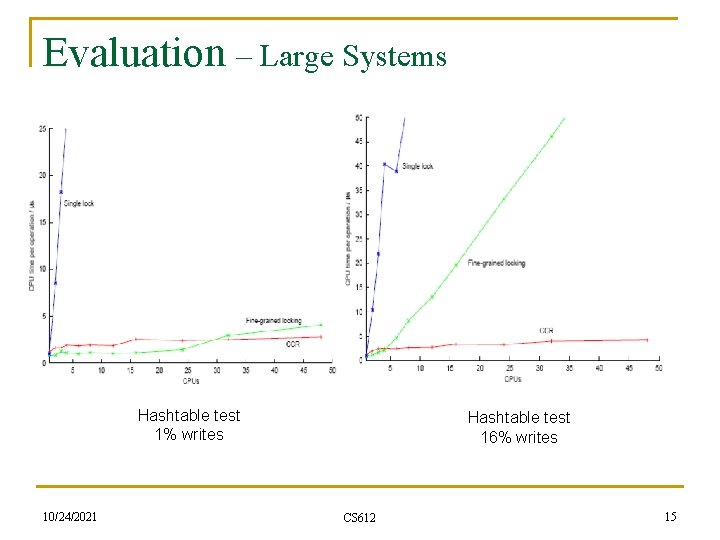

Evaluation – Large Systems Hashtable test 1% writes 10/24/2021 Hashtable test 16% writes CS 612 15

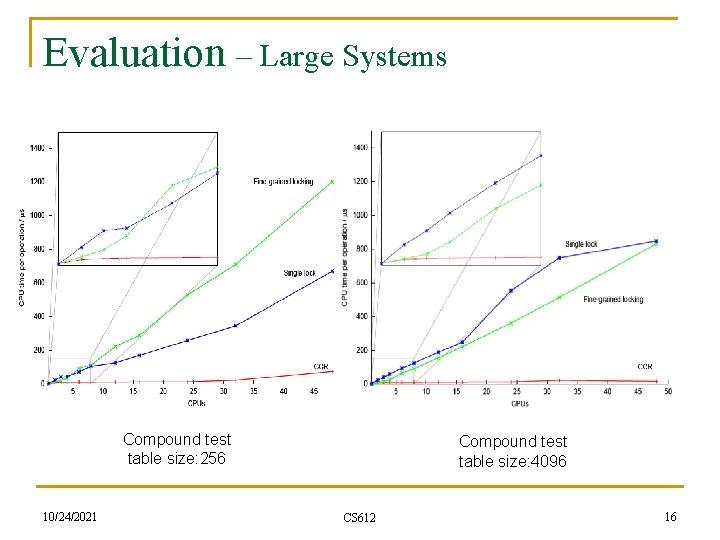

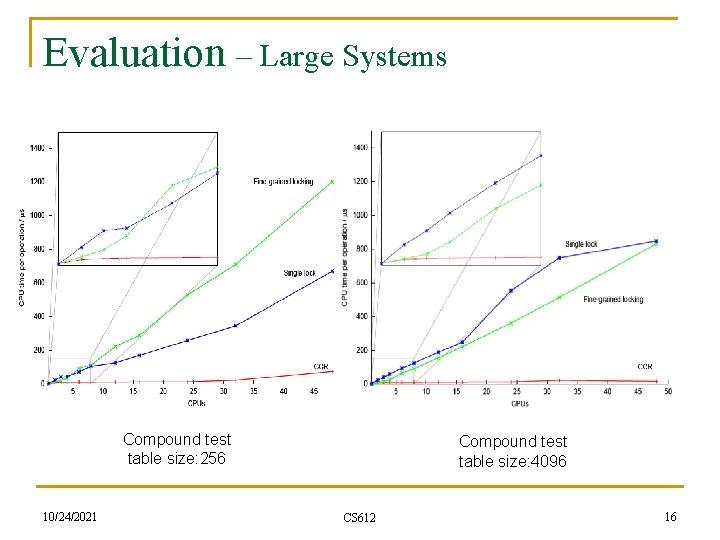

Evaluation – Large Systems Compound test table size: 256 10/24/2021 Compound test table size: 4096 CS 612 16

Future Work n Benchmarking and Evaluation q n Alternative STM Implementations q q n Use wide range of data structures If contention is rare, allow updates to be made in place without the indirection through a TD Composable Transactions [5] Hardware Support 10/24/2021 CS 612 17

References 1. 2. 3. 4. 5. n Harris, T. and Fraser, K. Language Support for Lightweight Transactions. In Proceedings of Object Oriented Programming, Systems, Languages & Applications. October, 2003. Shavit, N. and Touitou, D. Software Transactional Memory. In 14 th ACM Symposium on the Principles of Distributed Computing, 1995. Herlihy, M. , Luchangco, V. , Moir, M. , and Scherer III, W. N. Software Transactional Memory for Dynamic-Sized Data Structures. In Proceedings of the 22 nd Annual ACM Symposium on Principles of Distributed Computing, July 2003. Marathe, J. V. , Scherer III, W. N. , Scott, L. M. In DISC 2005, LNCS 3724, pp. 354– 368, 2005. Harris, T. , Marlow, S. , Jones, S. P. , Herlihy, M. Composable Memory Transactions. In PPo. PP’ 05, June 2005. Source Code: http: //www. cl. cam. ac. uk/Research/SRG/netos/lock-free 10/24/2021 CS 612 18