SNAP RD at FNAL Gustavo Cancelo Overview SNAP

- Slides: 17

SNAP R&D at FNAL Gustavo Cancelo

Overview SNAP was conceived about four years ago at LBNL as the next step after the Supernova Cosmology Project (dark energy). SNAP will be proposed to DOE and NASA as a candidate project for the Joint Dark Energy Mission. Successful R&D could lead to a FNAL collaboration in the fabrication of flight hardware. 12/7/2020 Gustavo Cancelo 2

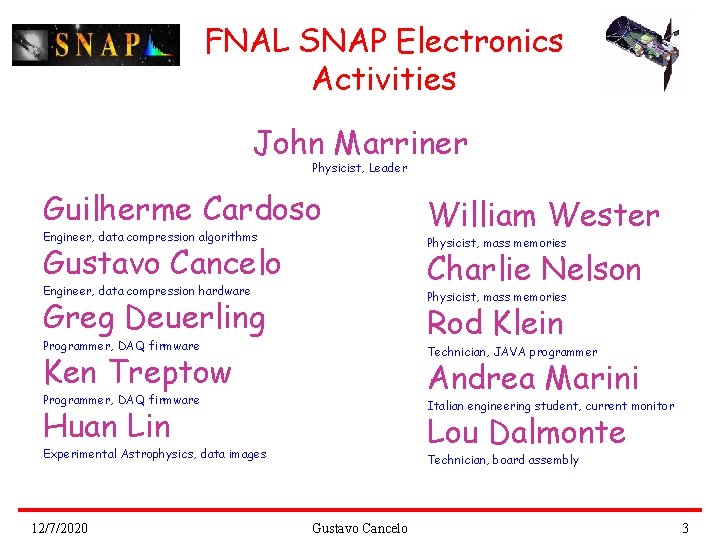

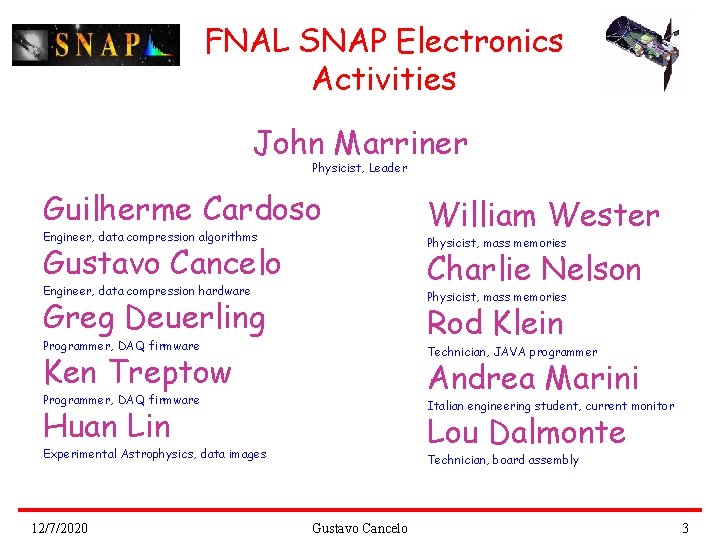

FNAL SNAP Electronics Activities John Marriner Physicist, Leader Guilherme Cardoso Engineer, data compression algorithms William Wester Gustavo Cancelo Physicist, mass memories Greg Deuerling Physicist, mass memories Ken Treptow Technician, JAVA programmer Huan Lin Italian engineering student, current monitor Charlie Nelson Engineer, data compression hardware Rod Klein Programmer, DAQ firmware Andrea Marini Programmer, DAQ firmware Lou Dalmonte Experimental Astrophysics, data images 12/7/2020 Technician, board assembly Gustavo Cancelo 3

R&D at FNAL Image Processing Solid-state recorder Mass memory storage FLASH memories are candidates due to a very high integration density and low power. Data manager hardware FPGAS are candidates due to high level of integration, flexibility and performance. Some radiation tolerant FPGAs are available. Data compression algorithms. Radiation Tests Memories and FPGAs. 12/7/2020 Gustavo Cancelo 4

Mass Memory Capacity: ~0. 5 TByte Imaging over 3 day orbit with x 2 compression Telemetry: 350 Mbit/s x 4 hrs Environmental constraints Radiation survivability (Van Allen belts) Low power and low mass to fit within budgets 12/7/2020 Gustavo Cancelo 5

Data compression Compression of data can reduce storage requirements considerably RICE algorithm adopted and part of CCSDS standard for loss-less compression Other slightly lossy algorithms LOCO Square root Wide field survey may need lossy compression 12/7/2020 Gustavo Cancelo 6

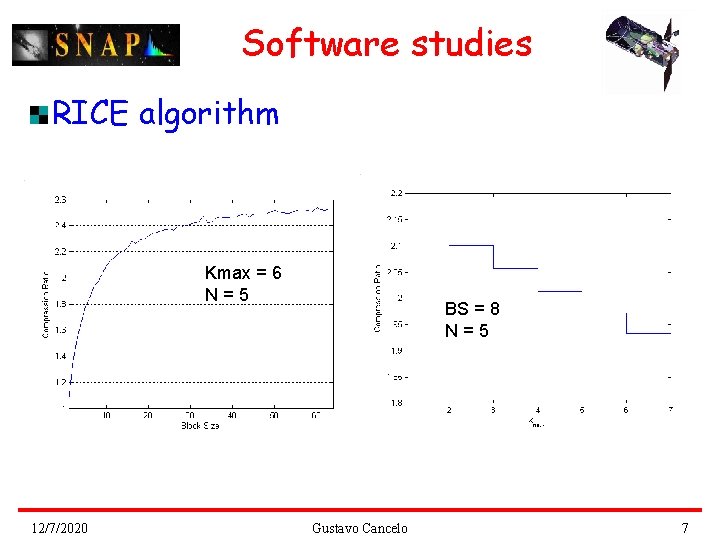

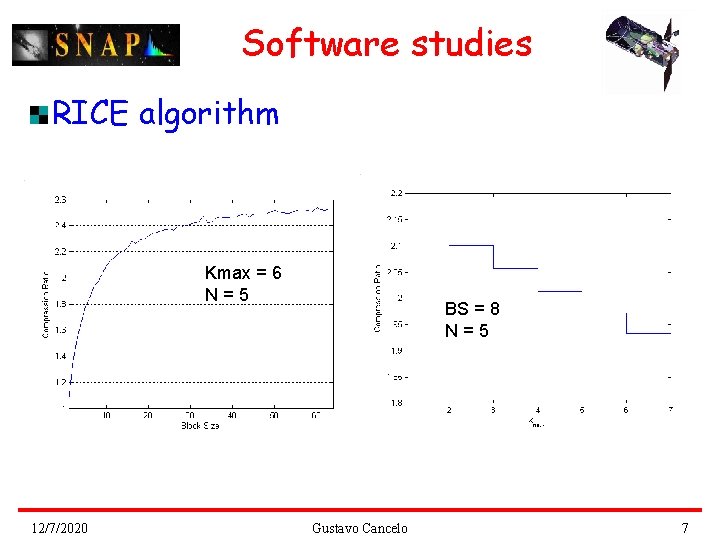

Software studies RICE algorithm Kmax = 6 N=5 12/7/2020 BS = 8 N=5 Gustavo Cancelo 7

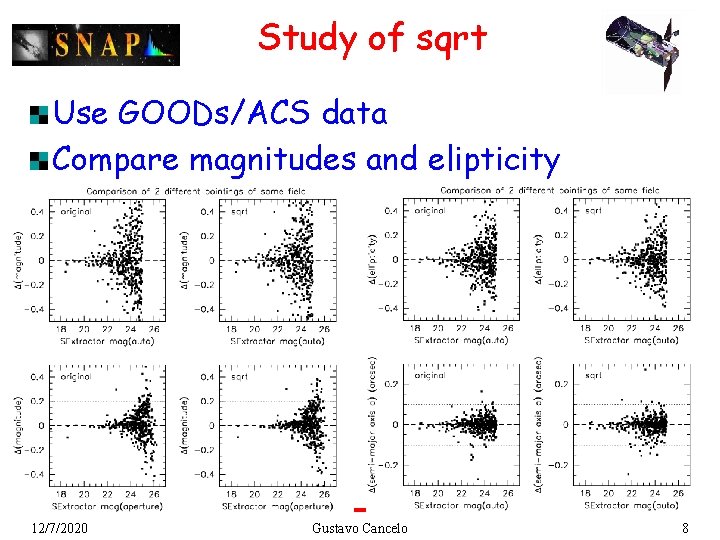

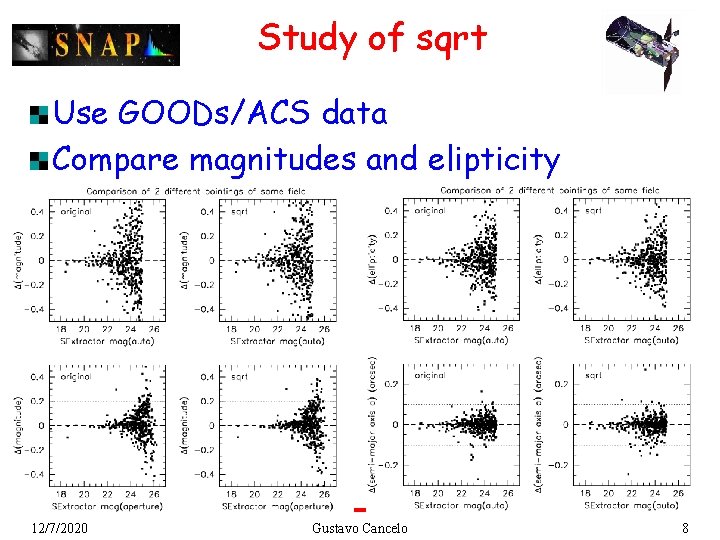

Study of sqrt Use GOODs/ACS data Compare magnitudes and elipticity 12/7/2020 Gustavo Cancelo 8

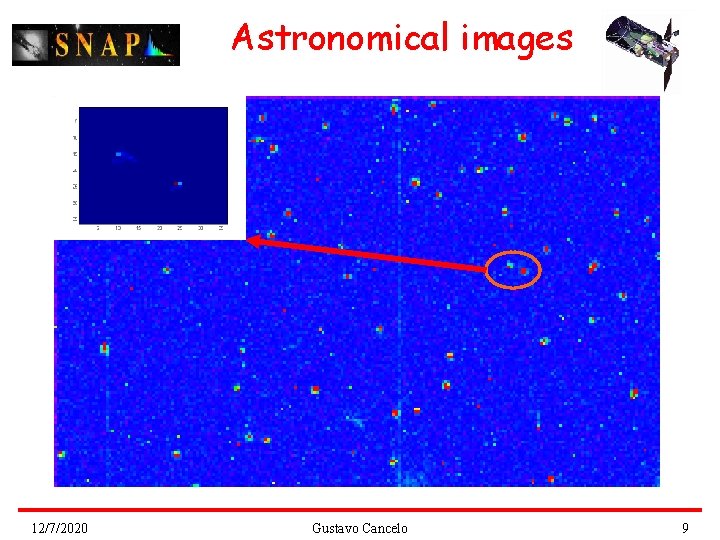

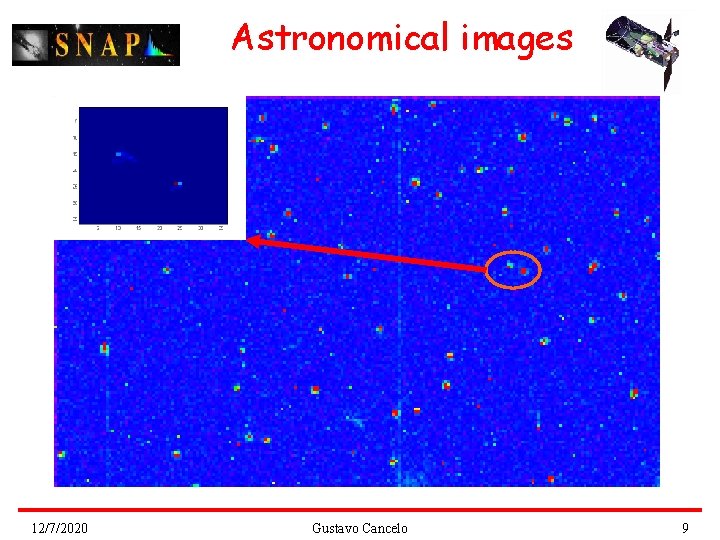

Astronomical images 12/7/2020 Gustavo Cancelo 9

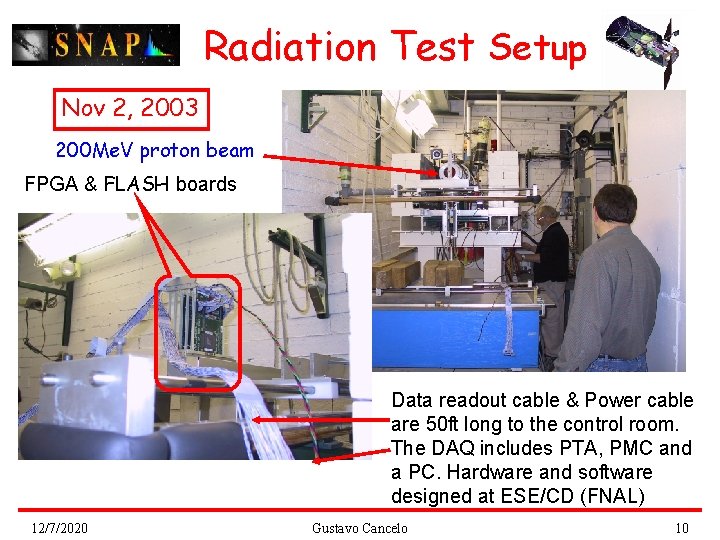

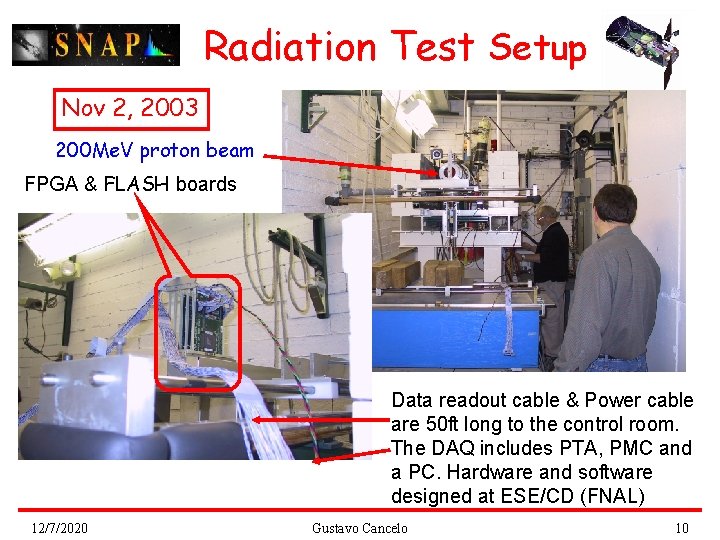

Radiation Test Setup Nov 2, 2003 200 Me. V proton beam FPGA & FLASH boards Data readout cable & Power cable are 50 ft long to the control room. The DAQ includes PTA, PMC and a PC. Hardware and software designed at ESE/CD (FNAL) 12/7/2020 Gustavo Cancelo 10

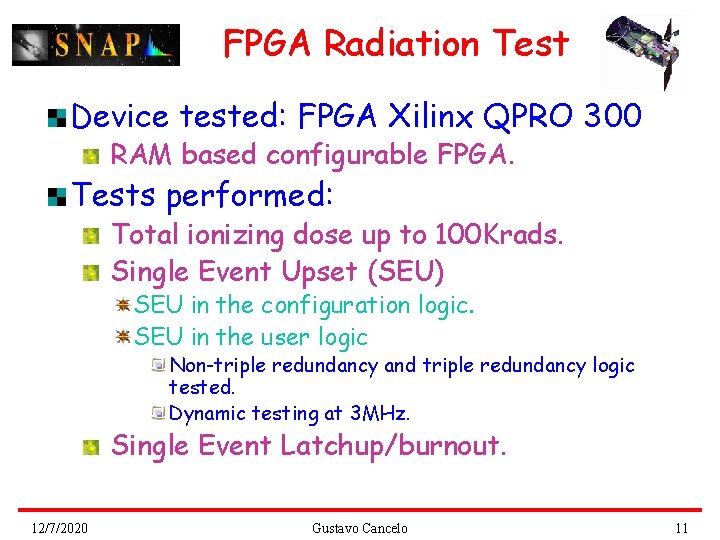

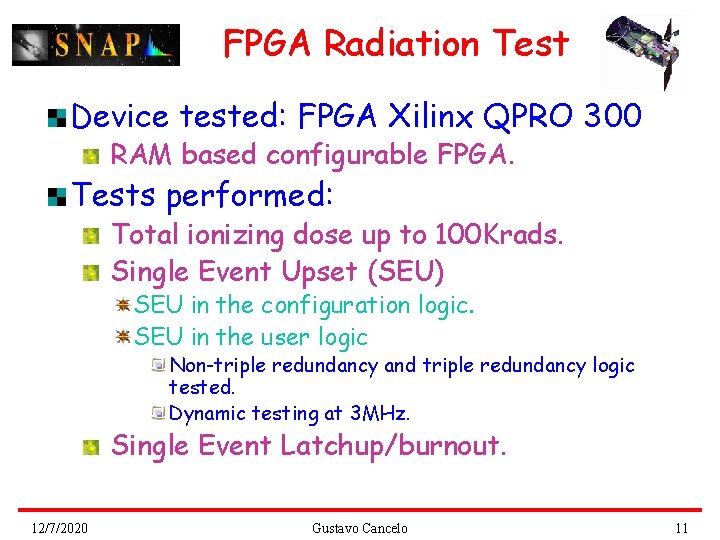

FPGA Radiation Test Device tested: FPGA Xilinx QPRO 300 RAM based configurable FPGA. Tests performed: Total ionizing dose up to 100 Krads. Single Event Upset (SEU) SEU in the configuration logic. SEU in the user logic Non-triple redundancy and triple redundancy logic tested. Dynamic testing at 3 MHz. Single Event Latchup/burnout. 12/7/2020 Gustavo Cancelo 11

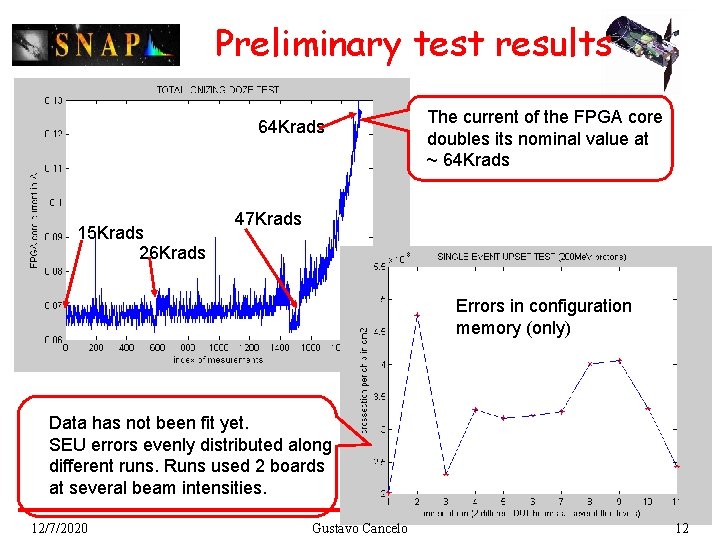

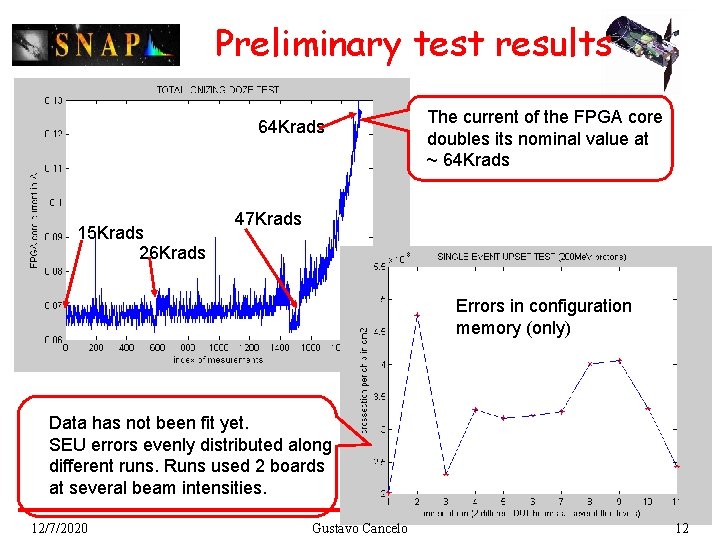

Preliminary test results 64 Krads 15 Krads 26 Krads The current of the FPGA core doubles its nominal value at ~ 64 Krads 47 Krads Errors in configuration memory (only) Data has not been fit yet. SEU errors evenly distributed along different runs. Runs used 2 boards at several beam intensities. 12/7/2020 Gustavo Cancelo 12

FLASH Irradiation study Six boards irradiated One to 70 Krad Five to 35 Krads Read, Write, Erase, RWE cycles, static Monitor currents and completion time Surprising results -> no chip failures Board to 70 Krad did fail, but recovered after a power cycle Other boards appeared fully functional Single event effects observed Total of ~350 errors – all single isolated errors Follow-up after boards are returned 12/7/2020 Gustavo Cancelo 13

Next steps Mass Memories Finish FLASH data analysis and work to study viability for space applications Investigate DRAMs and do FLASH follow-up Circulate requirements document Data compression FPGA implementation of RICE Look at LOCO algorithms Continue to work with astronomical images and space qualified programmable devices 12/7/2020 Gustavo Cancelo 14

SNAP R&D Schedule Preliminary Test report: Qtr 1 2004 Preliminary Sqrt. algorithm report: Qtr 1 2004 Preliminary LOCO algorithm report: Qtr 2 2004 Radiation Test Report: Qtr 4 2004 Zero Design Report (ZDR) FNAL contribution complete: Qtr 4 2004 Collaboration Design Report (CDR) FNAL contribution complete: Qtr 4 2006 12/7/2020 Gustavo Cancelo 15

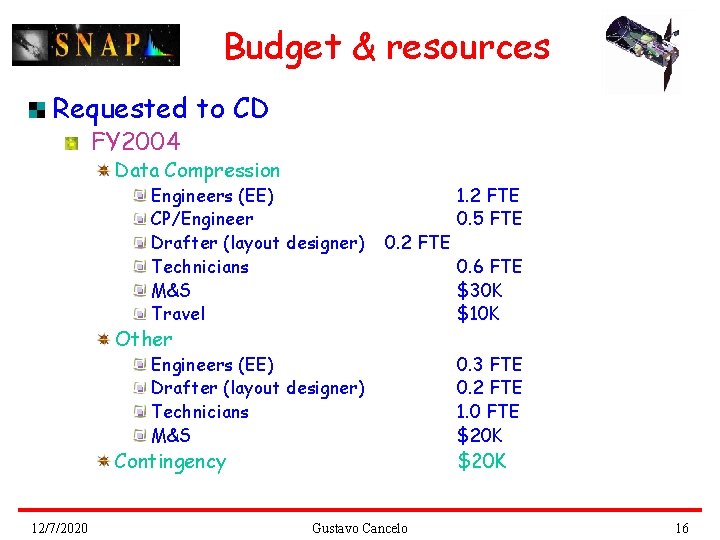

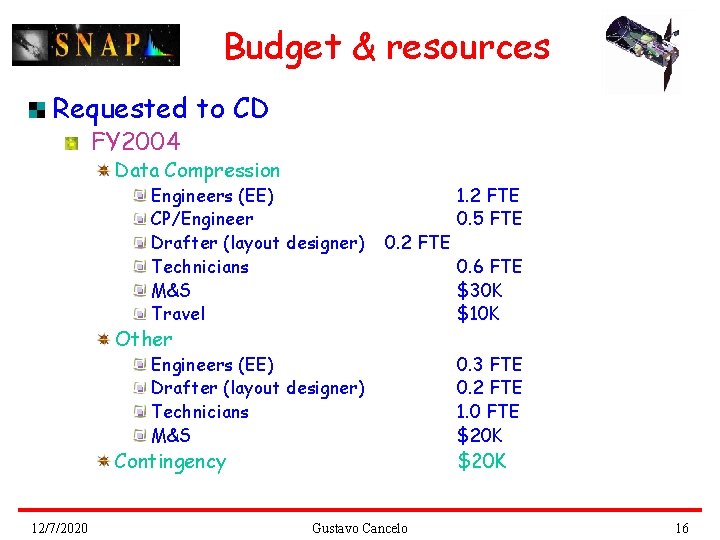

Budget & resources Requested to CD FY 2004 Data Compression Engineers (EE) CP/Engineer Drafter (layout designer) Technicians M&S Travel 0. 2 FTE Other Engineers (EE) Drafter (layout designer) Technicians M&S Contingency 12/7/2020 Gustavo Cancelo 1. 2 FTE 0. 5 FTE 0. 6 FTE $30 K $10 K 0. 3 FTE 0. 2 FTE 1. 0 FTE $20 K 16

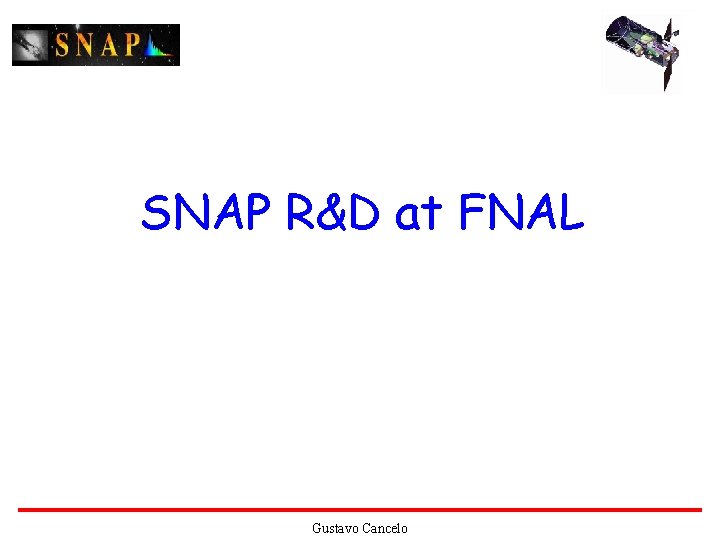

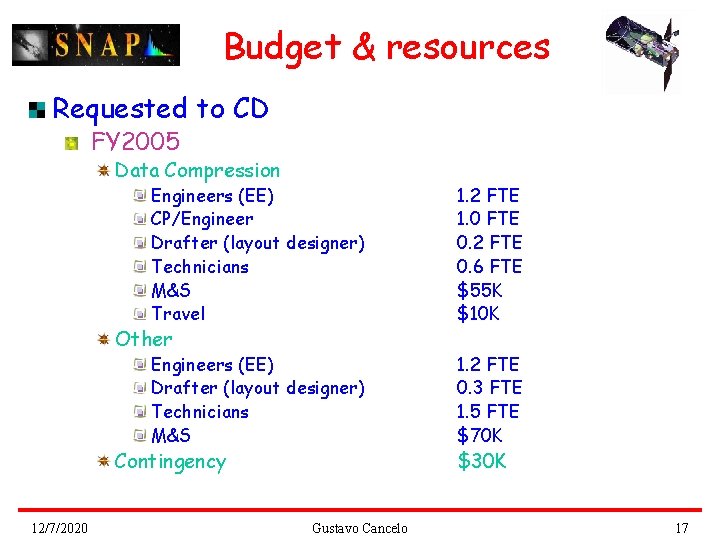

Budget & resources Requested to CD FY 2005 Data Compression Engineers (EE) CP/Engineer Drafter (layout designer) Technicians M&S Travel 1. 2 FTE 1. 0 FTE 0. 2 FTE 0. 6 FTE $55 K $10 K Engineers (EE) Drafter (layout designer) Technicians M&S 1. 2 FTE 0. 3 FTE 1. 5 FTE $70 K Other Contingency 12/7/2020 Gustavo Cancelo $30 K 17