Smarter Vision Platform Update Copyright 2013 Xilinx Agenda

- Slides: 55

Smarter Vision Platform Update © Copyright 2013 Xilinx.

Agenda Hardware Platforms SDI on 7 -Series Video over IP Video Processing Codecs Page 2 . © Copyright 2013 Xilinx.

Smarter Xilinx Smarter Vision Hardware Platforms Vision Page 3 . © Copyright 2013 Xilinx.

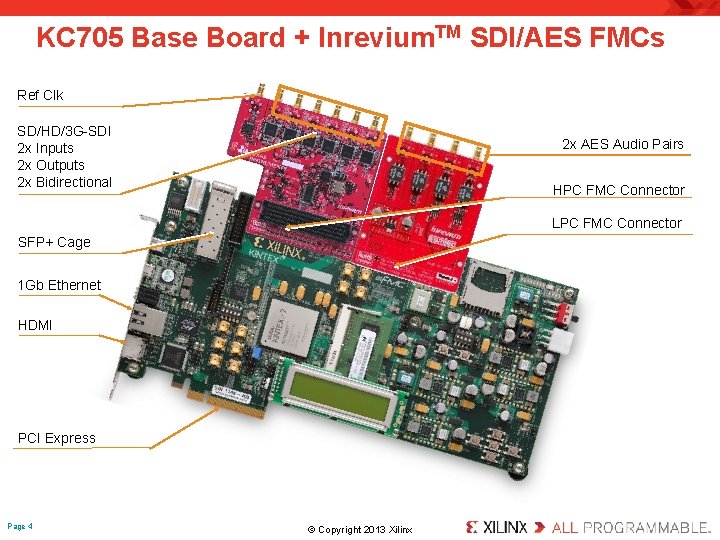

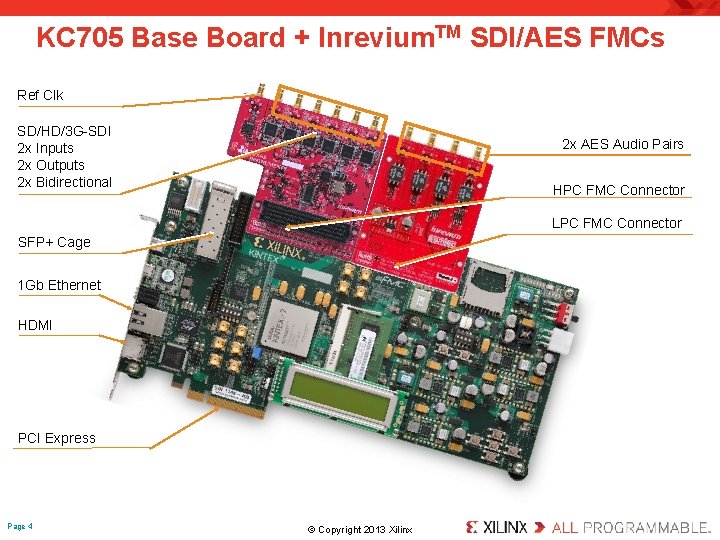

KC 705 Base Board + Inrevium. TM SDI/AES FMCs Ref Clk SD/HD/3 G-SDI 2 x Inputs 2 x Outputs 2 x Bidirectional 2 x AES Audio Pairs HPC FMC Connector LPC FMC Connector SFP+ Cage 1 Gb Ethernet HDMI PCI Express Page 4 . © Copyright 2013 Xilinx.

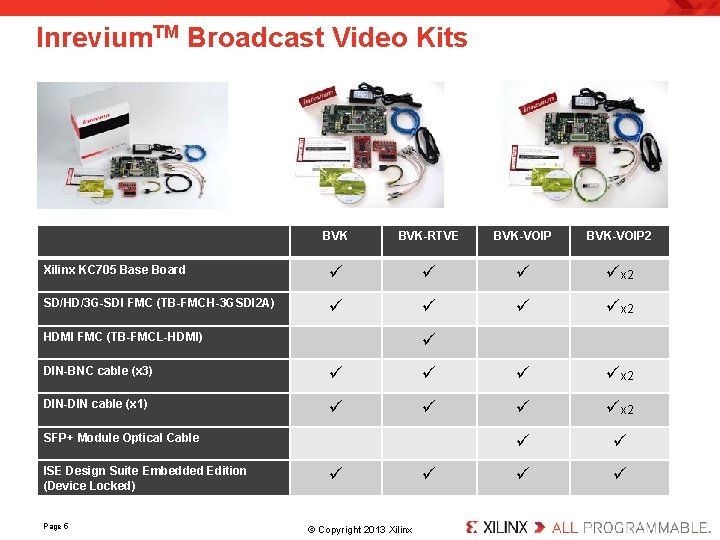

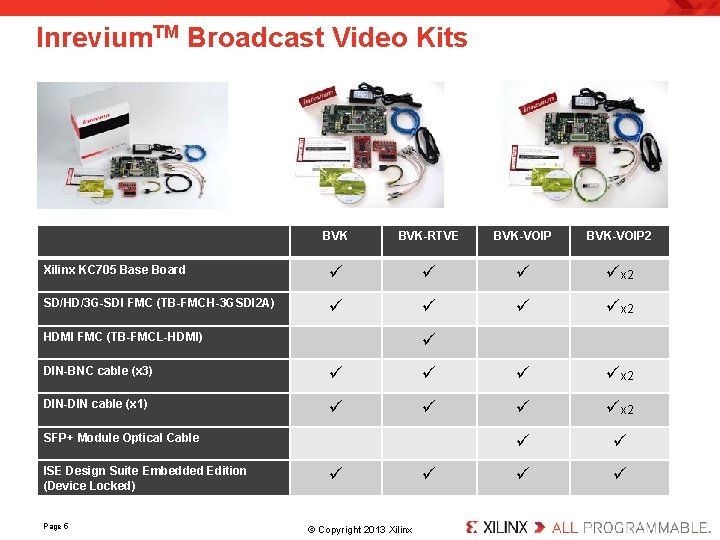

Inrevium. TM Broadcast Video Kits BVK-RTVE BVK-VOIP 2 Xilinx KC 705 Base Board x 2 SD/HD/3 G-SDI FMC (TB-FMCH-3 GSDI 2 A) x 2 HDMI FMC (TB-FMCL-HDMI) DIN-BNC cable (x 3) x 2 DIN-DIN cable (x 1) x 2 SFP+ Module Optical Cable ISE Design Suite Embedded Edition (Device Locked) Page 5 . © Copyright 2013 Xilinx.

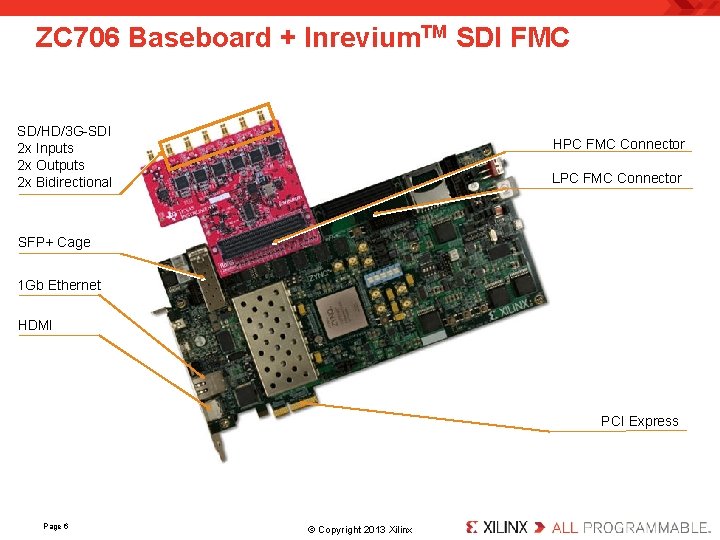

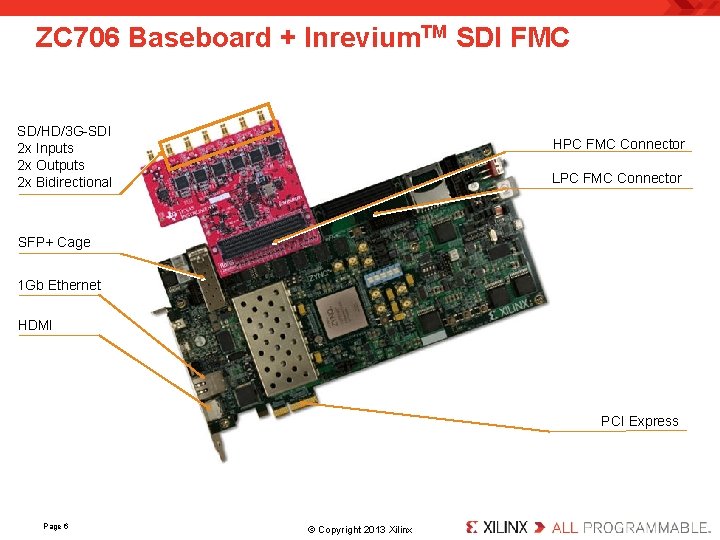

ZC 706 Baseboard + Inrevium. TM SDI FMC SD/HD/3 G-SDI 2 x Inputs 2 x Outputs 2 x Bidirectional HPC FMC Connector LPC FMC Connector SFP+ Cage 1 Gb Ethernet HDMI PCI Express Page 6 . © Copyright 2013 Xilinx.

Omni. Tek Zynq-7045 So. C Video Development Kit Broadcast-centric development platform. © Copyright 2013 Xilinx.

Inrevium. TM ACDC 1. 0 Kintex-7 Broadcast & Consumer Kit ACDC = Acquisition, Contribution, Distribution, Consumption Page 8 . © Copyright 2013 Xilinx.

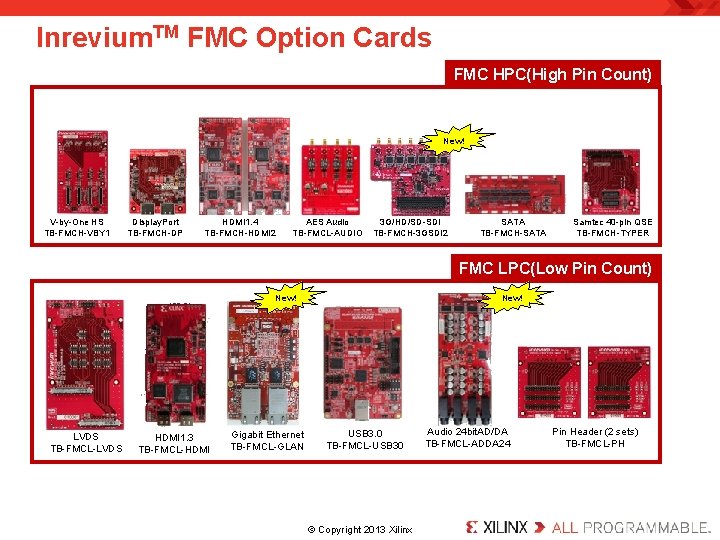

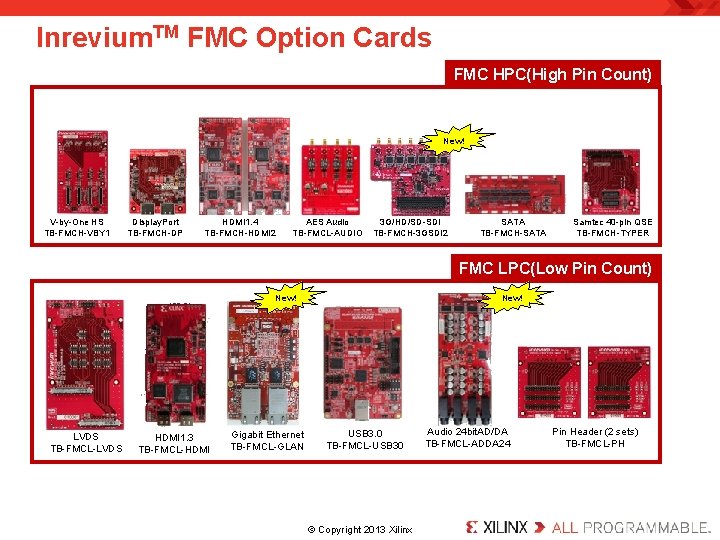

Inrevium. TM FMC Option Cards FMC HPC(High Pin Count) New! V-by-One HS TB-FMCH-VBY 1 Display. Port TB-FMCH-DP HDMI 1. 4 TB-FMCH-HDMI 2 AES Audio TB-FMCL-AUDIO 3 G/HD/SD-SDI TB-FMCH-3 GSDI 2 SATA TB-FMCH-SATA Samtec 40 -pin QSE TB-FMCH-TYPER FMC LPC(Low Pin Count) New! LVDS TB-FMCL-LVDS HDMI 1. 3 TB-FMCL-HDMI Gigabit Ethernet TB-FMCL-GLAN New! USB 3. 0 TB-FMCL-USB 30 . © Copyright 2013 Xilinx. Audio 24 bit. AD/DA TB-FMCL-ADDA 24 Pin Header (2 sets) TB-FMCL-PH

Smarter Xilinx Smarter Vision SDI on 7 -Series Vision Page 10 . © Copyright 2013 Xilinx.

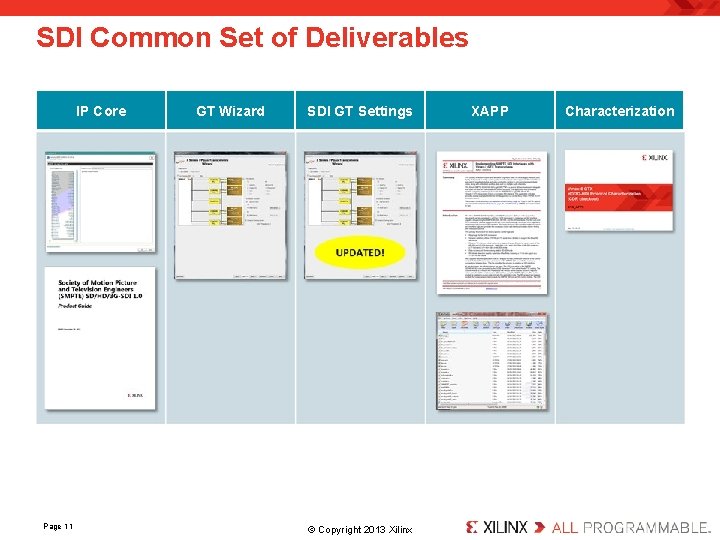

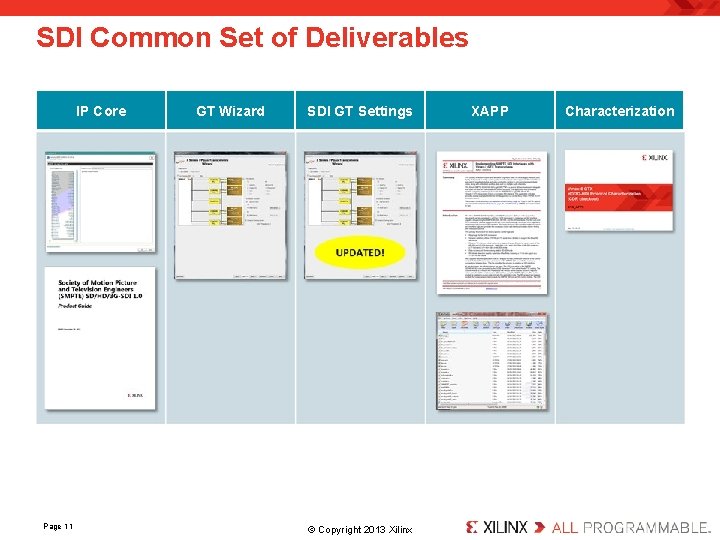

SDI Common Set of Deliverables IP Core Page 11 GT Wizard SDI GT Settings . © Copyright 2013 Xilinx. XAPP Characterization

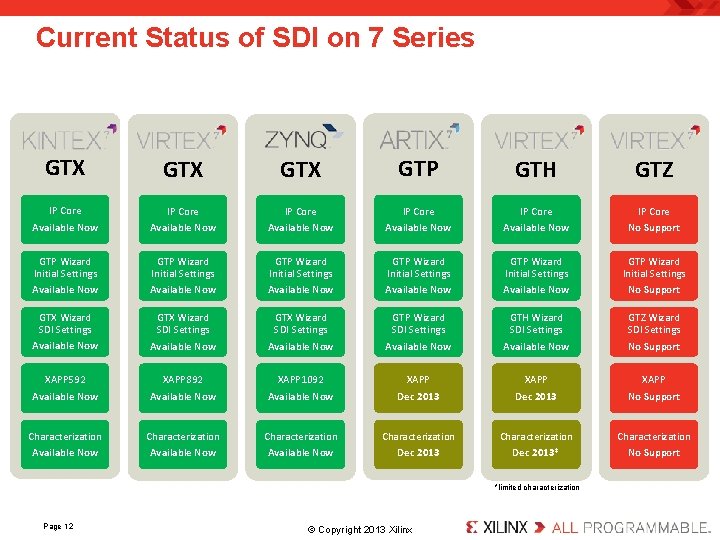

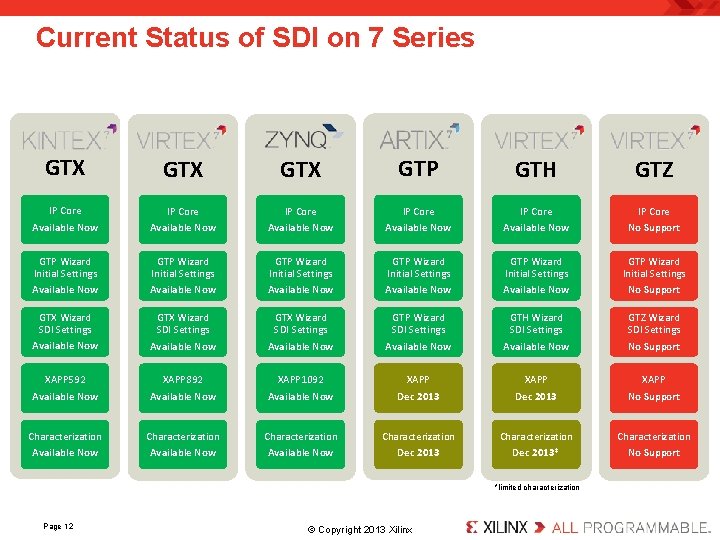

Current Status of SDI on 7 Series GTX GTX GTP GTH GTZ IP Core Available Now IP Core Available Now IP Core No Support GTP Wizard Initial Settings Available Now GTP Wizard Initial Settings Available Now GTP Wizard Initial Settings No Support GTX Wizard SDI Settings Available Now GTP Wizard SDI Settings Available Now GTH Wizard SDI Settings Available Now GTZ Wizard SDI Settings No Support XAPP 592 Available Now XAPP 892 Available Now XAPP 1092 Available Now XAPP Dec 2013 XAPP No Support Characterization Available Now Characterization Dec 2013* Characterization No Support *limited characterization Page 12 . © Copyright 2013 Xilinx.

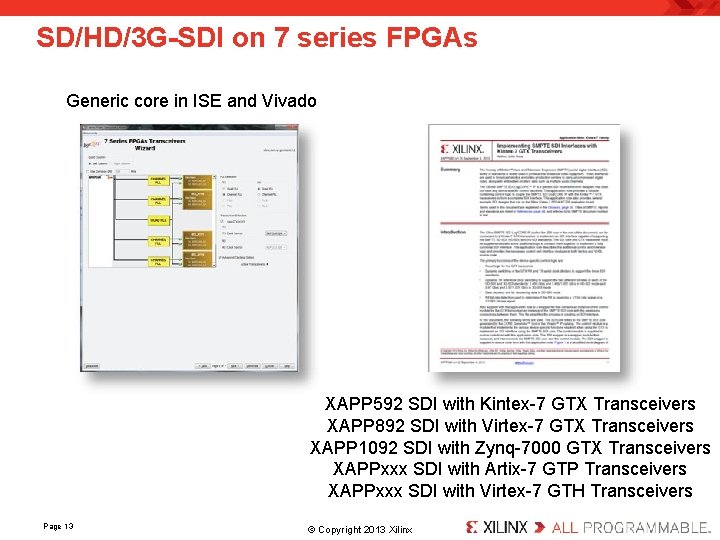

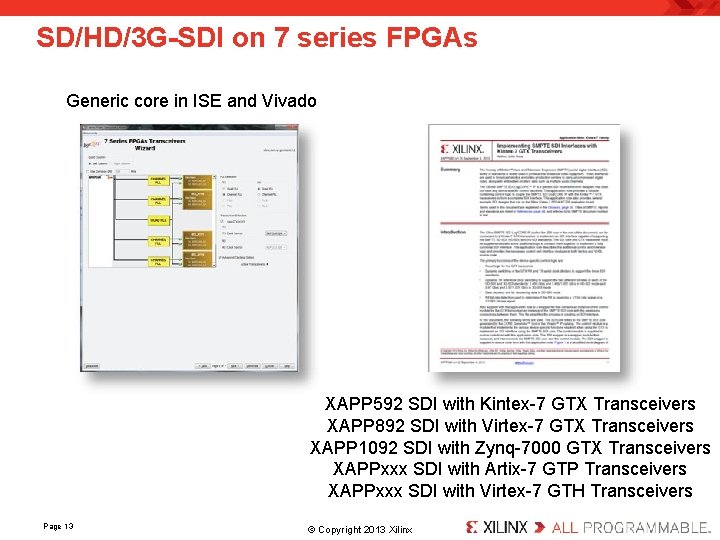

SD/HD/3 G-SDI on 7 series FPGAs Generic core in ISE and Vivado XAPP 592 SDI with Kintex-7 GTX Transceivers XAPP 892 SDI with Virtex-7 GTX Transceivers XAPP 1092 SDI with Zynq-7000 GTX Transceivers XAPPxxx SDI with Artix-7 GTP Transceivers XAPPxxx SDI with Virtex-7 GTH Transceivers Page 13 . © Copyright 2013 Xilinx.

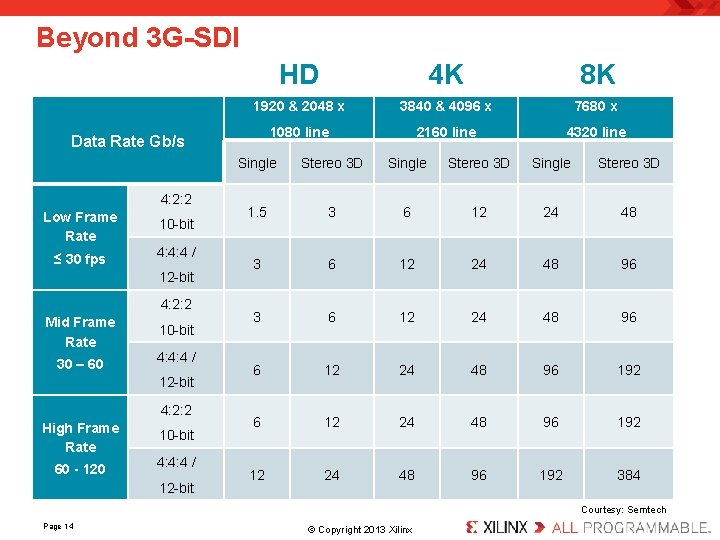

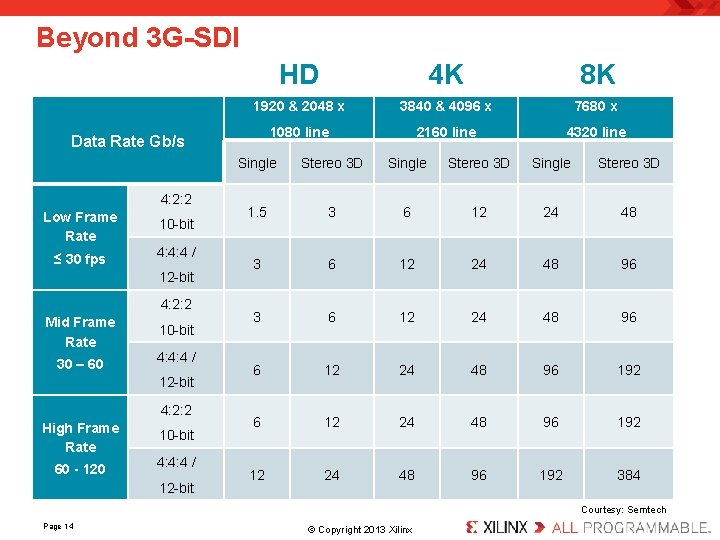

Beyond 3 G-SDI HD 4 K 8 K 1920 & 2048 x 3840 & 4096 x 7680 x 1080 line 2160 line 4320 line Data Rate Gb/s 4: 2: 2 Low Frame Rate ≤ 30 fps 10 -bit 4: 4: 4 / 12 -bit 4: 2: 2 Mid Frame Rate 30 – 60 10 -bit 4: 4: 4 / 12 -bit 4: 2: 2 High Frame Rate 60 - 120 10 -bit 4: 4: 4 / 12 -bit Single Stereo 3 D 1. 5 3 6 12 24 48 96 192 6 12 24 48 96 192 384 Courtesy: Semtech Page 14 . © Copyright 2013 Xilinx.

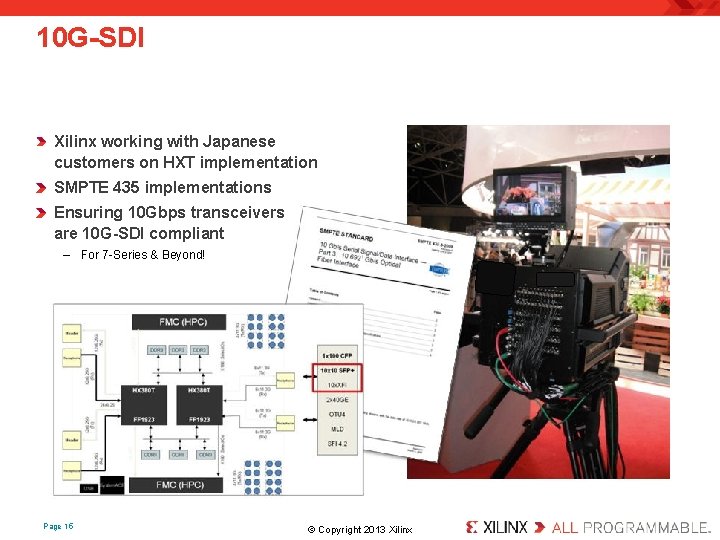

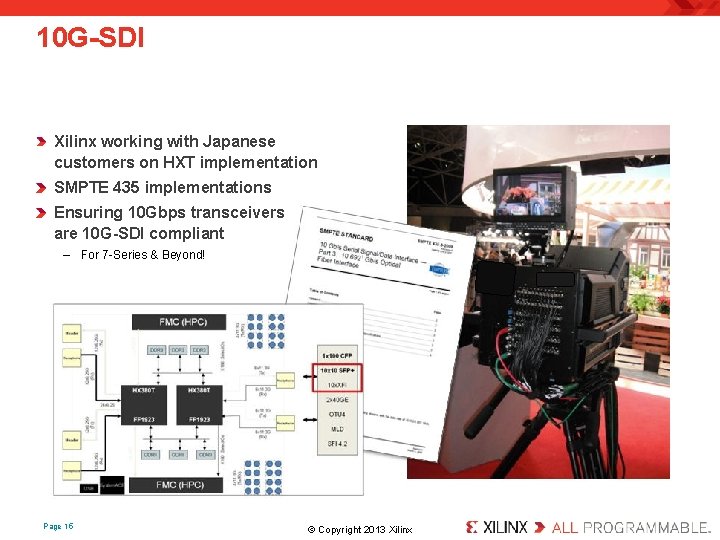

10 G-SDI Xilinx working with Japanese customers on HXT implementation SMPTE 435 implementations Ensuring 10 Gbps transceivers are 10 G-SDI compliant – For 7 -Series & Beyond! Page 15 . © Copyright 2013 Xilinx.

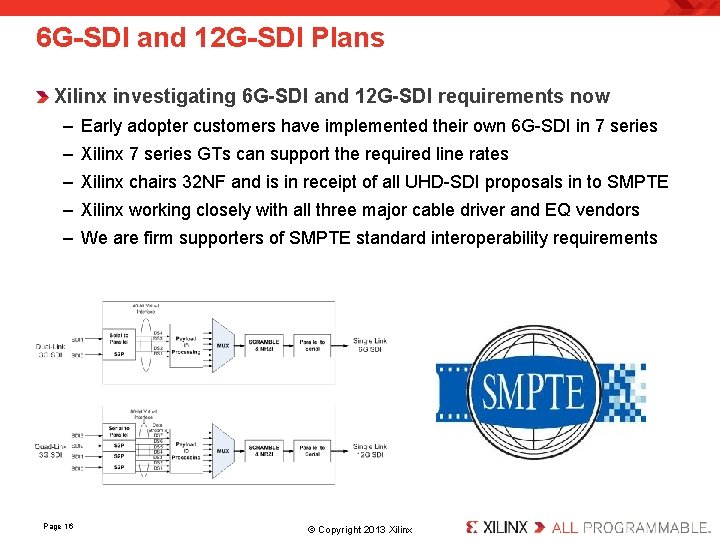

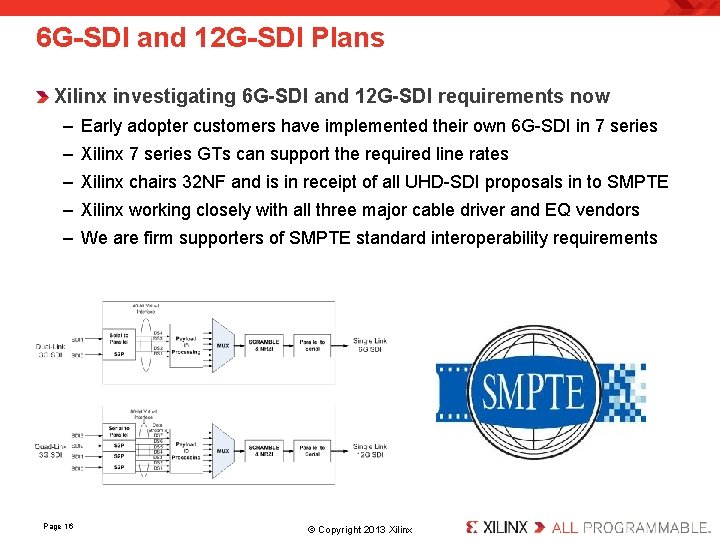

6 G-SDI and 12 G-SDI Plans Xilinx investigating 6 G-SDI and 12 G-SDI requirements now – Early adopter customers have implemented their own 6 G-SDI in 7 series – Xilinx 7 series GTs can support the required line rates – Xilinx chairs 32 NF and is in receipt of all UHD-SDI proposals in to SMPTE – Xilinx working closely with all three major cable driver and EQ vendors – We are firm supporters of SMPTE standard interoperability requirements Page 16 . © Copyright 2013 Xilinx.

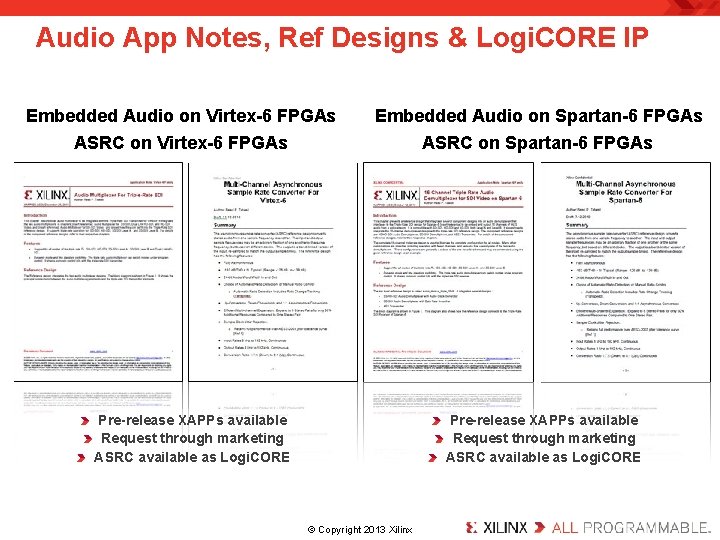

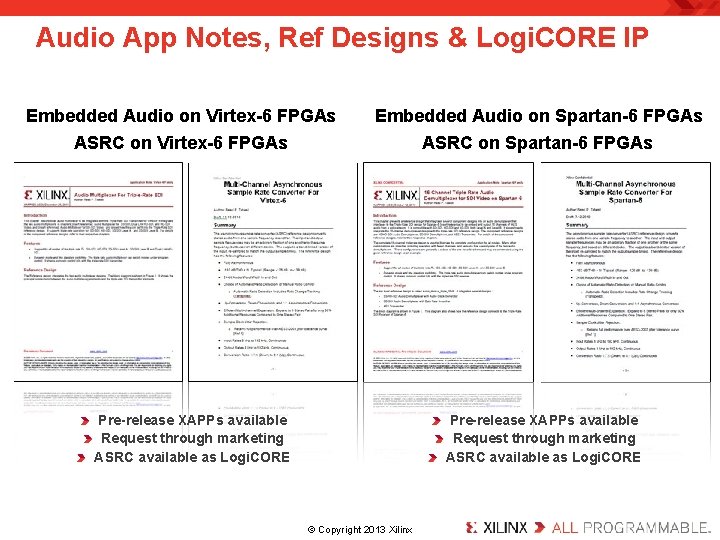

Audio App Notes, Ref Designs & Logi. CORE IP Embedded Audio on Virtex-6 FPGAs ASRC on Virtex-6 FPGAs Embedded Audio on Spartan-6 FPGAs ASRC on Spartan-6 FPGAs Pre-release XAPPs available Request through marketing ASRC available as Logi. CORE . © Copyright 2013 Xilinx.

Smarter Vision Video over IP Vision Page 18 . © Copyright 2013 Xilinx.

IEEE AVB and SMPTE 2022 Example Network Use Case AVB Network SMPTE 2022 Cameras, Switcher, Digital Signage (in stadium or studio) SMPTE 2022 Network IEEE AVB to SMPTE 2022 Bridge To OB van, studio or remote production suite on private 1 Gb or 10 Gb IP network Page 19 . © Copyright 2013 Xilinx.

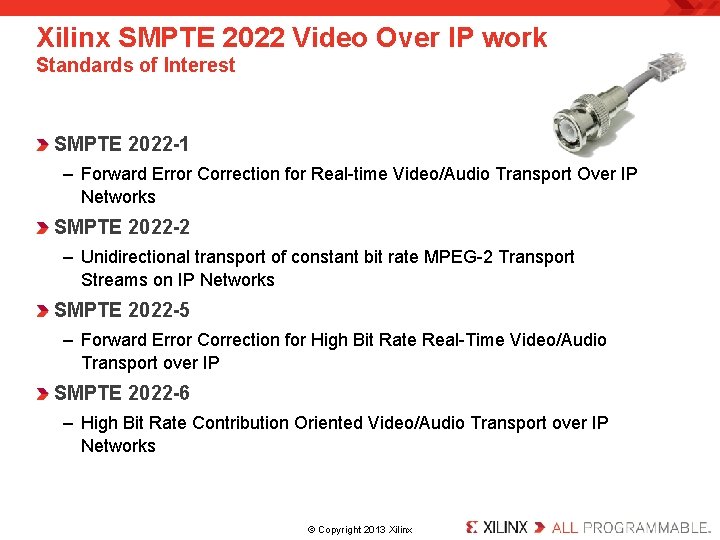

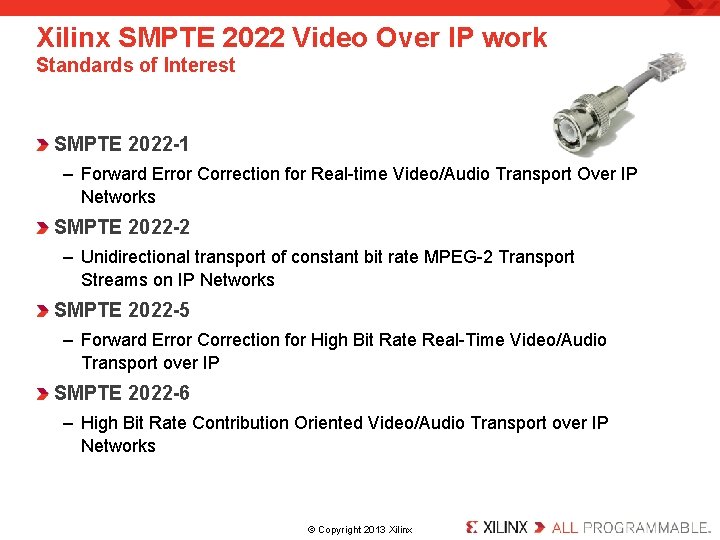

Xilinx SMPTE 2022 Video Over IP work Standards of Interest SMPTE 2022 -1 – Forward Error Correction for Real-time Video/Audio Transport Over IP Networks SMPTE 2022 -2 – Unidirectional transport of constant bit rate MPEG-2 Transport Streams on IP Networks SMPTE 2022 -5 – Forward Error Correction for High Bit Rate Real-Time Video/Audio Transport over IP SMPTE 2022 -6 – High Bit Rate Contribution Oriented Video/Audio Transport over IP Networks . © Copyright 2013 Xilinx.

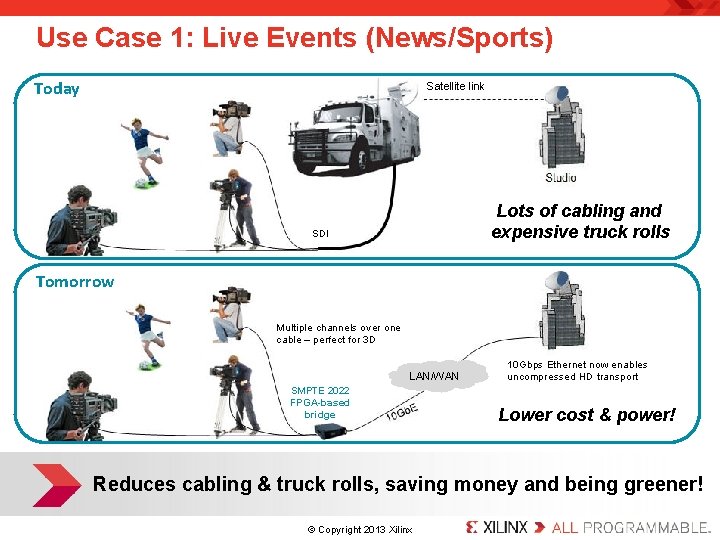

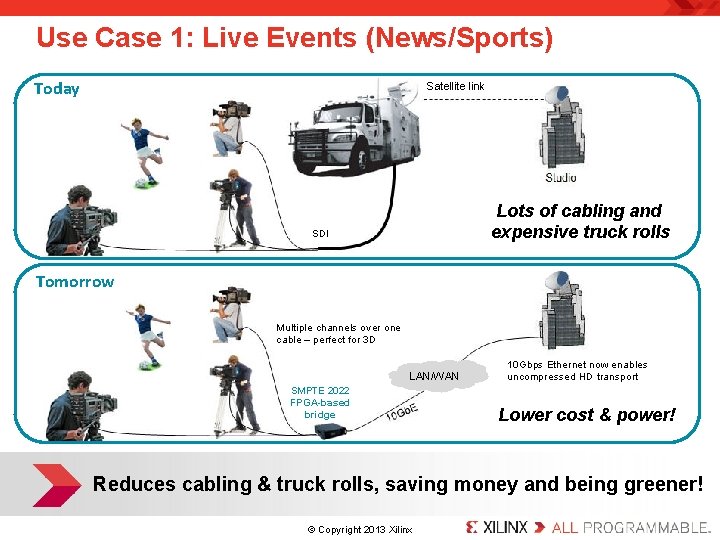

Use Case 1: Live Events (News/Sports) Today Satellite link Lots of cabling and expensive truck rolls SDI Tomorrow Multiple channels over one cable – perfect for 3 D LAN/WAN SMPTE 2022 FPGA-based bridge 10 Gbps Ethernet now enables uncompressed HD transport Lower cost & power! Reduces cabling & truck rolls, saving money and being greener!. © Copyright 2013 Xilinx.

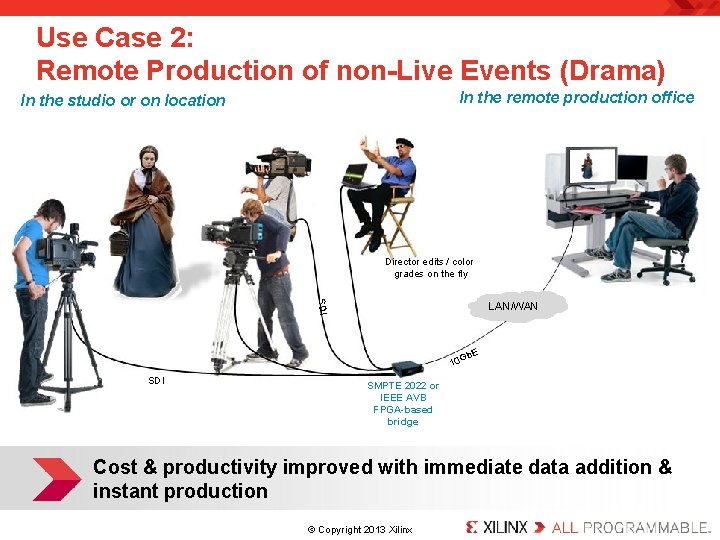

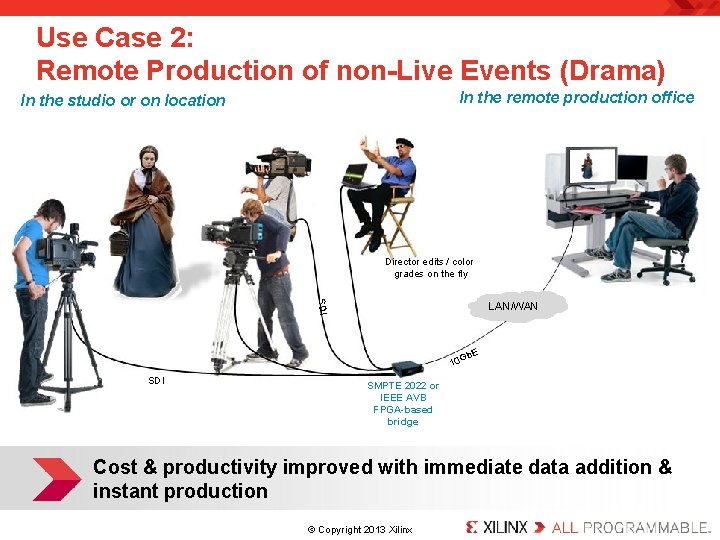

Use Case 2: Remote Production of non-Live Events (Drama) In the remote production office In the studio or on location Director edits / color grades on the fly SDI LAN/WAN E b 10 G SDI SMPTE 2022 or IEEE AVB FPGA-based bridge Cost & productivity improved with immediate data addition & instant production. © Copyright 2013 Xilinx.

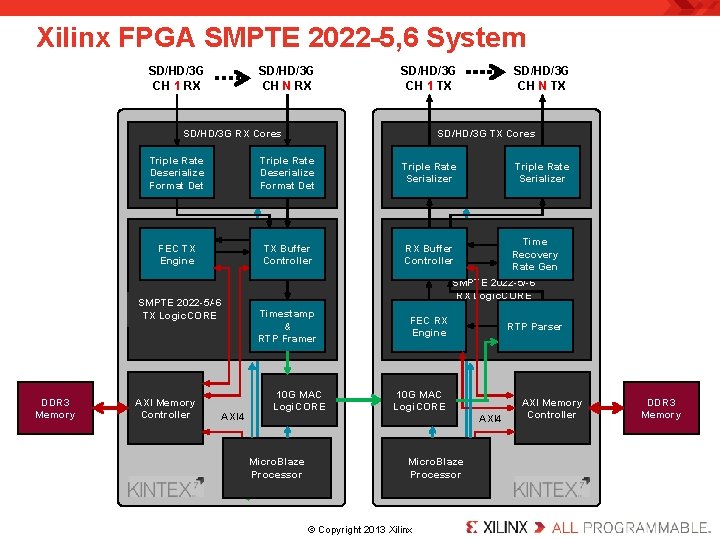

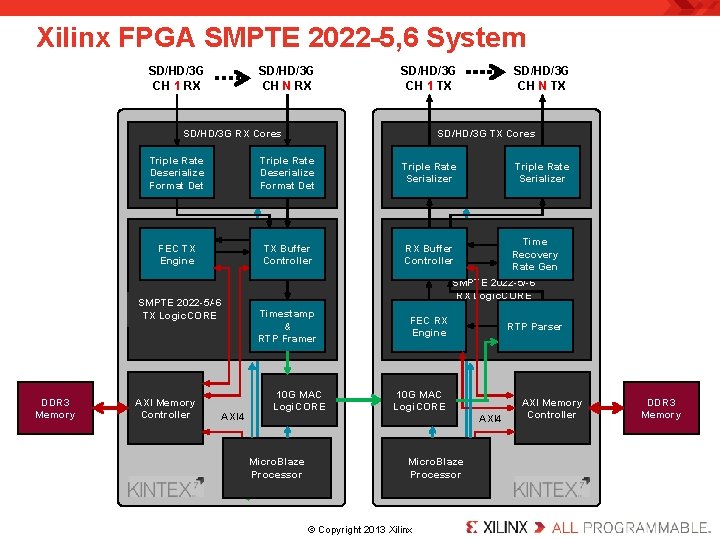

Xilinx FPGA SMPTE 2022 -5, 6 System SD/HD/3 G CH 1 RX SD/HD/3 G CH N RX SD/HD/3 G CH 1 TX SD/HD/3 G RX Cores DDR 3 Memory SD/HD/3 G TX Cores Triple Rate Deserialize Format Det Triple Rate Serializer FEC TX Engine TX Buffer Controller RX Buffer Controller Timestamp & RTP Framer FEC RX Engine SMPTE 2022 -5/-6 TX Logic. CORE AXI Memory Controller AXI 4 SD/HD/3 G CH N TX Triple Rate Serializer Time Recovery Rate Gen SMPTE 2022 -5/-6 RX Logic. CORE 10 G MAC Logi. CORE RTP Parser 10 G MAC Logi. CORE AXI 4 Micro. Blaze Processor . © Copyright 2013 Xilinx. AXI Memory Controller DDR 3 Memory

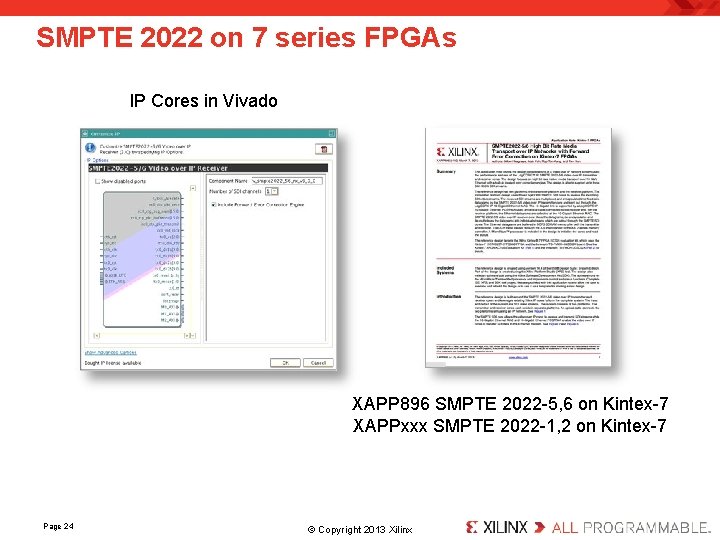

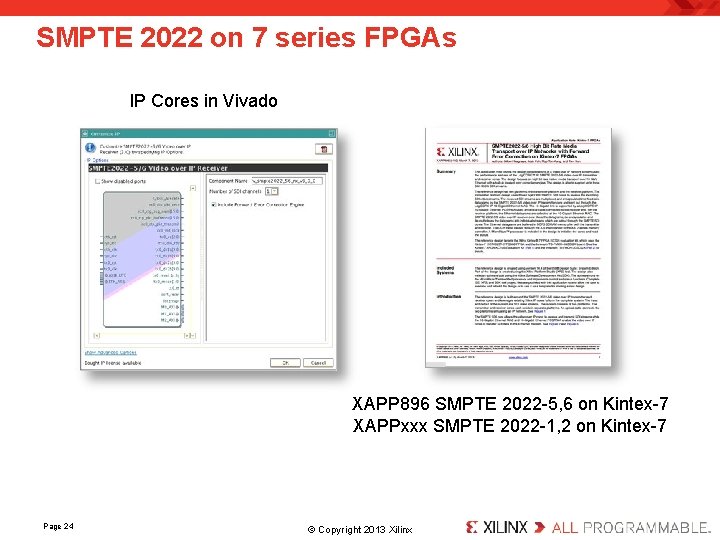

SMPTE 2022 on 7 series FPGAs IP Cores in Vivado XAPP 896 SMPTE 2022 -5, 6 on Kintex-7 XAPPxxx SMPTE 2022 -1, 2 on Kintex-7 Page 24 . © Copyright 2013 Xilinx.

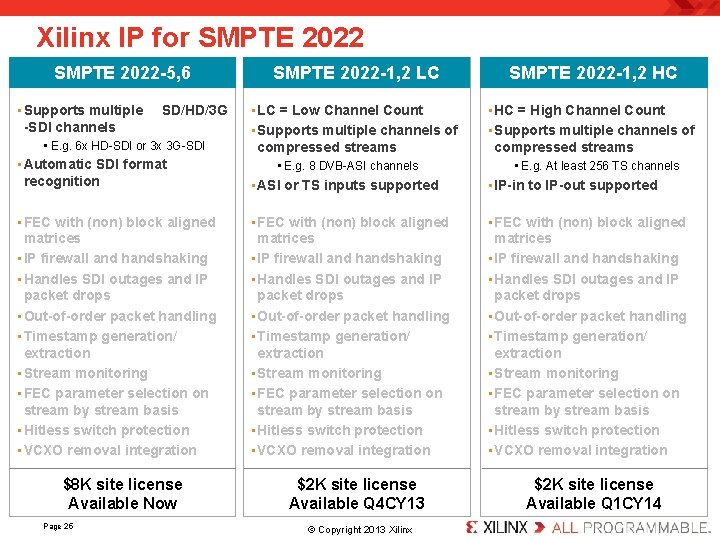

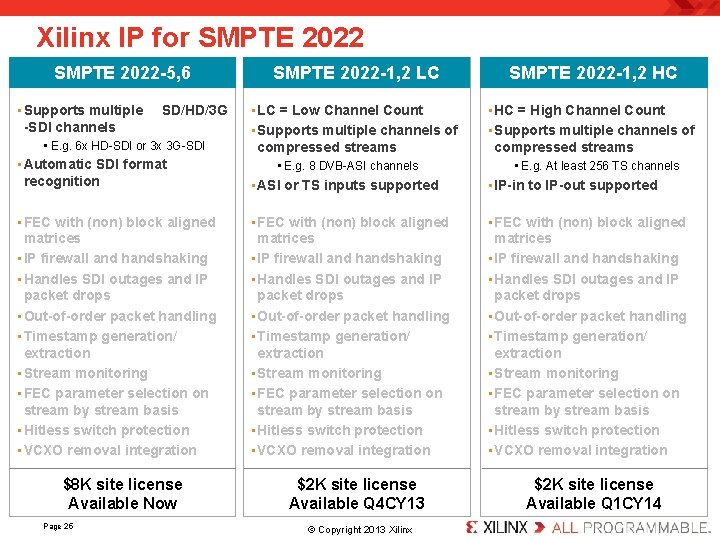

Xilinx IP for SMPTE 2022 -5, 6 • Supports multiple SD/HD/3 G -SDI channels • E. g. 6 x HD-SDI or 3 x 3 G-SDI • Automatic SDI format recognition • FEC with (non) block aligned matrices • IP firewall and handshaking • Handles SDI outages and IP packet drops • Out-of-order packet handling • Timestamp generation/ extraction • Stream monitoring • FEC parameter selection on stream by stream basis • Hitless switch protection • VCXO removal integration $8 K site license Available Now Page 25 SMPTE 2022 -1, 2 LC SMPTE 2022 -1, 2 HC • LC = Low Channel Count • HC = High Channel Count • Supports multiple channels of compressed streams • E. g. 8 DVB-ASI channels compressed streams • E. g. At least 256 TS channels • ASI or TS inputs supported • IP-in to IP-out supported . • FEC with (non) block aligned matrices • IP firewall and handshaking • Handles SDI outages and IP packet drops • Out-of-order packet handling • Timestamp generation/ extraction • Stream monitoring • FEC parameter selection on stream by stream basis • Hitless switch protection • VCXO removal integration $2 K site license Available Q 4 CY 13. © Copyright 2013 Xilinx. $2 K site license Available Q 1 CY 14

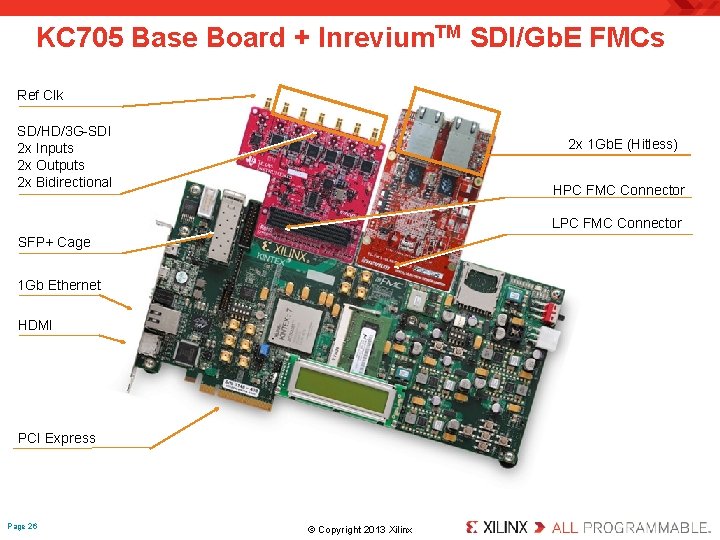

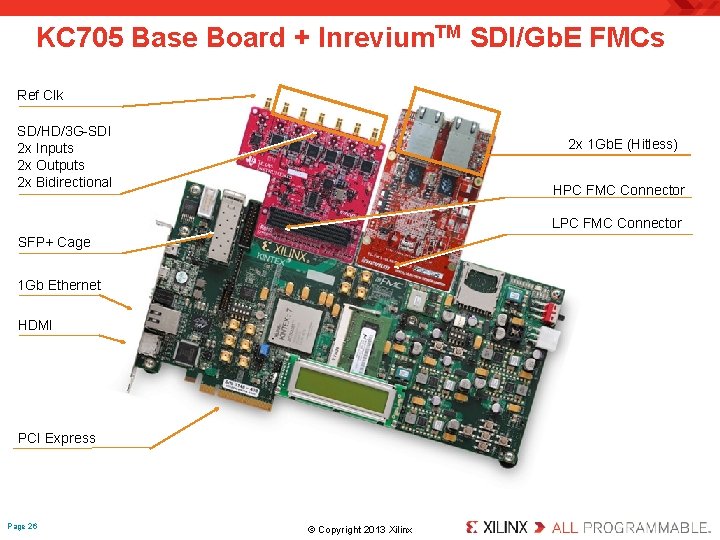

KC 705 Base Board + Inrevium. TM SDI/Gb. E FMCs Ref Clk SD/HD/3 G-SDI 2 x Inputs 2 x Outputs 2 x Bidirectional 2 x 1 Gb. E (Hitless) HPC FMC Connector LPC FMC Connector SFP+ Cage 1 Gb Ethernet HDMI PCI Express Page 26 . © Copyright 2013 Xilinx.

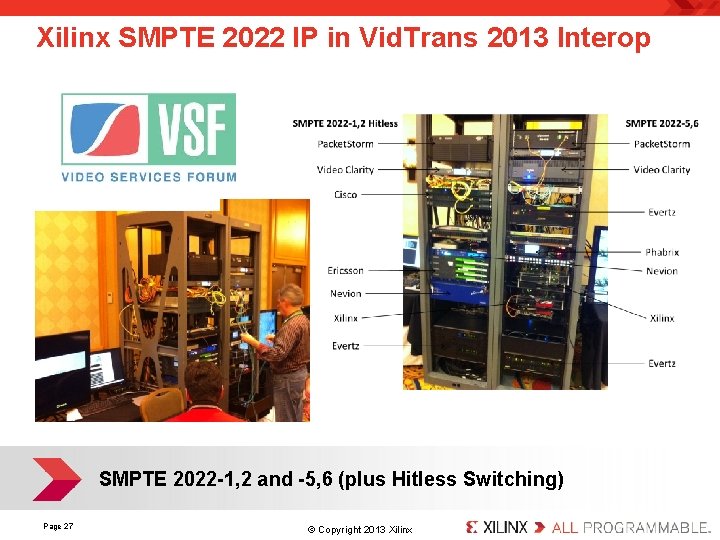

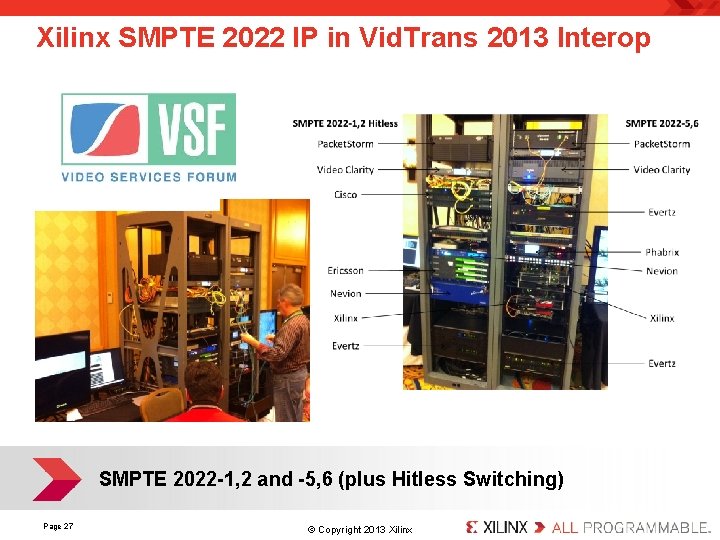

Xilinx SMPTE 2022 IP in Vid. Trans 2013 Interop SMPTE 2022 -1, 2 and -5, 6 (plus Hitless Switching) Page 27 . © Copyright 2013 Xilinx.

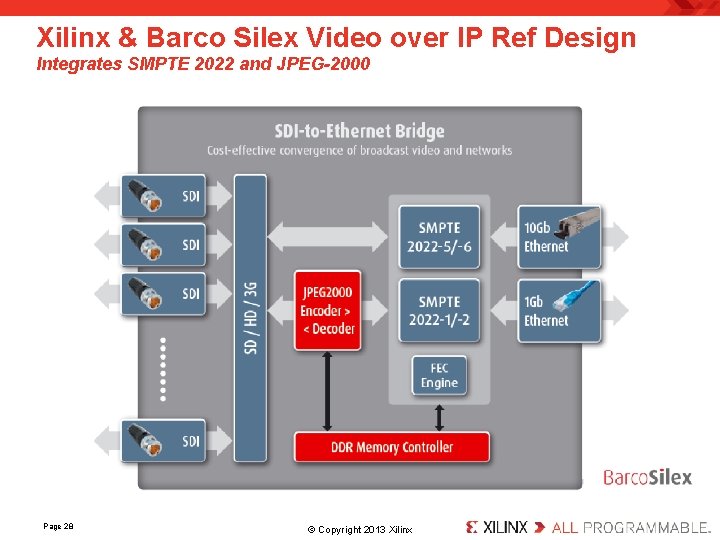

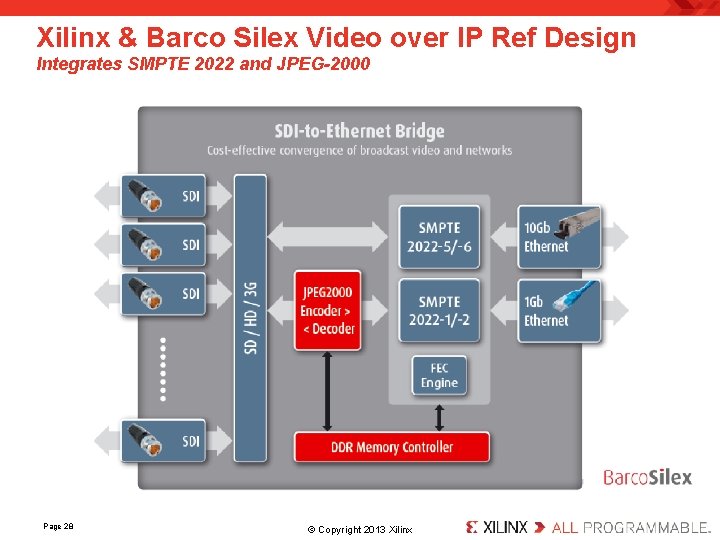

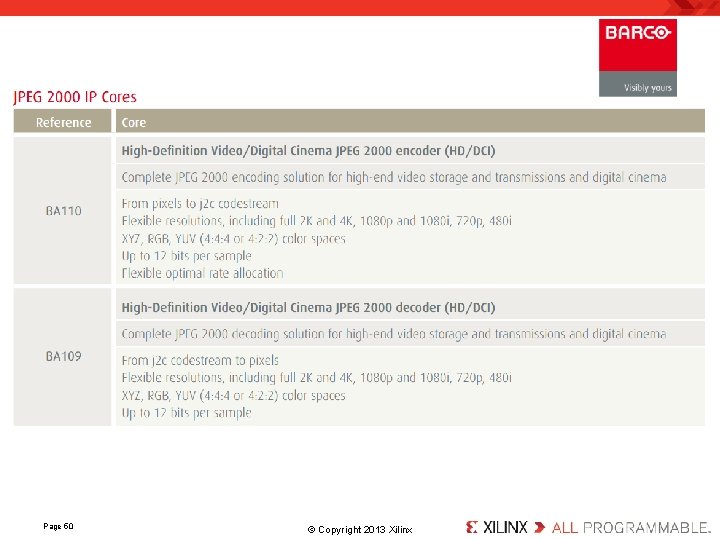

Xilinx & Barco Silex Video over IP Ref Design Integrates SMPTE 2022 and JPEG-2000 Page 28 . © Copyright 2013 Xilinx.

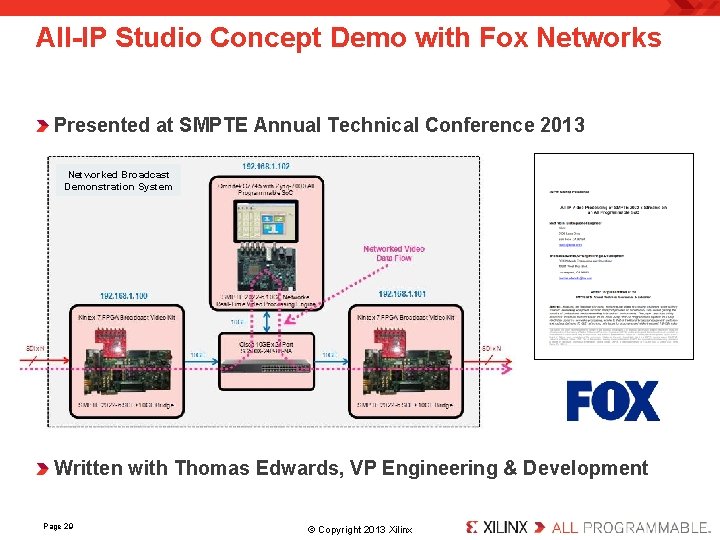

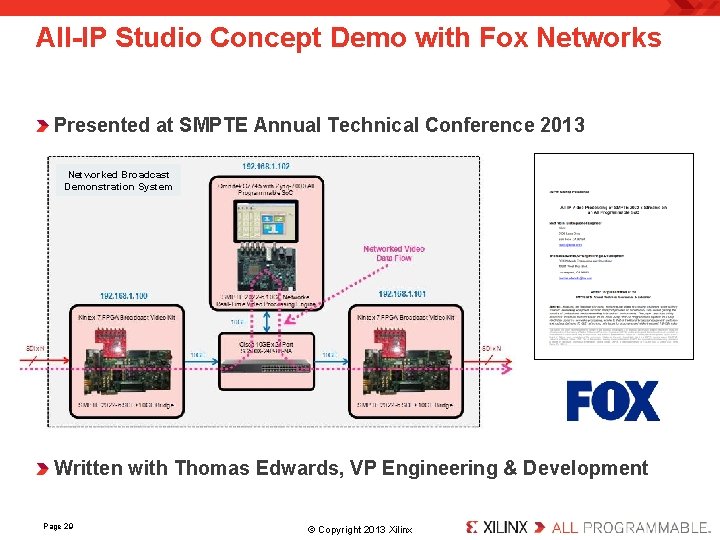

All-IP Studio Concept Demo with Fox Networks Presented at SMPTE Annual Technical Conference 2013 Networked Broadcast Demonstration System Written with Thomas Edwards, VP Engineering & Development Page 29 . © Copyright 2013 Xilinx.

Smarter Vision Video Processing Vision Page 30 . © Copyright 2013 Xilinx.

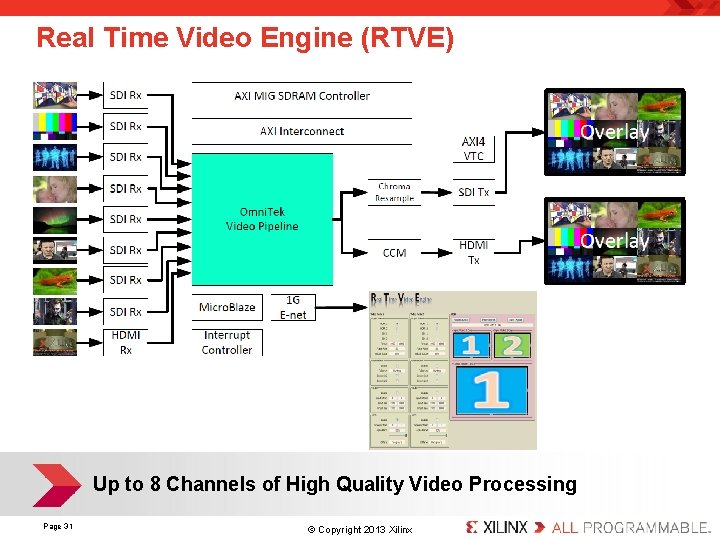

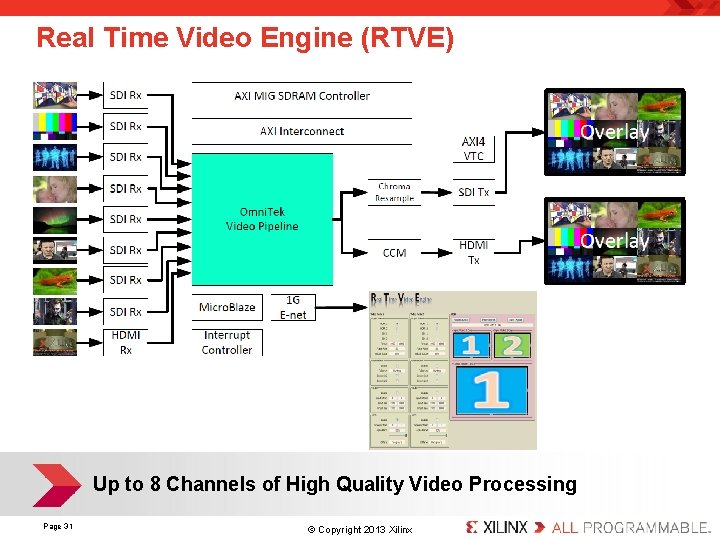

Real Time Video Engine (RTVE) Up to 8 Channels of High Quality Video Processing Page 31 . © Copyright 2013 Xilinx.

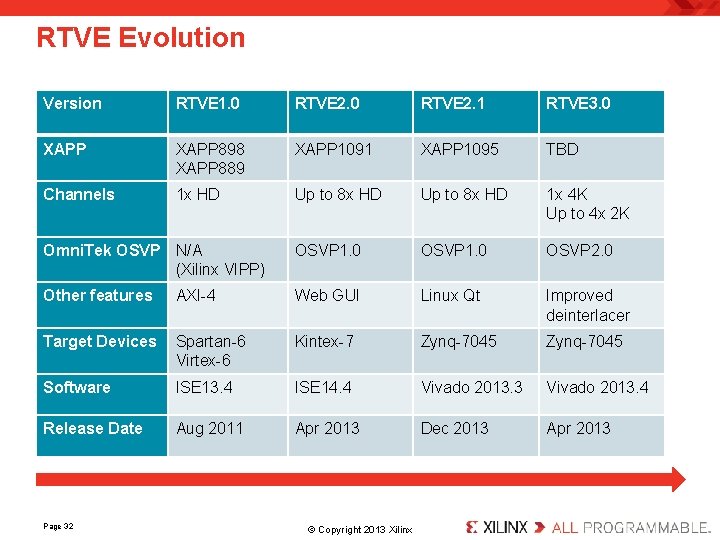

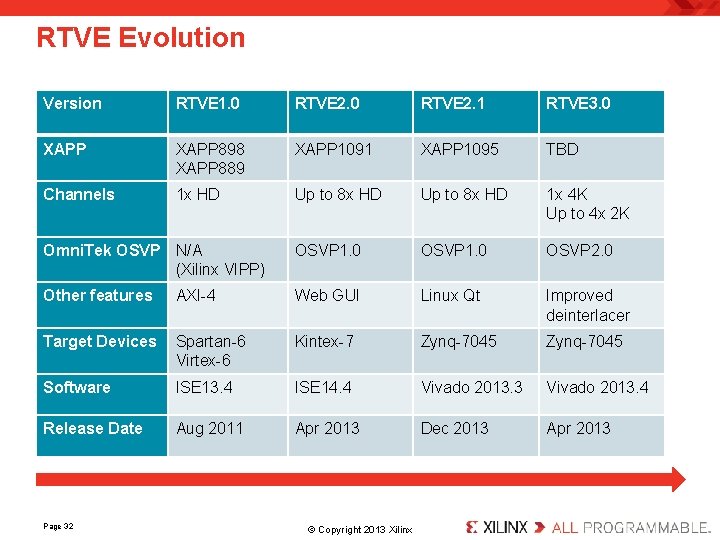

RTVE Evolution Version RTVE 1. 0 RTVE 2. 1 RTVE 3. 0 XAPP 898 XAPP 889 XAPP 1091 XAPP 1095 TBD Channels 1 x HD Up to 8 x HD 1 x 4 K Up to 4 x 2 K Omni. Tek OSVP N/A (Xilinx VIPP) OSVP 1. 0 OSVP 2. 0 Other features AXI-4 Web GUI Linux Qt Improved deinterlacer Target Devices Spartan-6 Virtex-6 Kintex-7 Zynq-7045 Software ISE 13. 4 ISE 14. 4 Vivado 2013. 3 Vivado 2013. 4 Release Date Aug 2011 Apr 2013 Dec 2013 Apr 2013 Page 32 . © Copyright 2013 Xilinx.

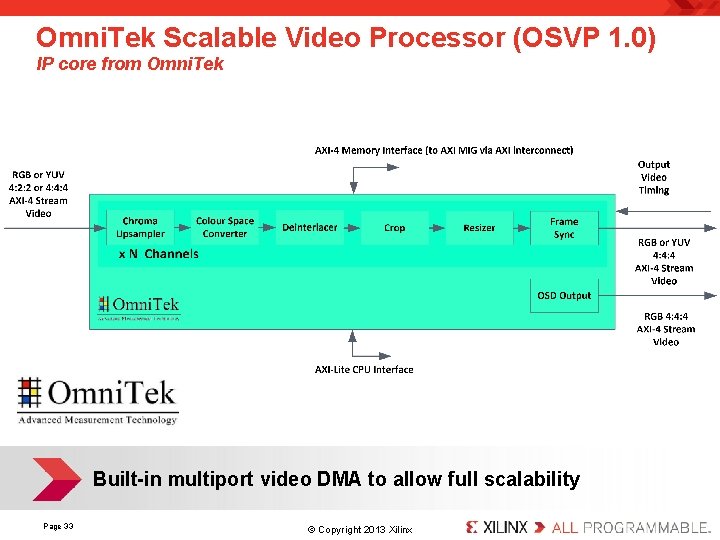

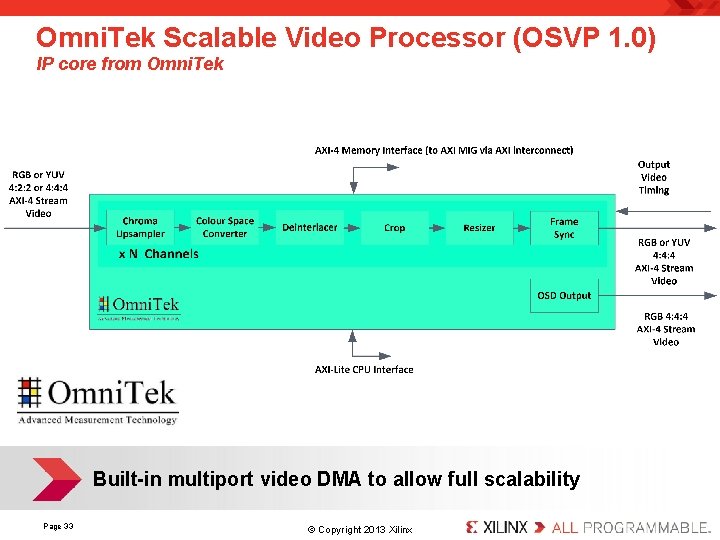

Omni. Tek Scalable Video Processor (OSVP 1. 0) IP core from Omni. Tek Built-in multiport video DMA to allow full scalability Page 33 . © Copyright 2013 Xilinx.

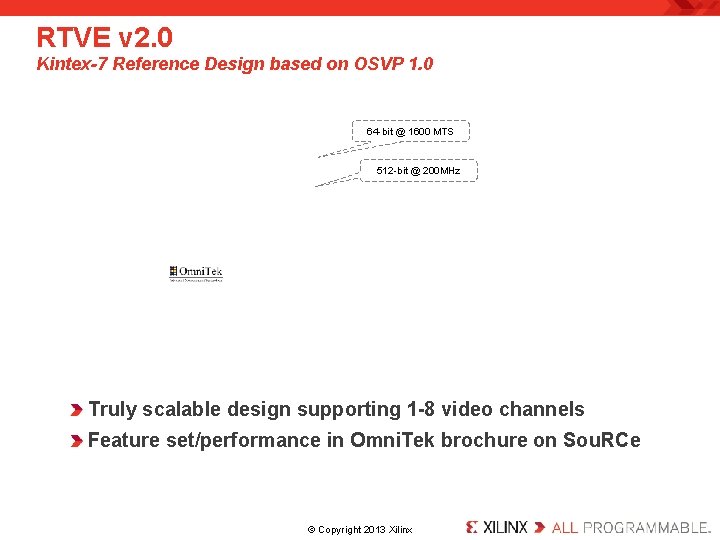

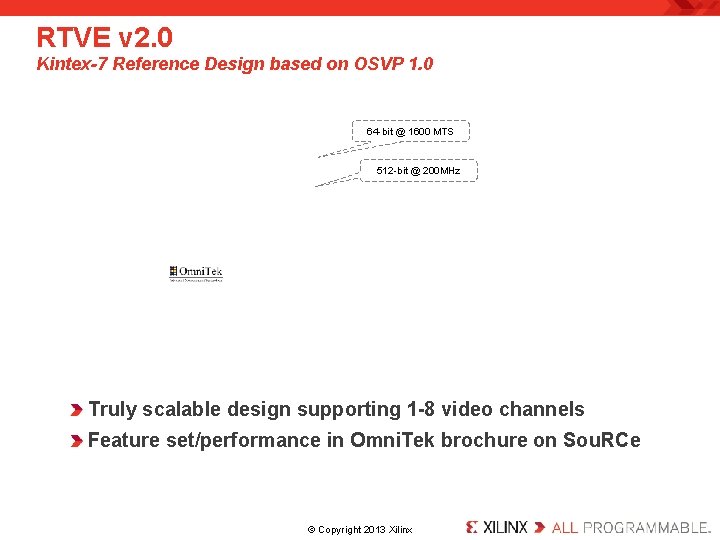

RTVE v 2. 0 Kintex-7 Reference Design based on OSVP 1. 0 64 -bit @ 1600 MTS 512 -bit @ 200 MHz Truly scalable design supporting 1 -8 video channels Feature set/performance in Omni. Tek brochure on Sou. RCe . © Copyright 2013 Xilinx.

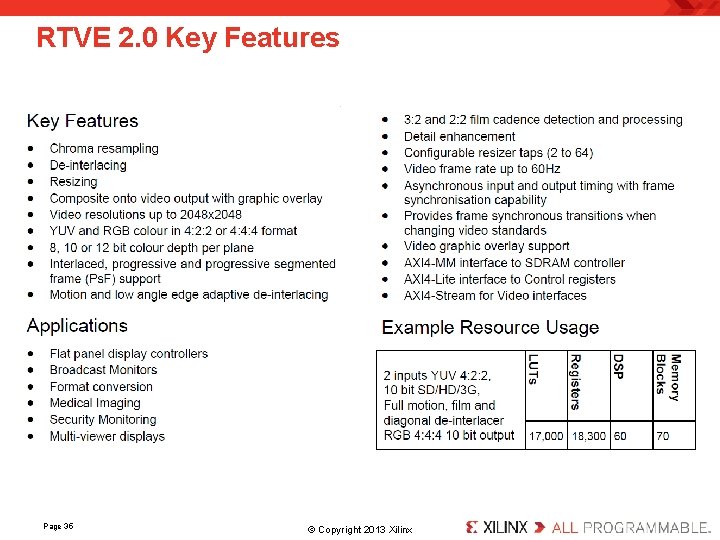

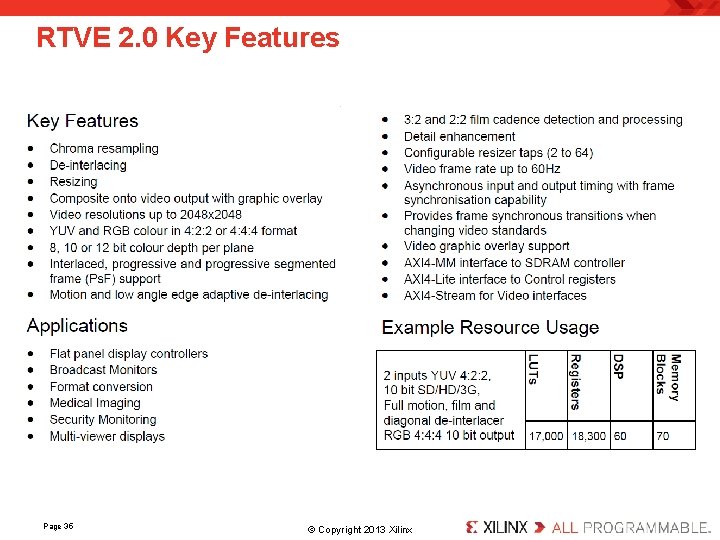

RTVE 2. 0 Key Features Page 35 . © Copyright 2013 Xilinx.

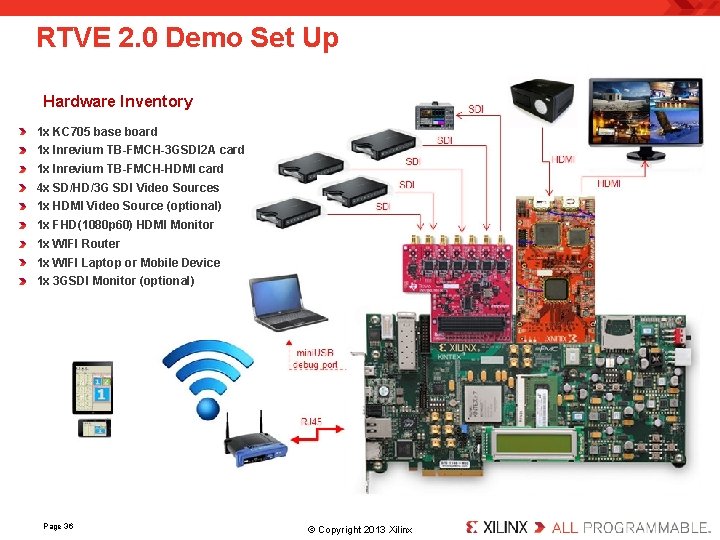

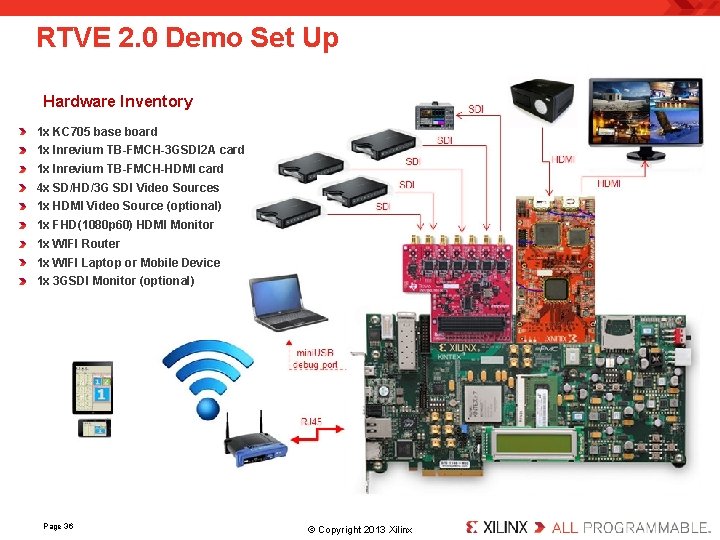

RTVE 2. 0 Demo Set Up Hardware Inventory 1 x KC 705 base board 1 x Inrevium TB-FMCH-3 GSDI 2 A card 1 x Inrevium TB-FMCH-HDMI card 4 x SD/HD/3 G SDI Video Sources 1 x HDMI Video Source (optional) 1 x FHD(1080 p 60) HDMI Monitor 1 x WIFI Router 1 x WIFI Laptop or Mobile Device 1 x 3 GSDI Monitor (optional) Page 36 . © Copyright 2013 Xilinx.

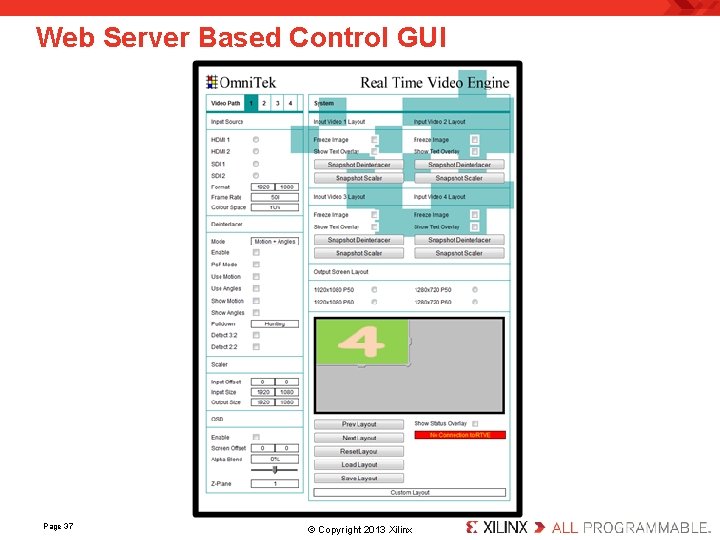

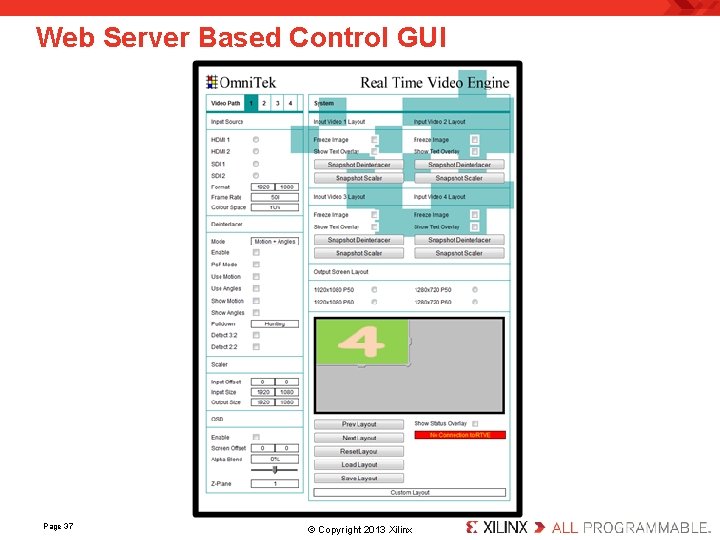

Web Server Based Control GUI Page 37 . © Copyright 2013 Xilinx.

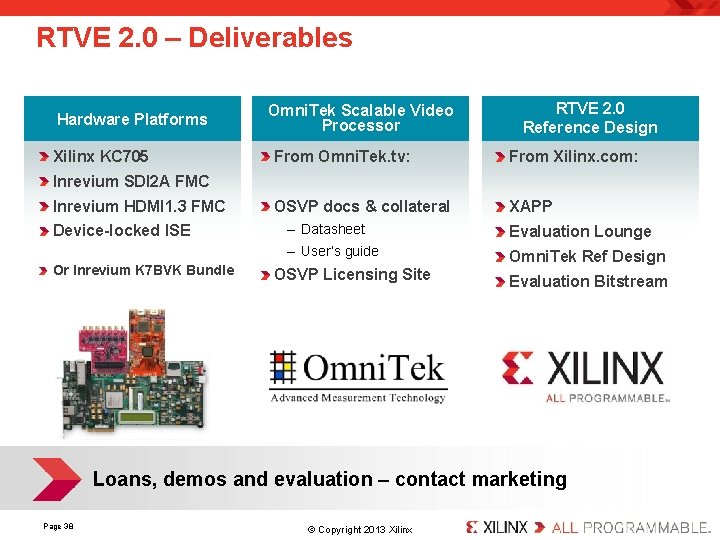

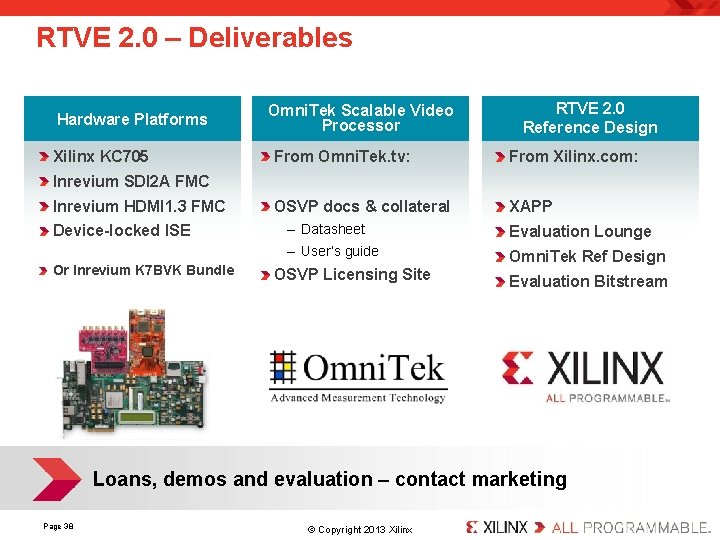

RTVE 2. 0 – Deliverables Hardware Platforms Xilinx KC 705 Omni. Tek Scalable Video Processor RTVE 2. 0 Reference Design From Omni. Tek. tv: From Xilinx. com: OSVP docs & collateral XAPP Inrevium SDI 2 A FMC Inrevium HDMI 1. 3 FMC Device-locked ISE Or Inrevium K 7 BVK Bundle – Datasheet Evaluation Lounge – User’s guide Omni. Tek Ref Design OSVP Licensing Site Evaluation Bitstream Loans, demos and evaluation – contact marketing Page 38 . © Copyright 2013 Xilinx.

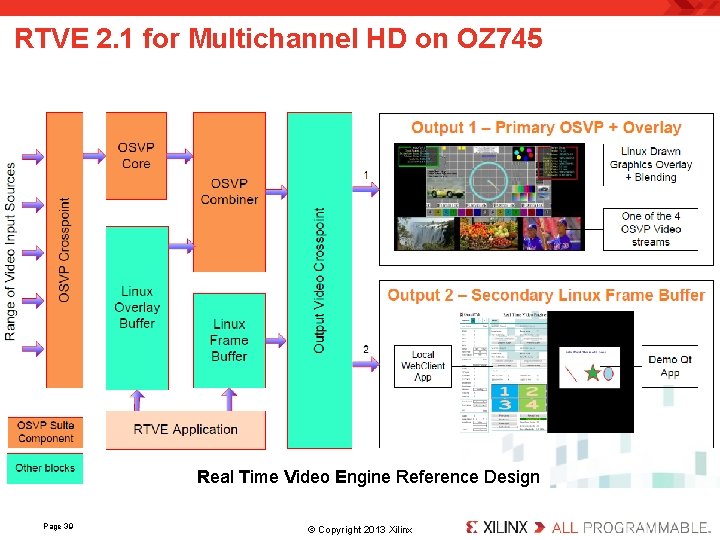

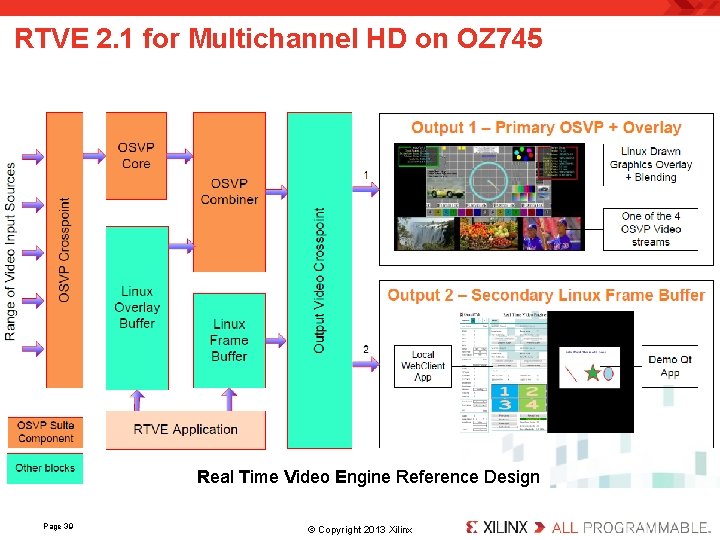

RTVE 2. 1 for Multichannel HD on OZ 745 Real Time Video Engine Reference Design Page 39 . © Copyright 2013 Xilinx.

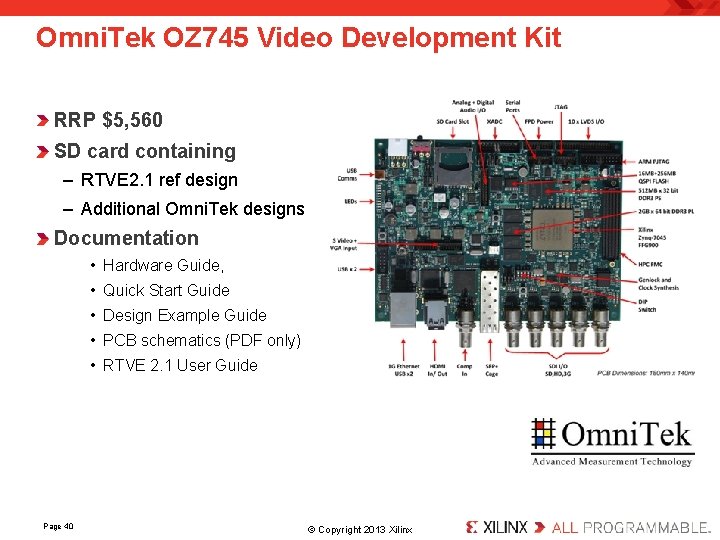

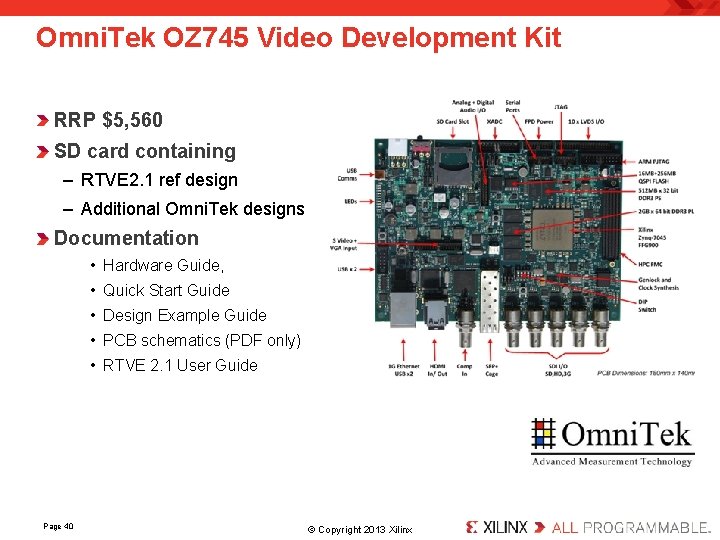

Omni. Tek OZ 745 Video Development Kit RRP $5, 560 SD card containing – RTVE 2. 1 ref design – Additional Omni. Tek designs Documentation • Hardware Guide, • Quick Start Guide • Design Example Guide • PCB schematics (PDF only) • RTVE 2. 1 User Guide Page 40 . © Copyright 2013 Xilinx.

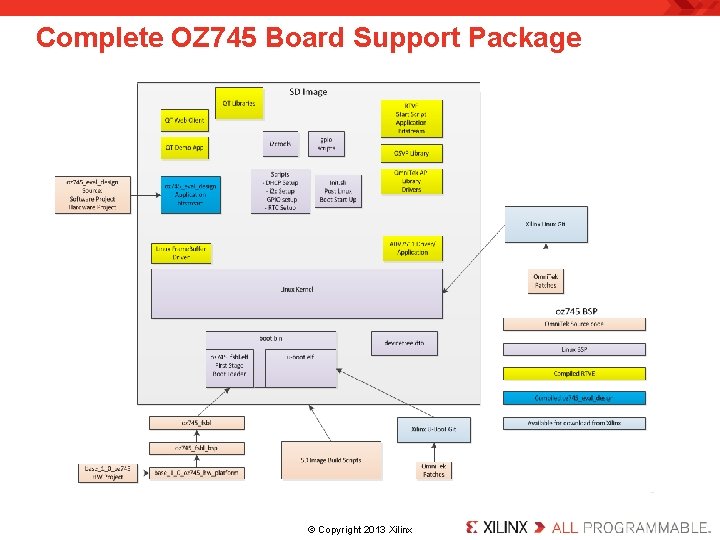

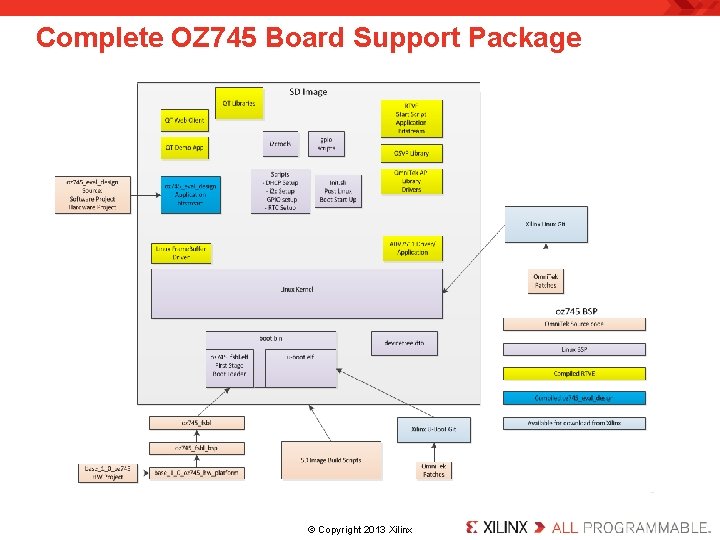

Complete OZ 745 Board Support Package . © Copyright 2013 Xilinx.

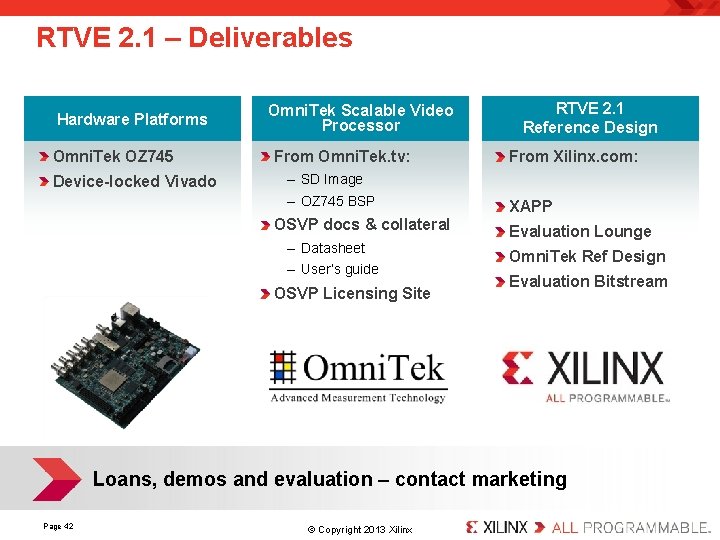

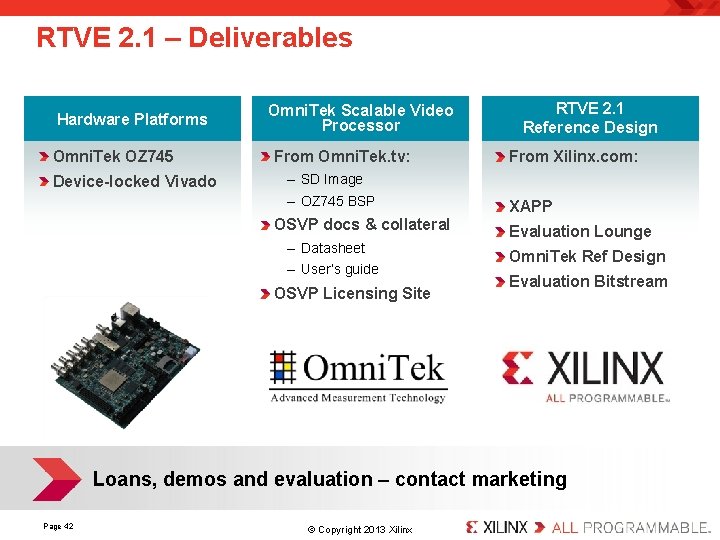

RTVE 2. 1 – Deliverables Hardware Platforms Omni. Tek OZ 745 Device-locked Vivado Omni. Tek Scalable Video Processor From Omni. Tek. tv: RTVE 2. 1 Reference Design From Xilinx. com: – SD Image – OZ 745 BSP OSVP docs & collateral – Datasheet – User’s guide OSVP Licensing Site XAPP Evaluation Lounge Omni. Tek Ref Design Evaluation Bitstream Loans, demos and evaluation – contact marketing Page 42 . © Copyright 2013 Xilinx.

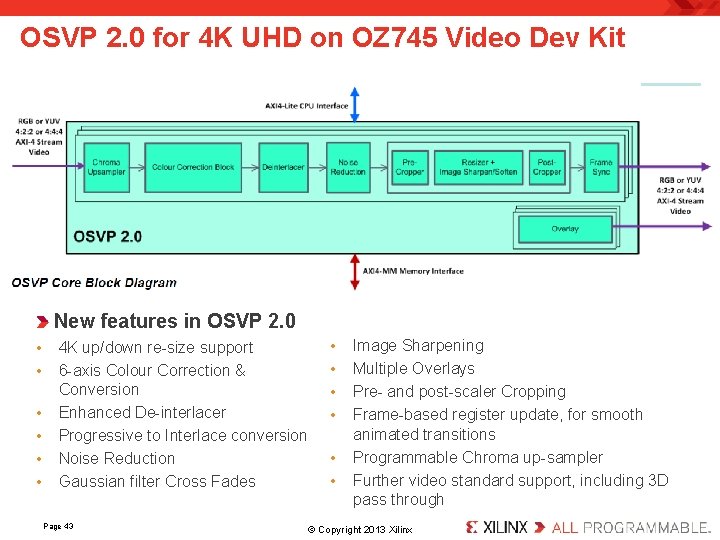

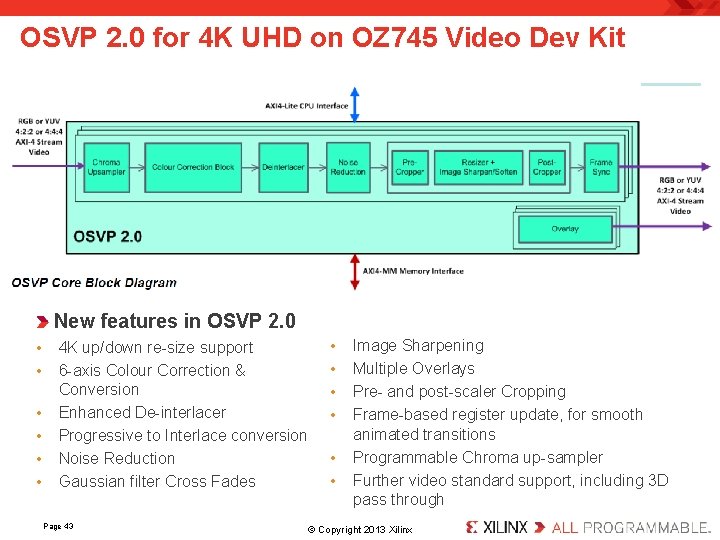

OSVP 2. 0 for 4 K UHD on OZ 745 Video Dev Kit New features in OSVP 2. 0 • • • 4 K up/down re-size support 6 -axis Colour Correction & Conversion Enhanced De-interlacer Progressive to Interlace conversion Noise Reduction Gaussian filter Cross Fades Page 43 • • • Image Sharpening Multiple Overlays Pre- and post-scaler Cropping Frame-based register update, for smooth animated transitions Programmable Chroma up-sampler Further video standard support, including 3 D pass through. © Copyright 2013 Xilinx.

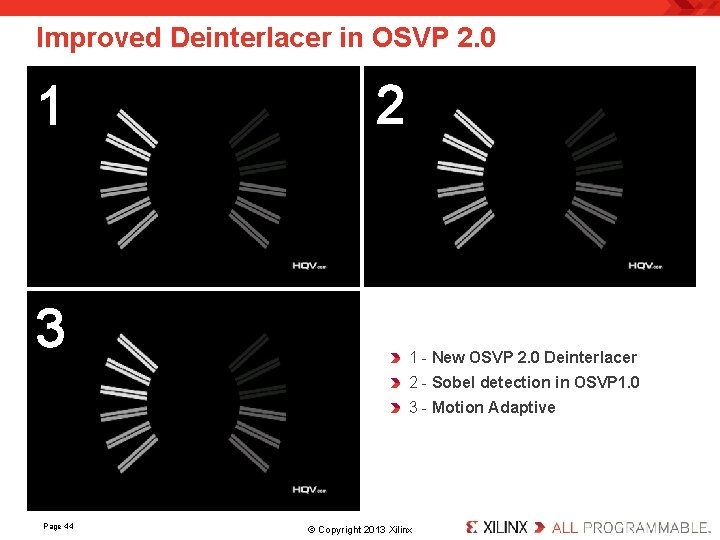

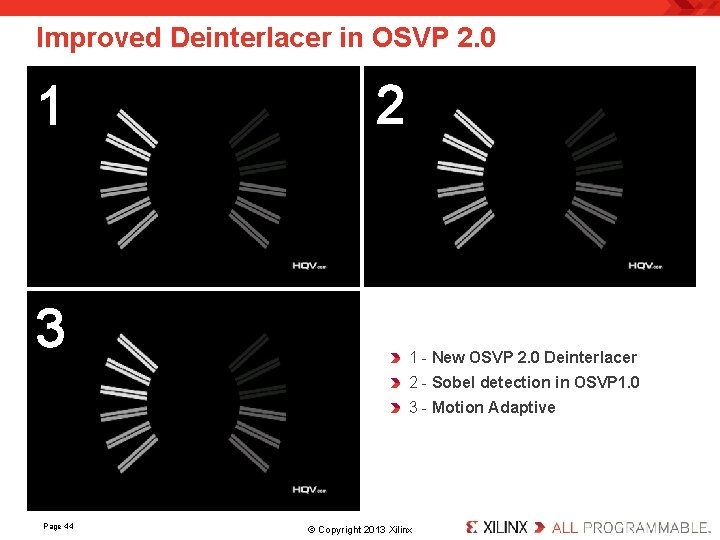

Improved Deinterlacer in OSVP 2. 0 2 1 3 1 - New OSVP 2. 0 Deinterlacer 2 - Sobel detection in OSVP 1. 0 3 - Motion Adaptive Page 44 . © Copyright 2013 Xilinx.

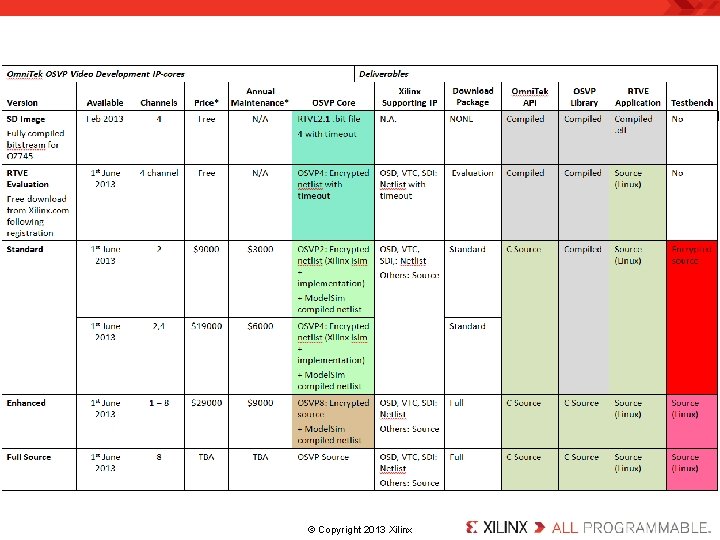

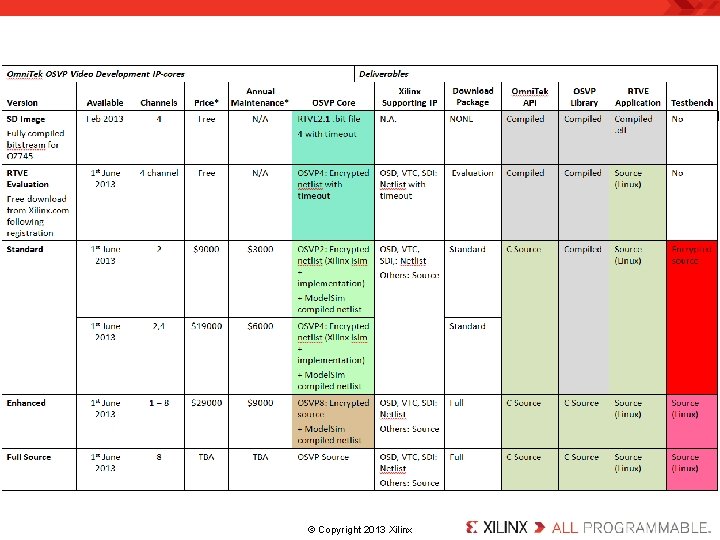

. © Copyright 2013 Xilinx.

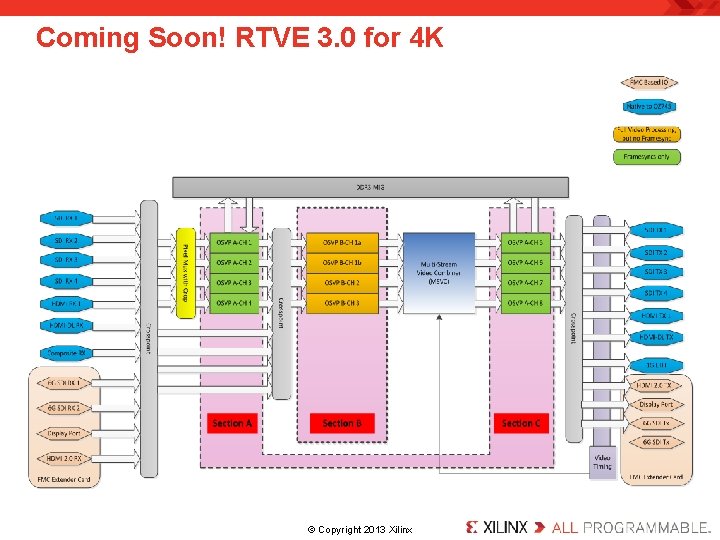

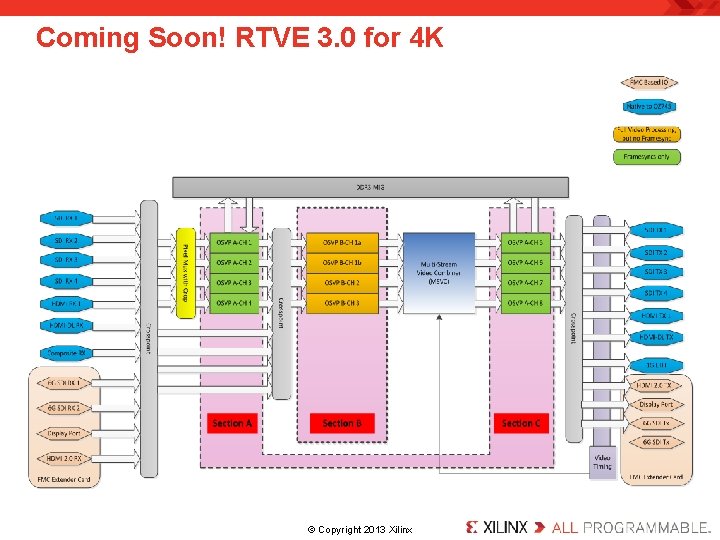

Coming Soon! RTVE 3. 0 for 4 K . © Copyright 2013 Xilinx.

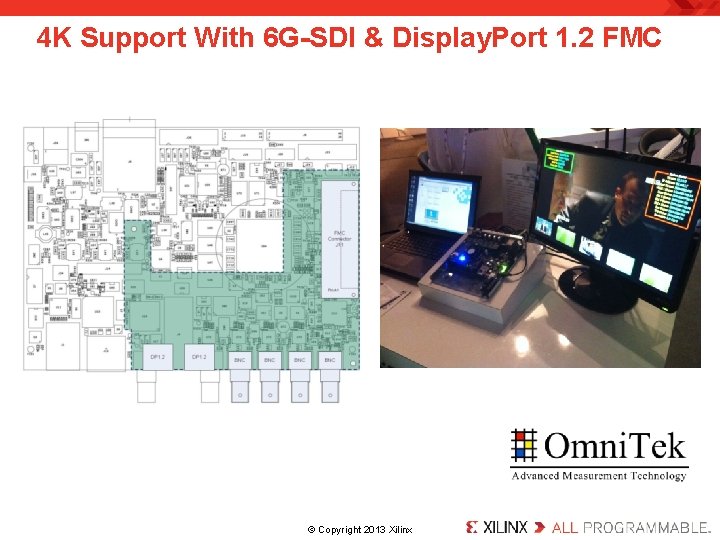

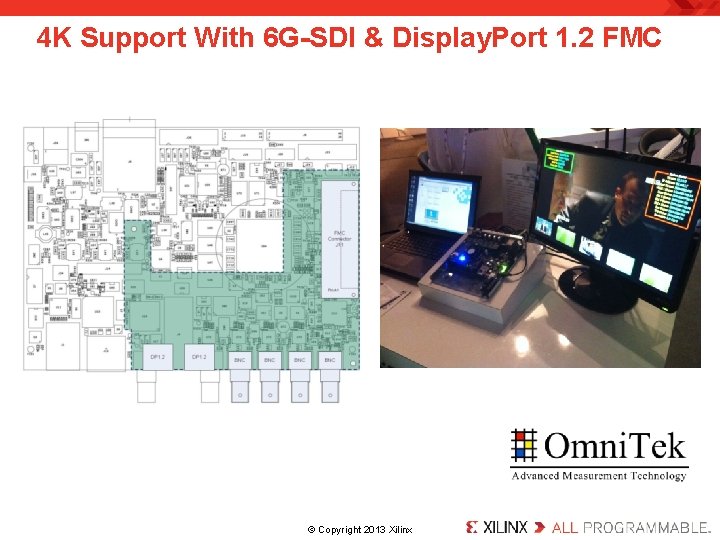

4 K Support With 6 G-SDI & Display. Port 1. 2 FMC . © Copyright 2013 Xilinx.

Smarter Vision Codecs Vision Page 48 . © Copyright 2013 Xilinx.

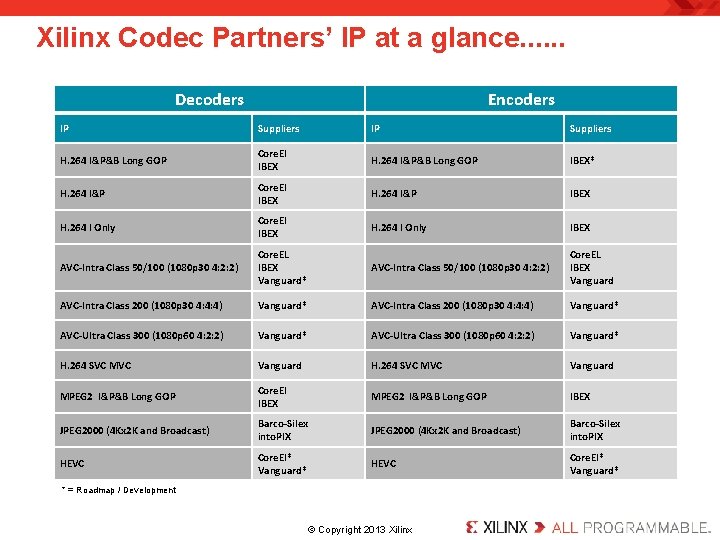

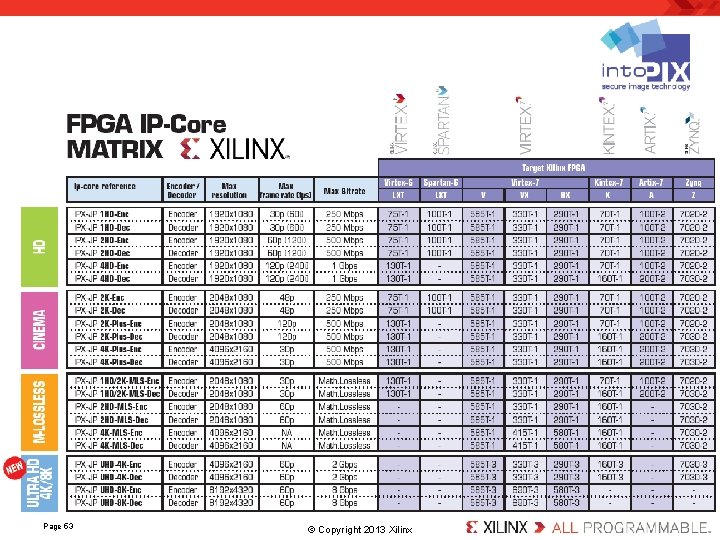

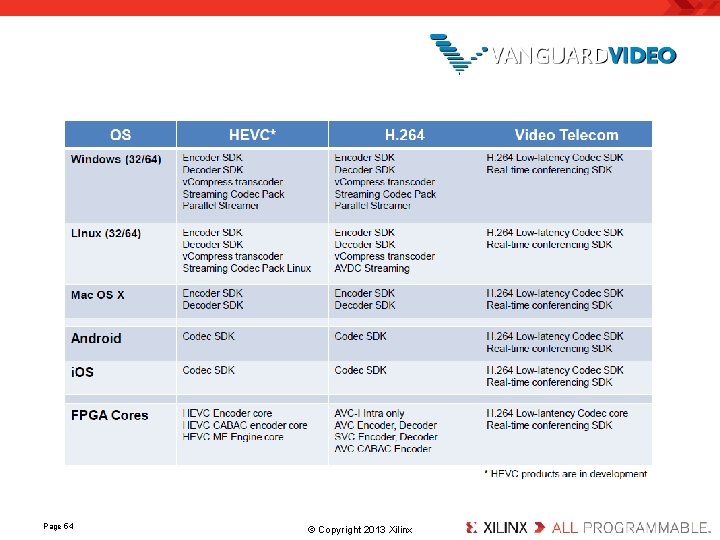

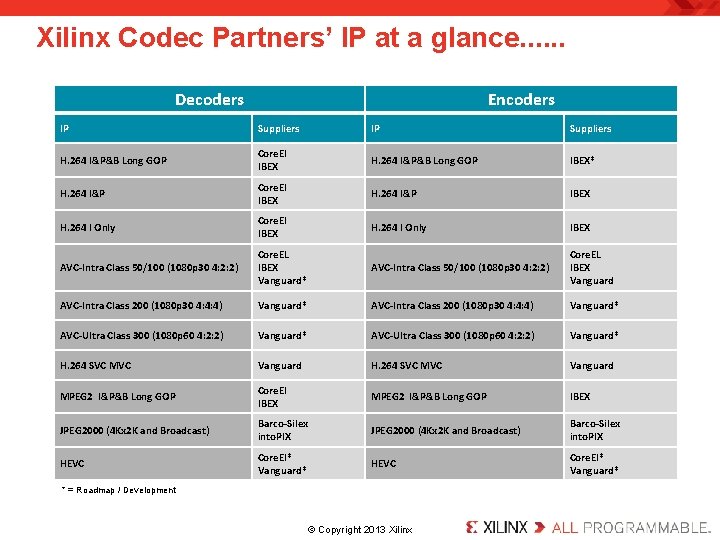

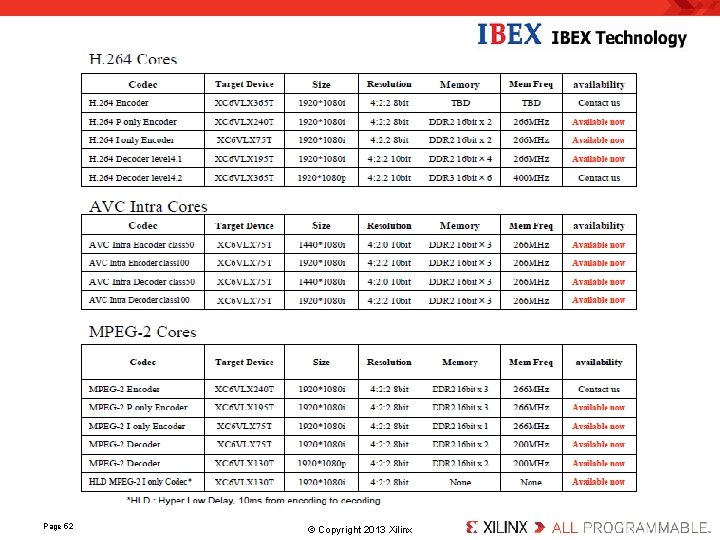

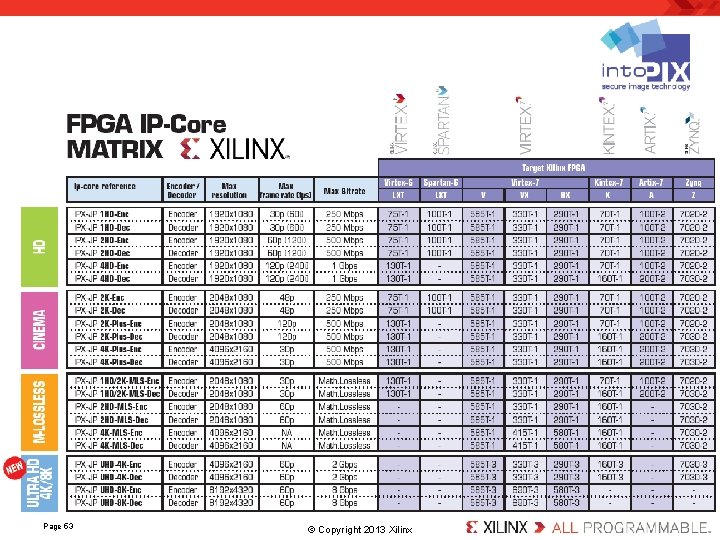

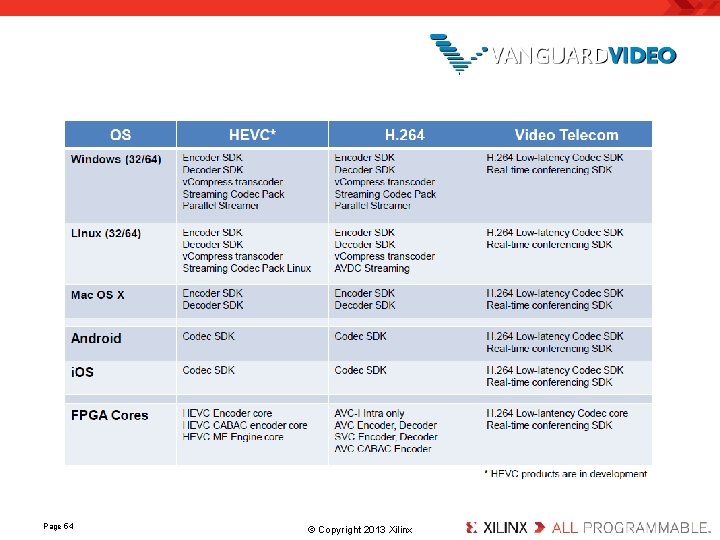

Xilinx Codec Partners’ IP at a glance. . . Decoders Encoders IP Suppliers H. 264 I&P&B Long GOP Core. El IBEX H. 264 I&P&B Long GOP IBEX* H. 264 I&P Core. El IBEX H. 264 I&P IBEX H. 264 I Only Core. El IBEX H. 264 I Only IBEX AVC-Intra Class 50/100 (1080 p 30 4: 2: 2) Core. EL IBEX Vanguard* AVC-Intra Class 50/100 (1080 p 30 4: 2: 2) Core. EL IBEX Vanguard AVC-Intra Class 200 (1080 p 30 4: 4: 4) Vanguard* AVC-Ultra Class 300 (1080 p 60 4: 2: 2) Vanguard* H. 264 SVC MVC Vanguard MPEG 2 I&P&B Long GOP Core. El IBEX MPEG 2 I&P&B Long GOP IBEX JPEG 2000 (4 Kx 2 K and Broadcast) Barco-Silex into. PIX HEVC Core. El* Vanguard* * = Roadmap / Development . © Copyright 2013 Xilinx.

Page 50 . © Copyright 2013 Xilinx.

Page 51 . © Copyright 2013 Xilinx.

Page 52 . © Copyright 2013 Xilinx.

Page 53 . © Copyright 2013 Xilinx.

Page 54 . © Copyright 2013 Xilinx.

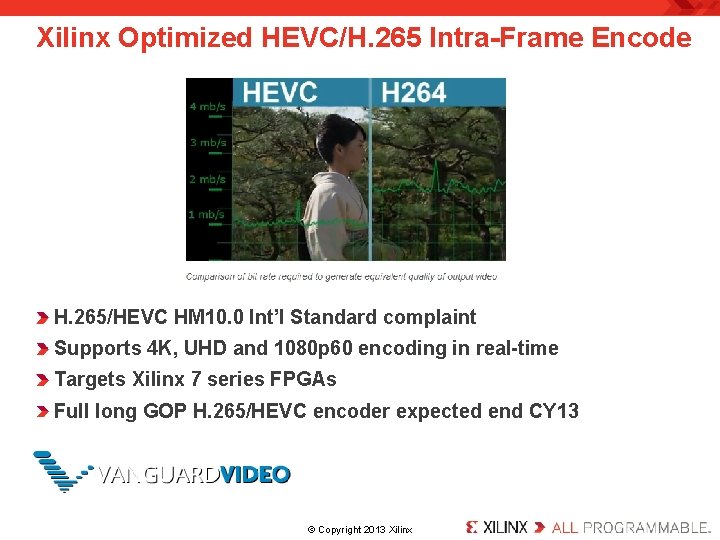

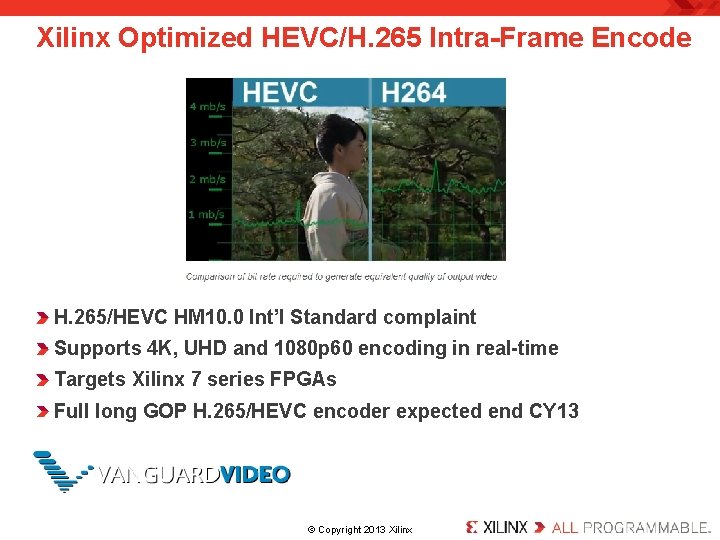

Xilinx Optimized HEVC/H. 265 Intra-Frame Encode H. 265/HEVC HM 10. 0 Int’l Standard complaint Supports 4 K, UHD and 1080 p 60 encoding in real-time Targets Xilinx 7 series FPGAs Full long GOP H. 265/HEVC encoder expected end CY 13 . © Copyright 2013 Xilinx.