Smart Reflex Power and Performance Management Technologies for

- Slides: 21

Smart. Reflex Power and Performance Management Technologies for 90 nm, 65 nm, and 45 nm Mobile Application Processors Farideh. Shiran Department of Electronics Carleton University, Ottawa, ON, Canada fshiran@doe. carleton. ca

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

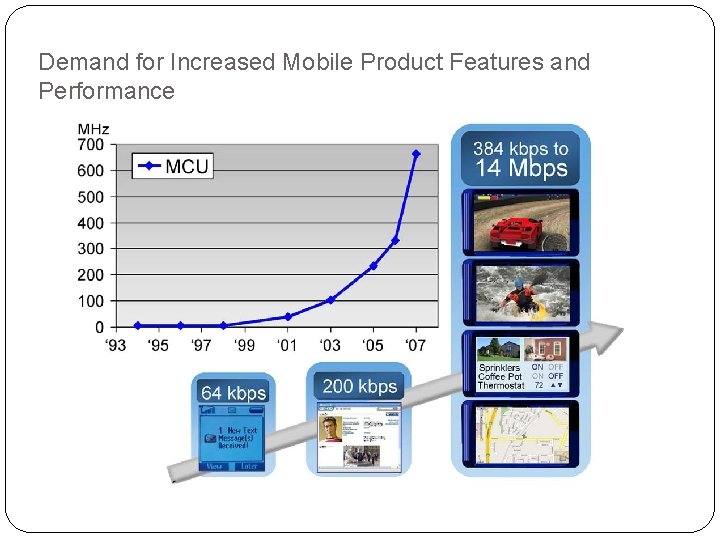

Introduction Demand for increasing features of handheld devices Processors speeds reaching 1 GHz and above Bottleneck: battery technology Trade-off: battery life versus higher speeds Technology Scaling Advantages Disadvantagrs

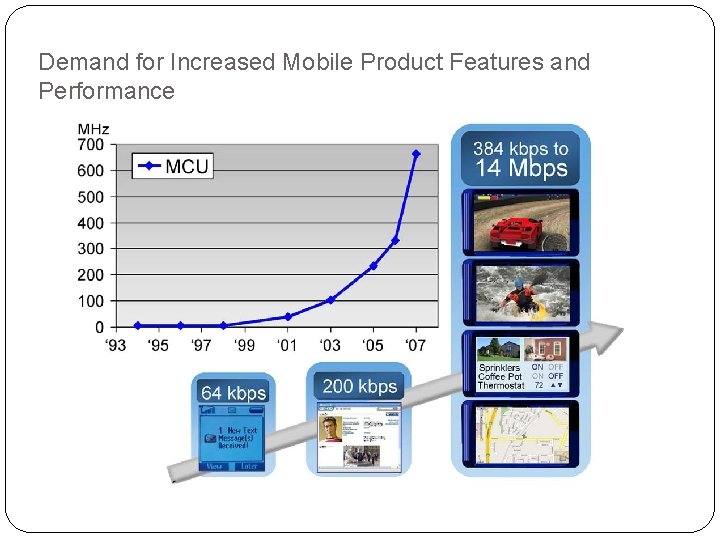

Demand for Increased Mobile Product Features and Performance

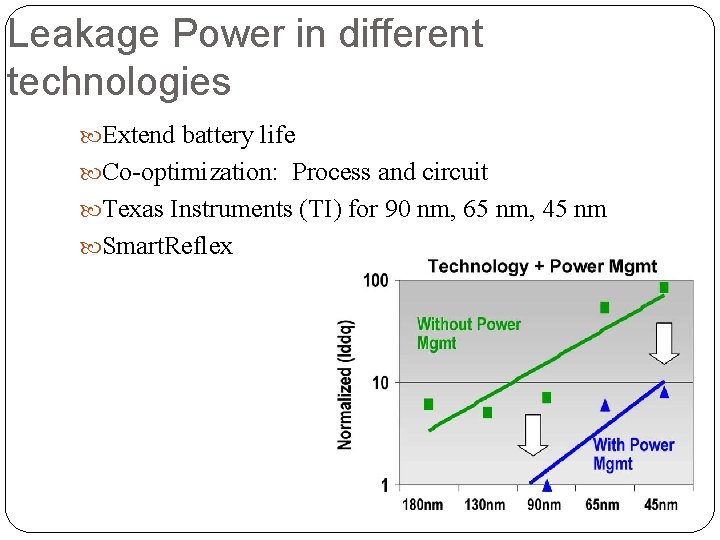

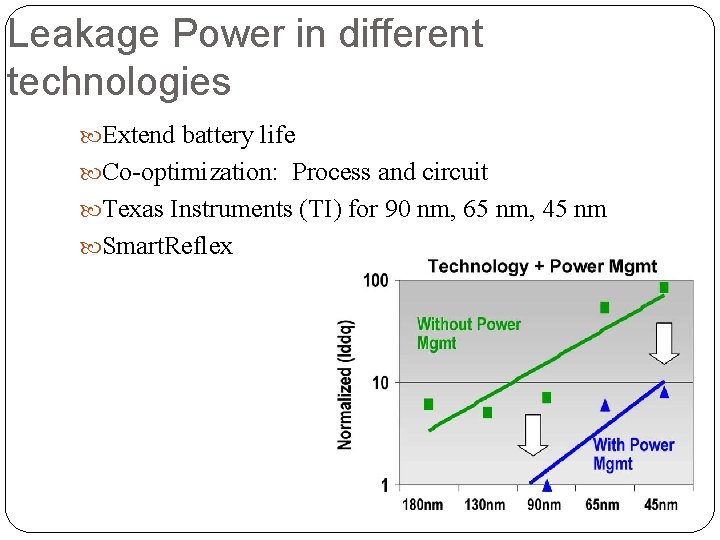

Leakage Power in different technologies Extend battery life Co-optimization: Process and circuit Texas Instruments (TI) for 90 nm, 65 nm, 45 nm Smart. Reflex

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

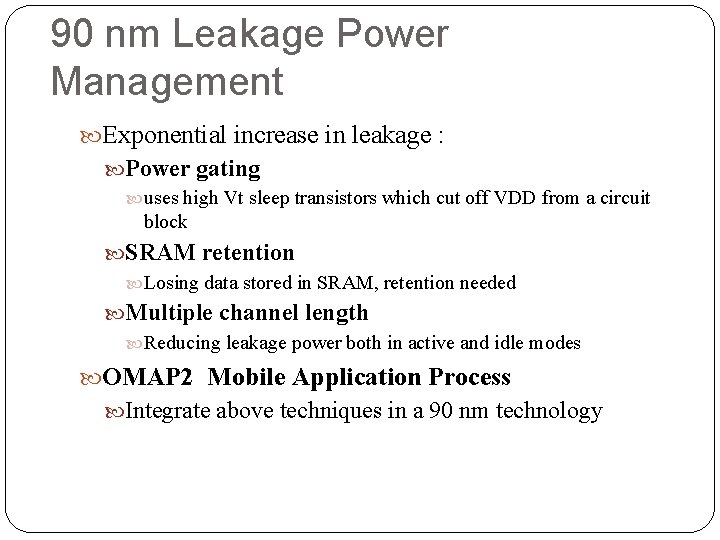

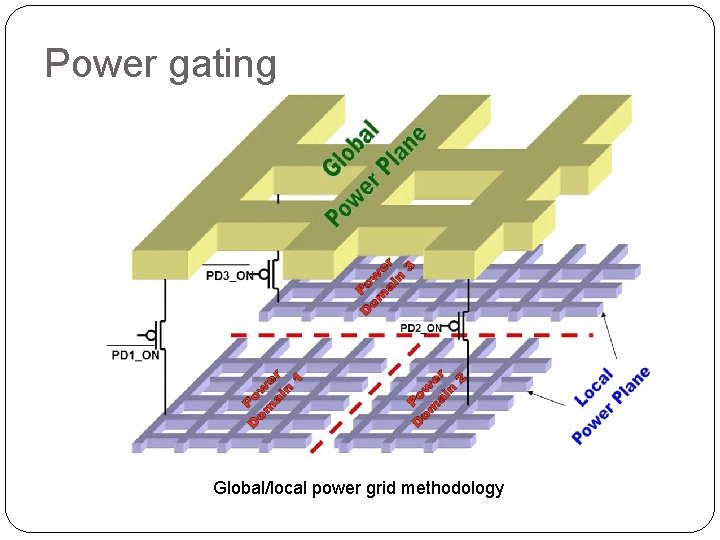

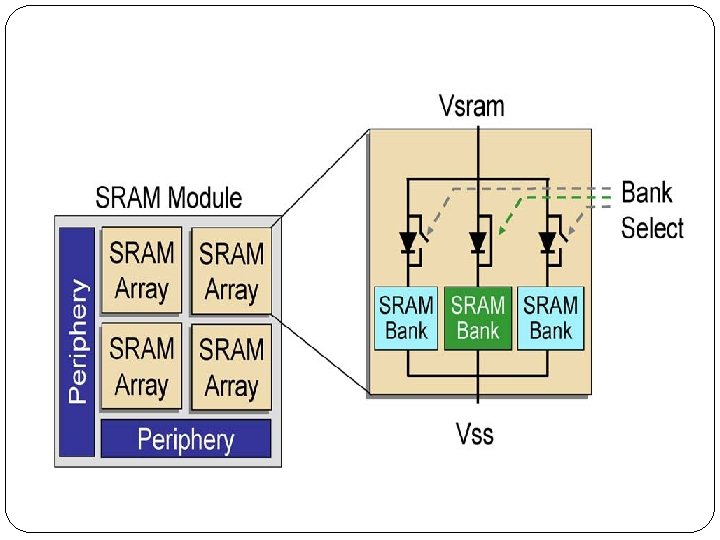

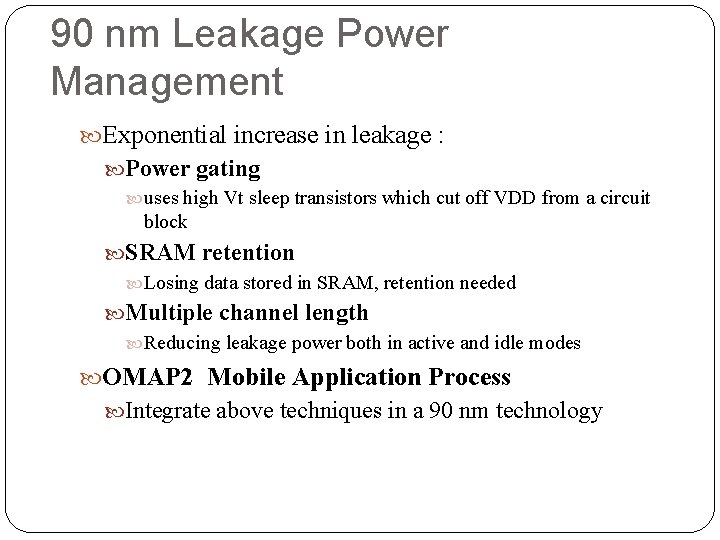

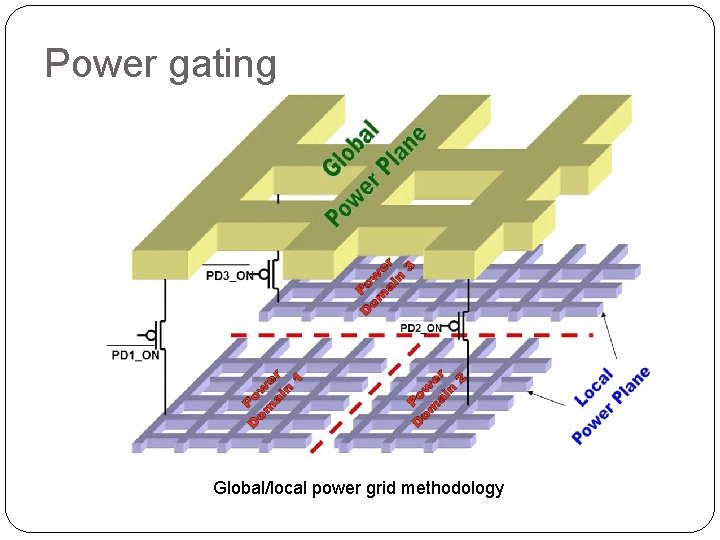

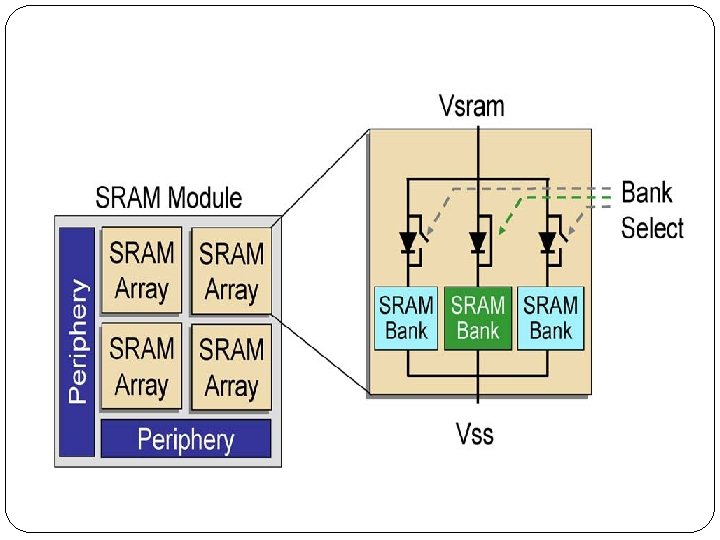

90 nm Leakage Power Management Exponential increase in leakage : Power gating uses high Vt sleep transistors which cut off VDD from a circuit block SRAM retention Losing data stored in SRAM, retention needed Multiple channel length Reducing leakage power both in active and idle modes OMAP 2 Mobile Application Process Integrate above techniques in a 90 nm technology

Power gating Global/local power grid methodology

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

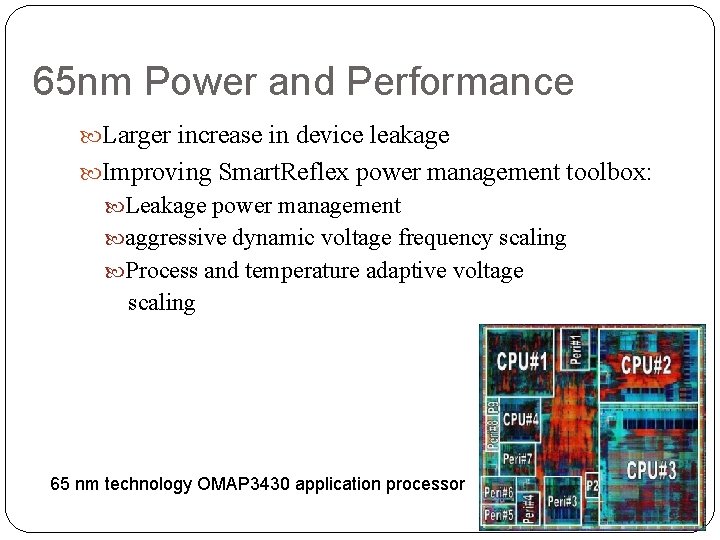

65 nm Power and Performance Larger increase in device leakage Improving Smart. Reflex power management toolbox: Leakage power management aggressive dynamic voltage frequency scaling Process and temperature adaptive voltage scaling 65 nm technology OMAP 3430 application processor

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

45 nm Power and Performance Further reduction of active leakage power and performance increase Adaptive body bias (ABB): FBB Retention Til Access (RTA) Full power state Low power state Single Chip 3. 5 Baseband Applications Processor Integrate above techniques in a 45 nm technology

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion

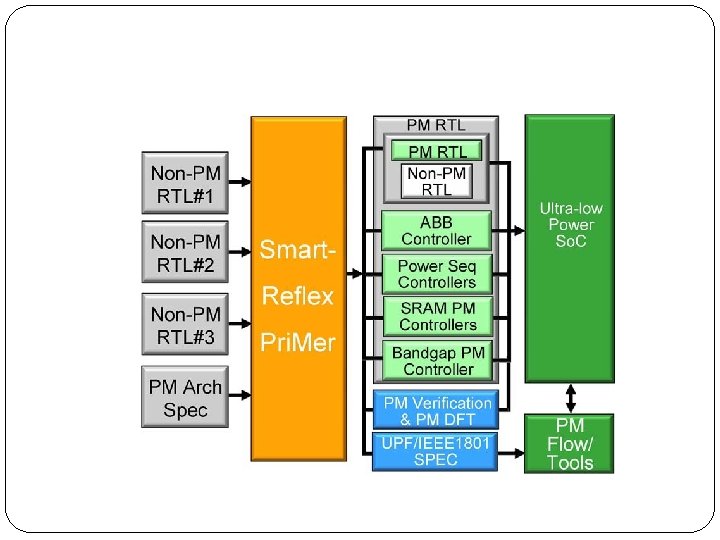

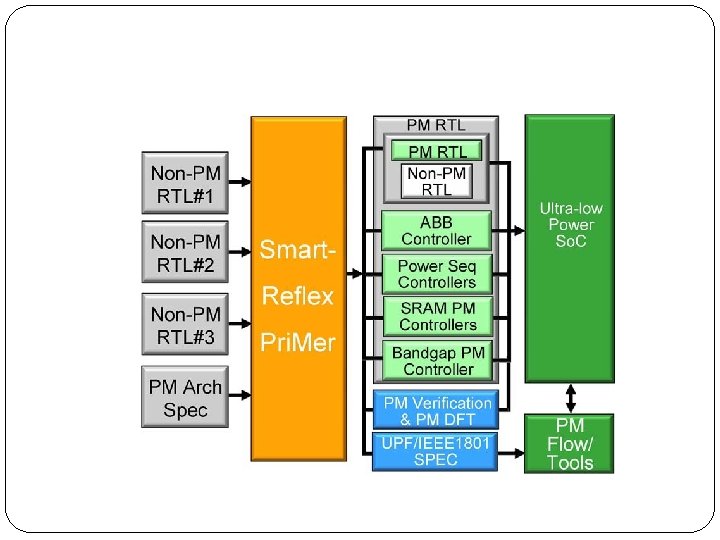

Design methodology and automation Smart. Reflex-Pri. Mer (Smart. Pri. Mer): Chip-level leakage management design methodology Power Managed (PM) modules Power-Aware Verification PM integrity check Power-aware simulations at RTL and gate levels Not power-aware Power-aware

Outline Introduction First Generation 90 nm Second Generation 65 nm Third Generation 45 nm Design Methodology and Automation Low Power Standard: IEEE-1801 Conclusion and Future Work

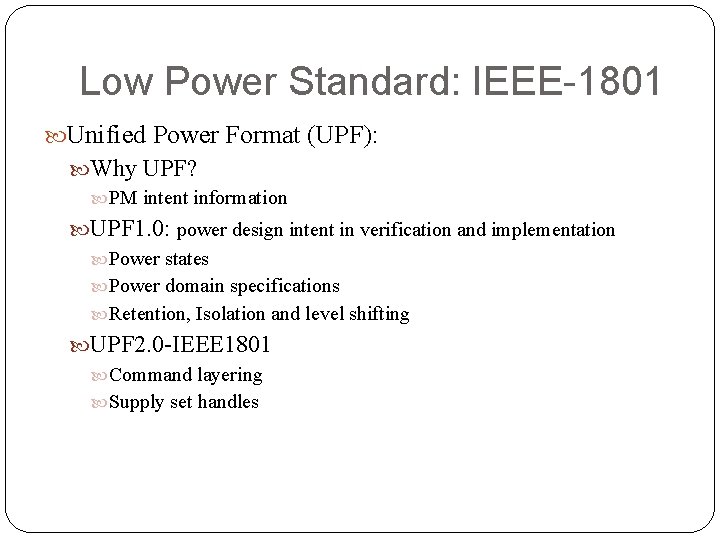

Low Power Standard: IEEE-1801 Unified Power Format (UPF): Why UPF? PM intent information UPF 1. 0: power design intent in verification and implementation Power states Power domain specifications Retention, Isolation and level shifting UPF 2. 0 -IEEE 1801 Command layering Supply set handles

Conclusions For higher performance (power management) Three generation technologies 90 nm, 65 nm, 40 nm design methodology Smart. Reflex-Pri. Mer Power-Aware Verification Standard UPF 1. 0 UPF 2. 0

Thank You