slicov mc pstroje Logick analyztor Logick analyztor slou

- Slides: 7

Číslicové měřící přístroje Logický analyzátor

Logický analyzátor • slouží pro diagnostiku a hledání poruch na paralelních sběrnicích • od číslicových paměťových osciloskopů se odlišuje velkým počtem kanálů a systémem zpracování informací (dat) • minimální počet kanálů je 8, u modulárních přístrojů se pak používají 16 bitové moduly umožňující rozšíření až na 192 kanálů • logický analyzátor rozlišuje dvě napěťové úrovně odpovídající stavu logické 0 (L – Low) a logické 1 (H – High) • nejjednodušší logické analyzátory pracují pouze s úrovněmi TTL logiky s rozlišovací úrovní cca 1, 4 V • rozsah paměti 4 k. B až několik MB • většina analyzátorů umožňuje před měřením nastavit prahové úrovně napětí a to až do napětí 20 V (pro CMOS a ECL)

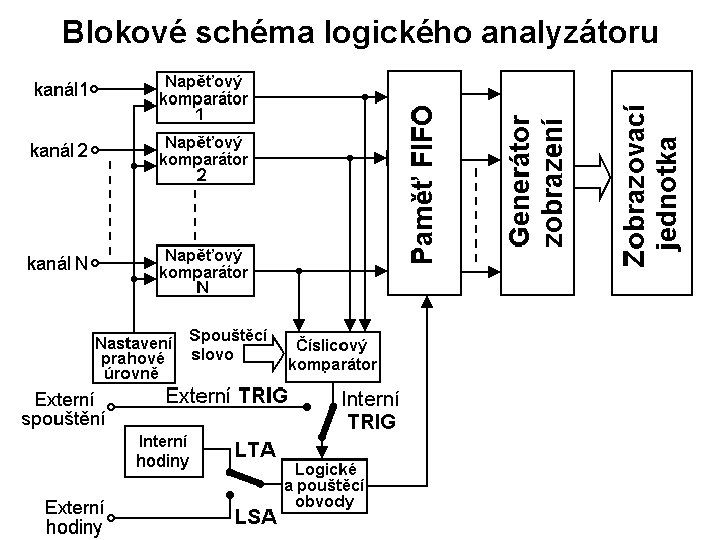

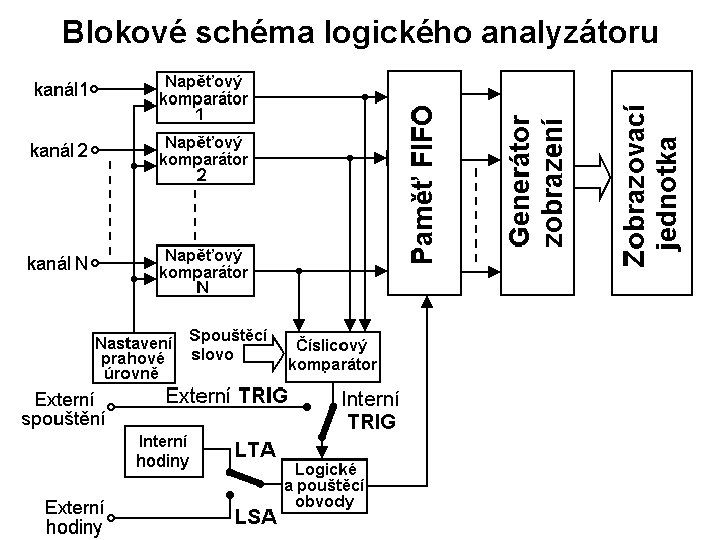

Blokové schéma logického analyzátoru

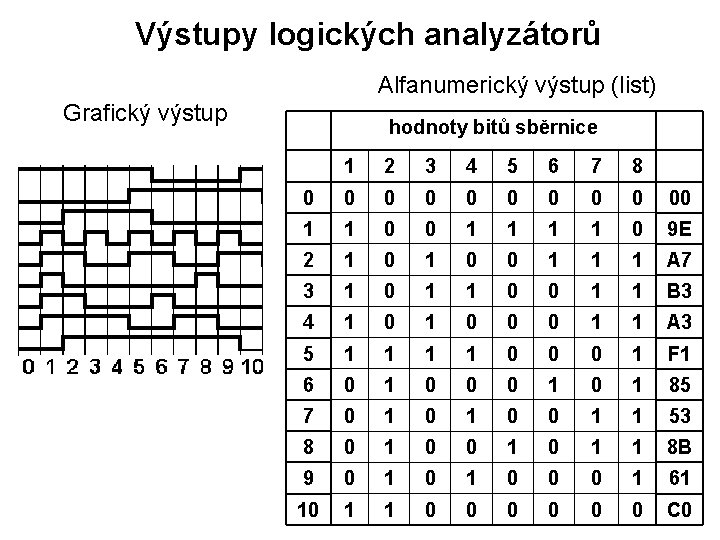

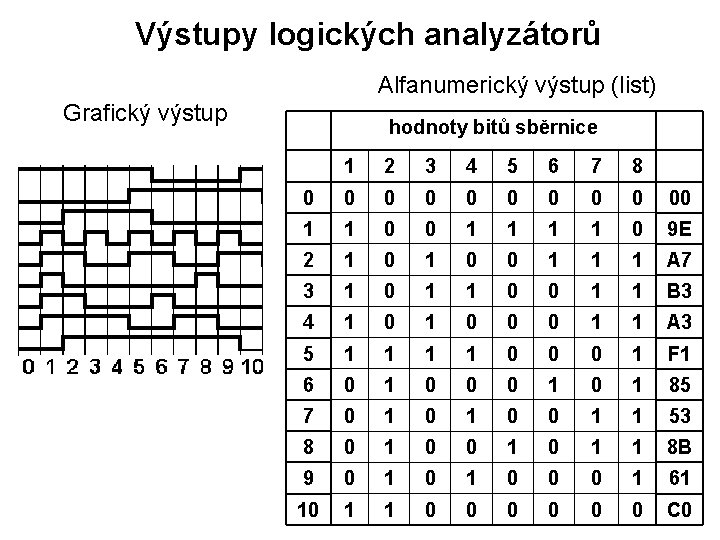

Princip činnosti • vstupní komparátory porovnávají napětí kanálů s nastavenými prahovými úrovněmi – výsledkem je hodnota H nebo L uložená do paměti FIFO • po zapnutí se paměť automaticky vynuluje a začne se plnit daty • po naplnění paměti se dříve uložená data přepisují novějšími • FIFO umožňuje logickému analyzátoru zaznamenání dějů (sběr dat) před příchodem spouštěcího impulzu • po ukončení sběru dat jsou pomocí generátoru zobrazení vytvořeny výstupy – Alfanumerickým výstupem je seznam (angl. list) ve zvoleném kódů – binárním, hexadecimálním, oktalovém nebo v BCD kódu – Grafickým výstupem je časový průběh signálů v jednotlivých kanálech – časový diagram

Výstupy logických analyzátorů Alfanumerický výstup (list) Grafický výstup hodnoty bitů sběrnice 1 2 3 4 5 6 7 8 0 0 0 0 00 1 1 0 9 E 2 1 0 0 1 1 1 A 7 3 1 0 1 1 0 0 1 1 B 3 4 1 0 0 0 1 1 A 3 5 1 1 0 0 0 1 F 1 6 0 1 0 0 0 1 85 7 0 1 0 0 1 1 53 8 0 1 0 1 1 8 B 9 0 1 0 0 0 1 61 10 1 1 0 0 0 C 0

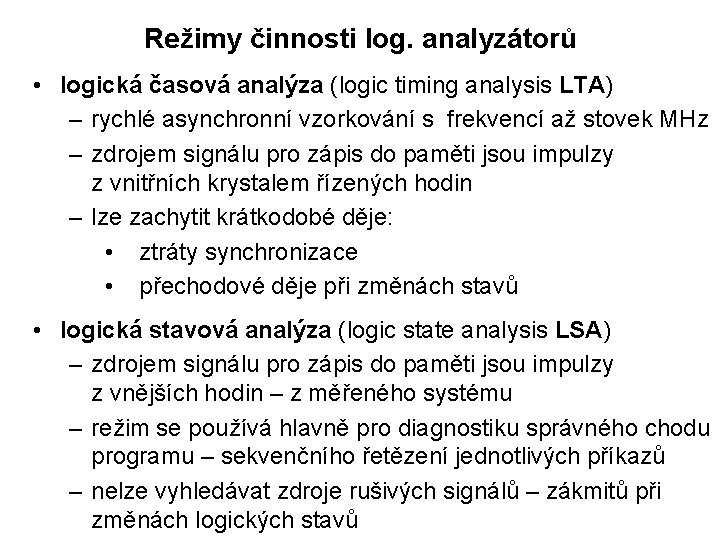

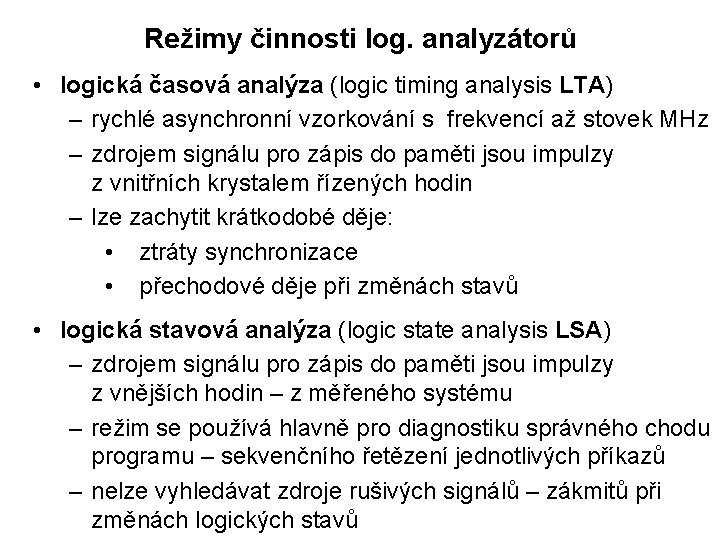

Režimy činnosti log. analyzátorů • logická časová analýza (logic timing analysis LTA) – rychlé asynchronní vzorkování s frekvencí až stovek MHz – zdrojem signálu pro zápis do paměti jsou impulzy z vnitřních krystalem řízených hodin – lze zachytit krátkodobé děje: • ztráty synchronizace • přechodové děje při změnách stavů • logická stavová analýza (logic state analysis LSA) – zdrojem signálu pro zápis do paměti jsou impulzy z vnějších hodin – z měřeného systému – režim se používá hlavně pro diagnostiku správného chodu programu – sekvenčního řetězení jednotlivých příkazů – nelze vyhledávat zdroje rušivých signálů – zákmitů při změnách logických stavů

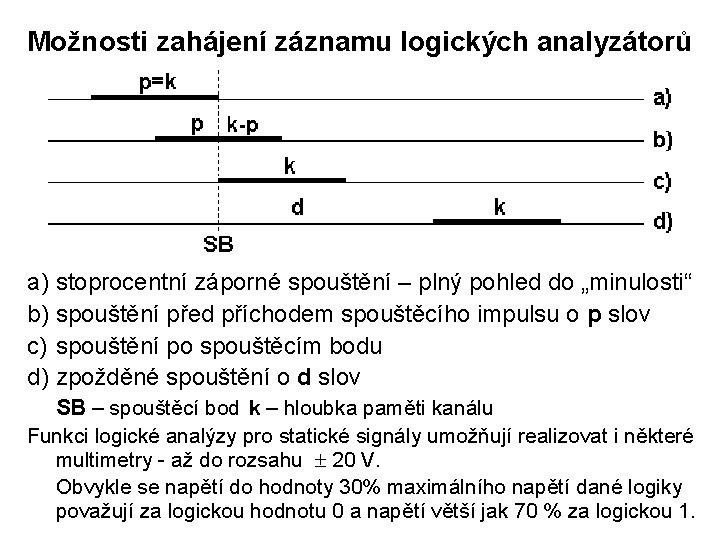

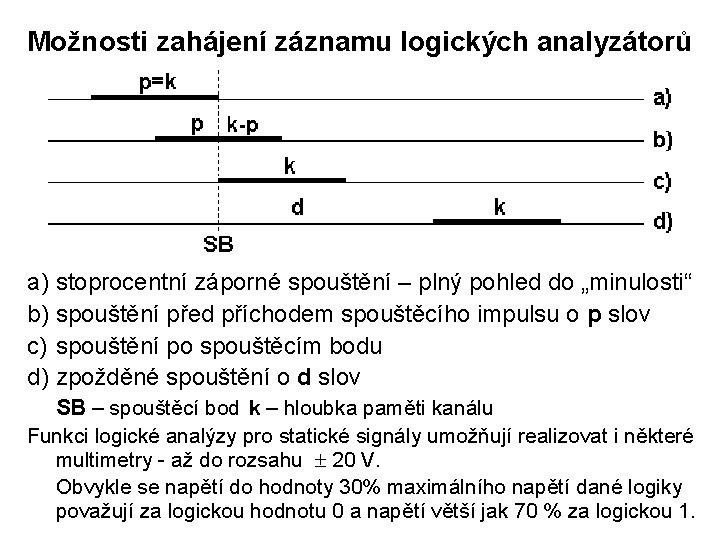

Možnosti zahájení záznamu logických analyzátorů a) stoprocentní záporné spouštění – plný pohled do „minulosti“ b) spouštění před příchodem spouštěcího impulsu o p slov c) spouštění po spouštěcím bodu d) zpožděné spouštění o d slov SB – spouštěcí bod k – hloubka paměti kanálu Funkci logické analýzy pro statické signály umožňují realizovat i některé multimetry - až do rozsahu 20 V. Obvykle se napětí do hodnoty 30% maximálního napětí dané logiky považují za logickou hodnotu 0 a napětí větší jak 70 % za logickou 1.