SLHC CMS EMU Upgrade Digital CFEB Ben Bylsma

SLHC CMS EMU Upgrade Digital CFEB Ben Bylsma The Ohio State University B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 1

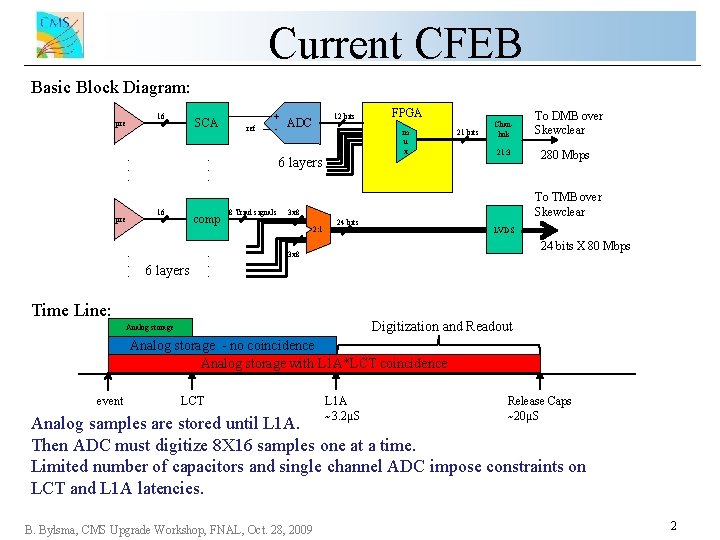

Current CFEB Basic Block Diagram: 16 pre SCA . . . + - . . . 16 pre ref comp 6 layers . . . 12 bits ADC m u x 6 layers 8 Triad signals FPGA 21 bits Chanlink 21: 3 280 Mbps To TMB over Skewclear 3 x 8 2: 1 To DMB over Skewclear 24 bits LVDS 24 bits X 80 Mbps 3 x 8 Time Line: Digitization and Readout Analog storage - no coincidence Analog storage with L 1 A*LCT coincidence event LCT L 1 A ~3. 2µS Release Caps ~20µS Analog samples are stored until L 1 A. Then ADC must digitize 8 X 16 samples one at a time. Limited number of capacitors and single channel ADC impose constraints on LCT and L 1 A latencies. B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 2

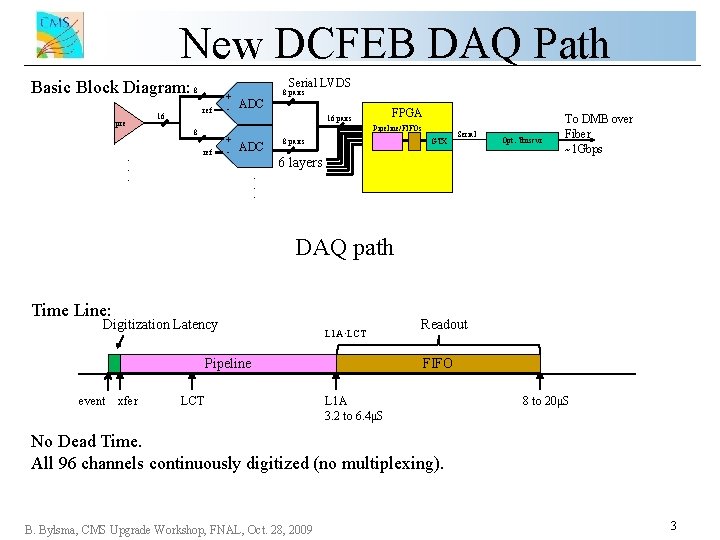

New DCFEB DAQ Path Serial LVDS Basic Block Diagram: 8 ref 16 pre ADC FPGA 16 pairs Pipeline/FIFOs 8. . . + - 8 pairs ref + - ADC GTX 8 pairs Serial 6 layers Opt. Trnscvr To DMB over Fiber ~1 Gbps . . . DAQ path Time Line: Digitization Latency L 1 A·LCT Pipeline event xfer LCT Readout FIFO L 1 A 3. 2 to 6. 4µS 8 to 20µS No Dead Time. All 96 channels continuously digitized (no multiplexing). B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 3

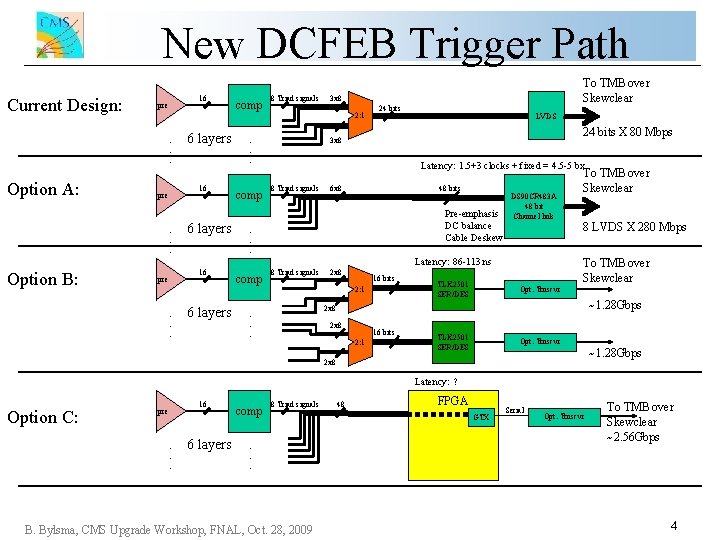

New DCFEB Trigger Path Current Design: 16 pre . . . Option A: 6 layers 16 pre . . . 6 layers comp 8 Triad signals comp 3 x 8 2: 1 . . . To TMB over Skewclear 24 bits LVDS 24 bits X 80 Mbps 3 x 8 Latency: 1. 5+3 clocks + fixed = 4. 5 -5 bx 8 Triad signals 6 x 8 48 bits Pre-emphasis DC balance Cable Deskew . . . DS 90 CR 483 A 48 bit Channel link 8 LVDS X 280 Mbps Latency: 86 -113 ns Option B: 16 pre . . . 6 layers comp 8 Triad signals 2 x 8 16 bits 2: 1 To TMB over Skewclear TLK 2501 SER/DES Opt. Trnscvr ~1. 28 Gbps 2 x 8 . . . 2 x 8 16 bits 2: 1 ~1. 28 Gbps 2 x 8 Latency: ? Option C: 16 pre . . . 6 layers comp 8 Triad signals . . . B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 48 FPGA GTX Serial Opt. Trnscvr To TMB over Skewclear ~2. 56 Gbps 4

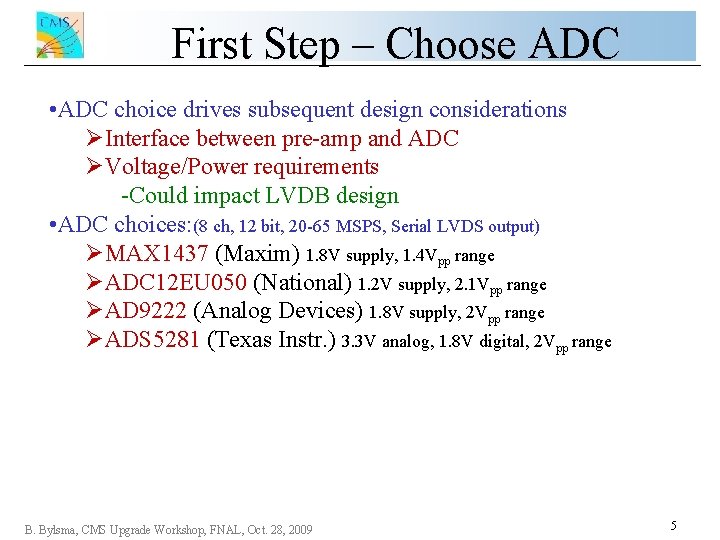

First Step – Choose ADC • ADC choice drives subsequent design considerations ØInterface between pre-amp and ADC ØVoltage/Power requirements -Could impact LVDB design • ADC choices: (8 ch, 12 bit, 20 -65 MSPS, Serial LVDS output) ØMAX 1437 (Maxim) 1. 8 V supply, 1. 4 Vpp range ØADC 12 EU 050 (National) 1. 2 V supply, 2. 1 Vpp range ØAD 9222 (Analog Devices) 1. 8 V supply, 2 Vpp range ØADS 5281 (Texas Instr. ) 3. 3 V analog, 1. 8 V digital, 2 Vpp range B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 5

Issues with ADCs • None are suitable drop-in replacements for SCA/ADC -ADC’s §All have differential inputs §Limits on common mode §Have internal input bias network -Pre-Amp §Single ended output §Limited range of baseline level §Designed to drive small capacitive load -Pre-Amp/ADC Interface §Mnfr. suggest transformer coupling (not an option for us) §Amplifier to generate differential signal (requires 96 amplifiers) §Direct couple single ended signal (common mode consequences) (level shifting/scaling) §AC couple single ended signal (common mode consequences) (no level shifting, but still have biasing to consider) B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 6

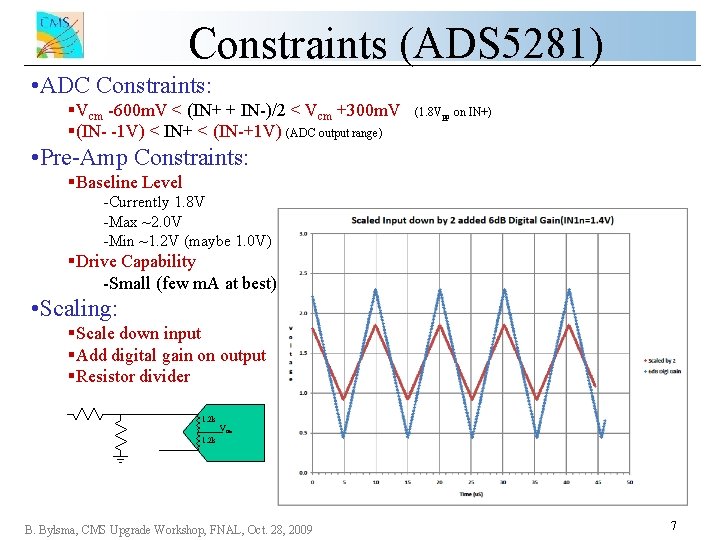

Constraints (ADS 5281) • ADC Constraints: §Vcm -600 m. V < (IN+ + IN-)/2 < Vcm +300 m. V §(IN- -1 V) < IN+ < (IN-+1 V) (ADC output range) (1. 8 Vpp on IN+) • Pre-Amp Constraints: §Baseline Level -Currently 1. 8 V -Max ~2. 0 V -Min ~1. 2 V (maybe 1. 0 V) §Drive Capability -Small (few m. A at best) • Scaling: §Scale down input §Add digital gain on output §Resistor divider 1. 2 k Vcm 1. 2 k B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 7

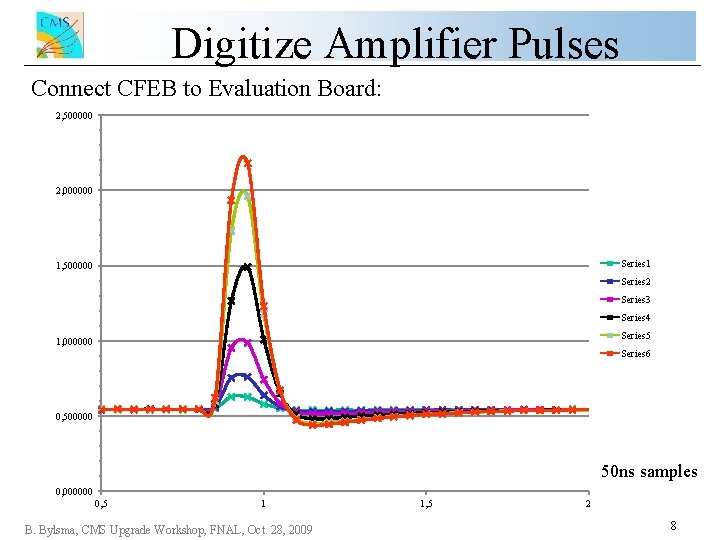

Digitize Amplifier Pulses Connect CFEB to Evaluation Board: 2, 500000 2, 000000 Series 1 1, 500000 Series 2 Series 3 Series 4 Series 5 1, 000000 Series 6 0, 500000 50 ns samples 0, 000000 0, 5 1 B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 1, 5 2 8

DCFEB Prototype Build prototype with four options for preamp/ADC interface Options include: ØDirect Coupling with scaling ØAC Coupling with scaling ØSingle to Differential with Analog Devices ADA 4950 ØSingle to Differential with TI THS 4524 DAQ path: ØVirtex 5 or 6 ØData sent in MAC level ethernet packets Trigger path: ØThree options (see slide 4) fiber or copper? ØMajor concern is additional latency (seems unavoidable) ØOther concerns: additional components/power consumption ØOn TMB end: compatibility with mezzanine board B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 9

Related Work Changes on ME 1/1 to accommodate DCFEBs: • 7 DCFEBs, same form factor (scheme exists) • Copper (and fiber) cables from DCFEBs to patch panel • New patch panel (copper cables 7 to 2) • New LVDB (power requirements TBD) Peripheral Crate: • New DMB (PCB design relatively straight forward) • New TMB (dependent on comparator transfer scheme) Decisions need to be made but should not be rushed B. Bylsma, CMS Upgrade Workshop, FNAL, Oct. 28, 2009 10

- Slides: 10