Sistemas Digitais Introduo ao Quartus II Introduo ao

- Slides: 25

Sistemas Digitais Introdução ao Quartus II

Introdução ao Quartus II l "Altera's Quartus® II software is such a superior development environment that I am quickly forgetting about any other PLD (programmable logic device) design tool. " – l Can Nguyen, Principal Staff Engineer, Broadband Communications Sector, Motorola "Quartus® II software is superior compared to other programmable logic tool offerings, which allows us to focus our time on meeting customer needs, rather than laboring over tool usage. “ – Dr. Greg Caso, VP Engineering, Escape Communications Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

Introdução ao Quartus II – Características l Entradas baseadas em texto (VHDL) ou diagrama esquemático (block diagram) l Projeto com uso de funções (blocos) de bibliotecas – – portas lógicas, flip-flops, pinos e outras primitivas possibilidade de criação de biblioteca do usuário (permite criação de símbolos) l Ferramentas para simulação e análise das saídas dos circuitos (waveforms) l Software integrado para geração de sistemas/plataformas: SOPC Builder l Conselheiro para otimização de temporização e recursos l Implementação na plataforma UP 1 Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

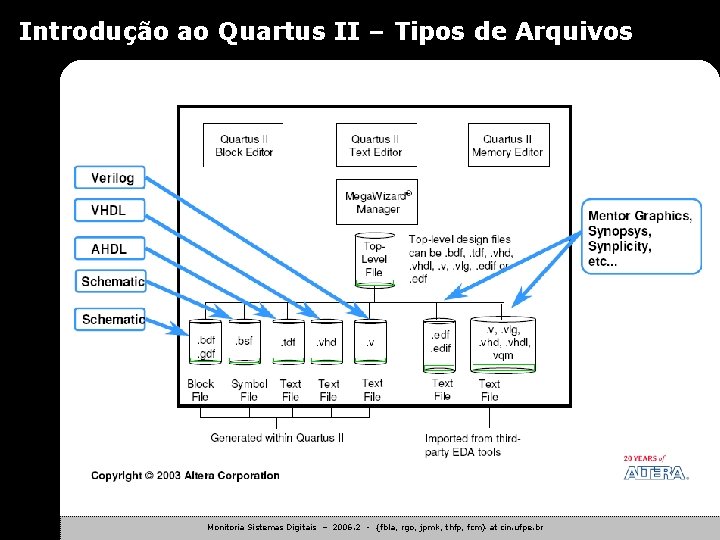

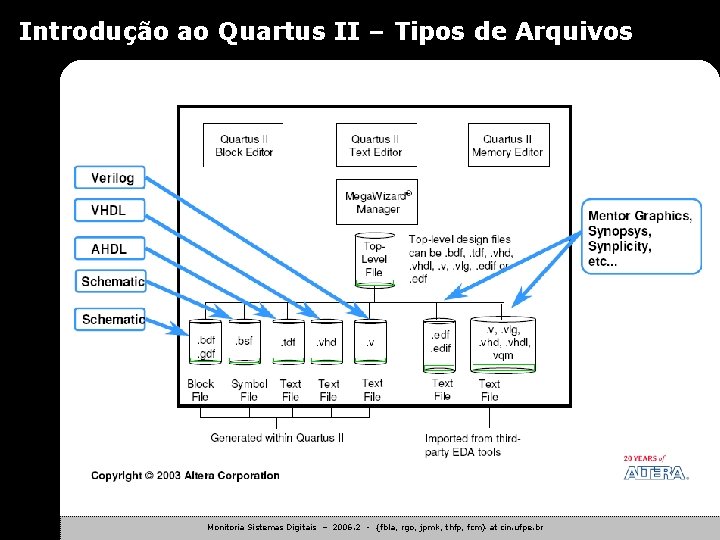

Introdução ao Quartus II – Tipos de Arquivos Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

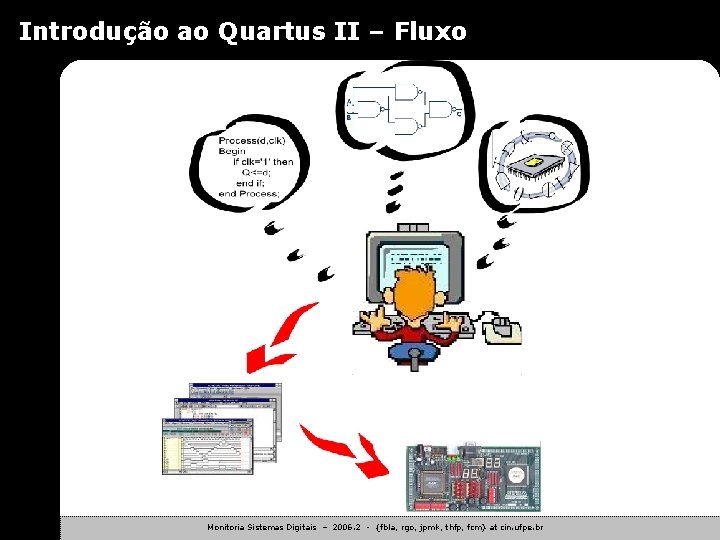

Introdução ao Quartus II – Fluxo l Fluxo de Desenvolvimento – – – Concepção do sistema em VHDL ou esquemático Submissão das entradas no sistema Simulação Correção de erros, quando necessário Implementação na UP 1 Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

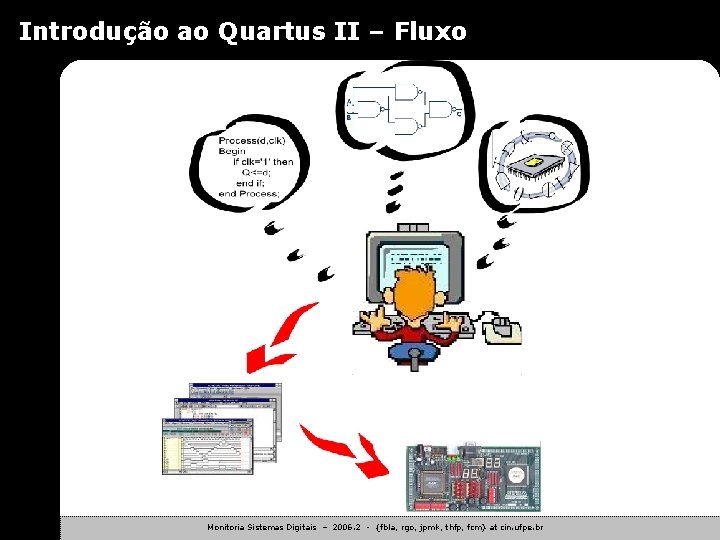

Introdução ao Quartus II – Fluxo Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

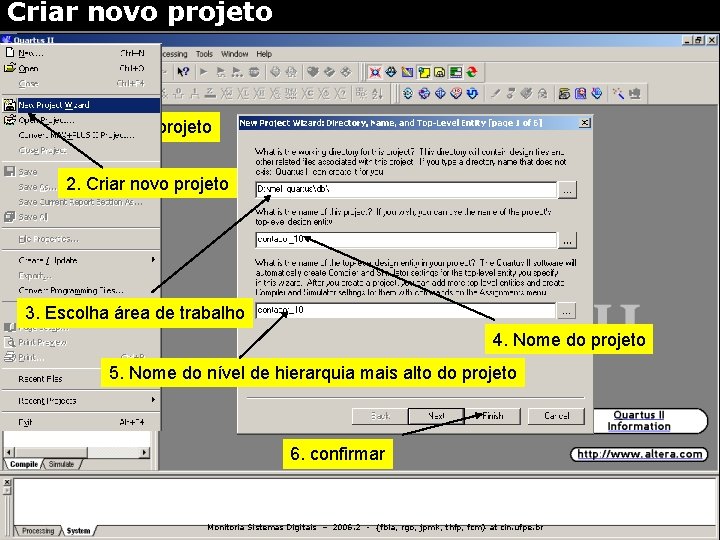

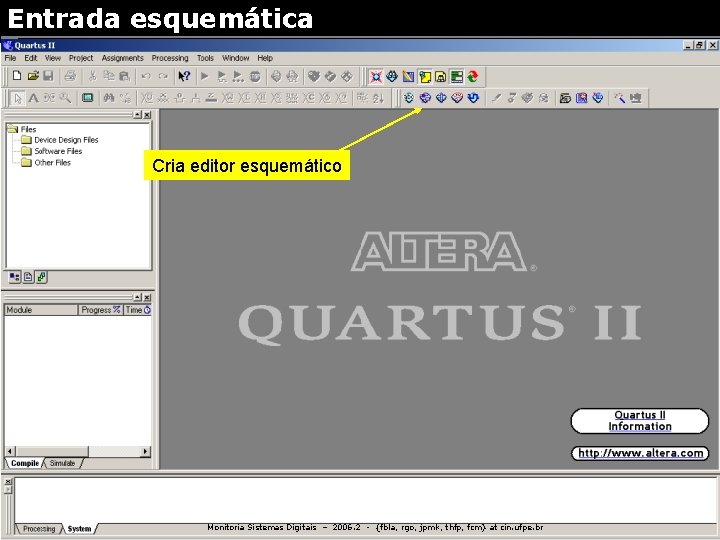

Introdução ao Quartus II – Ambiente l Ambiente de Projeto – – Criar novo projeto Entrada esquemática l – – Editor Compilar/mapear circuito no FPGA Simulação l Resultado (waveforms) Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

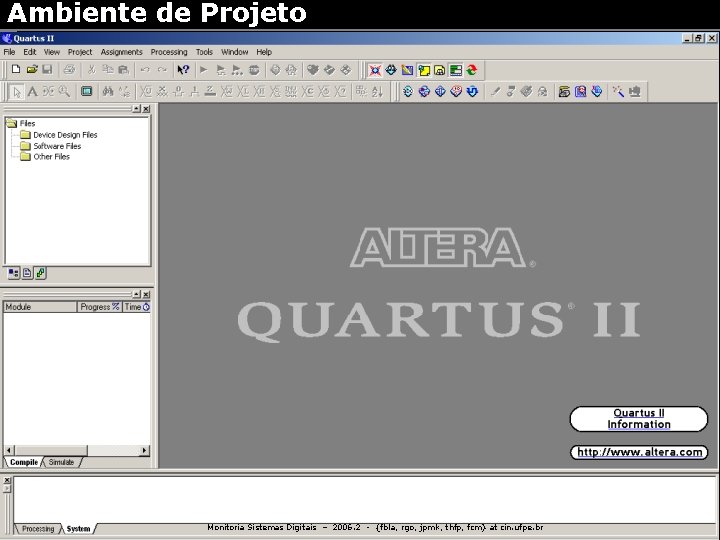

Ambiente de Projeto Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

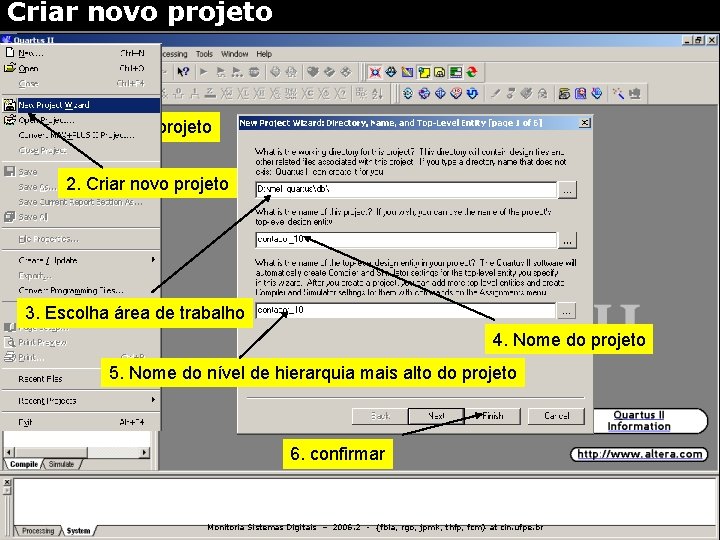

Criar novo projeto 1. Criar novo projeto 2. Criar novo projeto 3. Escolha área de trabalho 4. Nome do projeto 5. Nome do nível de hierarquia mais alto do projeto 6. confirmar Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

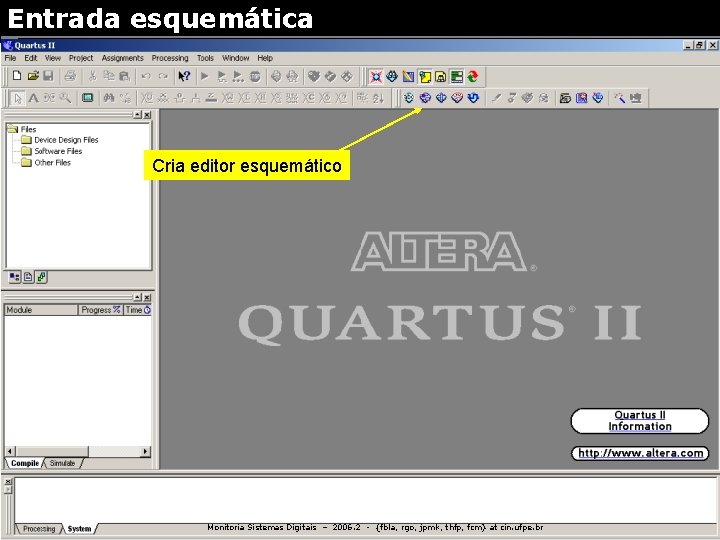

Entrada esquemática Cria editor esquemático Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

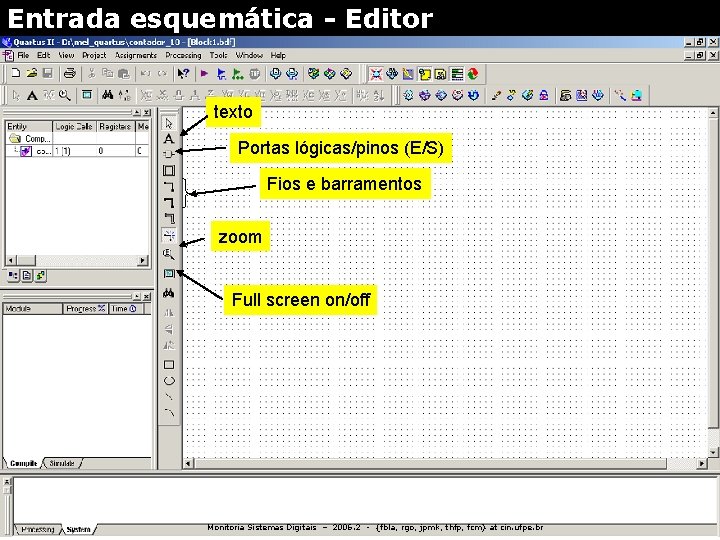

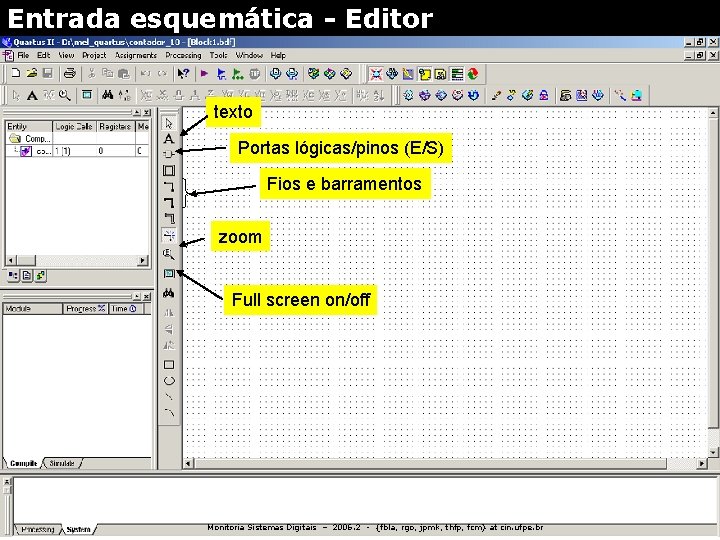

Entrada esquemática - Editor texto Portas lógicas/pinos (E/S) Fios e barramentos zoom Full screen on/off Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

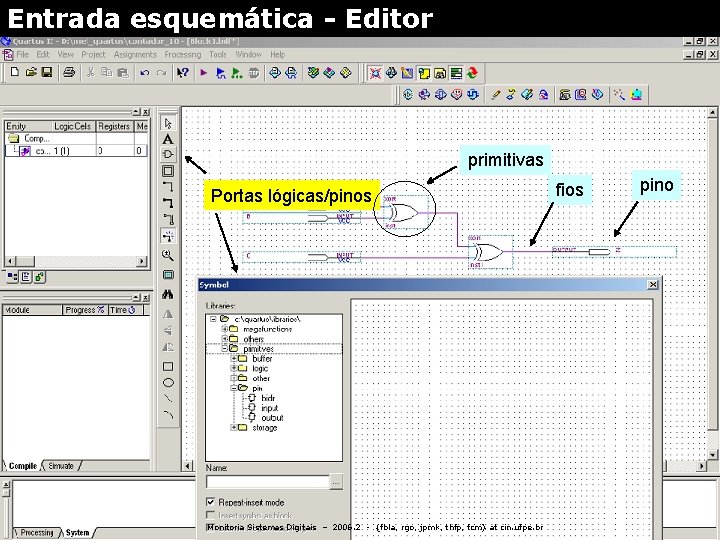

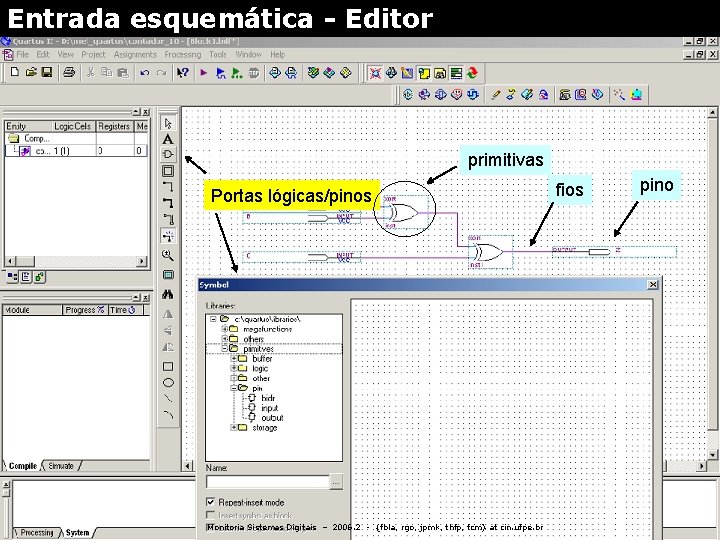

Entrada esquemática - Editor primitivas Portas lógicas/pinos Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br fios pino

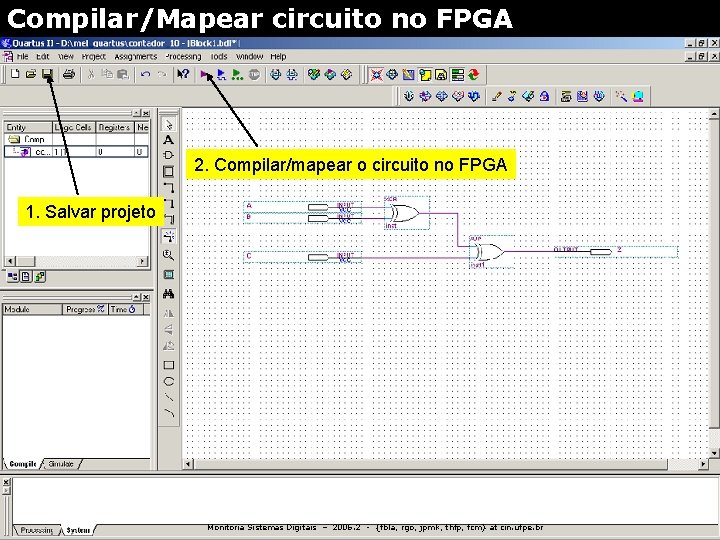

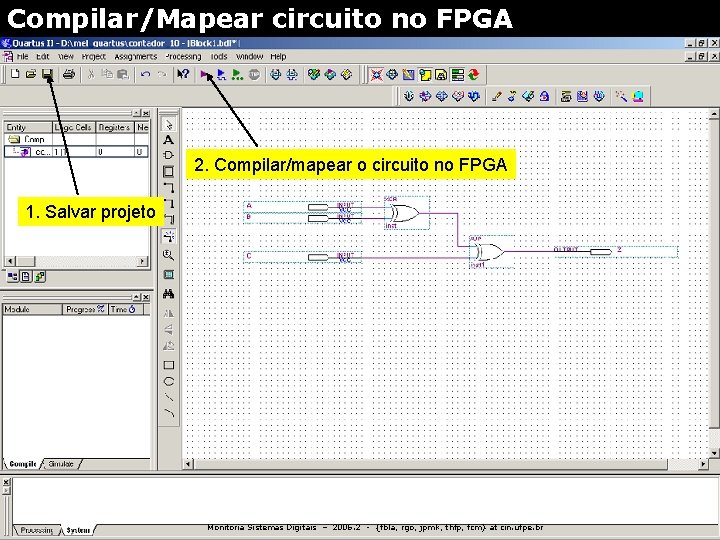

Compilar/Mapear circuito no FPGA 2. Compilar/mapear o circuito no FPGA 1. Salvar projeto Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

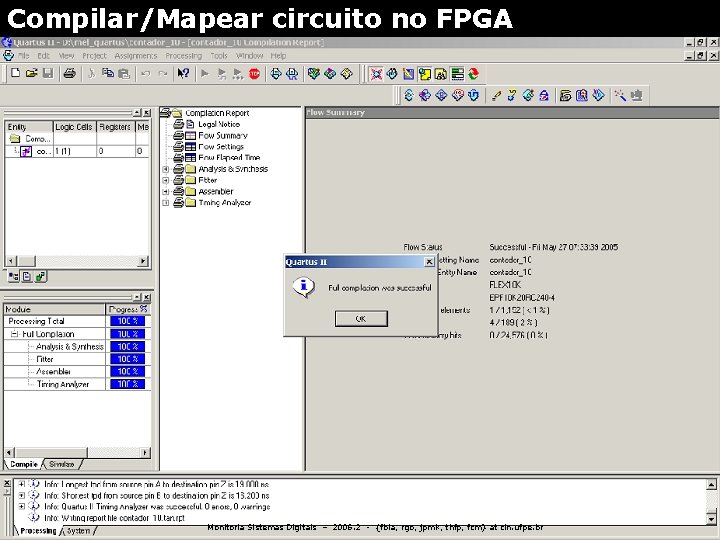

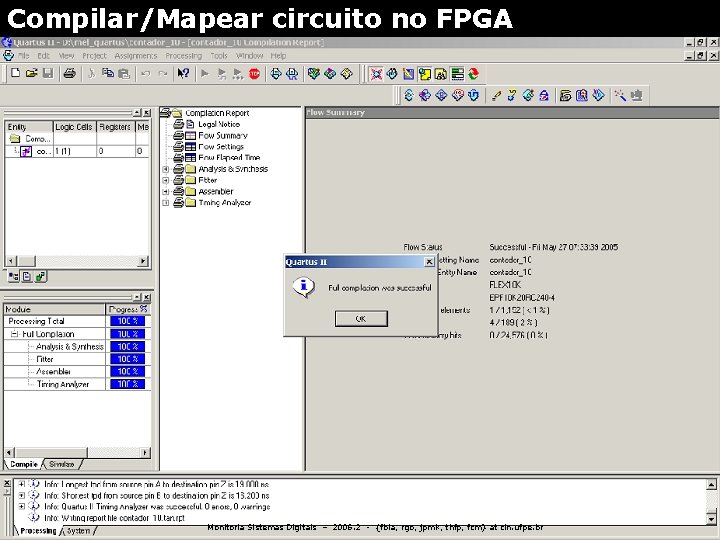

Compilar/Mapear circuito no FPGA Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

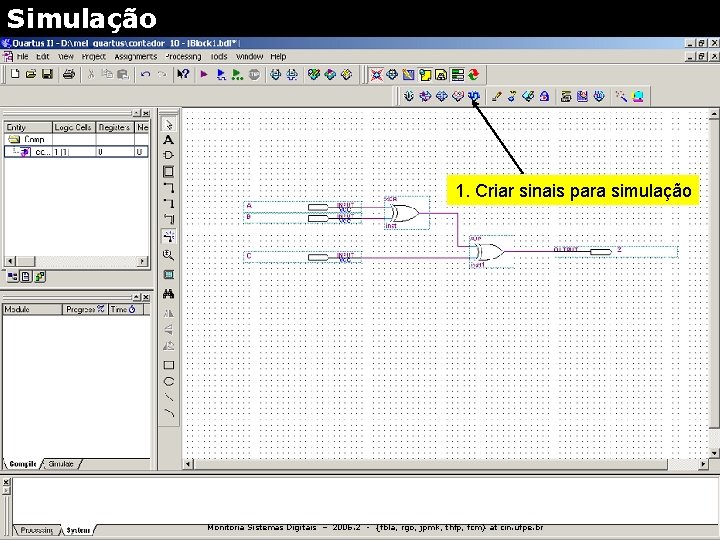

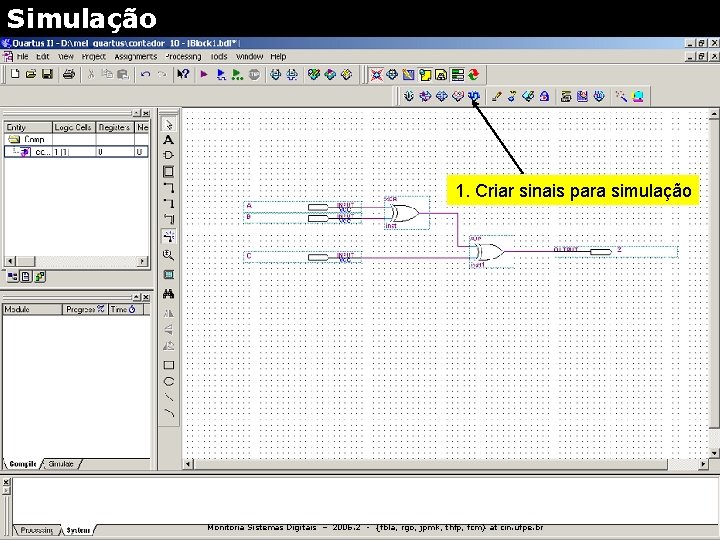

Simulação 1. Criar sinais para simulação Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

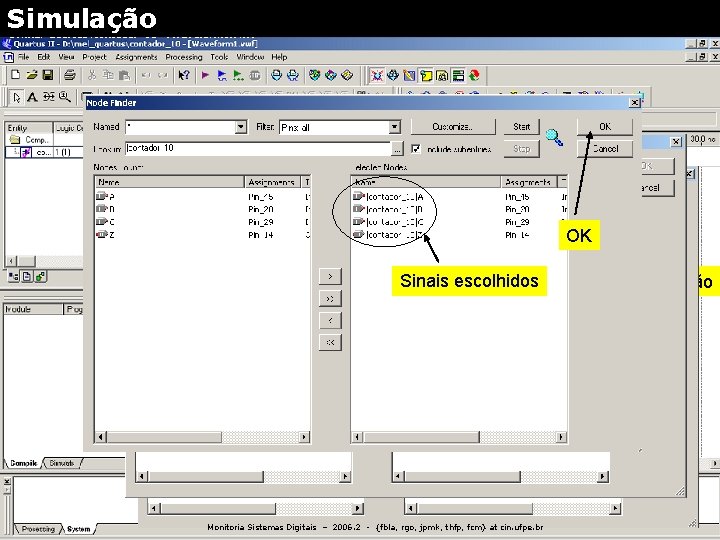

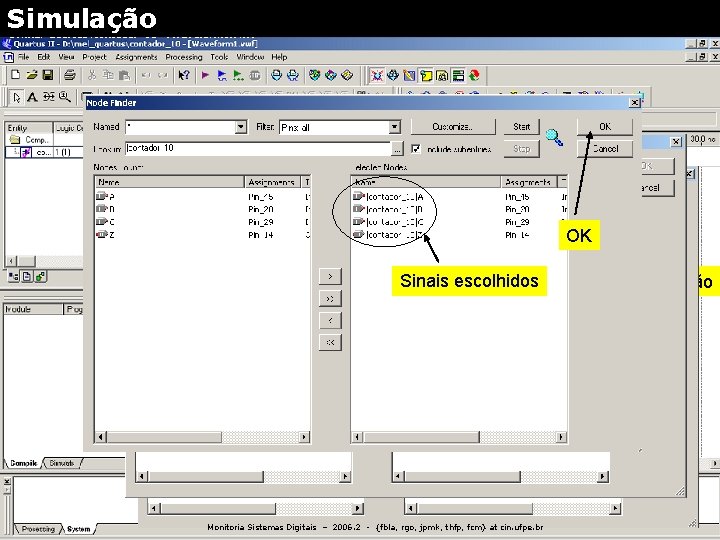

Simulação 4. Start 2. Click (botão direito) OK Sinais escolhidos 3. Selecione sinais p/simulação 4. Escolha sinais Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

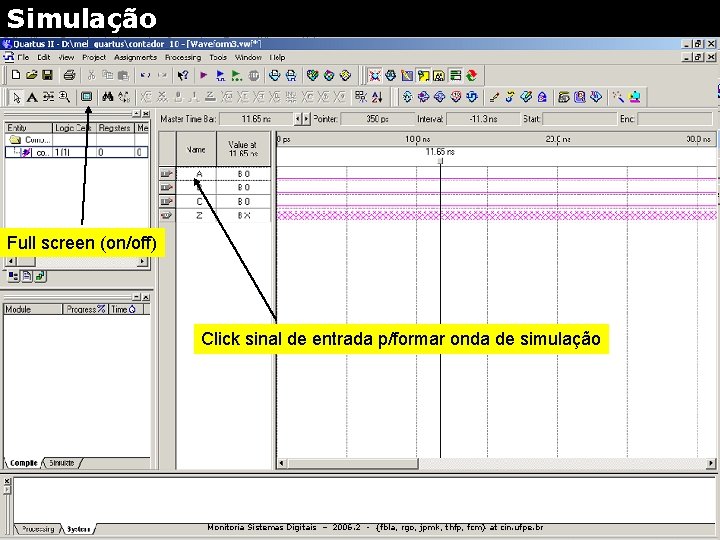

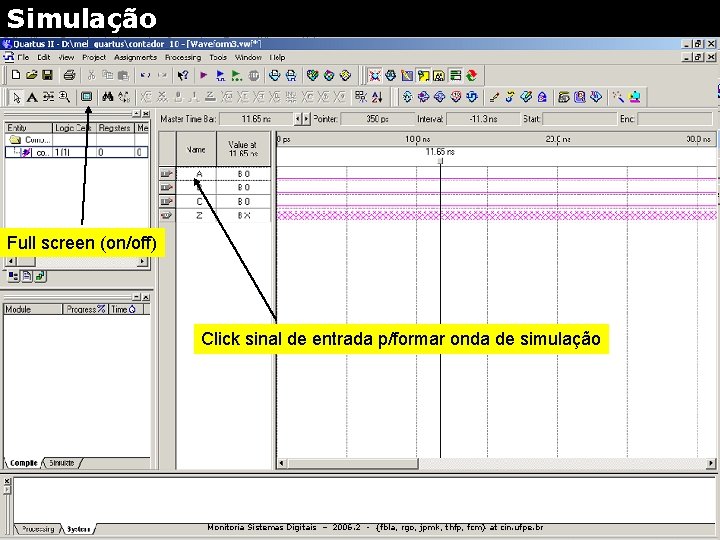

Simulação Full screen (on/off) Click sinal de entrada p/formar onda de simulação Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

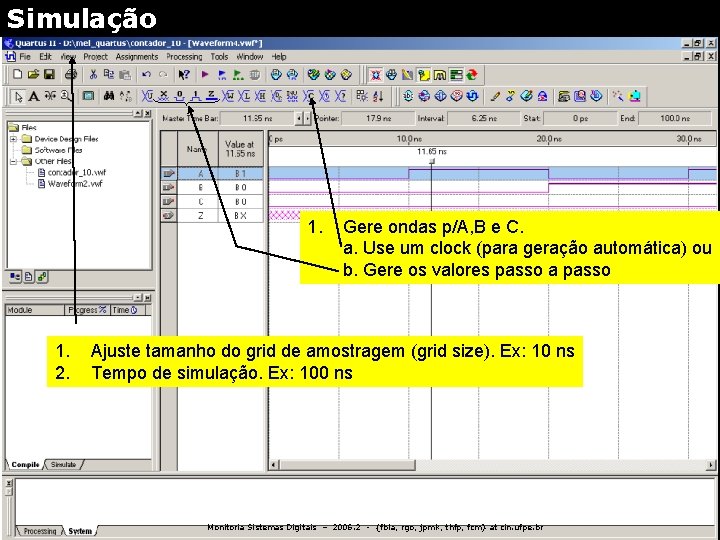

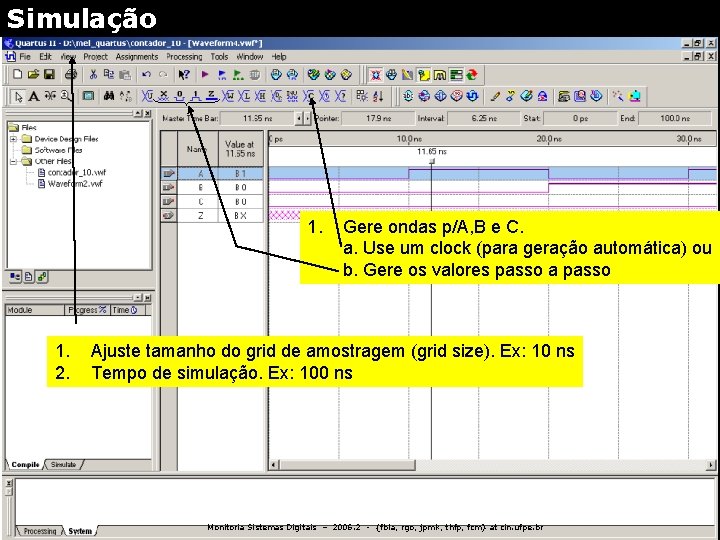

Simulação 1. 2. Gere ondas p/A, B e C. a. Use um clock (para geração automática) ou b. Gere os valores passo a passo Ajuste tamanho do grid de amostragem (grid size). Ex: 10 ns Tempo de simulação. Ex: 100 ns Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

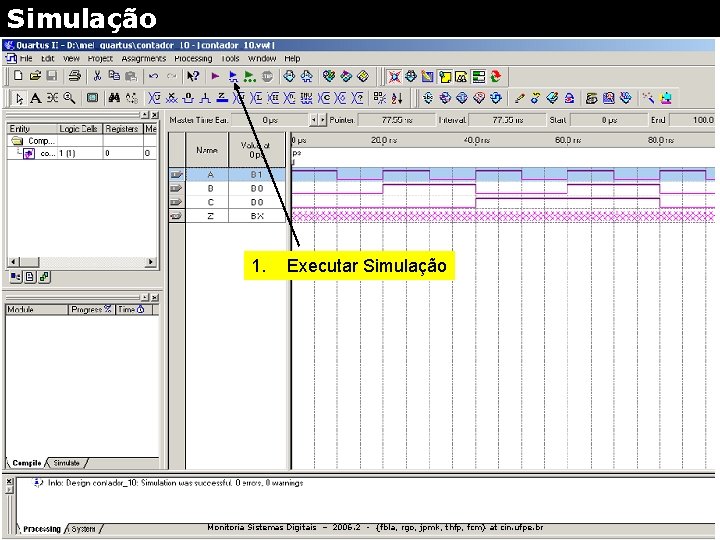

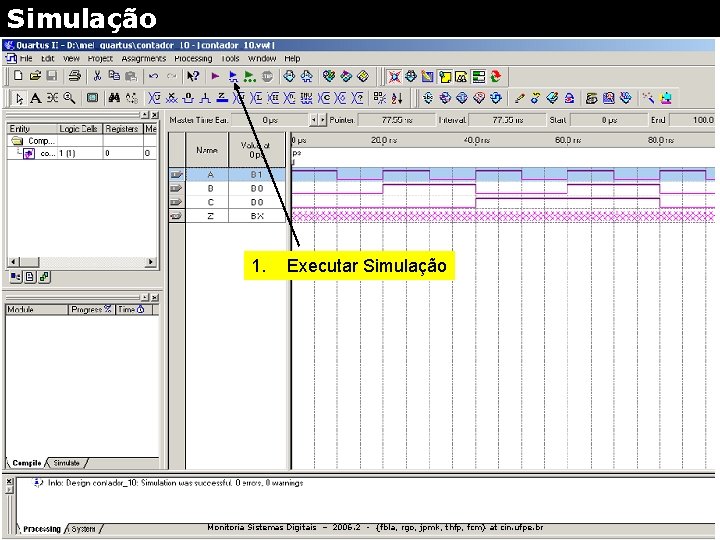

Simulação 1. Executar Simulação Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

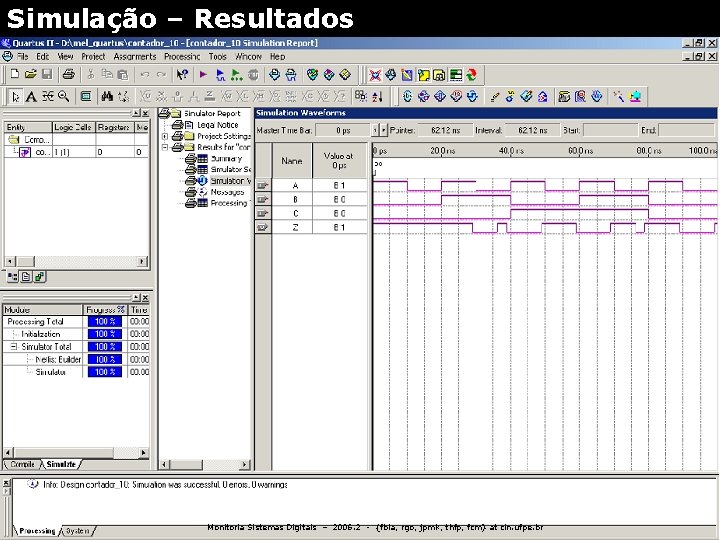

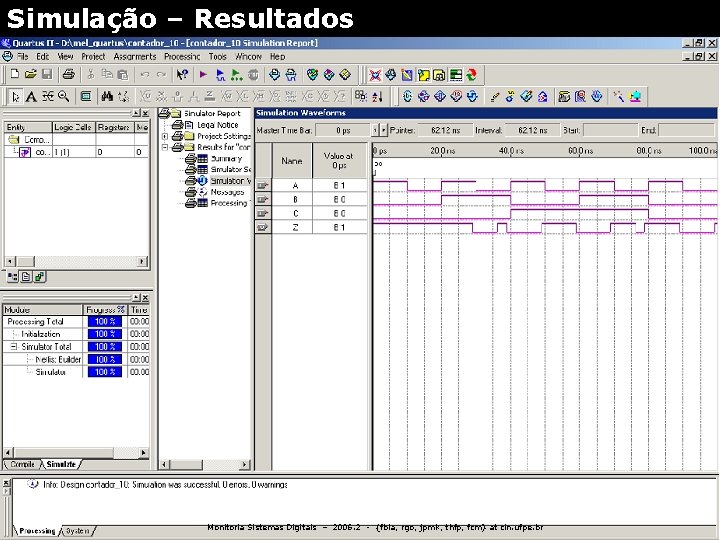

Simulação – Resultados Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

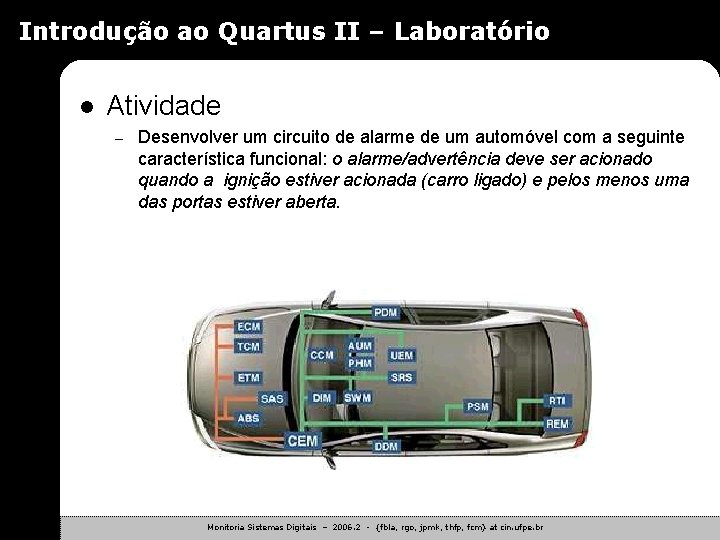

Introdução ao Quartus II – Laboratório l Atividade – Desenvolver um circuito de alarme de um automóvel com a seguinte característica funcional: o alarme/advertência deve ser acionado quando a ignição estiver acionada (carro ligado) e pelos menos uma das portas estiver aberta. Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

Introdução ao Quartus II – Laboratório l Atividade – Etapas do projeto: l l l Identificar os sinais de entrada e de saída do circuito; Levantar a tabela verdade do circuito; Deduzir e otimizar as equações booleanas da cada sinal de saída; Implementar o circuito no Quartus II; Baixar o circuito na UP 1 (plataforma de prototipação da Altera). Essa atividade deve ser apresentada até o final desta aula! Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

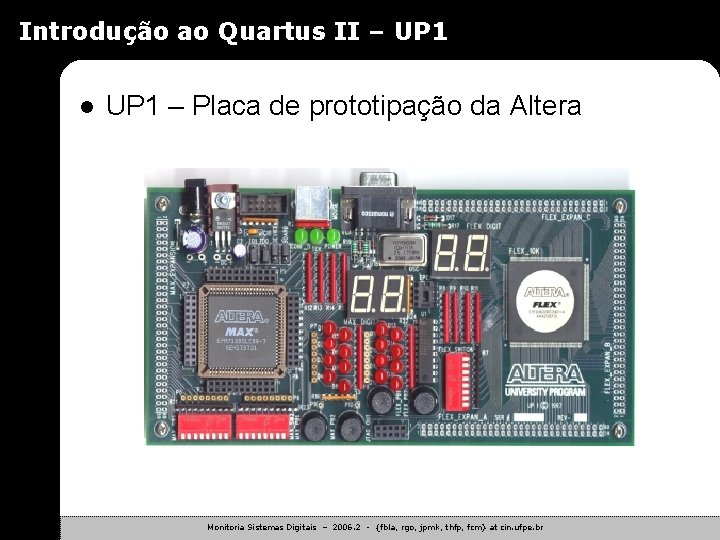

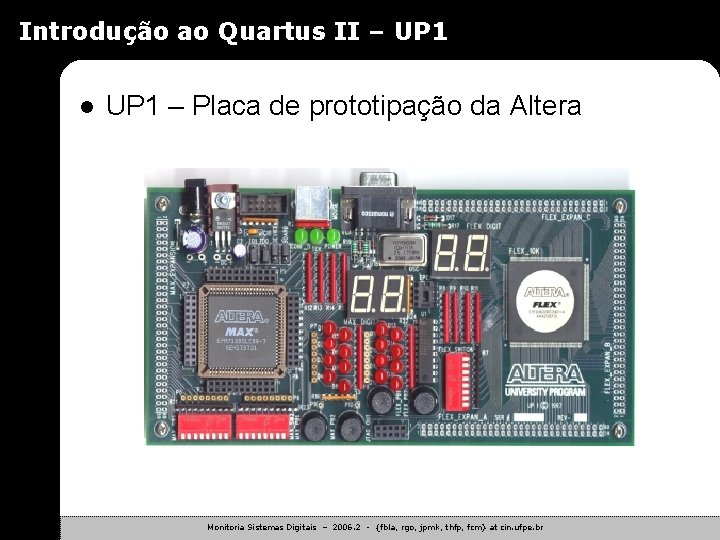

Introdução ao Quartus II – UP 1 l UP 1 – Placa de prototipação da Altera Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

Introdução ao Quartus II – Sugestões l Sugestões de Leitura: – Introduction to Quartus II (pdf) l – Getting Started With Quartus II Software l – http: //www. altera. com/products/software/products/quartus 2/getting-started/qtsgetting-started. html Quartus II Development Software Version 6. 0 Literature l l www. cin. ufpe. br/~if 675/arquivos/referencias/manuais/intro_to_quartus 2. pdf http: //www. altera. com/literature/lit-qts. jsp Sugestão de download: – Quartus II Web Edition Software Version 6. 0 l http: //www. altera. com/products/software/products/quartus 2 web/sofquarwebmain. html Monitoria Sistemas Digitais – 2006. 2 - {fbla, rgo, jpmk, thfp, fcm} at cin. ufpe. br

Sistemas Digitais Introdução ao Quartus II