Sistem Nombor Get Logik SISTEM NOMBOR ALGEBRA BOOLEAN

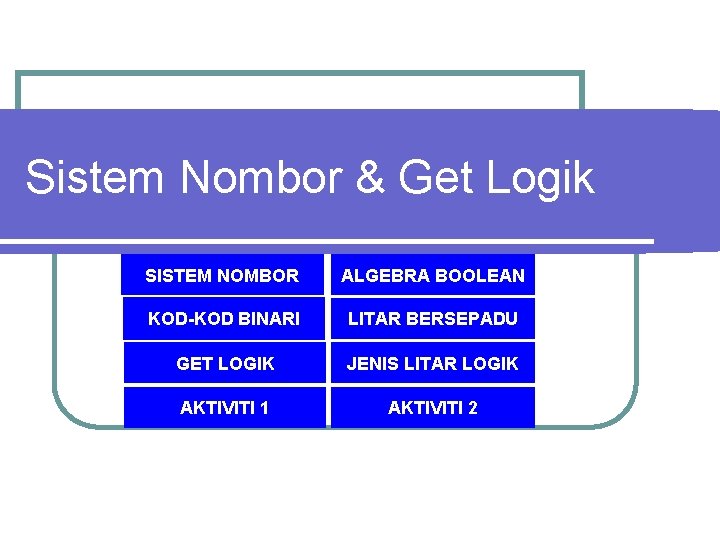

Sistem Nombor & Get Logik SISTEM NOMBOR ALGEBRA BOOLEAN KOD-KOD BINARI LITAR BERSEPADU GET LOGIK JENIS LITAR LOGIK AKTIVITI 1 AKTIVITI 2

GET LOGIK l Logik dalam sistem Binari digunakan untuk menyatakan proses dan operasi sesuatu maklumat Binari dari segi penyataan matematik! l Logik Binari terdiri pembolehubah Binari dan juga ‘operasi logik’. l Operasi ini memerlukan get-get logik.

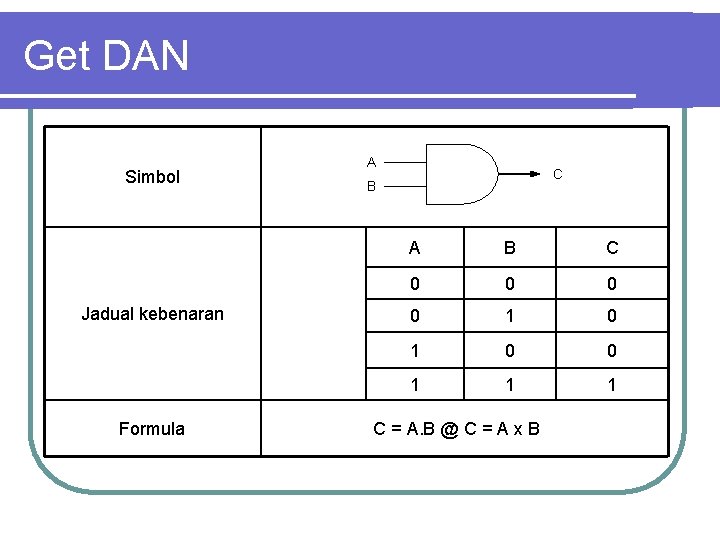

Get DAN Simbol Jadual kebenaran Formula A C B A B C 0 0 1 1 1 C = A. B @ C = A x B

Get ATAU Simbol Jadual kebenaran Formula A C B A B C 0 0 1 1 1 0 1 1 C=A+B

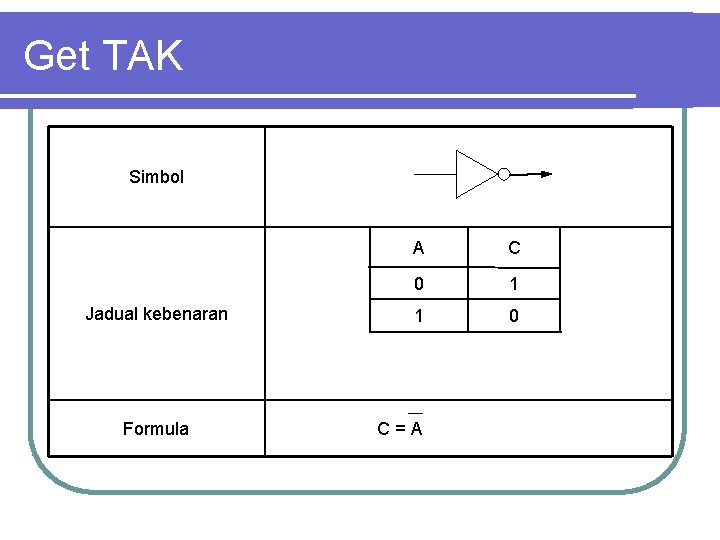

Get TAK Simbol Jadual kebenaran Formula A C 0 1 1 0 C=A

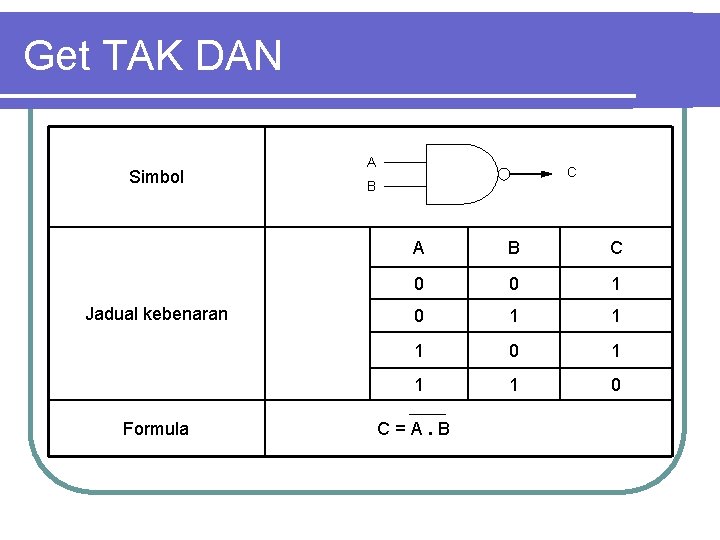

Get TAK DAN Simbol Jadual kebenaran Formula A C B A B C 0 0 1 1 1 0 C=A. B

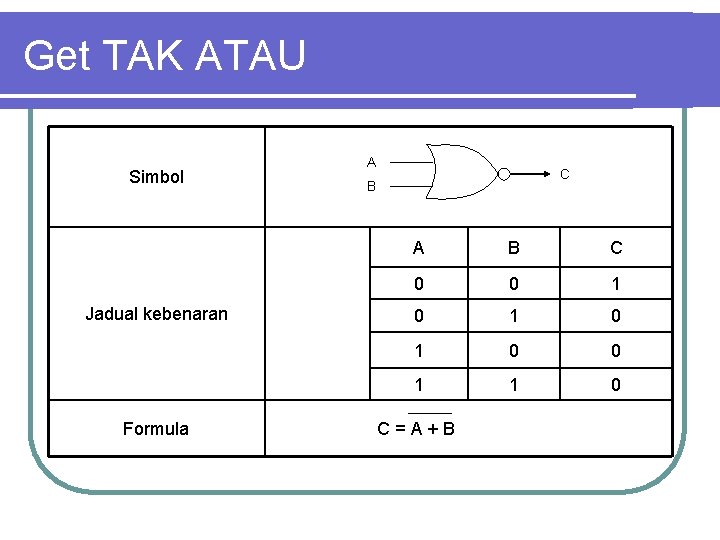

Get TAK ATAU Simbol Jadual kebenaran Formula A C B A B C 0 0 1 0 1 0 0 1 1 0 C=A+B

Get Eksklusif ATAU Simbol Jadual kebenaran Formula A C B A B C 0 0 1 1 1 0 C=A. B+A. B=A B

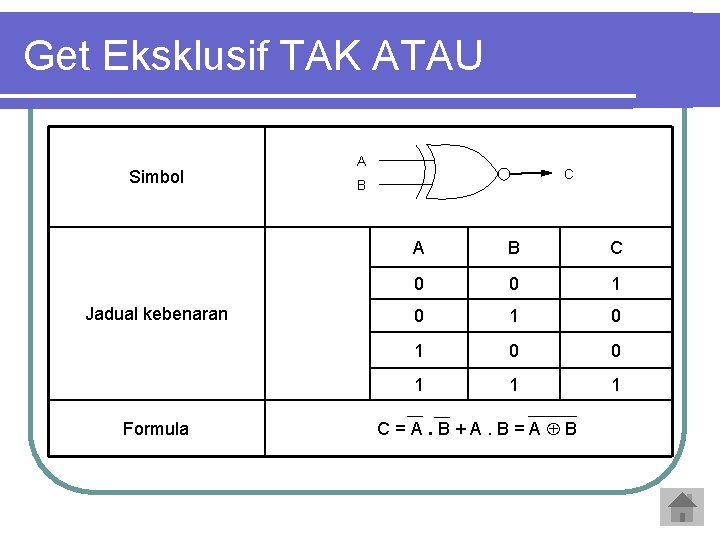

Get Eksklusif TAK ATAU Simbol Jadual kebenaran Formula A C B A B C 0 0 1 0 1 0 0 1 1 1 C=A. B+A. B=A B

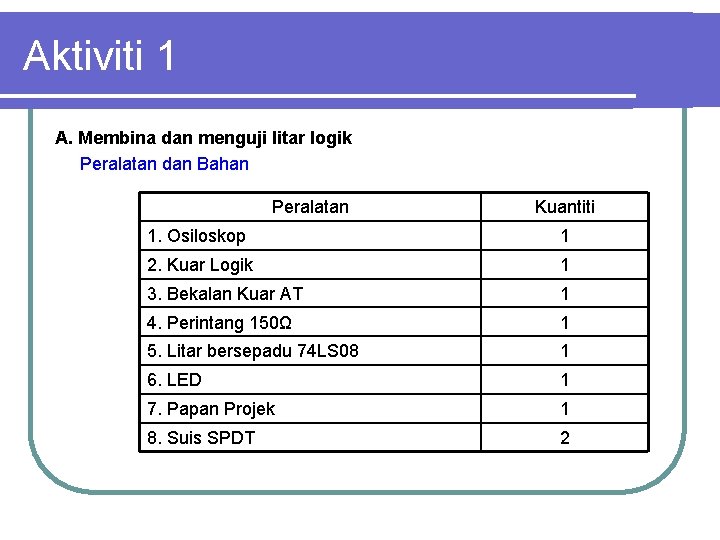

Aktiviti 1 A. Membina dan menguji litar logik Peralatan dan Bahan Peralatan Kuantiti 1. Osiloskop 1 2. Kuar Logik 1 3. Bekalan Kuar AT 1 4. Perintang 150Ω 1 5. Litar bersepadu 74 LS 08 1 6. LED 1 7. Papan Projek 1 8. Suis SPDT 2

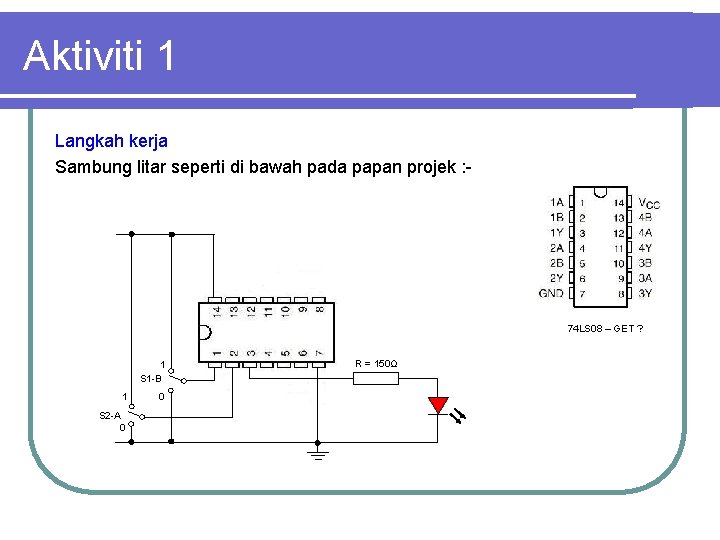

Aktiviti 1 Langkah kerja Sambung litar seperti di bawah pada papan projek : - 74 LS 08 – GET ? 1 S 1 -B 1 S 2 -A 0 0 R = 150Ω

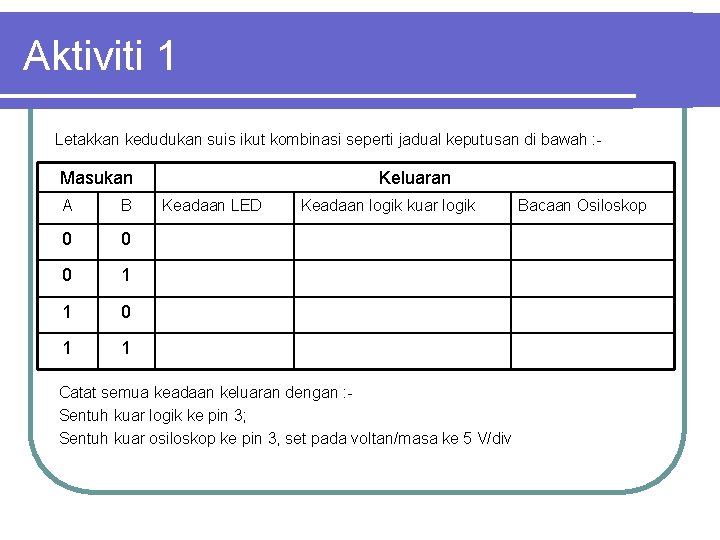

Aktiviti 1 Letakkan kedudukan suis ikut kombinasi seperti jadual keputusan di bawah : - Masukan A B 0 0 0 1 1 Keluaran Keadaan LED Keadaan logik kuar logik Catat semua keadaan keluaran dengan : Sentuh kuar logik ke pin 3; Sentuh kuar osiloskop ke pin 3, set pada voltan/masa ke 5 V/div Bacaan Osiloskop

Aktiviti 1 Perbincangan Apakah keadaan LED apabila keluaran berada pada logik 1. Berapakah voltan yang mewakili logik 1. Kesimpulan Dari ujikaji, apakah get pada litar bersepadu 74 LS 08.

Litar-litar Logik l Litar logik digital terdiri daripada 2 kategori iaitu: Litar logik gabungan (COMBINATIONAL) l Litar logik jujukan (SEQUENTIAL) l

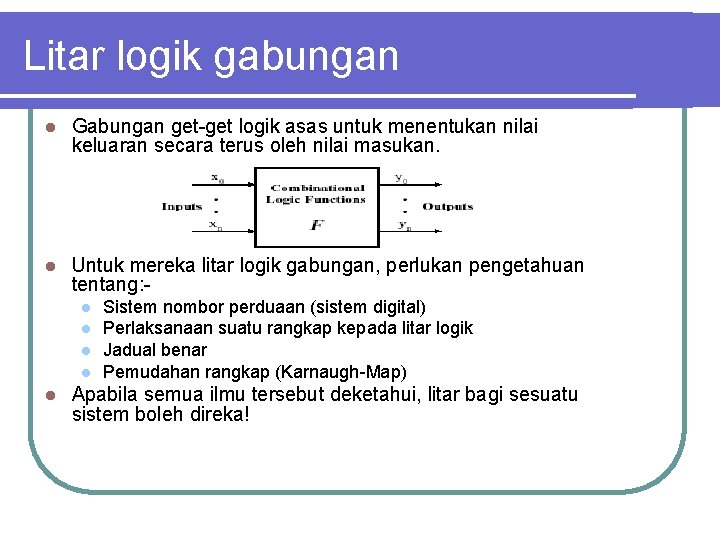

Litar logik gabungan l Gabungan get-get logik asas untuk menentukan nilai keluaran secara terus oleh nilai masukan. l Untuk mereka litar logik gabungan, perlukan pengetahuan tentang: l l l Sistem nombor perduaan (sistem digital) Perlaksanaan suatu rangkap kepada litar logik Jadual benar Pemudahan rangkap (Karnaugh-Map) Apabila semua ilmu tersebut deketahui, litar bagi sesuatu sistem boleh direka!

Litar logik gabungan l Beberapa jenis litar logik gabungan yang digunakan sumber alamat dalam ingatan: Pengkod (Encoder) l Penyahkod (Decoder) l Pemultipleks (Multiplexer) l Nyahmultipleks (Demultiplexer) l Pembanding (Comparator) l Penambah-Penuh (Full-Adder) l

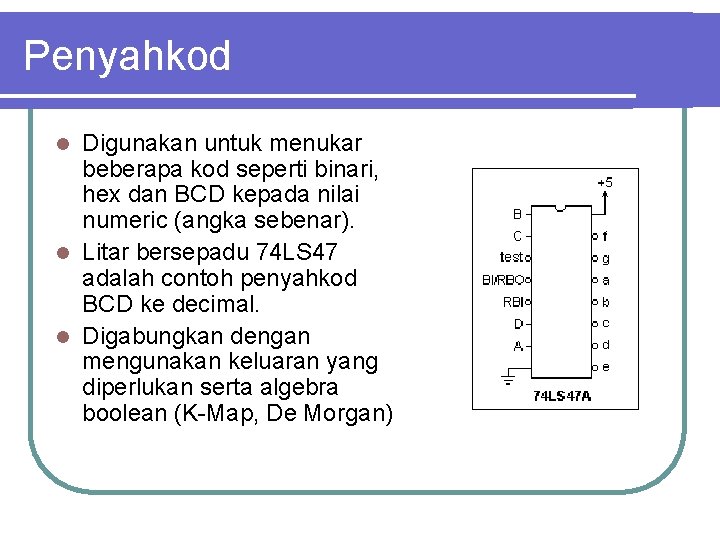

Penyahkod Digunakan untuk menukar beberapa kod seperti binari, hex dan BCD kepada nilai numeric (angka sebenar). l Litar bersepadu 74 LS 47 adalah contoh penyahkod BCD ke decimal. l Digabungkan dengan mengunakan keluaran yang diperlukan serta algebra boolean (K-Map, De Morgan) l

Litar Bersepadu (Integrated Circuit) l Cip Litar Bersepadu (IC Chip) terbahagi kepada beberapa jenis, berdasarkan bilangan get-get di dalamnya: l l l SSI (Smal Scale Integration), mengandungi kurang daripada 12 get-get asas per cip MSI (Medium Scale Integration), mengandungi 12 - 99 get-get asas per cip LSI (Large Scale Integration), mengandungi 100 999 get-get asas per cip VLSI (Very Large Scale Integration) mengandungi 10, 000 - 99, 999 get-get asas per cip ULSI (Ultra Large Scale Integration), mengandungi lebih 100, 000 get-get asas per cip

Litar Bersepadu l Keluarga Litar Bersepadu (IC Chip) yang utama terbahagi kepada 2 iaitu : l Bipolar Junction Transistor (BJT) l l l TTL ECL Metal Oxide Semiconductor (MOS) – drp FET l l l PMOS NMOS CMOS

Litar Bersepadu TTL (transistor-transistor logic) – yang merujuk kepada penggunaan BJT dalam pembinaannya. l Ada beberapa jenis TTL iaitu; standard TTL, low-power TTL, Schottky TTL, low-power Schottky TTL, advanced Schottky TTL. l CMOS (complementary metal oxide semiconductor) – merujuk kepada penggunaan PMOS dan NMOS dalam pembinaannya. l Sesuatu cip yang dibina dengan menggunakan TTL dan CMOS akan menjalankan fungsi dan operasi yang sama. Yang membezakannya hanyalah ciri prestasinya (performance characteristic). l

Algebra Boolean l Boolean Algebra adalah pernyataan matematik bagi sistem digit. l Penting untuk tujuan pemahaman dan analisis litar sistem digit.

Algebra Boolean l Hukum 1. Hukum Tukar-tertib (Commutative Laws) ABC = ACB = CBA A+B+C = B+C+A = C+A+B 2. Hukum Sekutuan (Associative Laws) A+(B+C) = (A+B)+C A(BC) = (AB)C 3. Hukum Taburan (Distributive Laws) A(B+C) = AB+AC

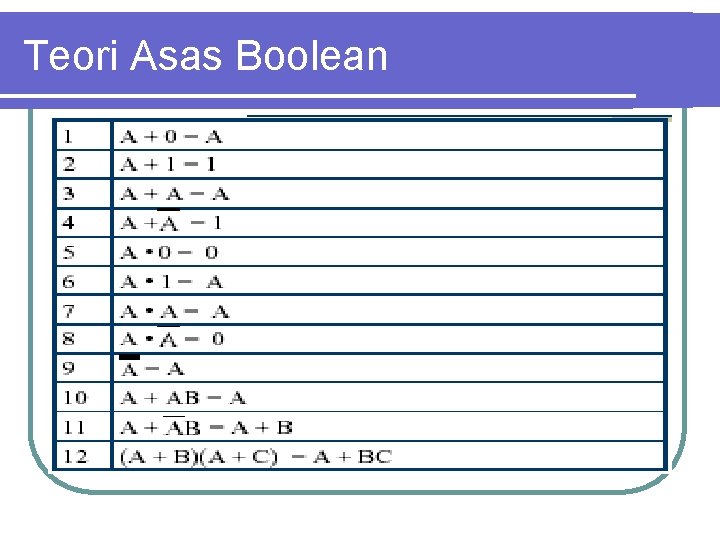

Teori Asas Boolean

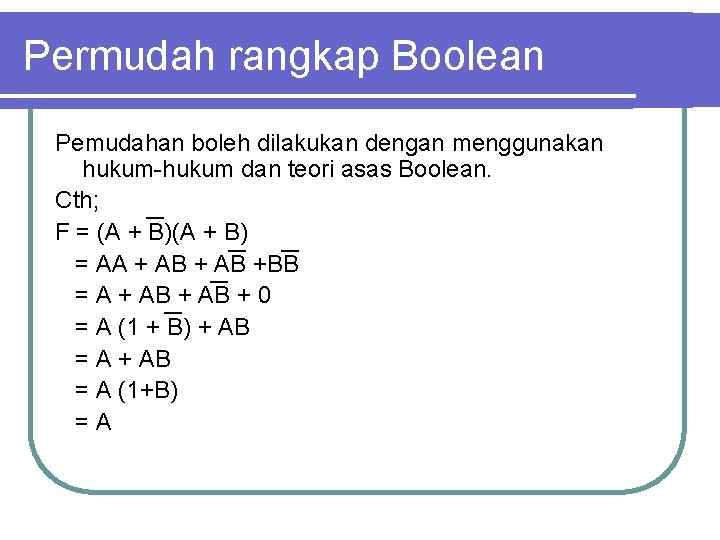

Permudah rangkap Boolean Pemudahan boleh dilakukan dengan menggunakan hukum-hukum dan teori asas Boolean. Cth; F = (A + B) = AA + AB +BB = A + AB + 0 = A (1 + B) + AB = A (1+B) =A

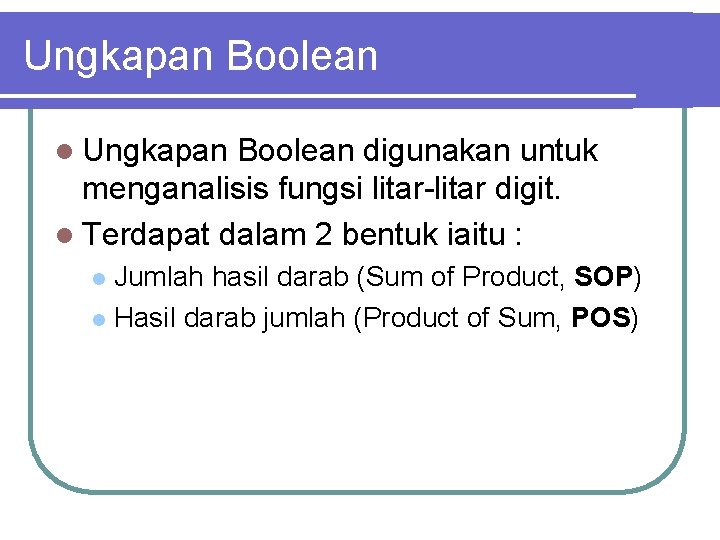

Ungkapan Boolean l Ungkapan Boolean digunakan untuk menganalisis fungsi litar-litar digit. l Terdapat dalam 2 bentuk iaitu : Jumlah hasil darab (Sum of Product, SOP) l Hasil darab jumlah (Product of Sum, POS) l

SOP(jumlah hasil darab) l Gabungan litar get DAN(hasil darab) dan ATAU(jumlah) l Contoh Y = AB + CD A B Y C D

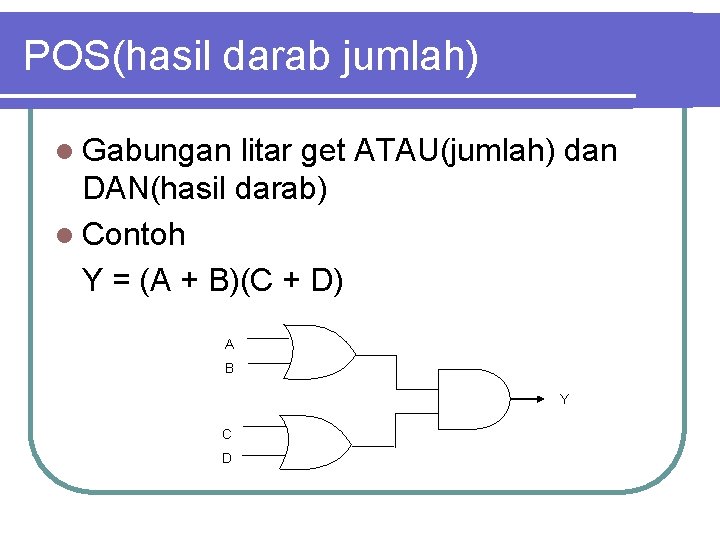

POS(hasil darab jumlah) l Gabungan litar get ATAU(jumlah) dan DAN(hasil darab) l Contoh Y = (A + B)(C + D) A B Y C D

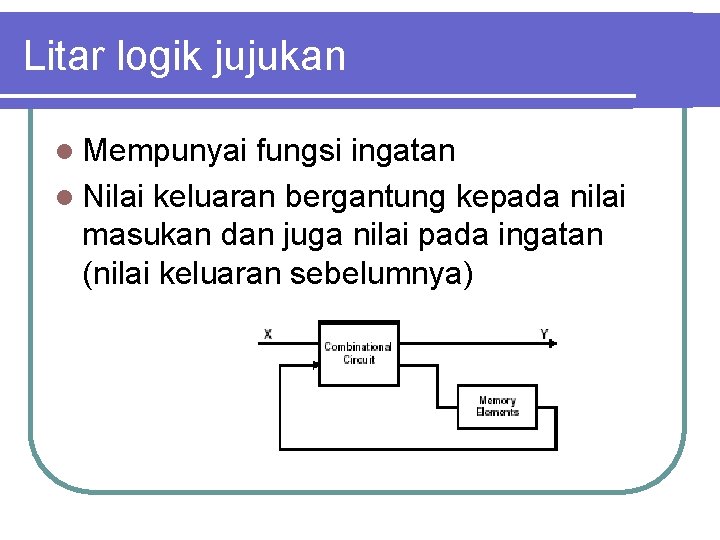

Litar logik jujukan l Mempunyai fungsi ingatan l Nilai keluaran bergantung kepada nilai masukan dan juga nilai pada ingatan (nilai keluaran sebelumnya)

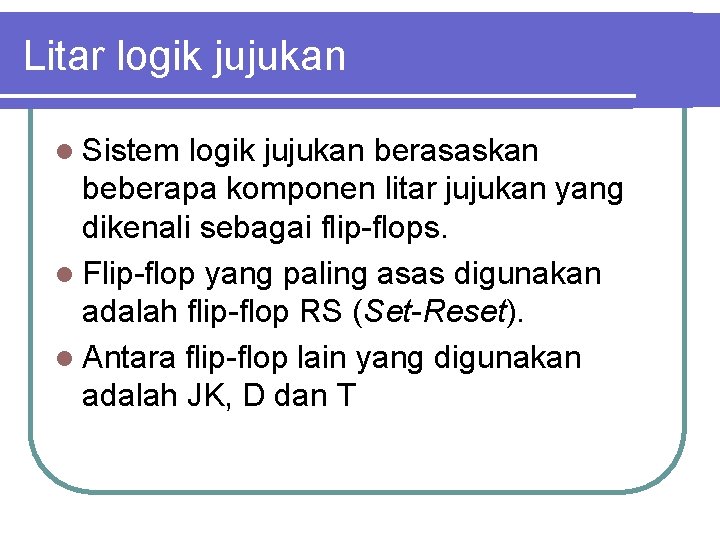

Litar logik jujukan l Sistem logik jujukan berasaskan beberapa komponen litar jujukan yang dikenali sebagai flip-flops. l Flip-flop yang paling asas digunakan adalah flip-flop RS (Set-Reset). l Antara flip-flop lain yang digunakan adalah JK, D dan T

Flip-Flop RS Tatarajah S Simbol Q Get TAK DAN S Q R R Q Q S Q Get TAK ATAU R Q

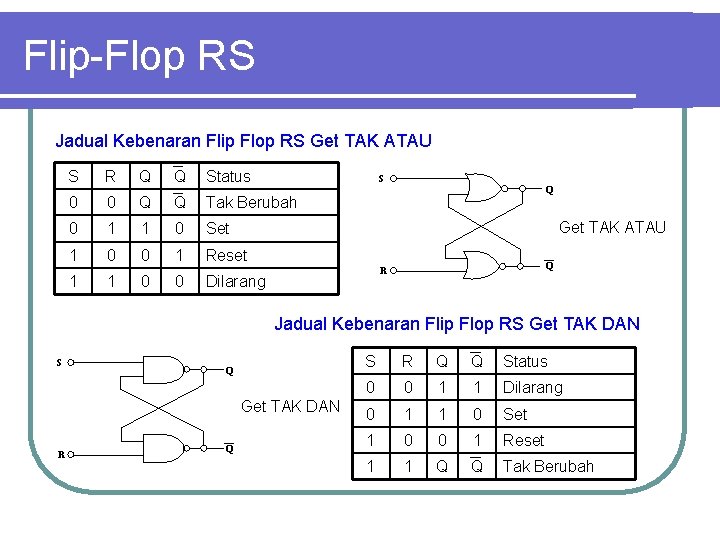

Flip-Flop RS Jadual Kebenaran Flip Flop RS Get TAK ATAU S R Q Q Status 0 0 Q Q Tak Berubah 0 1 1 0 Set 1 0 0 1 Reset 1 1 0 0 S Q Get TAK ATAU Q R Dilarang Jadual Kebenaran Flip Flop RS Get TAK DAN S Q Get TAK DAN R Q S R Q Q Status 0 0 1 1 Dilarang 0 1 1 0 Set 1 0 0 1 Reset 1 1 Q Q Tak Berubah

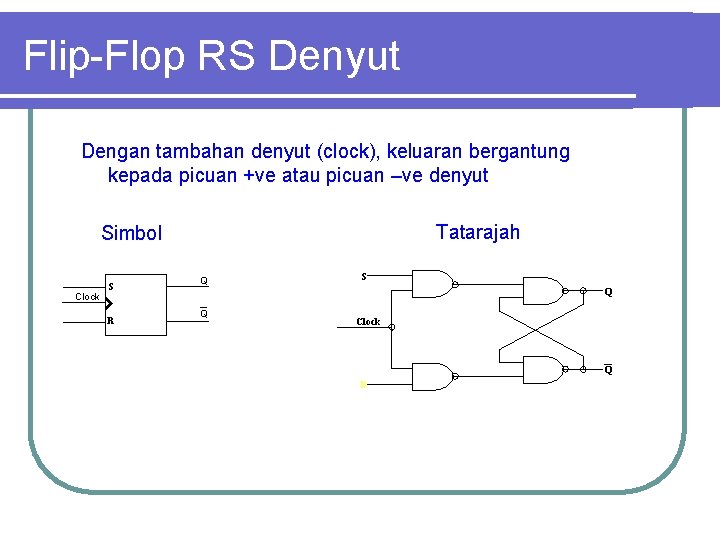

Flip-Flop RS Denyut Dengan tambahan denyut (clock), keluaran bergantung kepada picuan +ve atau picuan –ve denyut Tatarajah Simbol Clock S R Q S Q Q Clock Q R

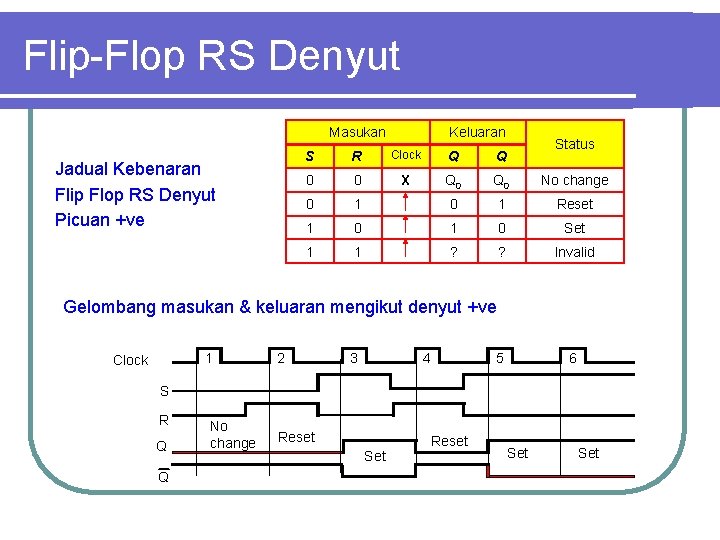

Flip-Flop RS Denyut Masukan Jadual Kebenaran Flip Flop RS Denyut Picuan +ve Keluaran Status S R Clock Q Q 0 0 X Q 0 No change 0 1 Reset 1 0 Set 1 1 ? ? Invalid 5 6 Gelombang masukan & keluaran mengikut denyut +ve 1 Clock 2 3 4 S R Q Q No change Reset Set Set

Litar logik jujukan l Litar Jujukan berdasarkan kepada penggunaan flip-flop adalah seperti : - Penghitung (Counter) l Shift Register l Memory Device l Pemasa (Timer 555) l

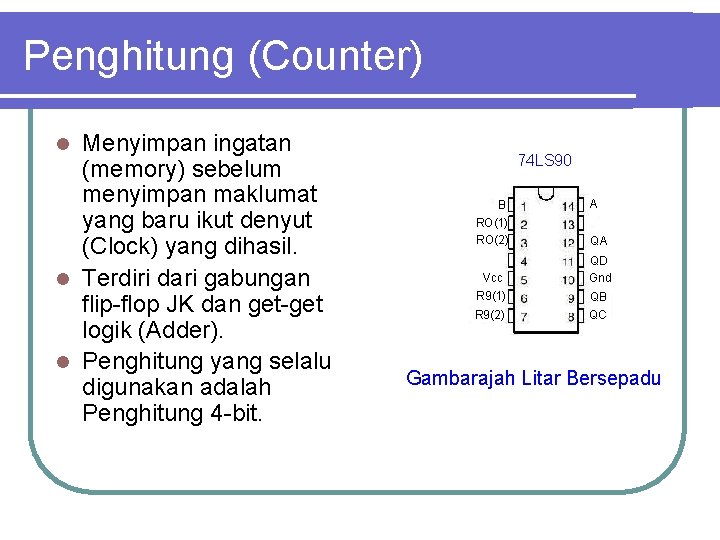

Penghitung (Counter) Menyimpan ingatan (memory) sebelum menyimpan maklumat yang baru ikut denyut (Clock) yang dihasil. l Terdiri dari gabungan flip-flop JK dan get-get logik (Adder). l Penghitung yang selalu digunakan adalah Penghitung 4 -bit. l 74 LS 90 B RO(1) RO(2) Vcc R 9(1) R 9(2) A QA QD Gnd QB QC Gambarajah Litar Bersepadu

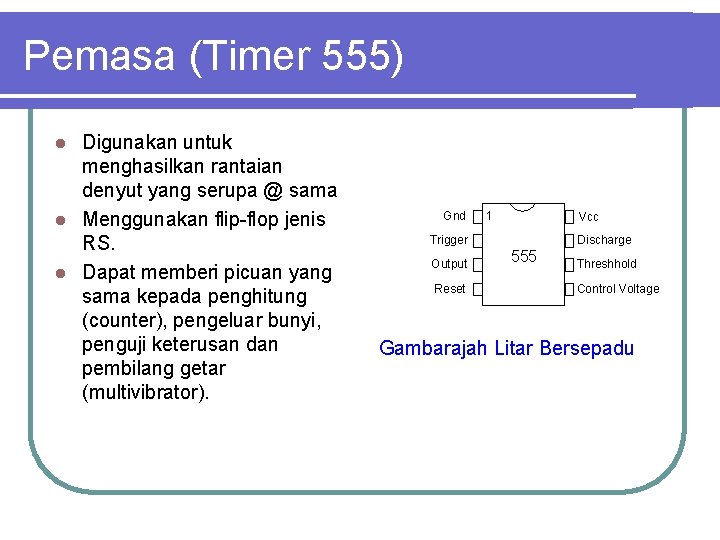

Pemasa (Timer 555) Digunakan untuk menghasilkan rantaian denyut yang serupa @ sama l Menggunakan flip-flop jenis RS. l Dapat memberi picuan yang sama kepada penghitung (counter), pengeluar bunyi, penguji keterusan dan pembilang getar (multivibrator). l Gnd 1 Vcc Trigger Output Reset Discharge 555 Threshhold Control Voltage Gambarajah Litar Bersepadu

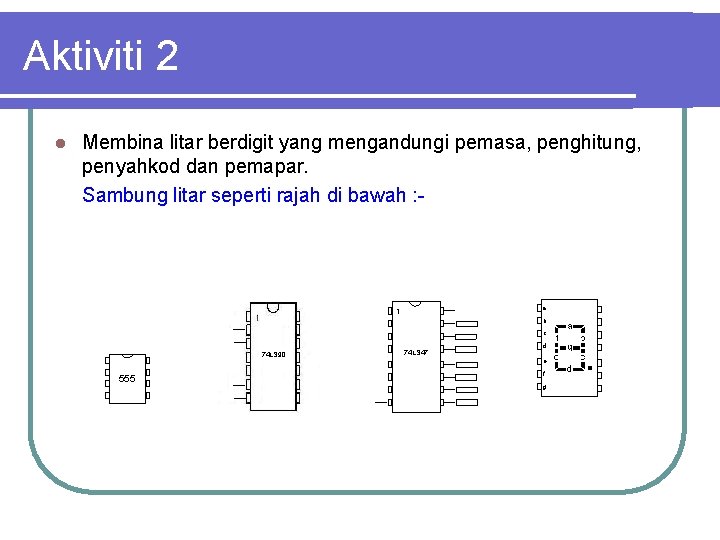

Aktiviti 2 l Membina litar berdigit yang mengandungi pemasa, penghitung, penyahkod dan pemapar. Sambung litar seperti rajah di bawah : - a 1 b c 74 LS 90 555 74 LS 47 d e f g

Aktiviti 2 Perbincangan Dari litar yang dibina, namakan komponen yang termasuk dalam kategori litar logik berkombinasi.

- Slides: 38