Single Flux Quantum SFQ 6 Likharev IEEE Trans

![バタフライユニット測定の例 Data pattern 1 Re[x(0)] = 0111, Im[x(0)] = 1101, Re[x(1)] = 1011, Im[x(1)] バタフライユニット測定の例 Data pattern 1 Re[x(0)] = 0111, Im[x(0)] = 1101, Re[x(1)] = 1011, Im[x(1)]](https://slidetodoc.com/presentation_image_h/063103bd22f9112bf926fa4ace1d9a0b/image-32.jpg)

![CMOS FFT Processorとの比較 [4] This study 35 Technology Bit-width Power [m. W] Clock Frequency CMOS FFT Processorとの比較 [4] This study 35 Technology Bit-width Power [m. W] Clock Frequency](https://slidetodoc.com/presentation_image_h/063103bd22f9112bf926fa4ace1d9a0b/image-36.jpg)

- Slides: 51

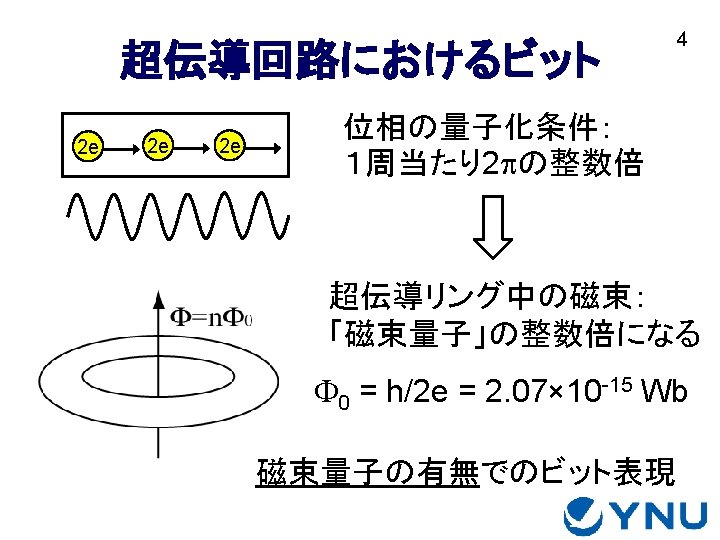

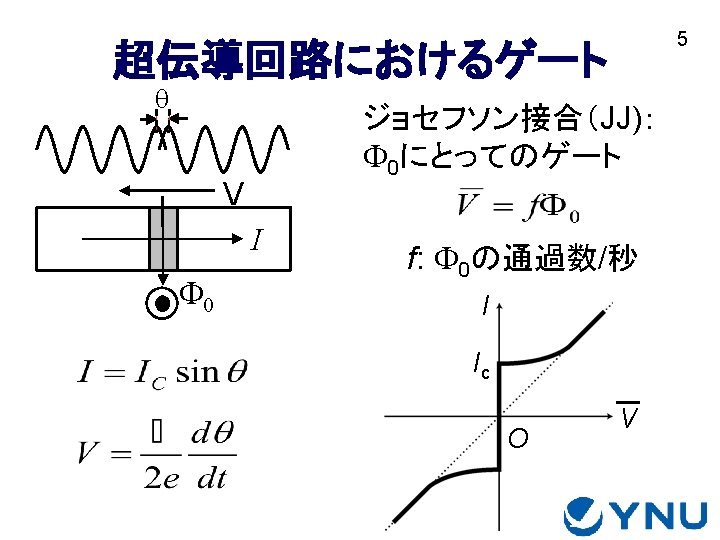

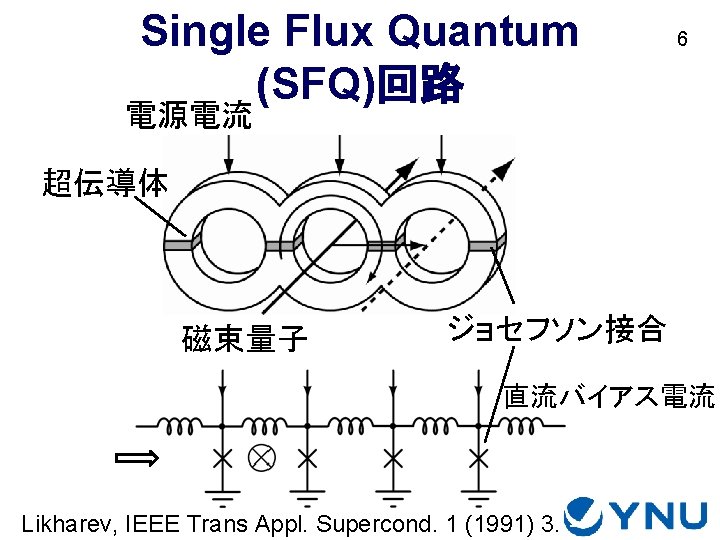

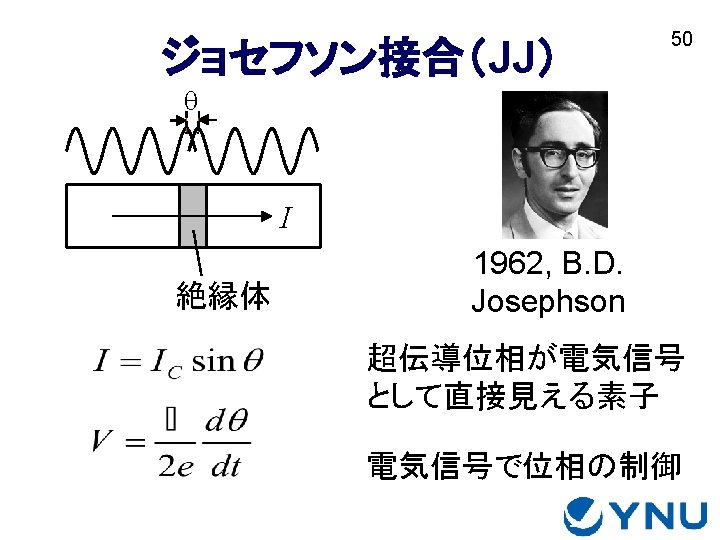

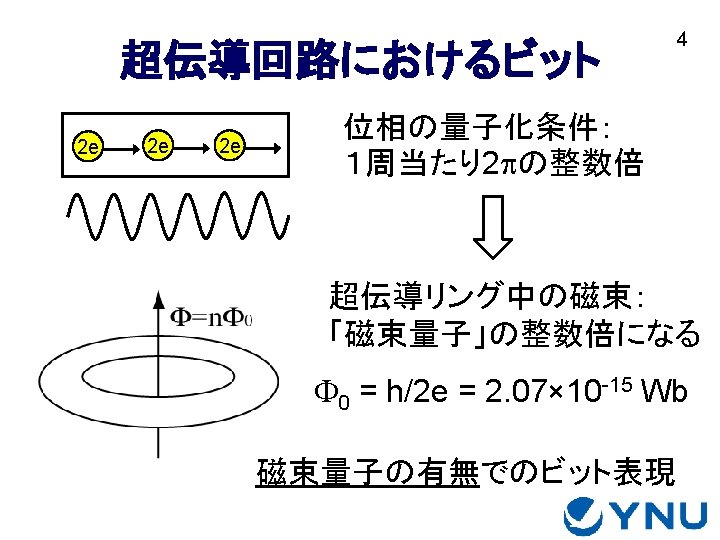

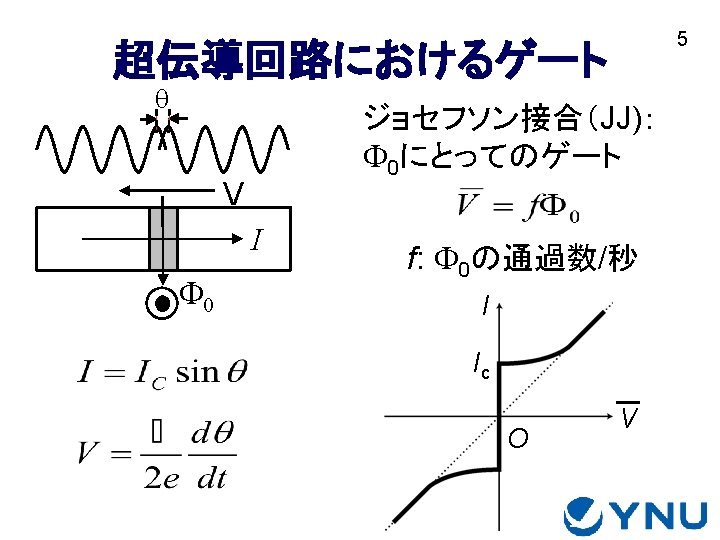

Single Flux Quantum (SFQ)回路 6 電源電流 超伝導体 磁束量子 ジョセフソン接合 直流バイアス電流 Likharev, IEEE Trans Appl. Supercond. 1 (1991) 3.

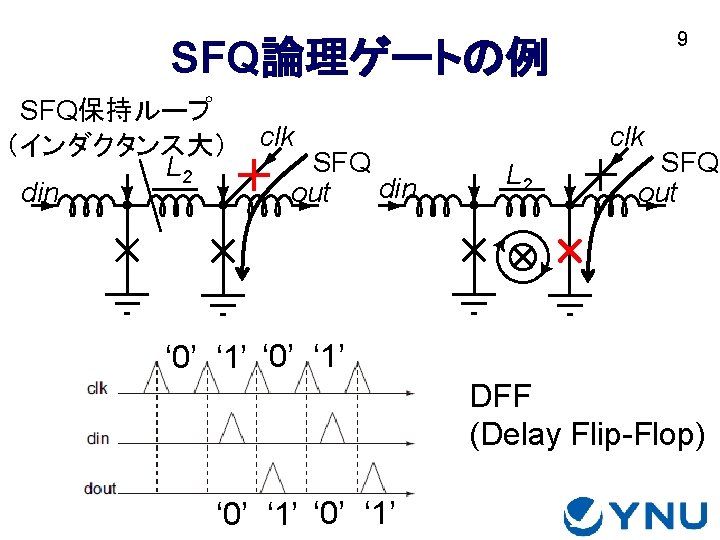

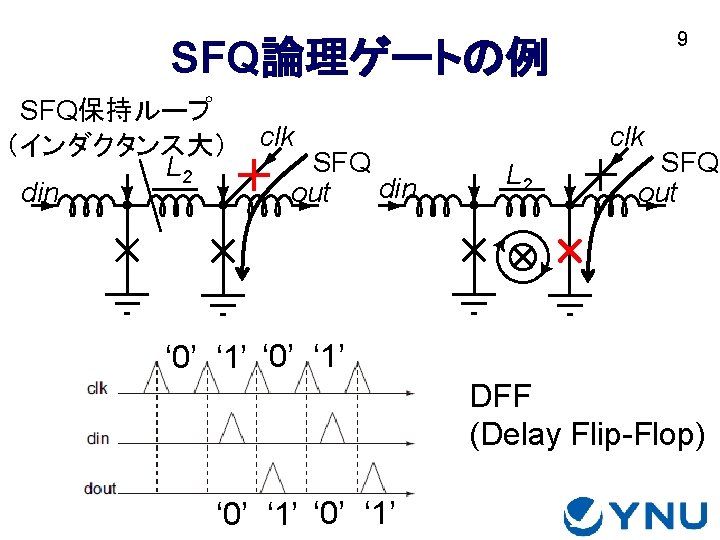

9 SFQ論理ゲートの例 SFQ保持ループ (インダクタンス大) L 2 din clk SFQ din out clk L 2 SFQ out ‘ 0’ ‘ 1’ DFF (Delay Flip-Flop) ‘ 0’ ‘ 1’

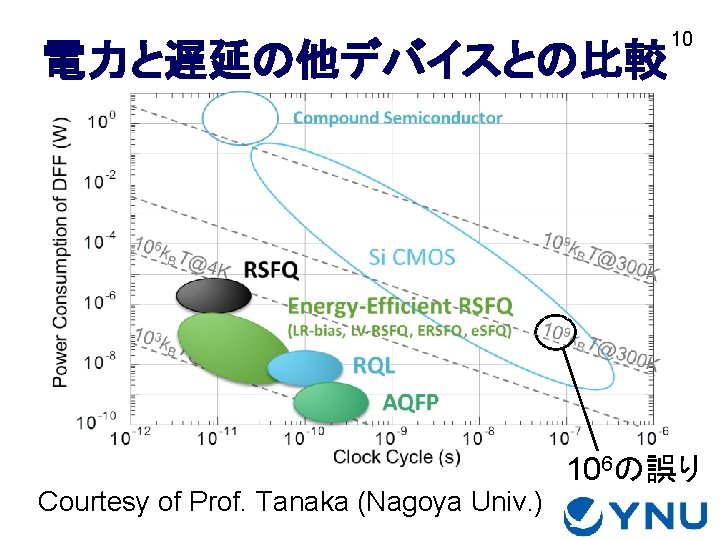

電力と遅延の他デバイスとの比較 Courtesy of Prof. Tanaka (Nagoya Univ. ) 10 106の誤り

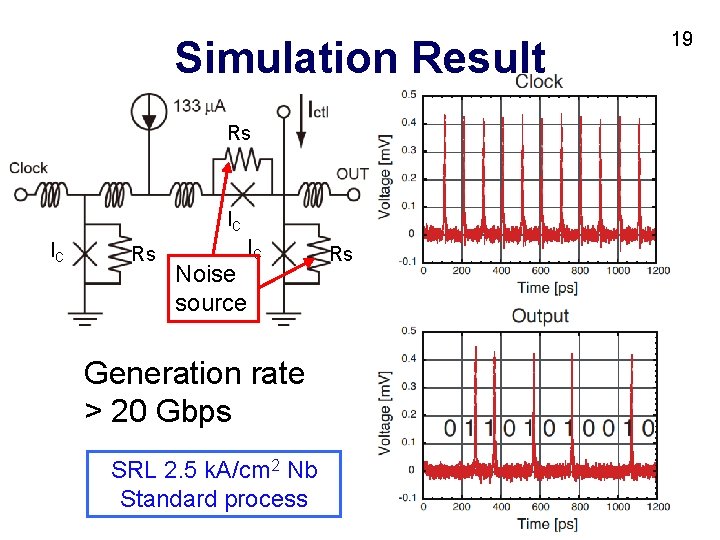

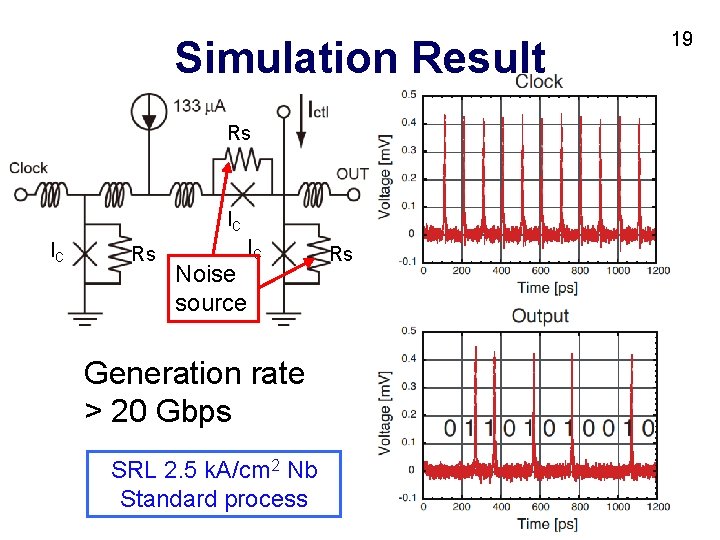

18 SFQ物理乱数生成器 Rs IC IC Rs IC = 216 m. A, Rs = 1. 73 W, L = 2. 52 p. H 49. 1 m. A Yamanashi et al. , IEEE TAS 19 (2009) 630.

Simulation Result Rs IC IC Rs IC Noise source Generation rate > 20 Gbps SRL 2. 5 k. A/cm 2 Nb Standard process Rs 19

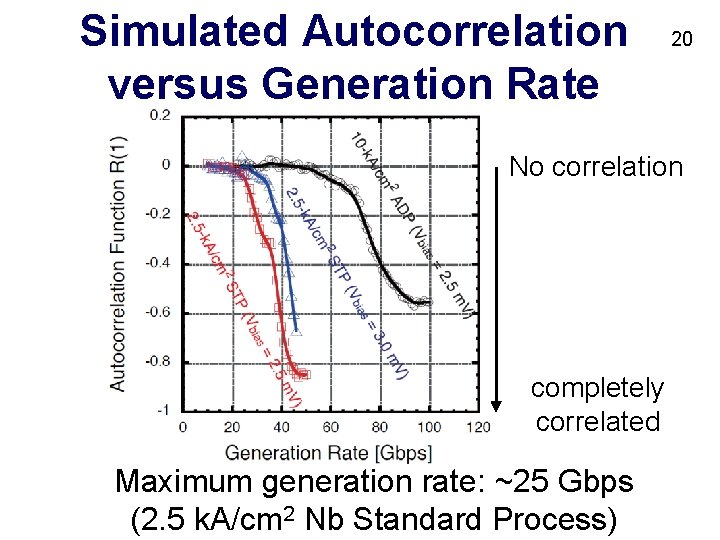

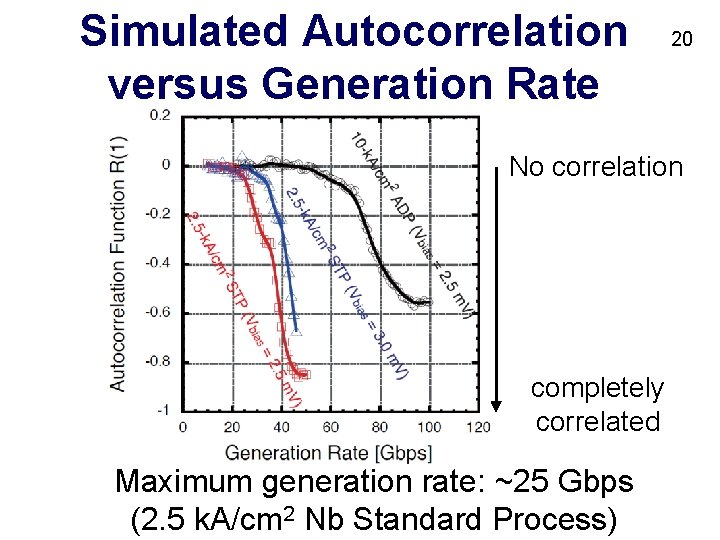

Simulated Autocorrelation versus Generation Rate 20 No correlation completely correlated Maximum generation rate: ~25 Gbps (2. 5 k. A/cm 2 Nb Standard Process)

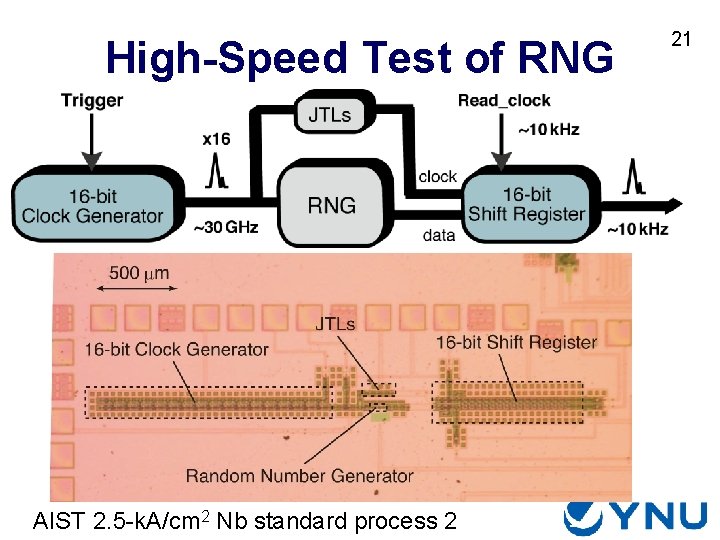

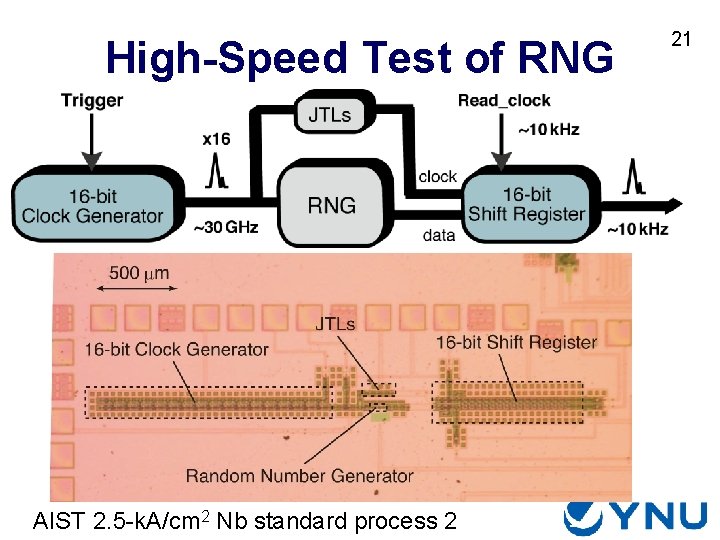

High-Speed Test of RNG AIST 2. 5 -k. A/cm 2 Nb standard process 2 21

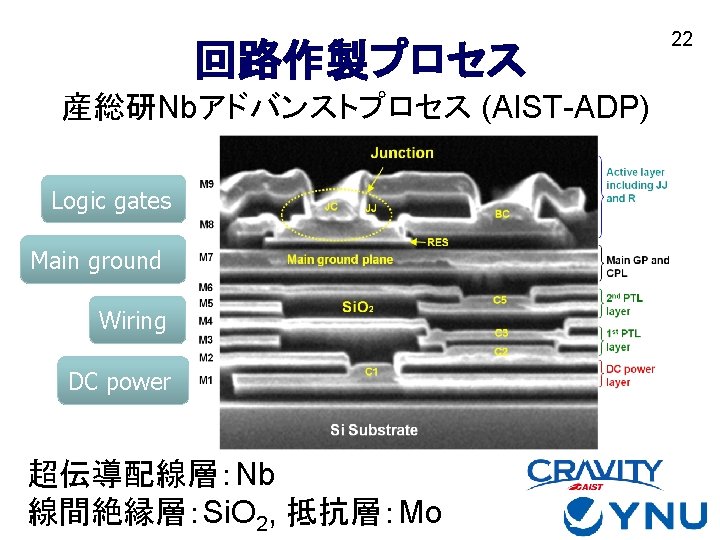

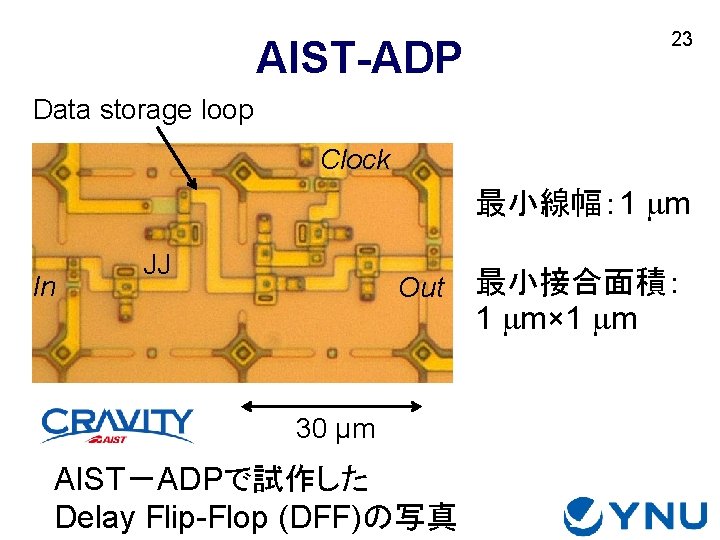

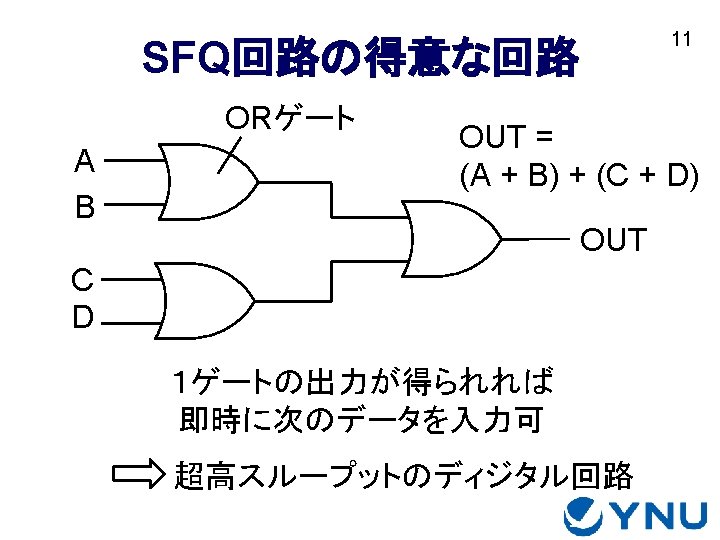

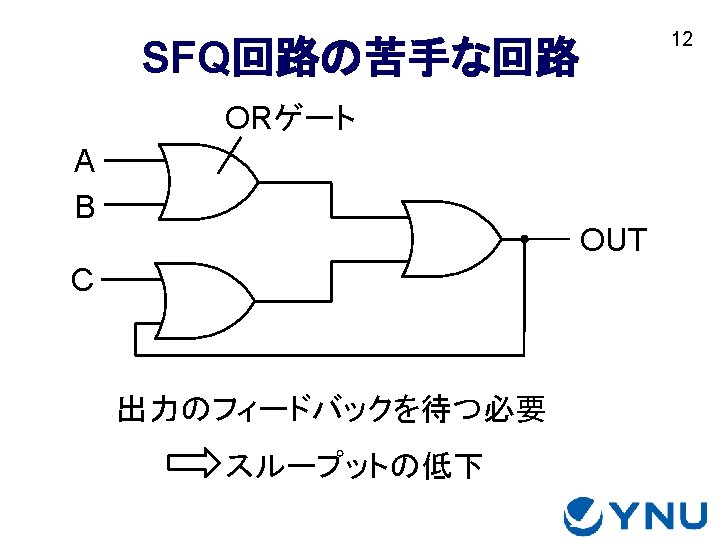

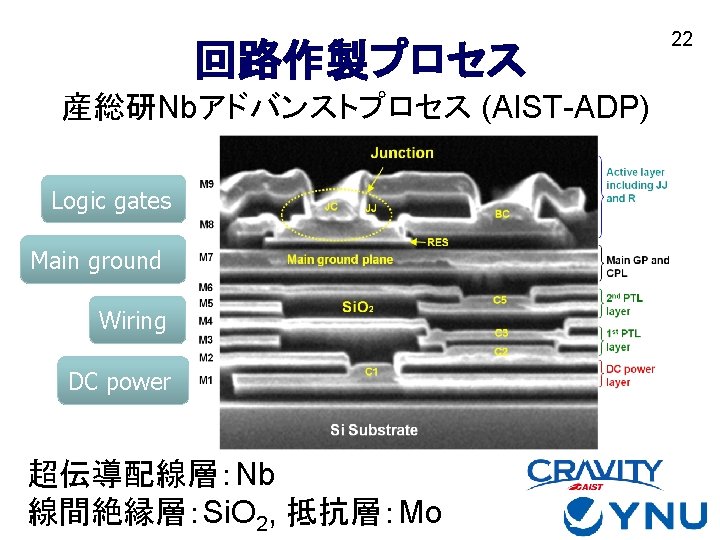

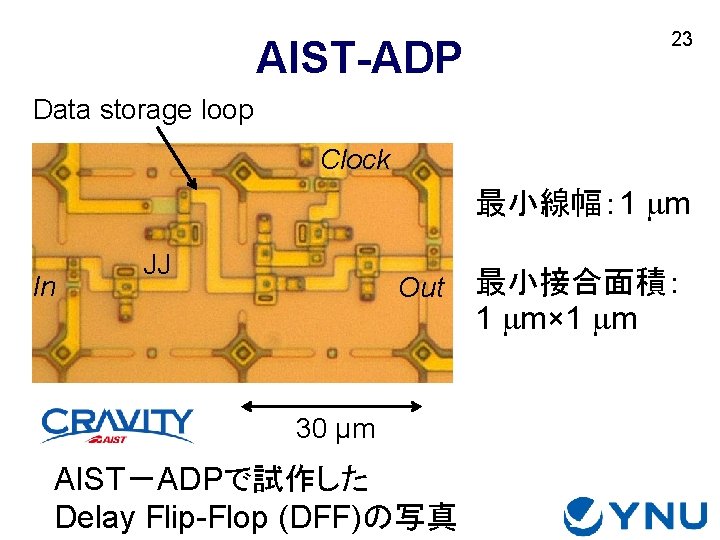

AIST-ADP 23 Data storage loop Clock 最小線幅: 1 mm In JJ Out 30 μm AIST-ADPで試作した Delay Flip-Flop (DFF)の写真 最小接合面積: 1 mm× 1 mm

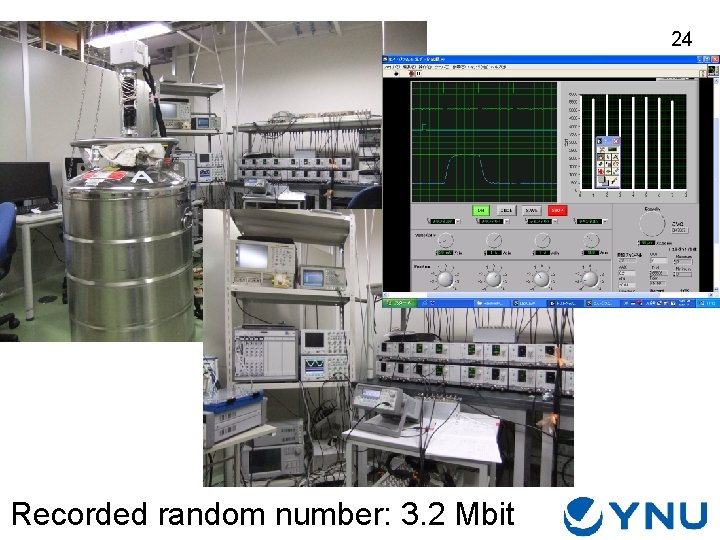

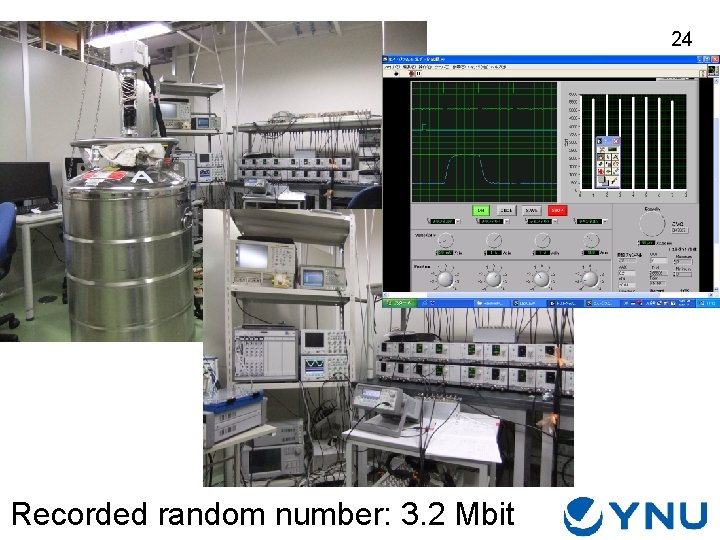

24 Recorded random number: 3. 2 Mbit

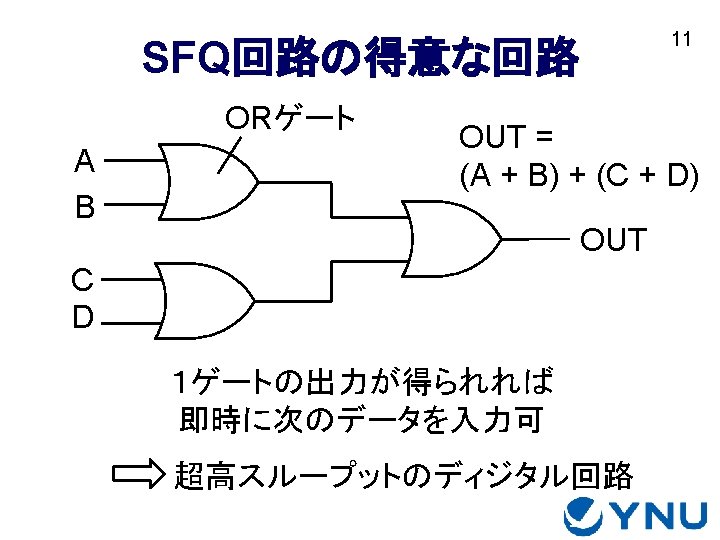

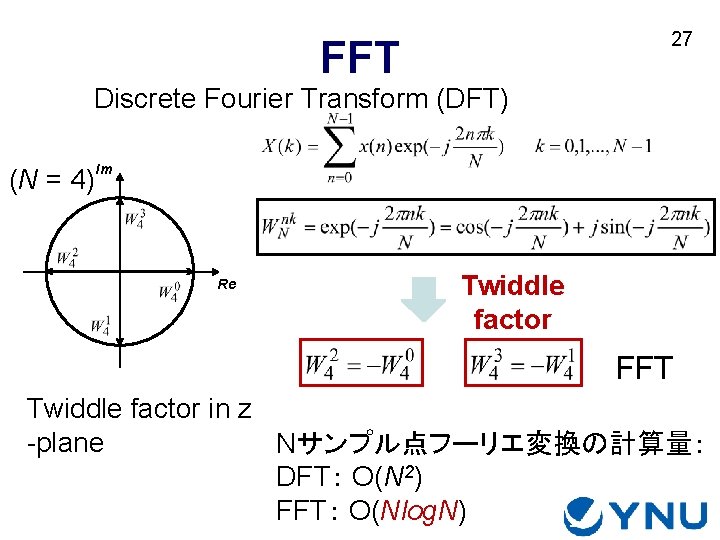

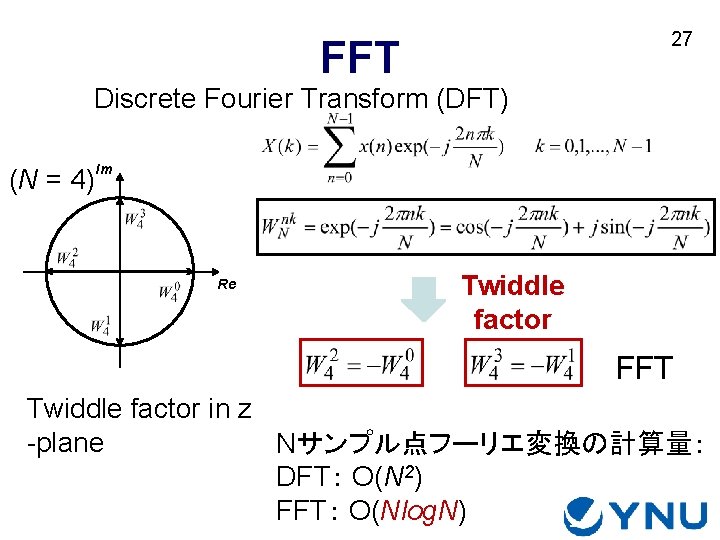

27 FFT Discrete Fourier Transform (DFT) (N = 4) Im Re Twiddle factor FFT Twiddle factor in z -plane Nサンプル点フーリエ変換の計算量: DFT: O(N 2) FFT: O(Nlog. N)

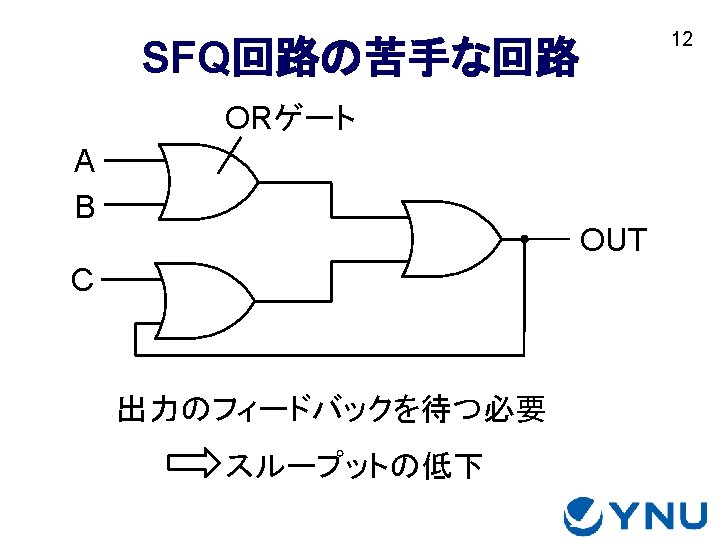

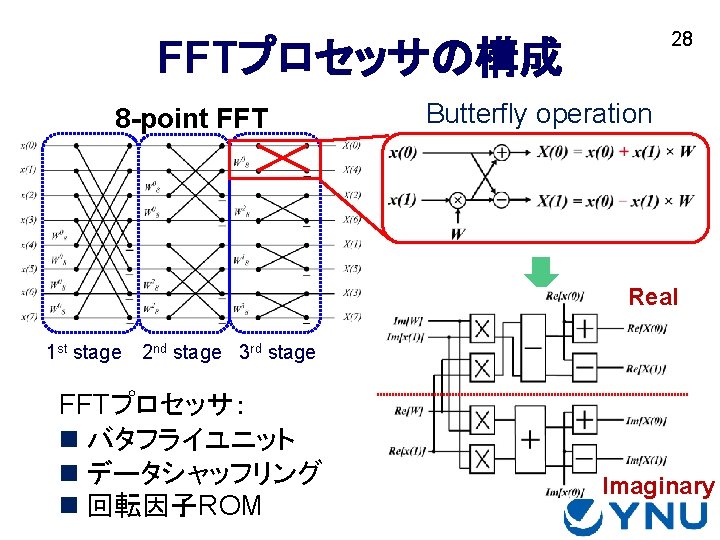

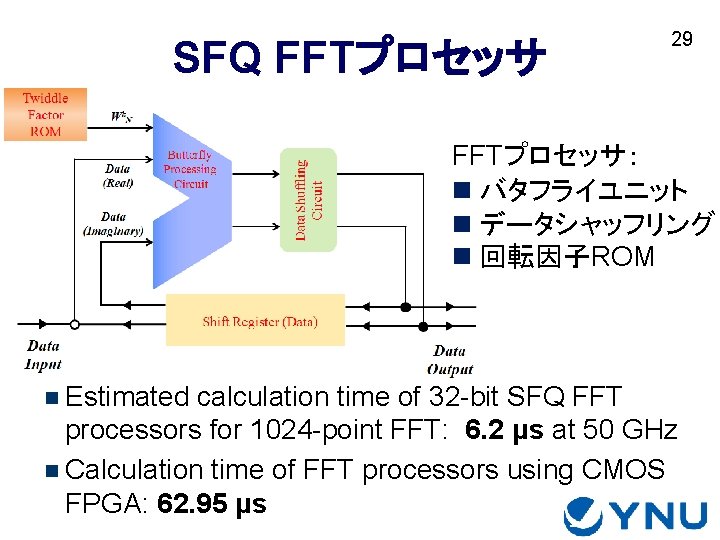

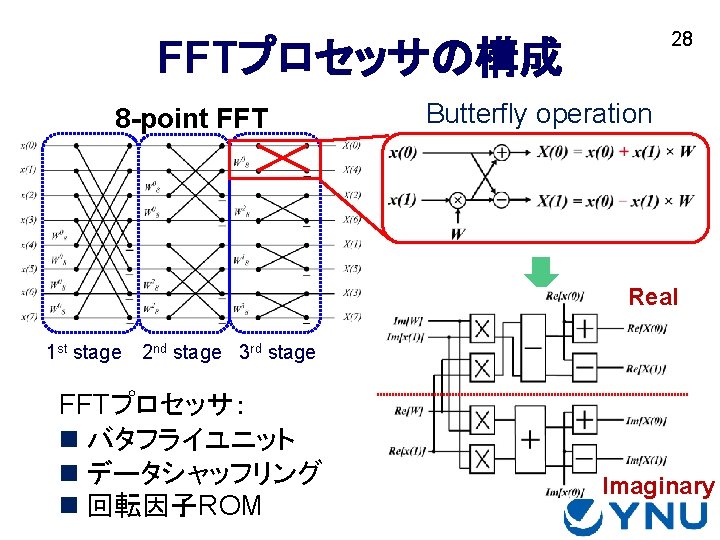

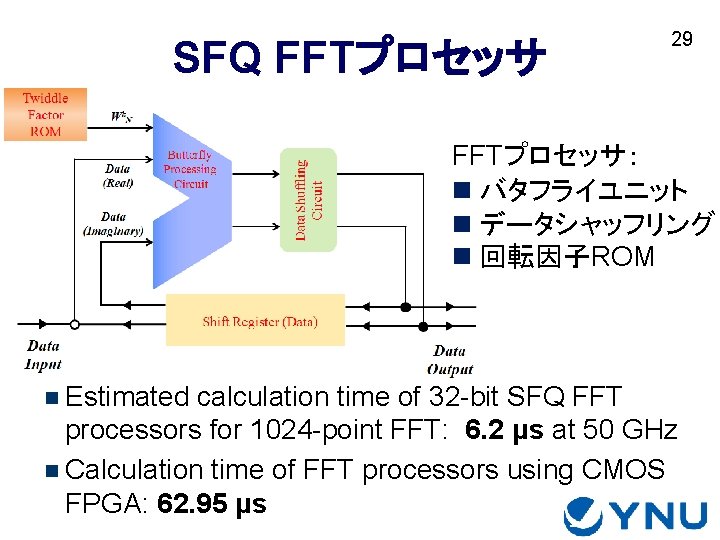

28 FFTプロセッサの構成 8 -point FFT Butterfly operation Real 1 st stage 2 nd stage 3 rd stage FFTプロセッサ: n バタフライユニット n データシャッフリング n 回転因子ROM Imaginary

SFQ FFTプロセッサ 29 FFTプロセッサ: n バタフライユニット n データシャッフリング n 回転因子ROM n Estimated calculation time of 32 -bit SFQ FFT processors for 1024 -point FFT: 6. 2 μs at 50 GHz n Calculation time of FFT processors using CMOS FPGA: 62. 95 μs

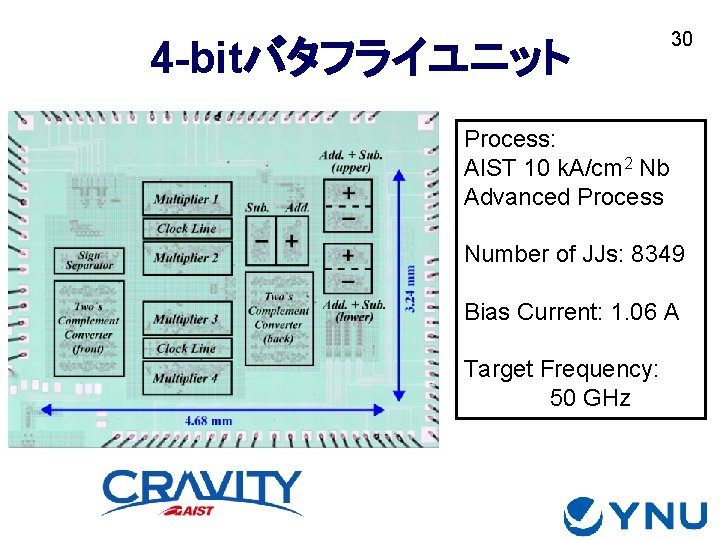

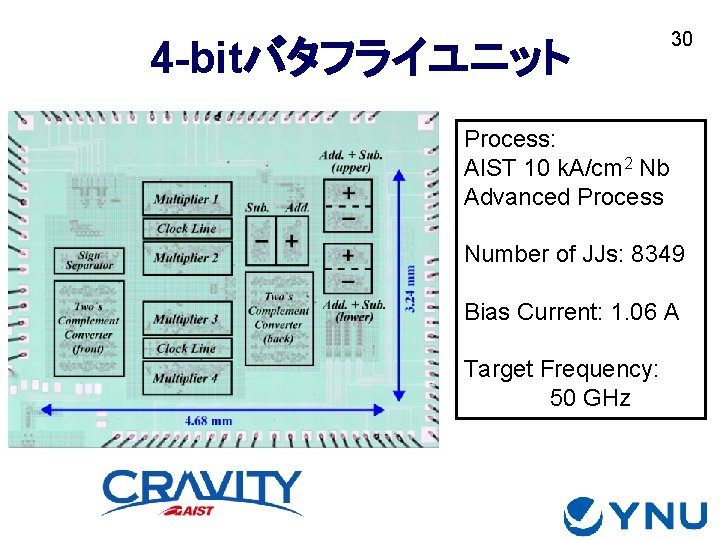

4 -bitバタフライユニット 30 Process: AIST 10 k. A/cm 2 Nb Advanced Process Number of JJs: 8349 Bias Current: 1. 06 A Target Frequency: 50 GHz

![バタフライユニット測定の例 Data pattern 1 Rex0 0111 Imx0 1101 Rex1 1011 Imx1 バタフライユニット測定の例 Data pattern 1 Re[x(0)] = 0111, Im[x(0)] = 1101, Re[x(1)] = 1011, Im[x(1)]](https://slidetodoc.com/presentation_image_h/063103bd22f9112bf926fa4ace1d9a0b/image-32.jpg)

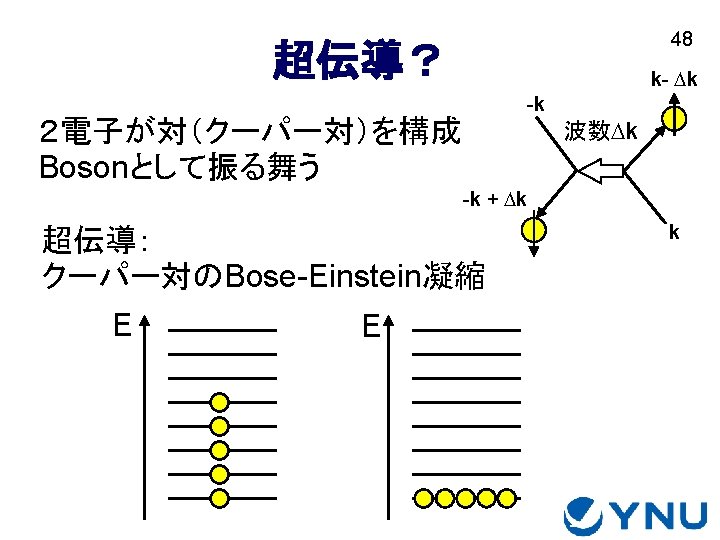

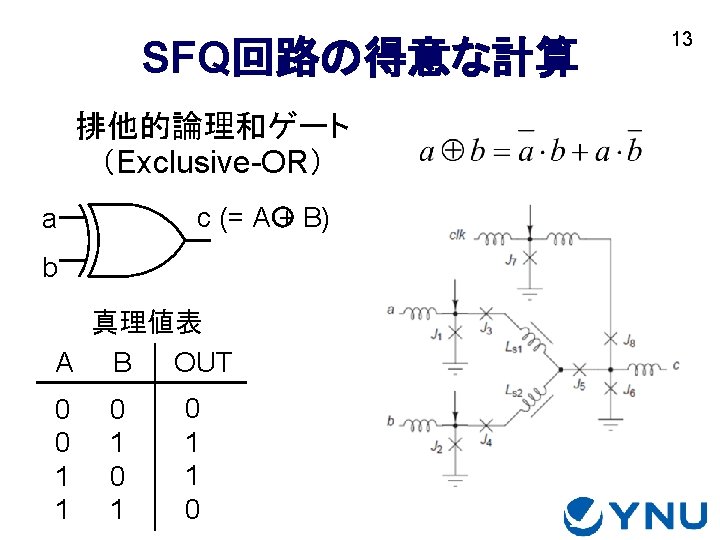

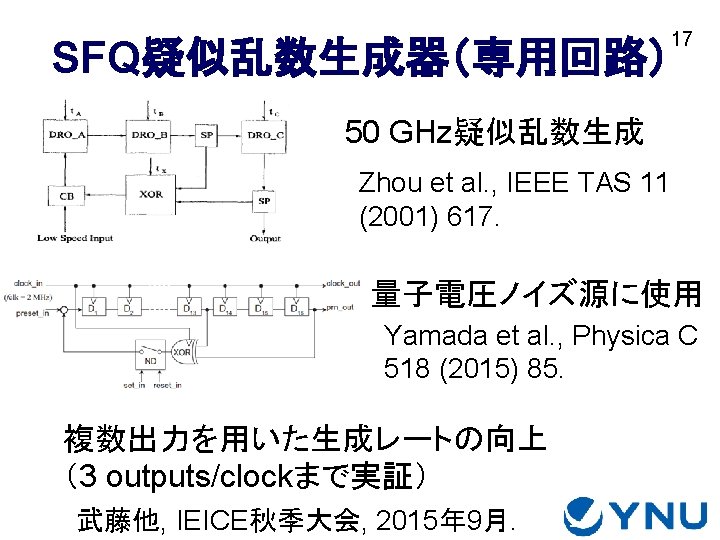

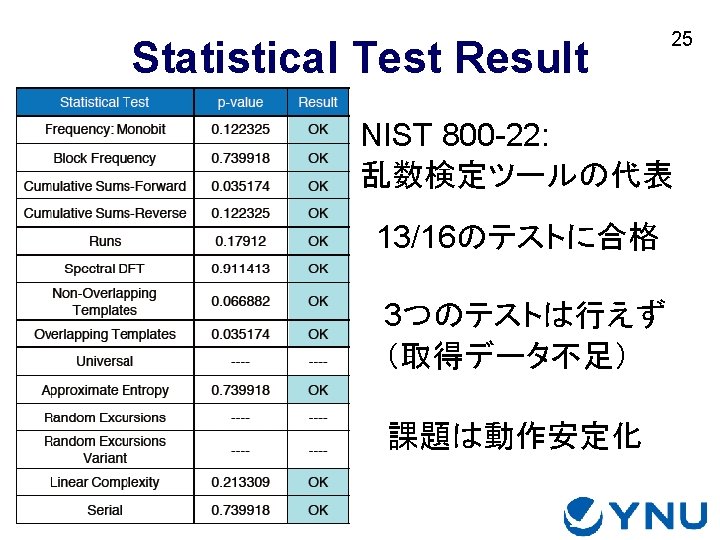

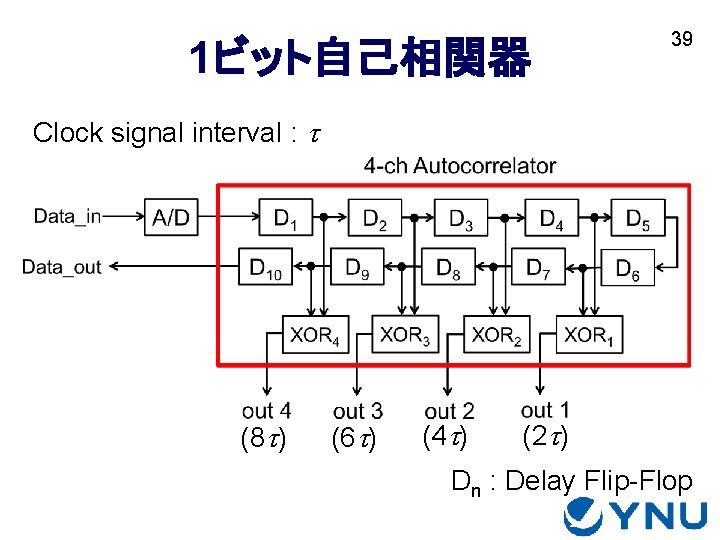

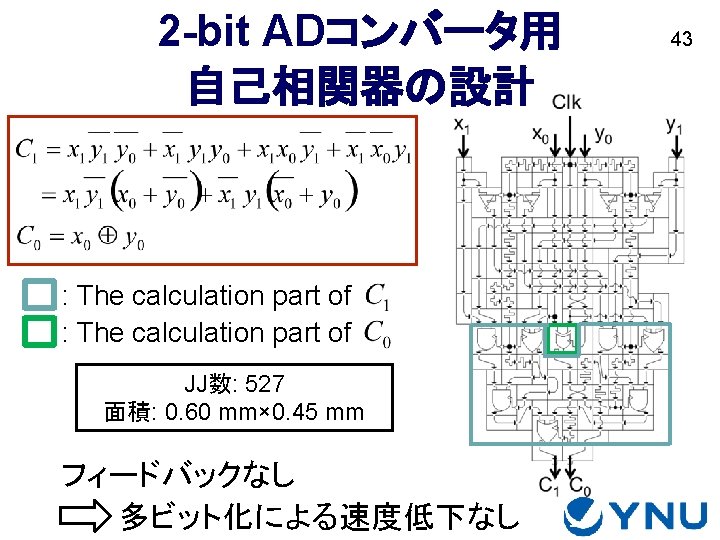

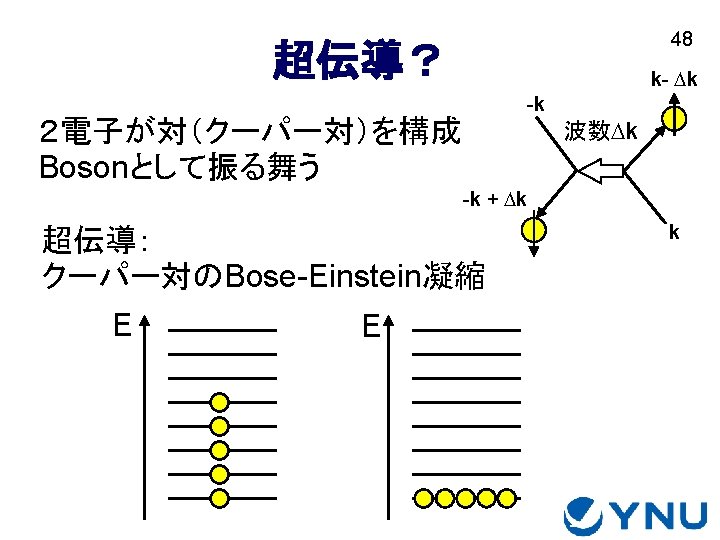

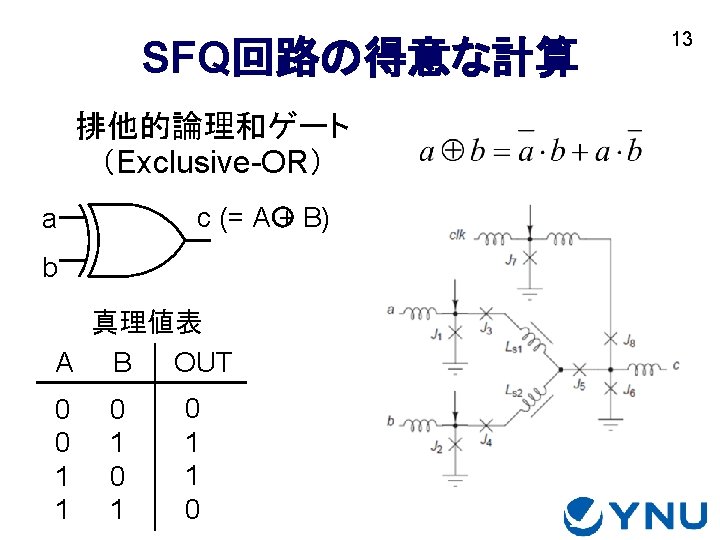

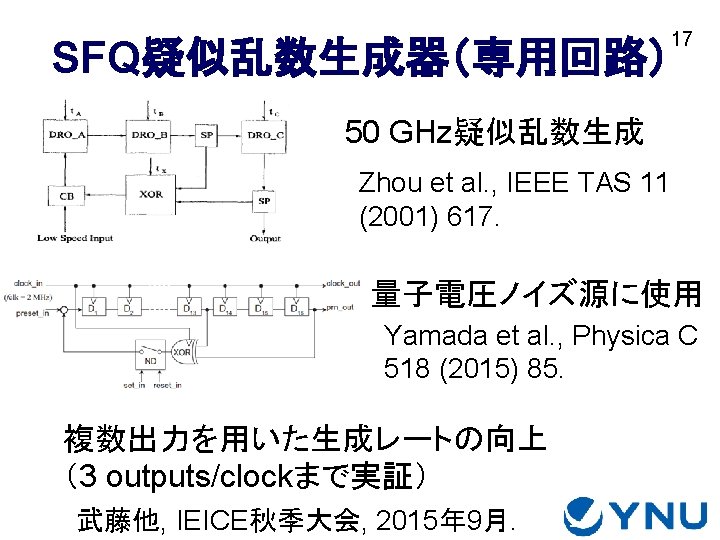

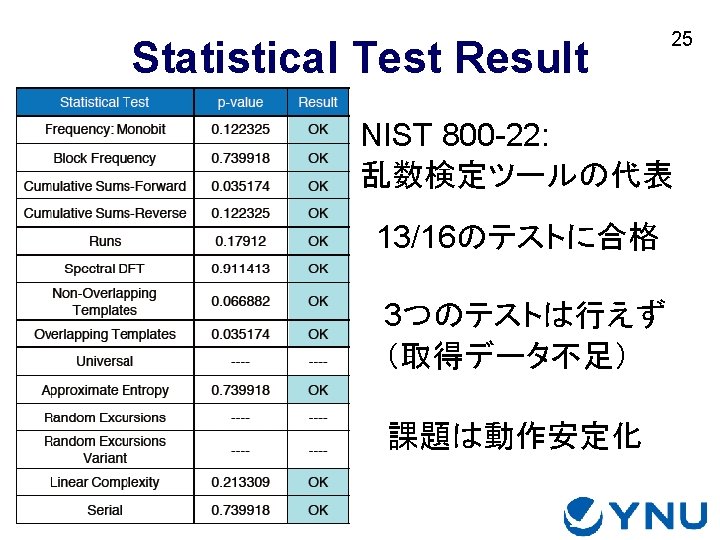

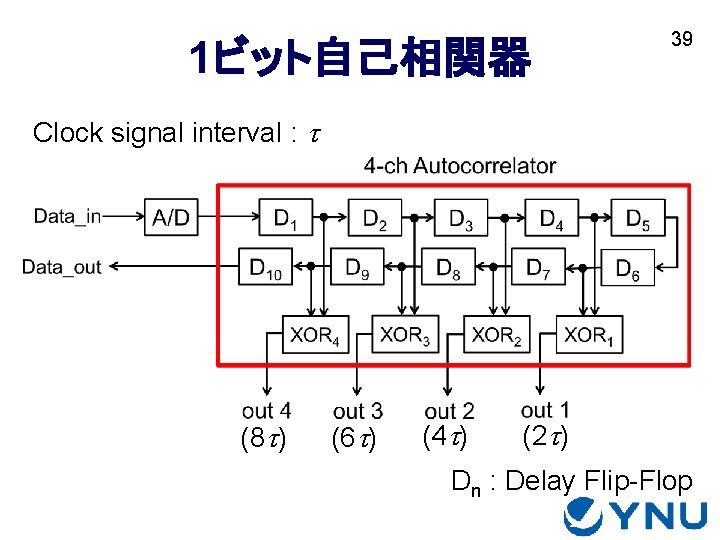

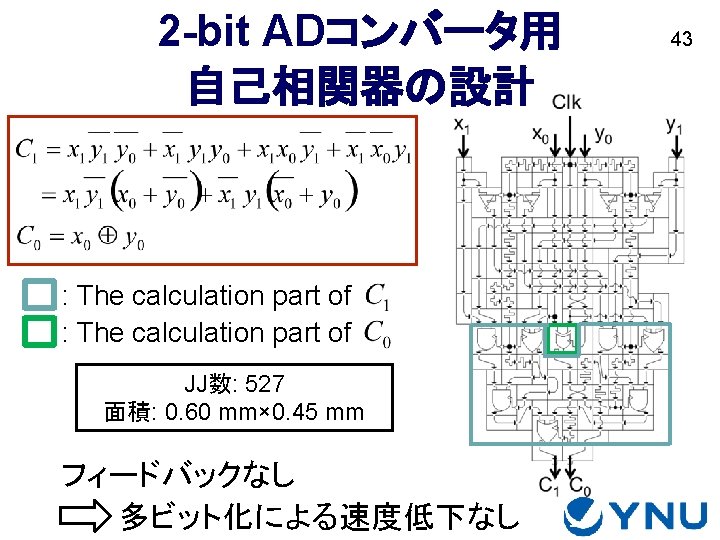

バタフライユニット測定の例 Data pattern 1 Re[x(0)] = 0111, Im[x(0)] = 1101, Re[x(1)] = 1011, Im[x(1)] = 1111, Re[W] = 1101, Im[W] = 1001 Re[X(0)] = 100100, Re[X(1)] = 010100 31 Data pattern 2 Re[x(0)] = 0110, Im[x(0)] = 1010, Re[x(1)] = 1011, Im[x(1)] = 1100, Re[W] = 1001, Im[W] = 1011, Re[X(0)] = 100111, Re[X(1)] = 001001

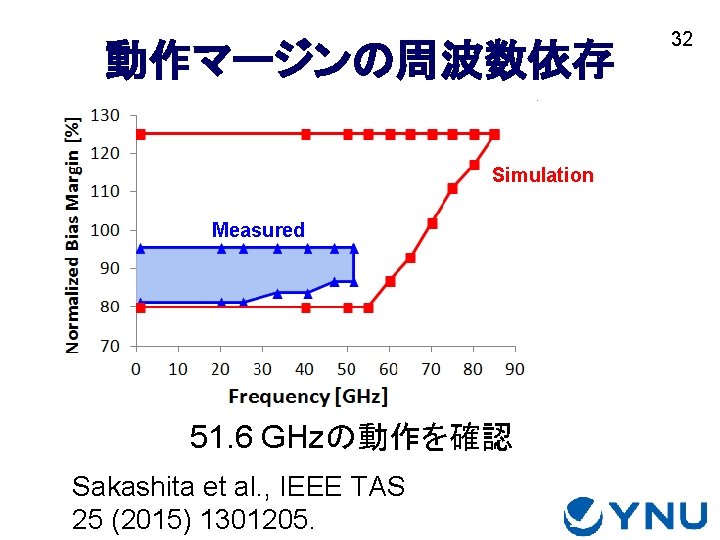

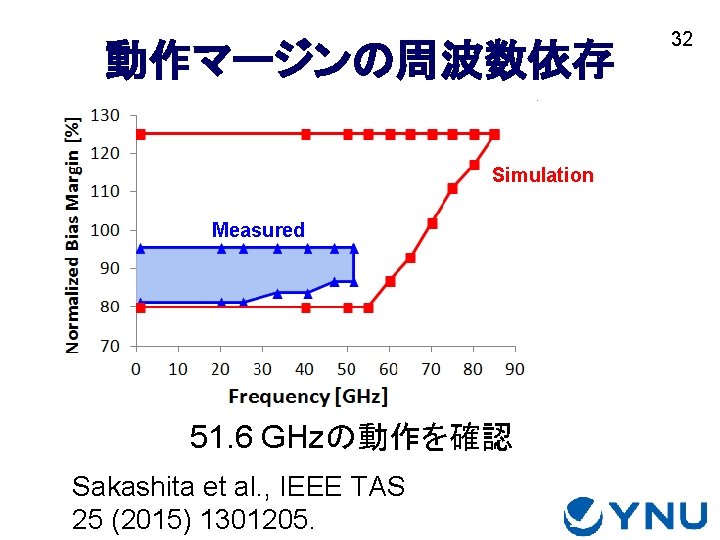

動作マージンの周波数依存 Simulation Measured 51. 6 GHzの動作を確認 Sakashita et al. , IEEE TAS 25 (2015) 1301205. 32

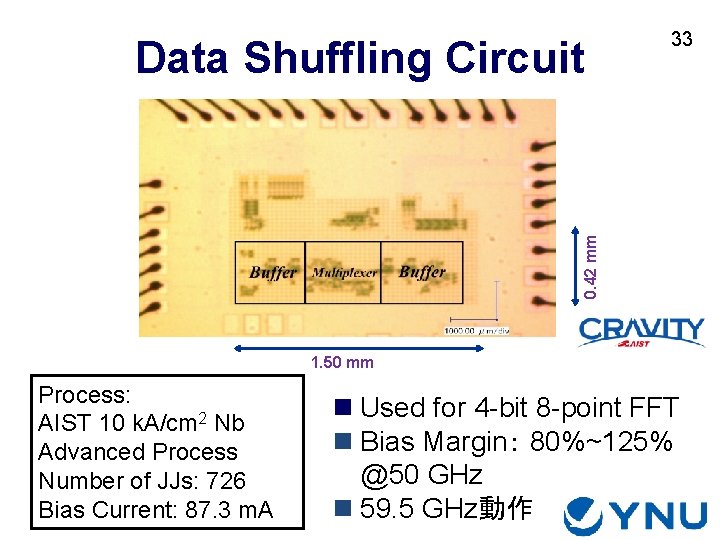

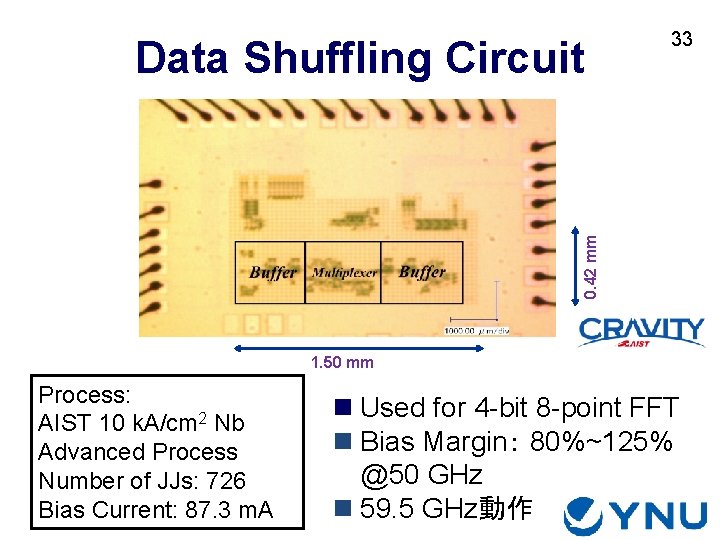

0. 42 mm Data Shuffling Circuit 33 1. 50 mm Process: AIST 10 k. A/cm 2 Nb Advanced Process Number of JJs: 726 Bias Current: 87. 3 m. A n Used for 4 -bit 8 -point FFT n Bias Margin: 80%~125% @50 GHz n 59. 5 GHz動作

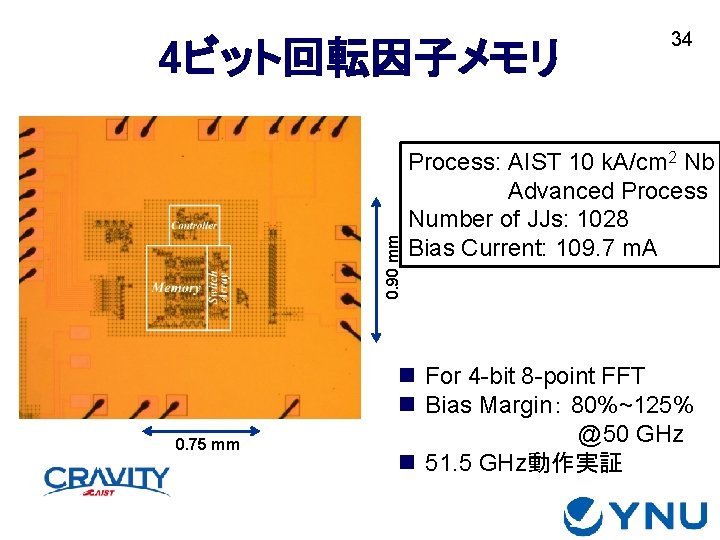

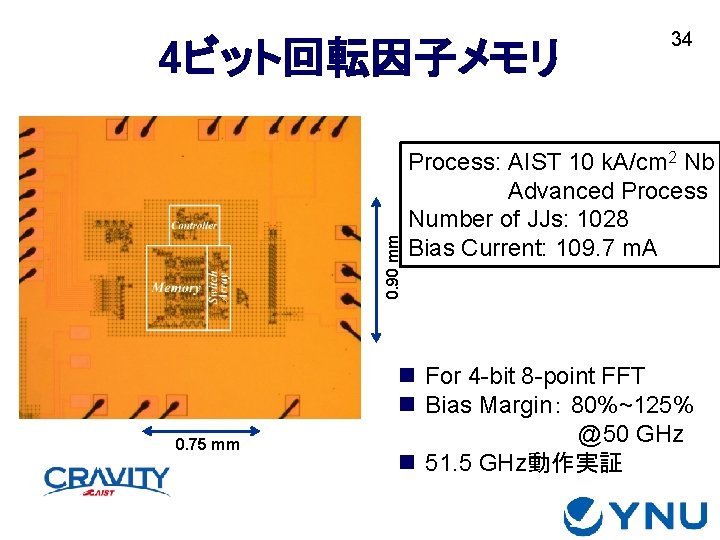

0. 90 mm 4ビット回転因子メモリ 0. 75 mm 34 Process: AIST 10 k. A/cm 2 Nb Advanced Process Number of JJs: 1028 Bias Current: 109. 7 m. A n For 4 -bit 8 -point FFT n Bias Margin: 80%~125% @50 GHz n 51. 5 GHz動作実証

![CMOS FFT Processorとの比較 4 This study 35 Technology Bitwidth Power m W Clock Frequency CMOS FFT Processorとの比較 [4] This study 35 Technology Bit-width Power [m. W] Clock Frequency](https://slidetodoc.com/presentation_image_h/063103bd22f9112bf926fa4ace1d9a0b/image-36.jpg)

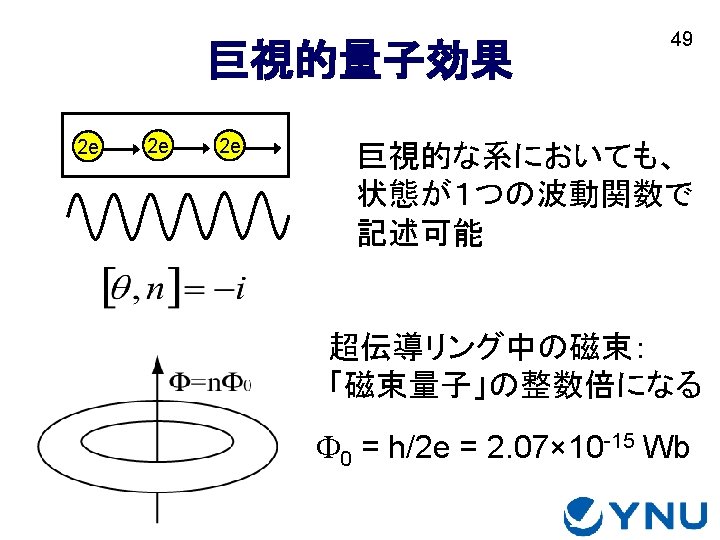

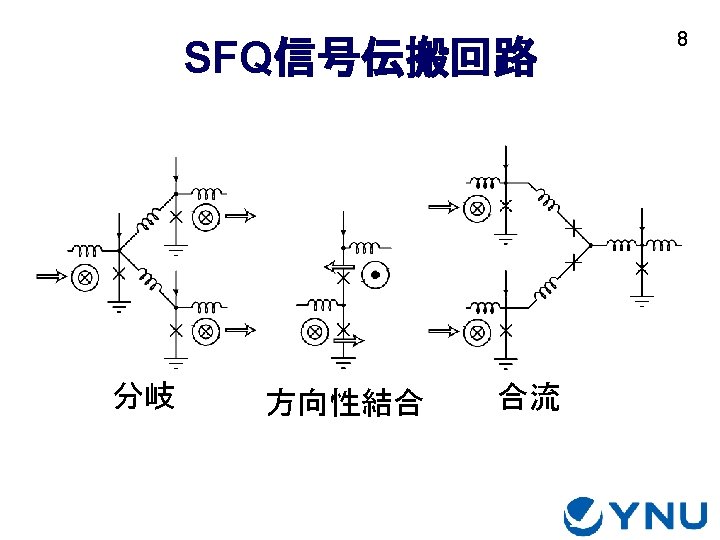

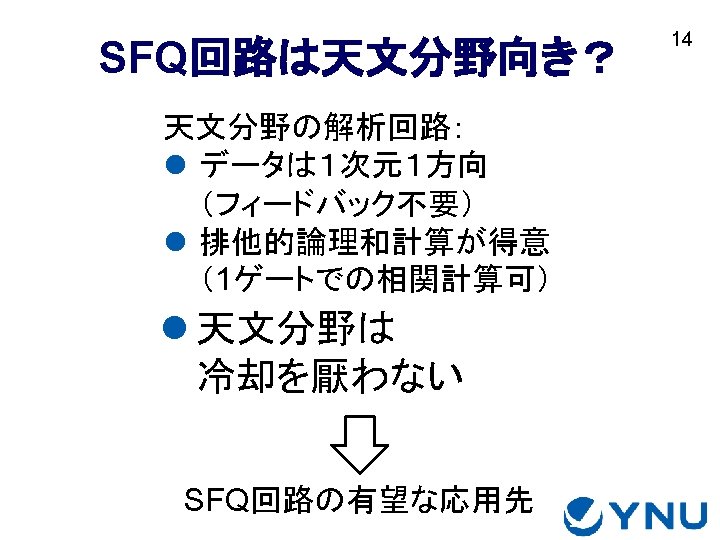

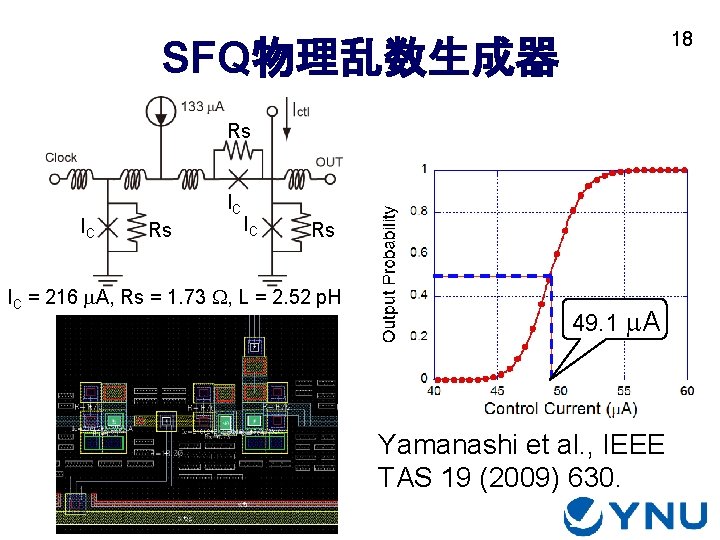

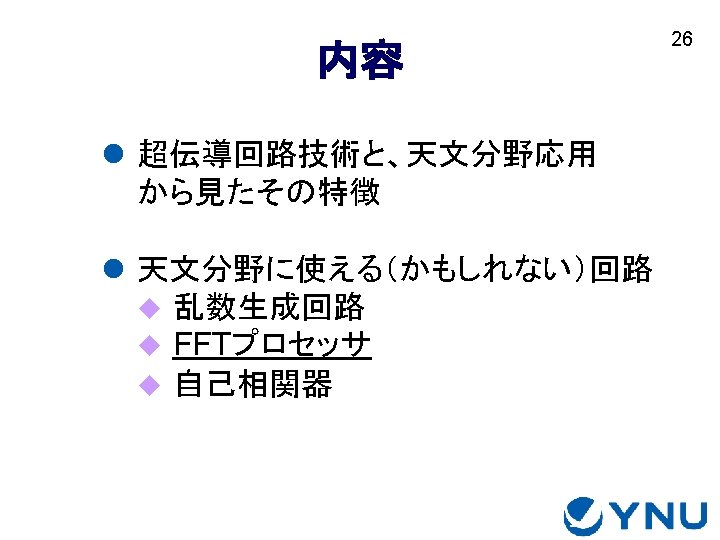

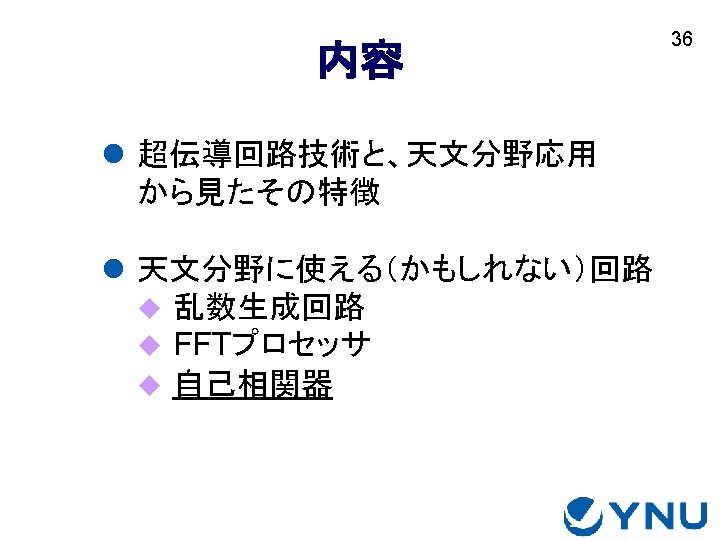

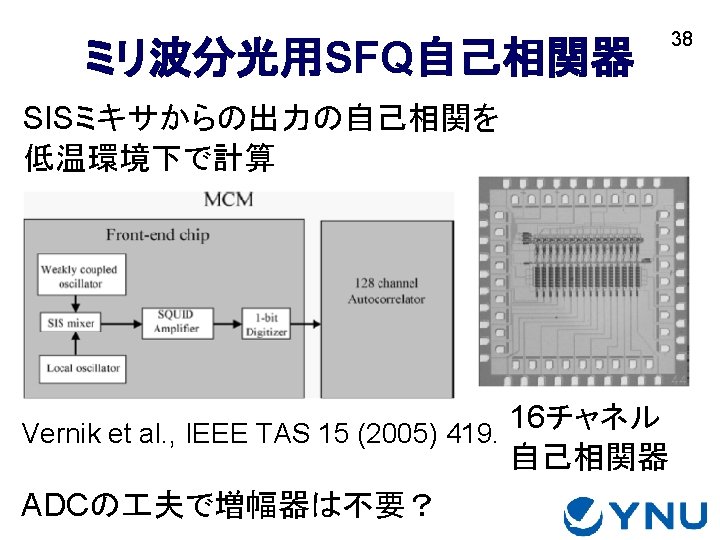

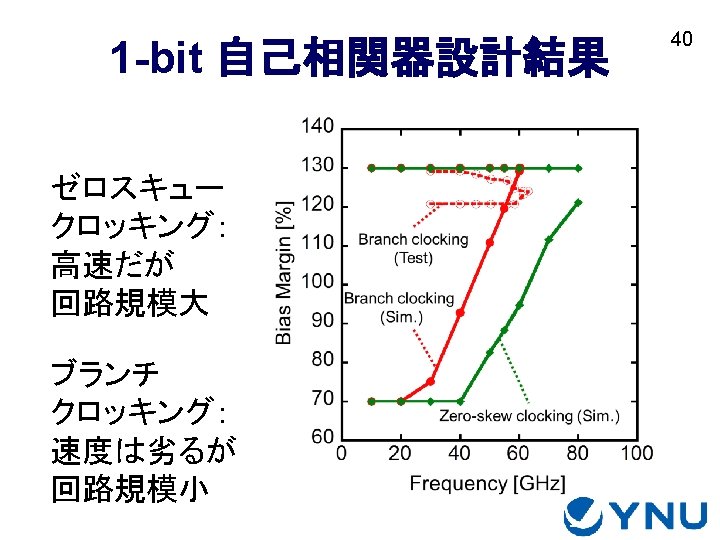

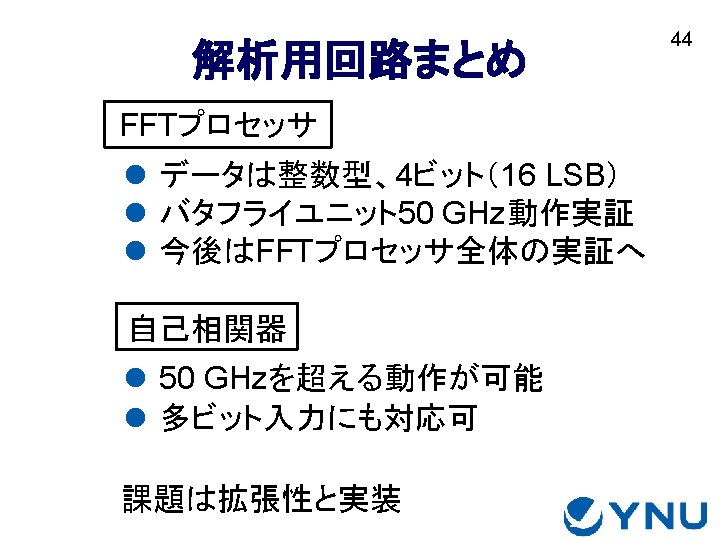

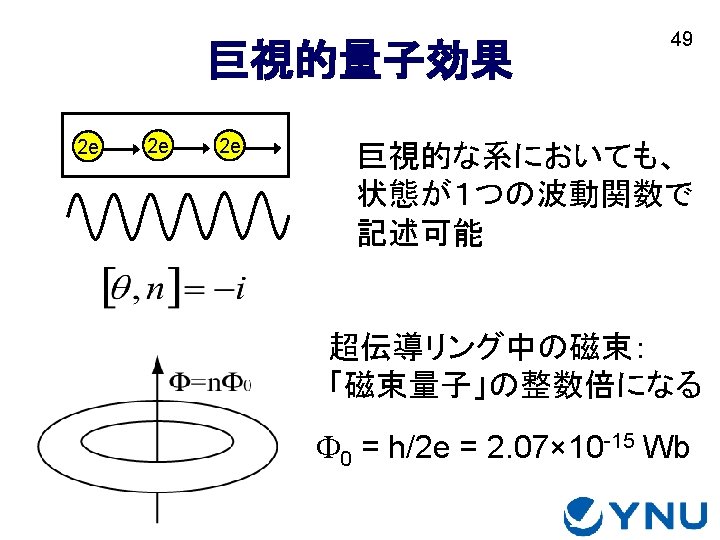

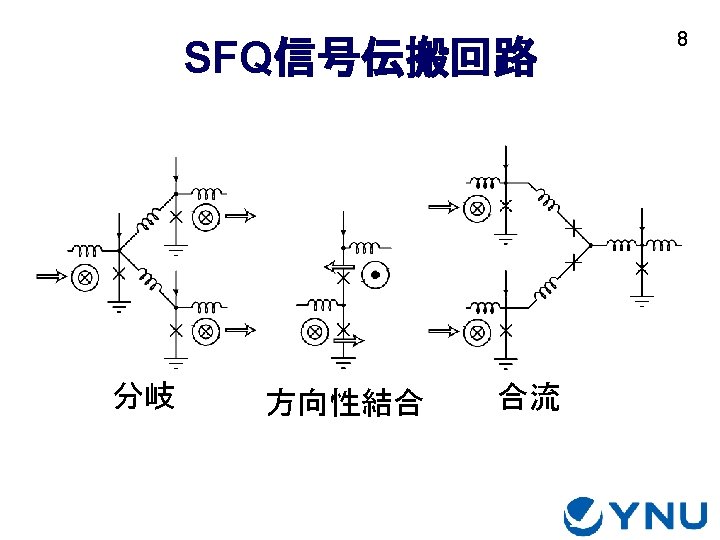

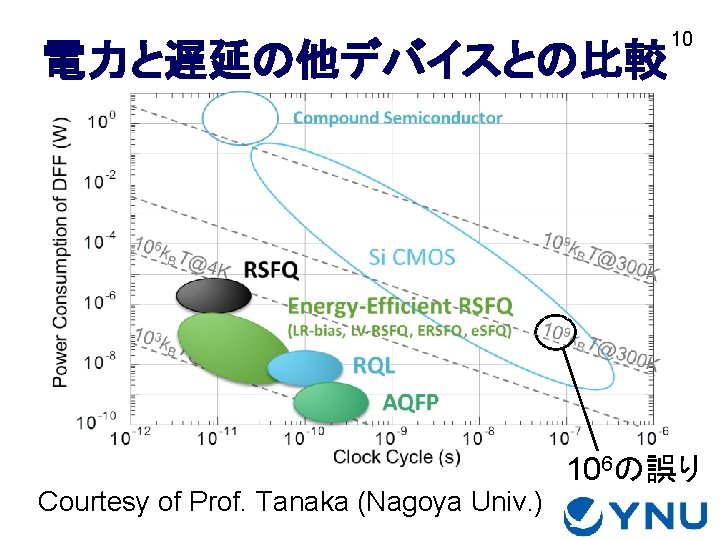

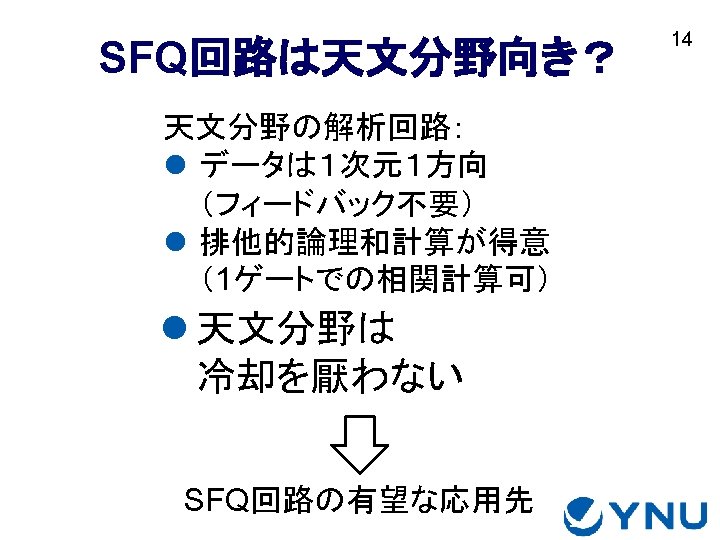

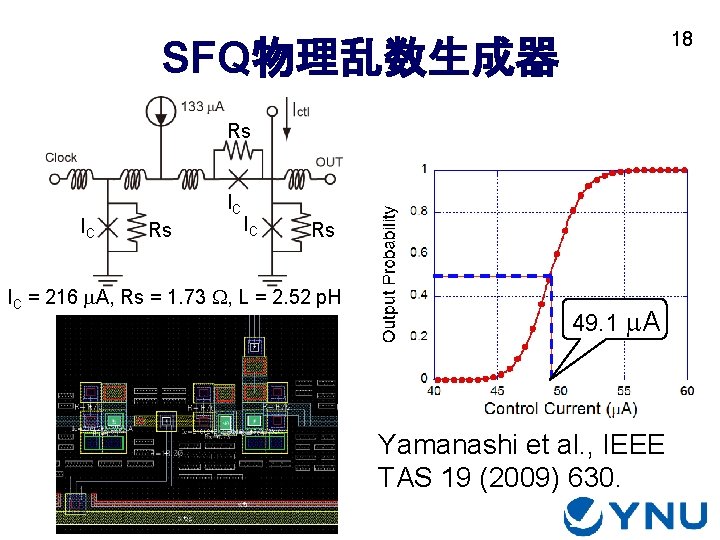

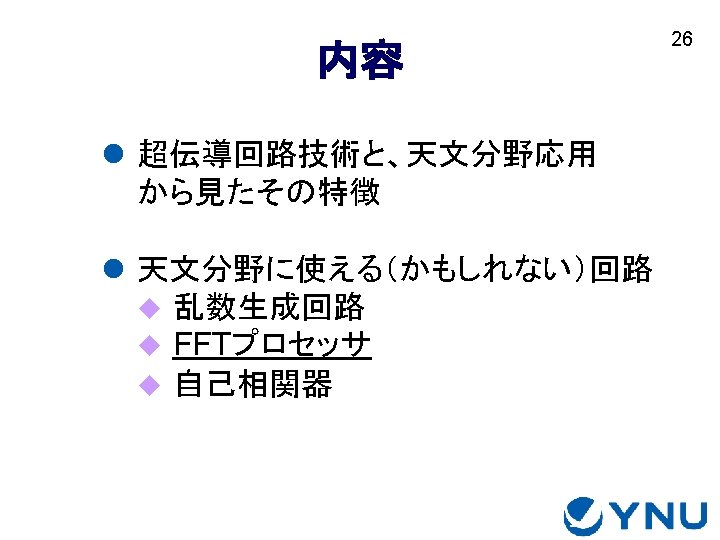

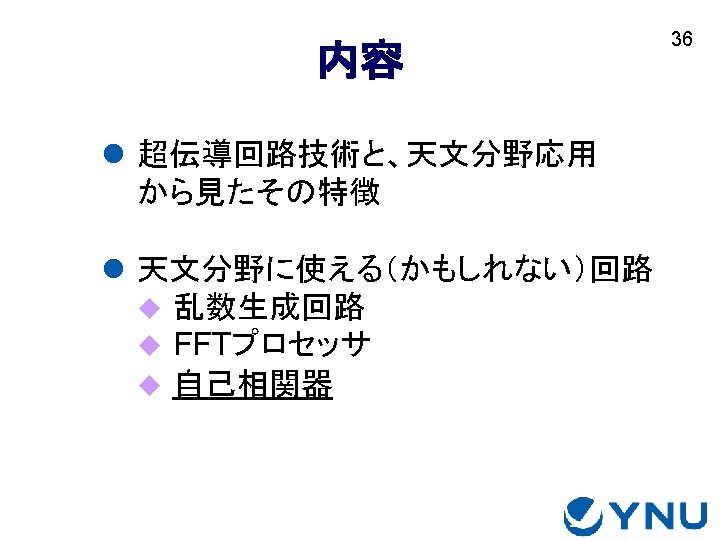

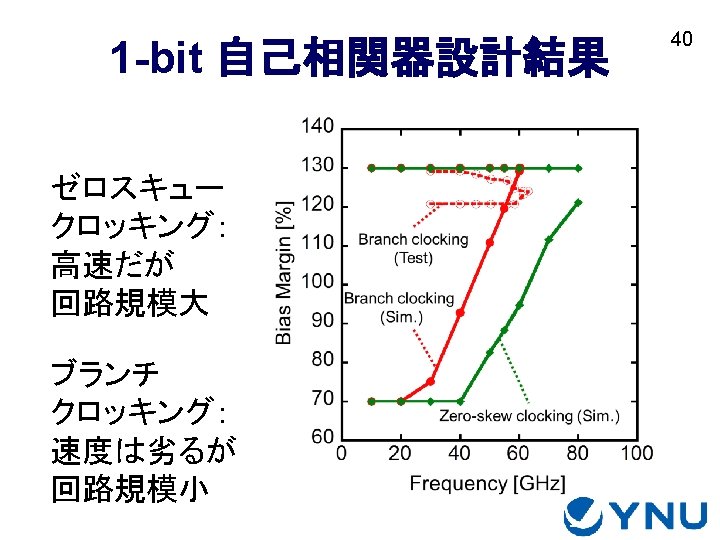

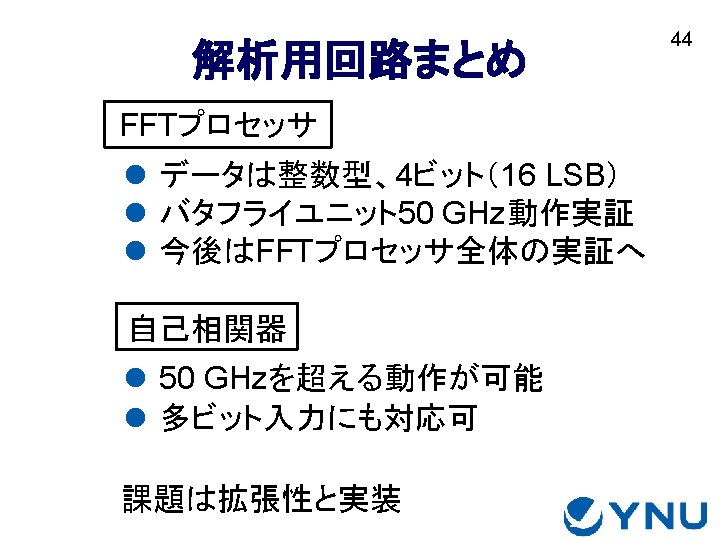

CMOS FFT Processorとの比較 [4] This study 35 Technology Bit-width Power [m. W] Clock Frequency [GHz] Energy per operation (× 10 -12 J) 0. 11 μm 1 mm Nb (JC = 10 k. A/cm 2) 16 2. 17 0. 100 21. 70 16 4. 86 1. 56 3. 115 エネルギー効率で 1桁の優位性 (低電力SFQ回路を使えば 2 -3桁優位) [4] M. Fonsenca et al. , “Design of Pipelined Butterflies from Radix-2 FFT with Decimation in Time Algorithm Using Efficient Adder Compressors”, IEEE Latin American Symposium on Circuit and Systems (LASCAS) 2011.

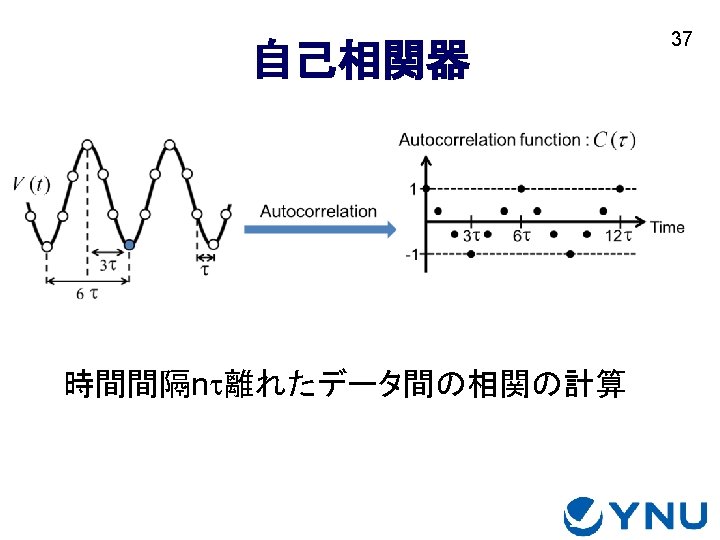

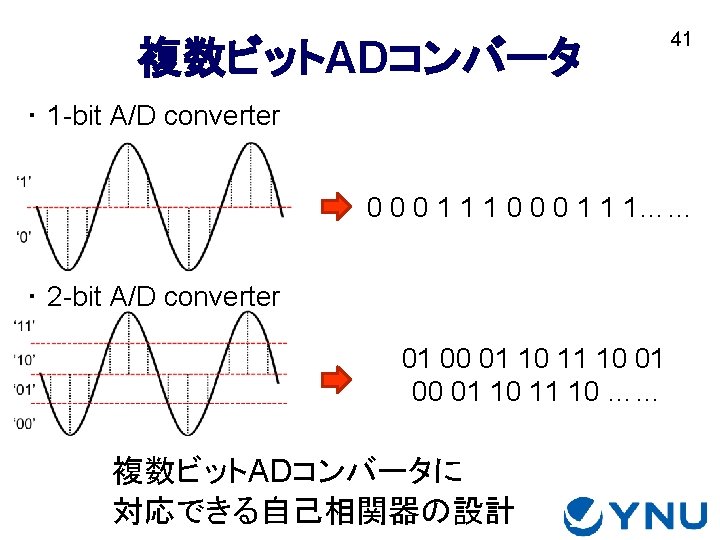

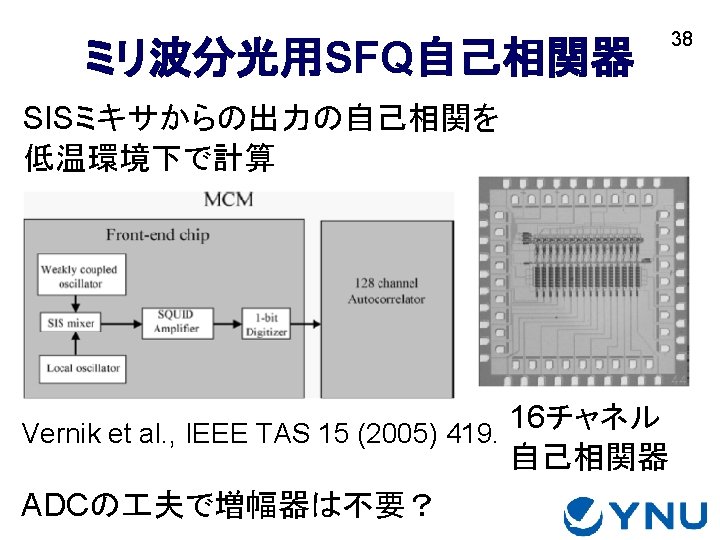

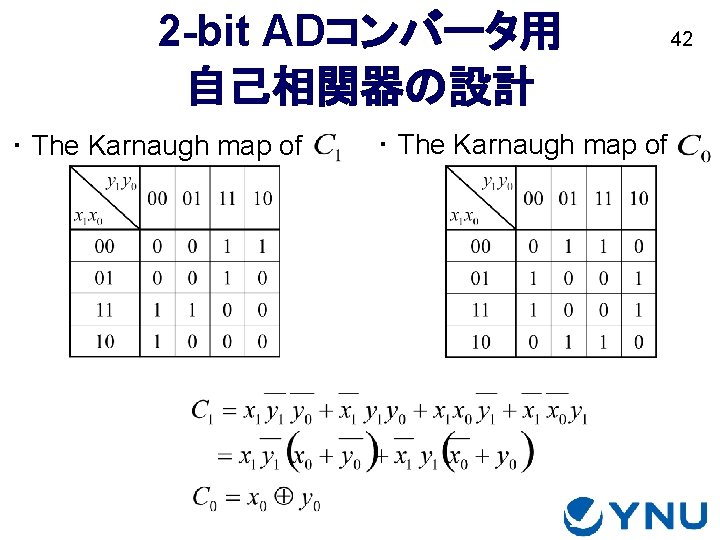

1ビット自己相関器 39 Clock signal interval : t (8 t) (6 t) (4 t) (2 t) Dn : Delay Flip-Flop

47