Simultaneous Sampling ADC Data Acquisition System for the

- Slides: 6

Simultaneous Sampling ADC Data Acquisition System for the QUIET Experiment Mircea Bogdan, Dorothea Samtleben, Keith Vanderlinde The University of Chicago Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 1

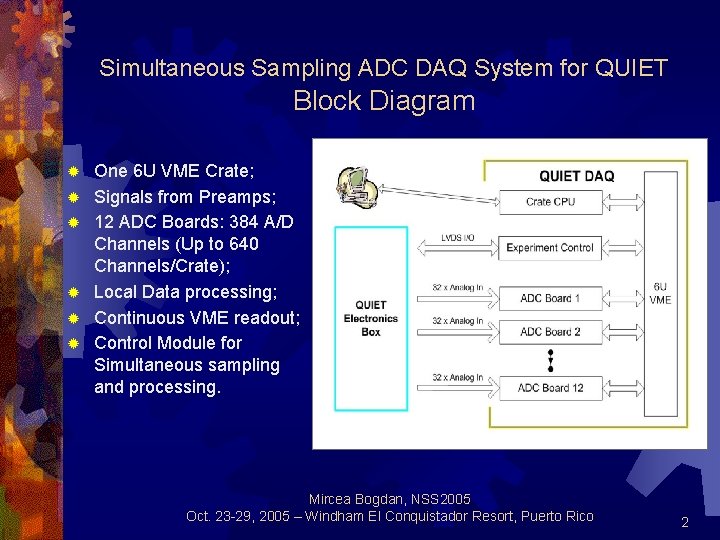

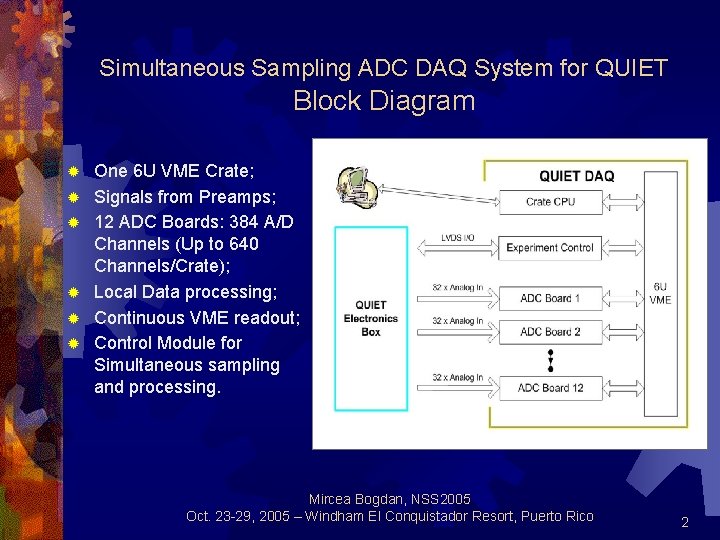

Simultaneous Sampling ADC DAQ System for QUIET Block Diagram ® ® ® One 6 U VME Crate; Signals from Preamps; 12 ADC Boards: 384 A/D Channels (Up to 640 Channels/Crate); Local Data processing; Continuous VME readout; Control Module for Simultaneous sampling and processing. Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 2

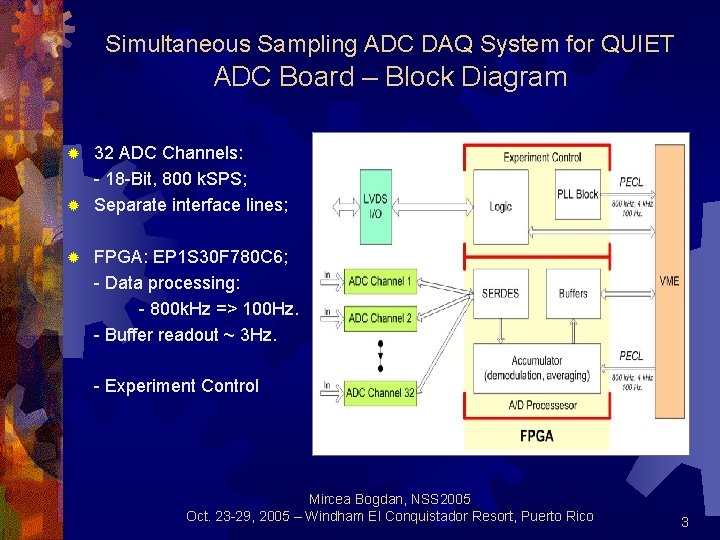

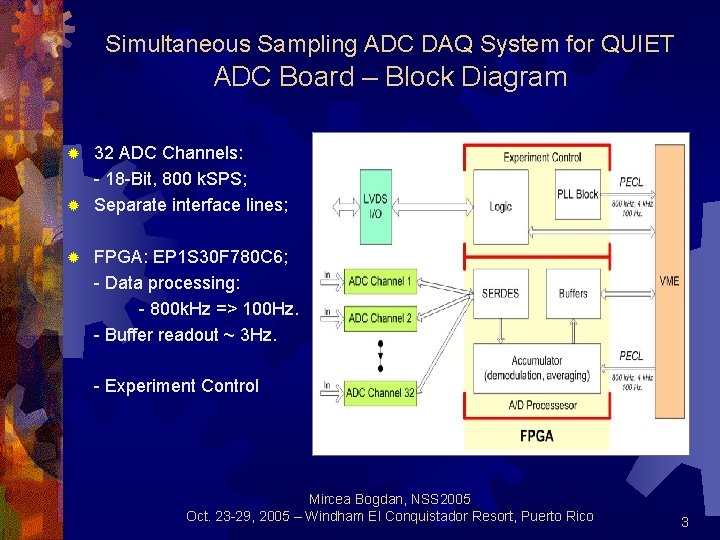

Simultaneous Sampling ADC DAQ System for QUIET ADC Board – Block Diagram 32 ADC Channels: - 18 -Bit, 800 k. SPS; ® Separate interface lines; ® ® FPGA: EP 1 S 30 F 780 C 6; - Data processing: - 800 k. Hz => 100 Hz. - Buffer readout ~ 3 Hz. - Experiment Control Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 3

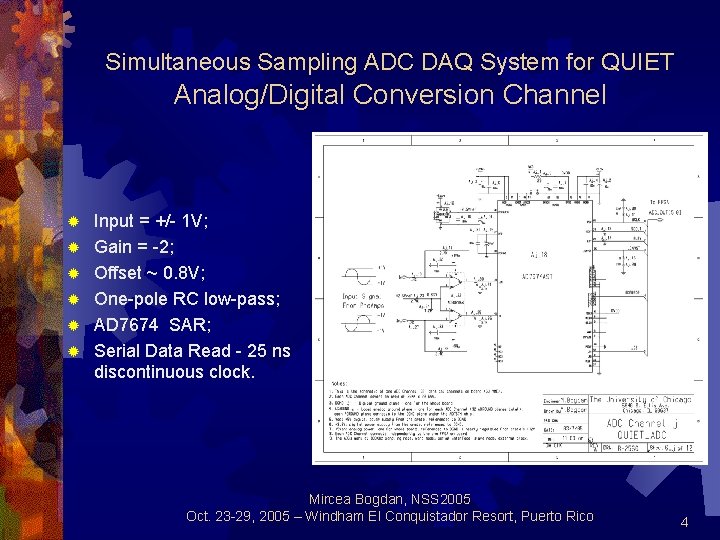

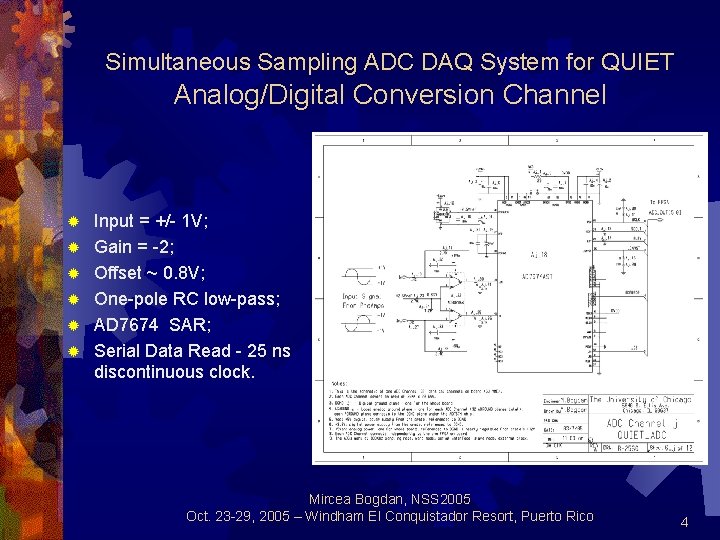

Simultaneous Sampling ADC DAQ System for QUIET Analog/Digital Conversion Channel ® ® ® Input = +/- 1 V; Gain = -2; Offset ~ 0. 8 V; One-pole RC low-pass; AD 7674 SAR; Serial Data Read - 25 ns discontinuous clock. Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 4

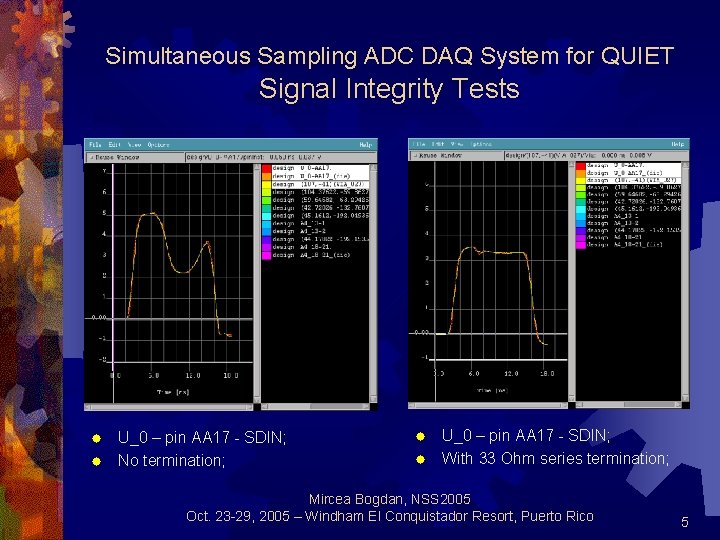

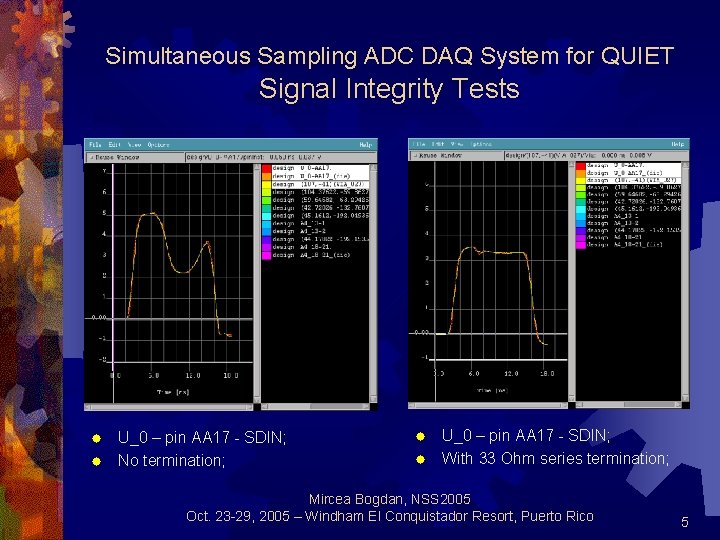

Simultaneous Sampling ADC DAQ System for QUIET Signal Integrity Tests U_0 – pin AA 17 - SDIN; ® No termination; ® U_0 – pin AA 17 - SDIN; ® With 33 Ohm series termination; ® Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 5

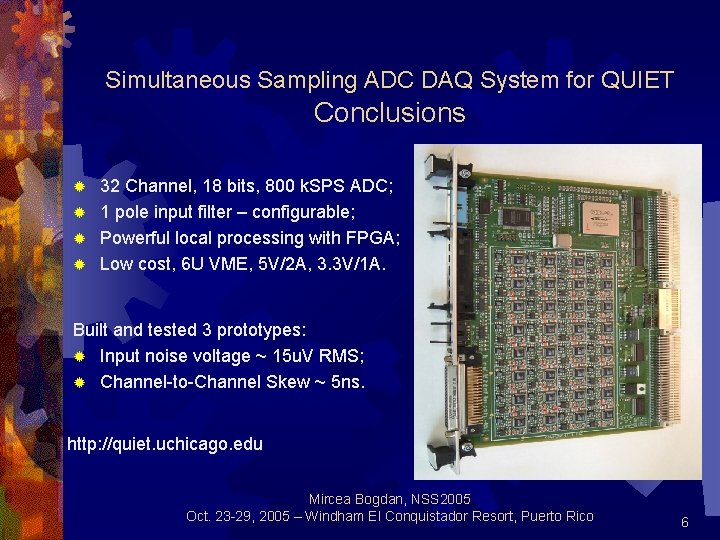

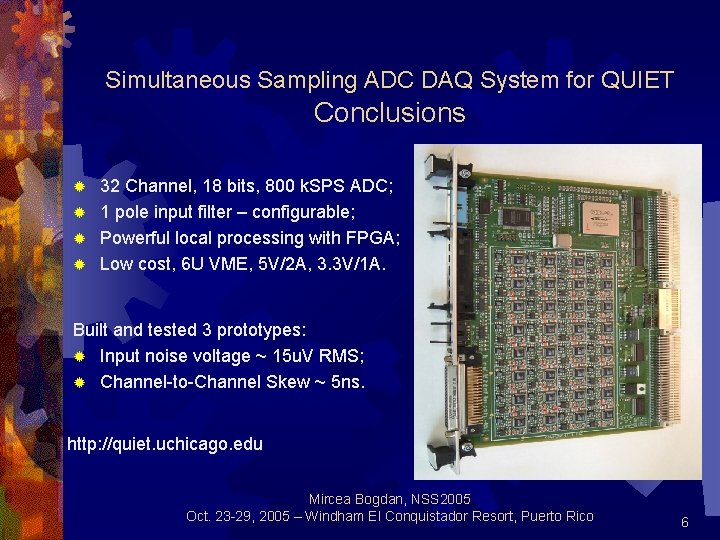

Simultaneous Sampling ADC DAQ System for QUIET Conclusions 32 Channel, 18 bits, 800 k. SPS ADC; ® 1 pole input filter – configurable; ® Powerful local processing with FPGA; ® Low cost, 6 U VME, 5 V/2 A, 3. 3 V/1 A. ® Built and tested 3 prototypes: ® Input noise voltage ~ 15 u. V RMS; ® Channel-to-Channel Skew ~ 5 ns. http: //quiet. uchicago. edu Mircea Bogdan, NSS 2005 Oct. 23 -29, 2005 – Windham El Conquistador Resort, Puerto Rico 6