SimulationBased Reliability Analysis For Advanced Designs and Applications

Simulation-Based Reliability Analysis For Advanced Designs and Applications Xuguang Shen, Joddy Wang 06/20/2019

Outline • Why simulation-based reliability analysis is important • SNPS holistic reliability modeling and simulation(MOSRA) • Failure rate simulation requirements and flow • Showcases Synopsys Confidential Information © 2019 Synopsys, Inc. 2

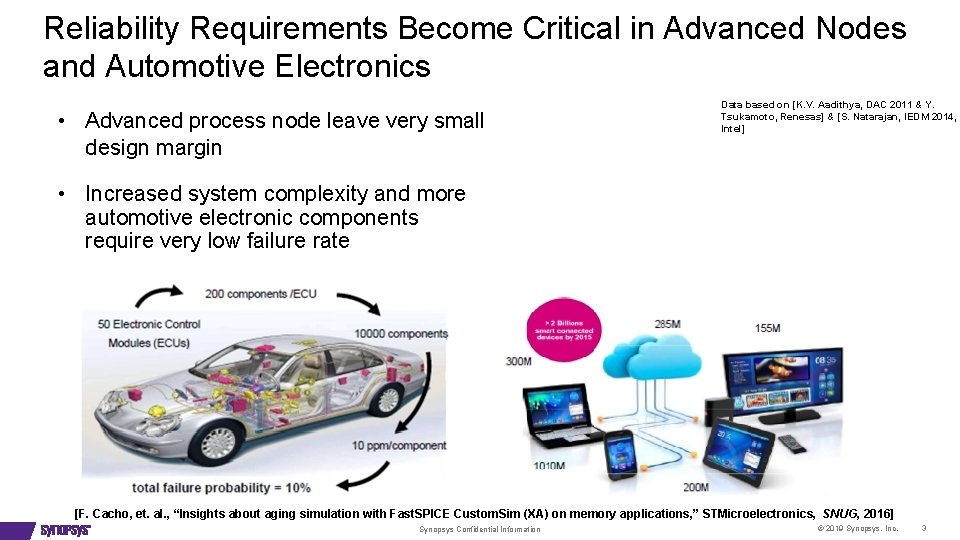

Reliability Requirements Become Critical in Advanced Nodes and Automotive Electronics • Advanced process node leave very small design margin Data based on [K. V. Aadithya, DAC 2011 & Y. Tsukamoto, Renesas] & [S. Natarajan, IEDM 2014, Intel] • Increased system complexity and more automotive electronic components require very low failure rate [F. Cacho, et. al. , “Insights about aging simulation with Fast. SPICE Custom. Sim (XA) on memory applications, ” STMicroelectronics, SNUG, 2016] Synopsys Confidential Information © 2019 Synopsys, Inc. 3

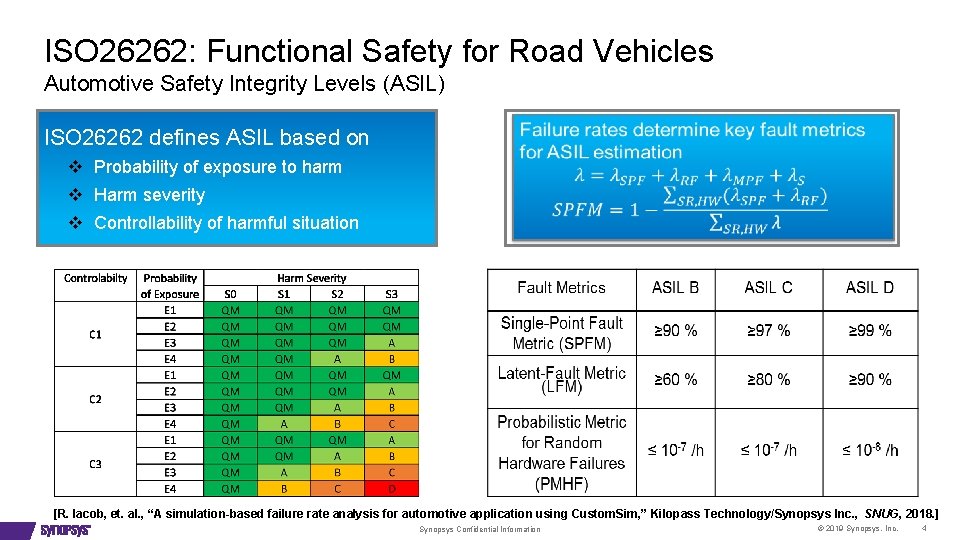

ISO 26262: Functional Safety for Road Vehicles Automotive Safety Integrity Levels (ASIL) ISO 26262 defines ASIL based on v Probability of exposure to harm v Harm severity v Controllability of harmful situation [R. Iacob, et. al. , “A simulation-based failure rate analysis for automotive application using Custom. Sim, ” Kilopass Technology/Synopsys Inc. , SNUG, 2018. ] Synopsys Confidential Information © 2019 Synopsys, Inc. 4

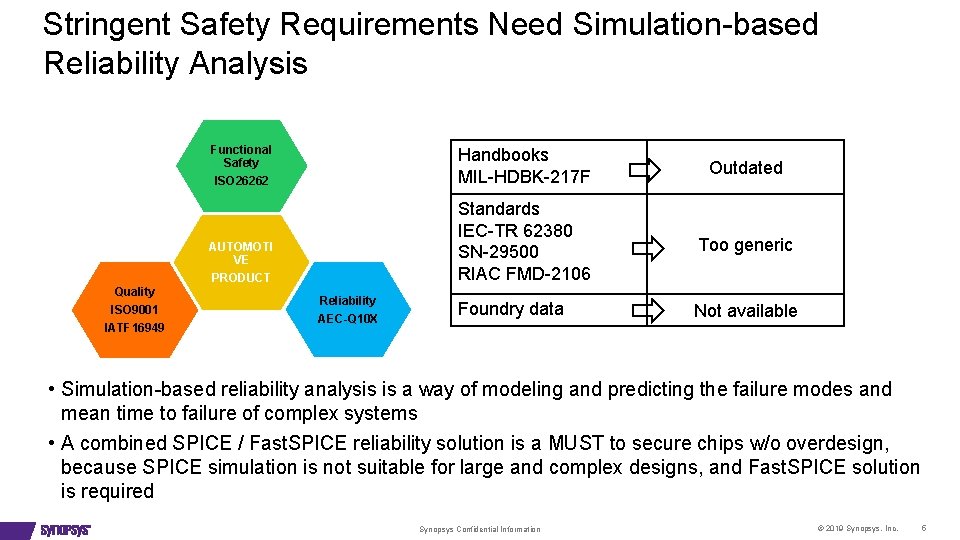

Stringent Safety Requirements Need Simulation-based Reliability Analysis Quality ISO 9001 IATF 16949 Functional Safety ISO 26262 Handbooks MIL-HDBK-217 F Outdated AUTOMOTI VE PRODUCT Standards IEC-TR 62380 SN-29500 RIAC FMD-2106 Too generic Foundry data Not available Reliability AEC-Q 10 X • Simulation-based reliability analysis is a way of modeling and predicting the failure modes and mean time to failure of complex systems • A combined SPICE / Fast. SPICE reliability solution is a MUST to secure chips w/o overdesign, because SPICE simulation is not suitable for large and complex designs, and Fast. SPICE solution is required Synopsys Confidential Information © 2019 Synopsys, Inc. 5

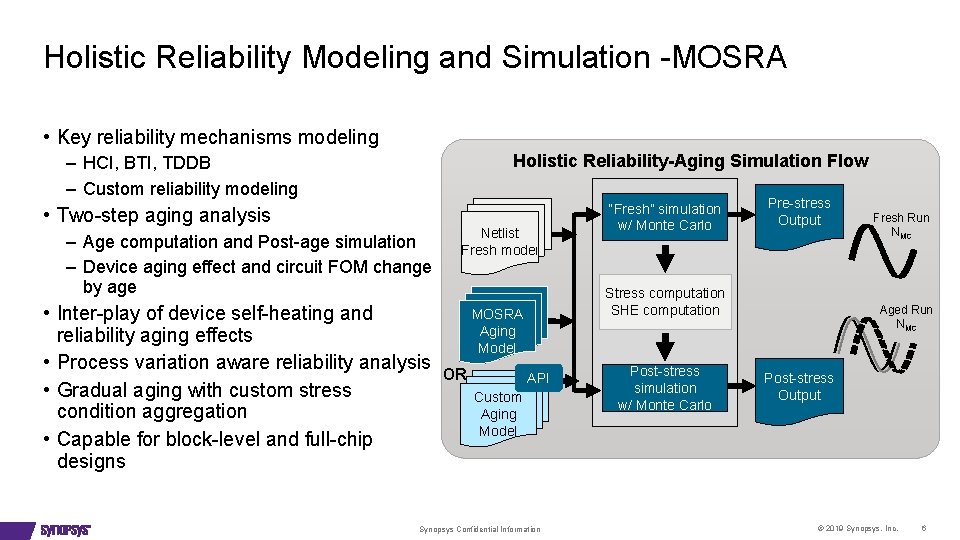

Holistic Reliability Modeling and Simulation -MOSRA • Key reliability mechanisms modeling Holistic Reliability-Aging Simulation Flow – HCI, BTI, TDDB – Custom reliability modeling • Two-step aging analysis – Age computation and Post-age simulation – Device aging effect and circuit FOM change by age • Inter-play of device self-heating and reliability aging effects • Process variation aware reliability analysis • Gradual aging with custom stress condition aggregation • Capable for block-level and full-chip designs Netlist Fresh model Pre-stress Output Stress computation SHE computation MOSRA Aging Model OR “Fresh” simulation w/ Monte Carlo API Custom Aging Model Synopsys Confidential Information Post-stress simulation w/ Monte Carlo Fresh Run NMC Aged Run NMC Post-stress Output © 2019 Synopsys, Inc. 6

Integration of MOSRA in SNPS SPICE/Fast. SPICE Simulators • Data management is critical for efficient reliability-aging simulation – – Multiple-millions components in complex designs, hence Fast. SPICE performance / capacity Huge amount of dynamic transient signals need to be processed for aging computation Millions of unique MOSFETs exists in aged simulation Custom mission profiles, variability-aware aging analysis lead to many simulations in design/verification cycle • Conventional waveform-based post-processing aging analysis approach does not work – Excessive memory and runtime – Limited to very small circuit only • MOSRA integration is seamless integrated in SPICE/Fast. SPICE simulators – Shared simulation database and common input/output data model – In memory computation of aging and post-age simulation – Same SPICE/Fast. SPICE capacity and performance for w/ and w/o aging Synopsys Confidential Information © 2019 Synopsys, Inc. 7

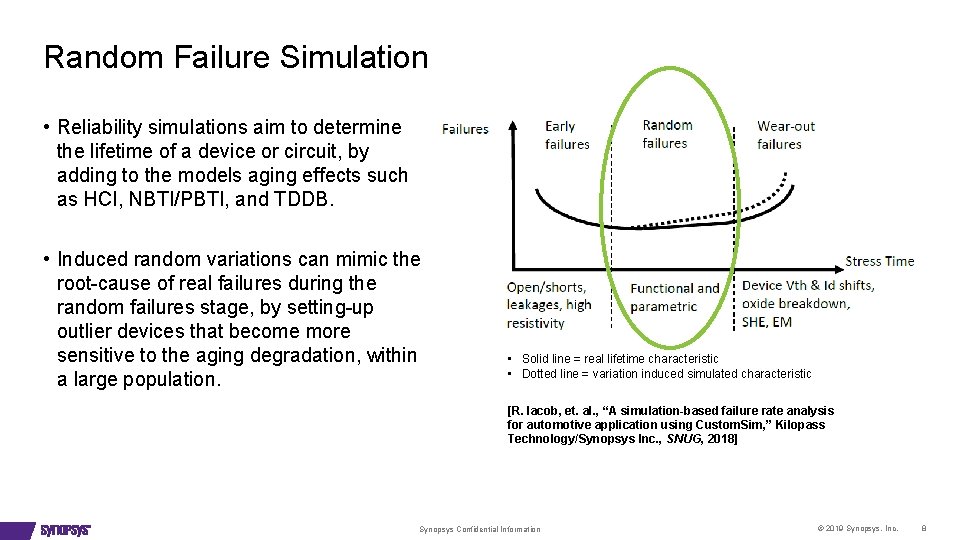

Random Failure Simulation • Reliability simulations aim to determine the lifetime of a device or circuit, by adding to the models aging effects such as HCI, NBTI/PBTI, and TDDB. • Induced random variations can mimic the root-cause of real failures during the random failures stage, by setting-up outlier devices that become more sensitive to the aging degradation, within a large population. • Solid line = real lifetime characteristic • Dotted line = variation induced simulated characteristic [R. Iacob, et. al. , “A simulation-based failure rate analysis for automotive application using Custom. Sim, ” Kilopass Technology/Synopsys Inc. , SNUG, 2018] Synopsys Confidential Information © 2019 Synopsys, Inc. 8

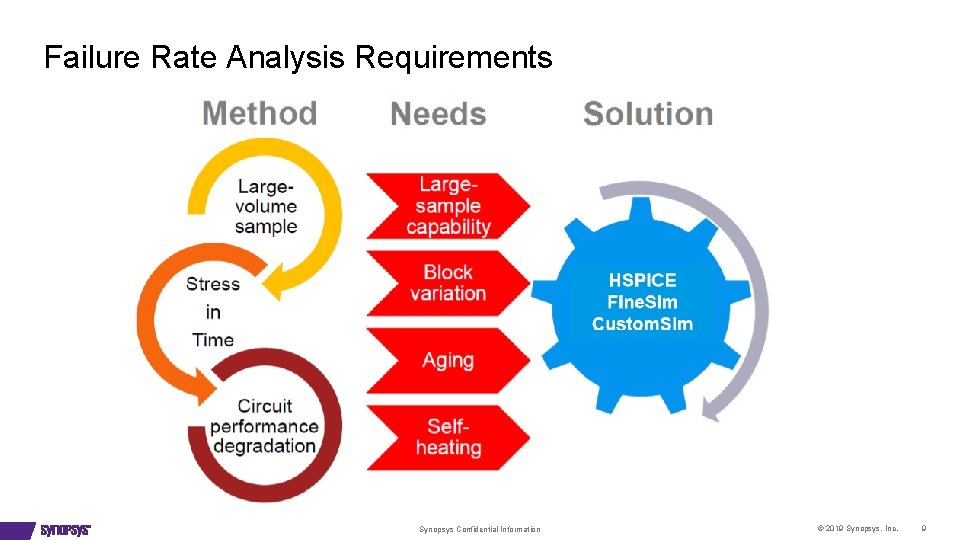

Failure Rate Analysis Requirements Synopsys Confidential Information © 2019 Synopsys, Inc. 9

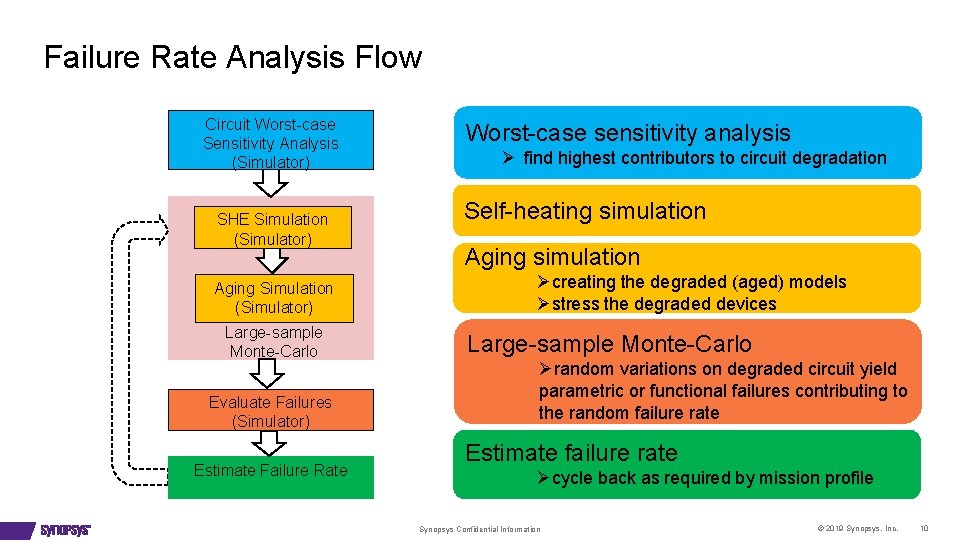

Failure Rate Analysis Flow Circuit Worst-case Sensitivity Analysis (Simulator) SHE Simulation (Simulator) Aging Simulation (Simulator) Large-sample Monte-Carlo Evaluate Failures (Simulator) Estimate Failure Rate Worst-case sensitivity analysis Ø find highest contributors to circuit degradation Self-heating simulation Aging simulation Øcreating the degraded (aged) models Østress the degraded devices Large-sample Monte-Carlo Ørandom variations on degraded circuit yield parametric or functional failures contributing to the random failure rate Estimate failure rate Øcycle back as required by mission profile Synopsys Confidential Information © 2019 Synopsys, Inc. 10

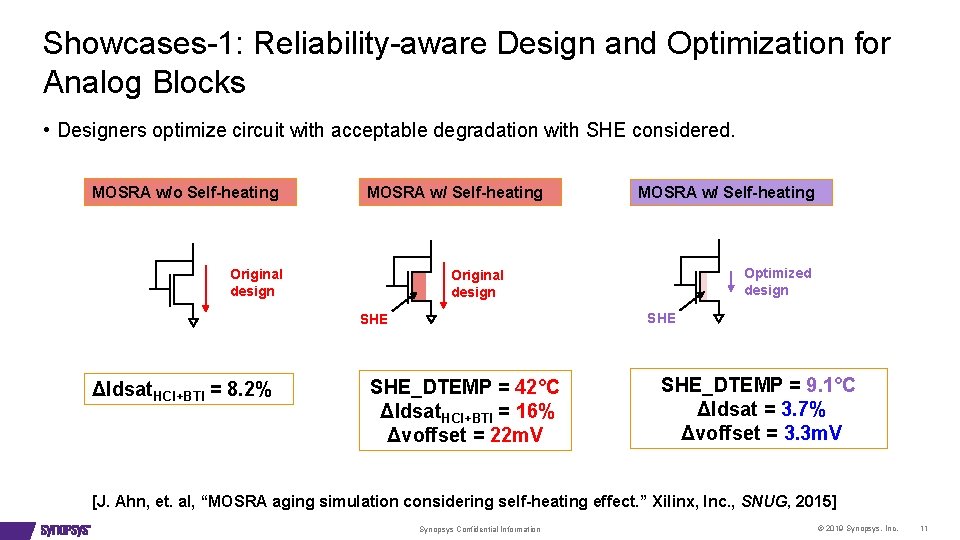

Showcases-1: Reliability-aware Design and Optimization for Analog Blocks • Designers optimize circuit with acceptable degradation with SHE considered. MOSRA w/o Self-heating MOSRA w/ Self-heating Original design Optimized design Original design SHE ΔIdsat. HCI+BTI = 8. 2% MOSRA w/ Self-heating SHE_DTEMP = 42°C ΔIdsat. HCI+BTI = 16% Δvoffset = 22 m. V SHE_DTEMP = 9. 1°C ΔIdsat = 3. 7% Δvoffset = 3. 3 m. V [J. Ahn, et. al, “MOSRA aging simulation considering self-heating effect. ” Xilinx, Inc. , SNUG, 2015] Synopsys Confidential Information © 2019 Synopsys, Inc. 11

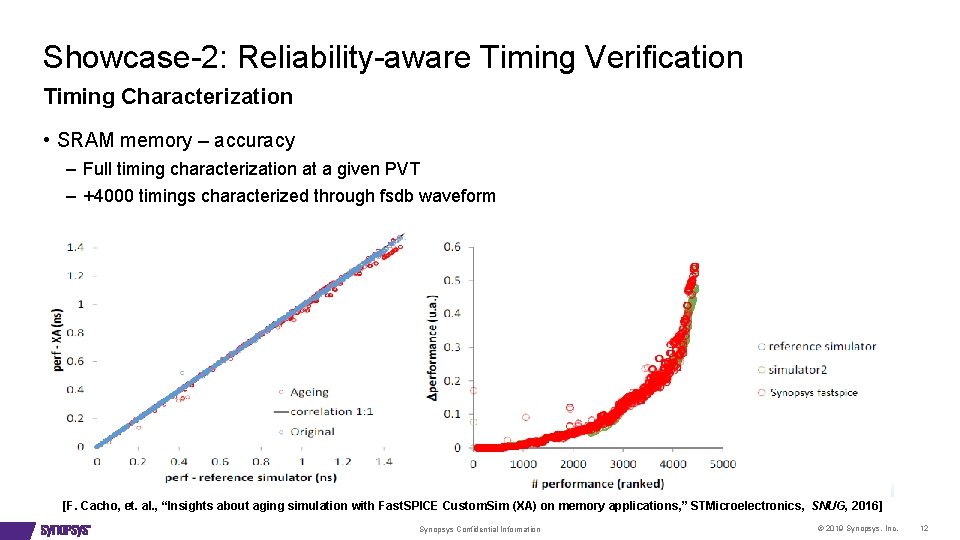

Showcase-2: Reliability-aware Timing Verification Timing Characterization • SRAM memory – accuracy – Full timing characterization at a given PVT – +4000 timings characterized through fsdb waveform [F. Cacho, et. al. , “Insights about aging simulation with Fast. SPICE Custom. Sim (XA) on memory applications, ” STMicroelectronics, SNUG, 2016] Synopsys Confidential Information © 2019 Synopsys, Inc. 12

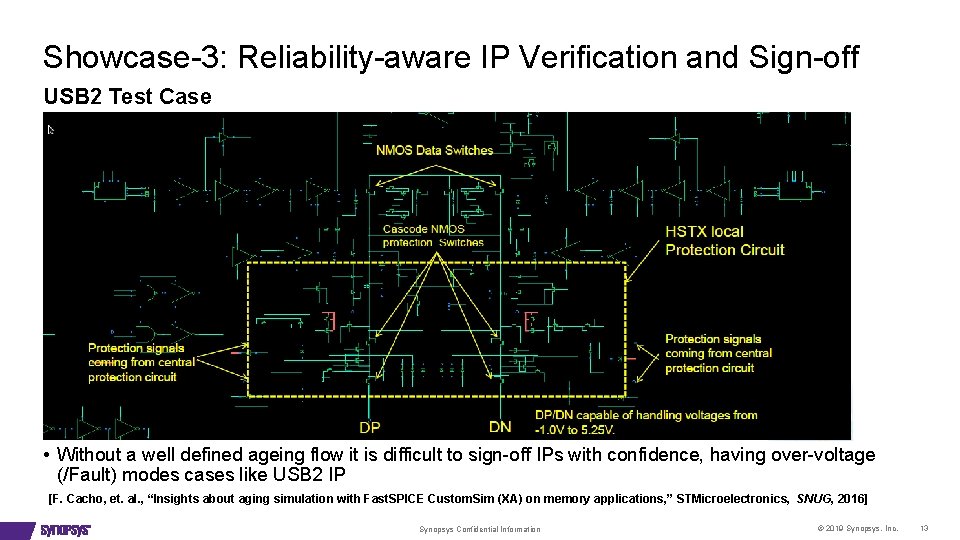

Showcase-3: Reliability-aware IP Verification and Sign-off USB 2 Test Case • Without a well defined ageing flow it is difficult to sign-off IPs with confidence, having over-voltage (/Fault) modes cases like USB 2 IP [F. Cacho, et. al. , “Insights about aging simulation with Fast. SPICE Custom. Sim (XA) on memory applications, ” STMicroelectronics, SNUG, 2016] Synopsys Confidential Information © 2019 Synopsys, Inc. 13

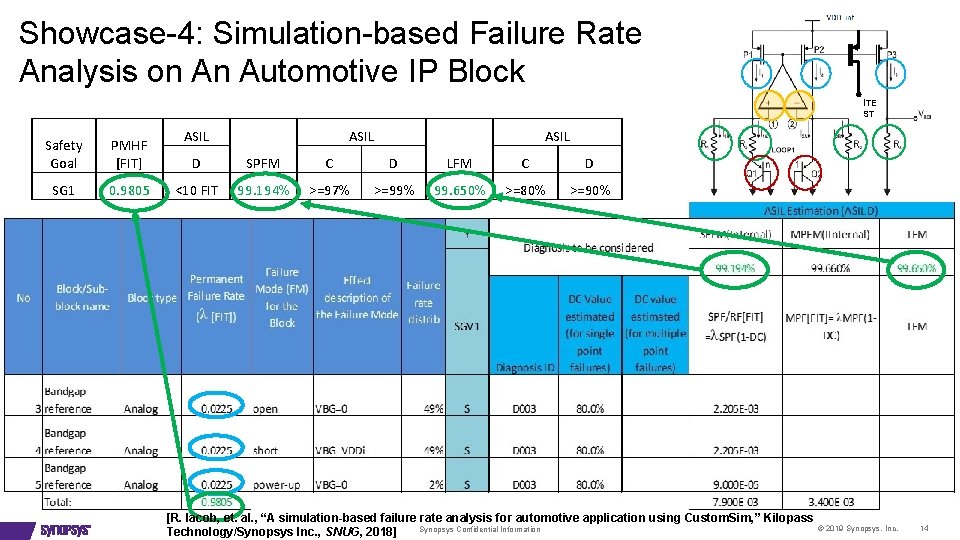

Showcase-4: Simulation-based Failure Rate Analysis on An Automotive IP Block ITE ST Safety Goal PMHF [FIT] SG 1 0. 9805 ASIL D SPFM C D LFM C D <10 FIT 99. 194% >=97% >=99% 99. 650% >=80% >=90% SEoo. C: current-mode bandgap reference [R. Iacob, et. al. , “A simulation-based failure rate analysis for automotive application using Custom. Sim, ” Kilopass © 2019 Synopsys, Inc. Synopsys Confidential Information Technology/Synopsys Inc. , SNUG, 2018] 14

Summary • Neither outdated handbooks nor too generic standards can meet the stringent safety requirements due to system complexity and advanced node development. • Simulation-based reliability analysis is a way of modeling and predicting the failure modes and mean time to failure of complex systems. • Synopsys simulation tool provides comprehensive reliability analysis, with high performance and capacity, makes a simulation-based approach for advanced design and application become possible. Synopsys Confidential Information © 2019 Synopsys, Inc. 15

References and Acknowledgement • References – A. Fan, et. al. , “Advanced Circuit Reliability Verification for Robust Design”, IRPS, 2019 – R. Wang, et. al. , “Random telegraph noise (RTN) in advanced logic devices and circuits, ” IEDM, 2018. – R. Iacob, et. al. , “A simulation-based failure rate analysis for automotive application using Custom. Sim, ” Kilopass Technology/Synopsys Inc. , SNUG, 2018. – K. Khu, et. al. , “Custom MOSRA model with gate voltage effect for aging simulation, ” TDK-Micronas Gmb. H and Ad. MOS Gmb. H, SNUG, 2018. – H. Thanikasalam, “Self-Heat Aware EM Simulation and Analysis with Custom. Sim™ for Fin. FET Devices and Smaller Geometries, ” Synopsys, SNUG, 2017. – F. Cacho, et. al. , “Insights about aging simulation with Fast. SPICE Custom. Sim (XA) on memory applications, ” STMicroelectronics, SNUG, 2016. – J. Ahn, et. al, “MOSRA aging simulation considering self-heating effect. ” Xilinx, Inc. , SNUG, 2015. – L. Li, “ 28 nm MOSFET Aging Modeling and Simulation using HSPICE”, Altera/Intel Corp. , SNUG, 2011. • Thanks to Zhaoping Chen and Dehuang Wu for their valuable discussions Synopsys Confidential Information © 2019 Synopsys, Inc. 16

- Slides: 16