Silicon Zero Suppression System Piotr Kulinich March 18

![Protocol for ®Mode=0�(System) to RACEway TIME from RACEway N_codes= 4*N_DACs +[Reset_? +Xilinx_? ] 31 Protocol for ®Mode=0�(System) to RACEway TIME from RACEway N_codes= 4*N_DACs +[Reset_? +Xilinx_? ] 31](https://slidetodoc.com/presentation_image/829e20d6b1f57117fa67d2ad04f3c716/image-16.jpg)

- Slides: 19

Silicon Zero Suppression System Piotr Kulinich March 18, 2000 (some small correction from Sept 2002)

Main task �Collect data from all Front-End-Controllers (FEC) �Ship data on optical fibers to the counting room for processing in Mercury Crate �Distribute trigger, control and calibration signals to the FEC� s (VA and silicon detectors)

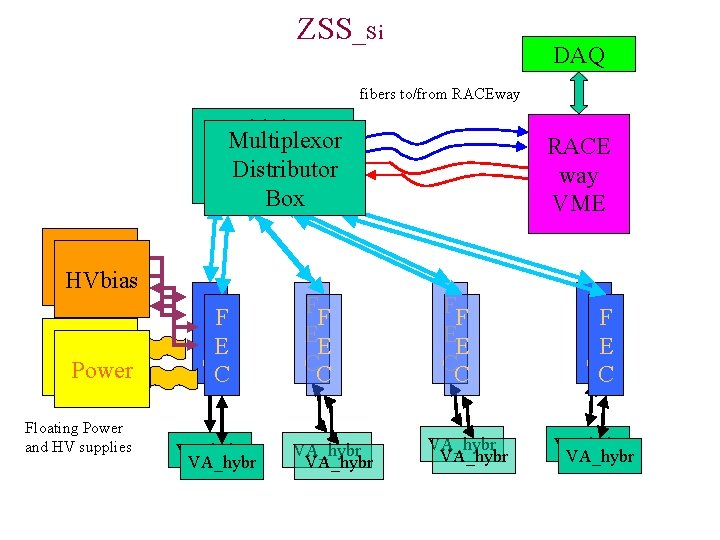

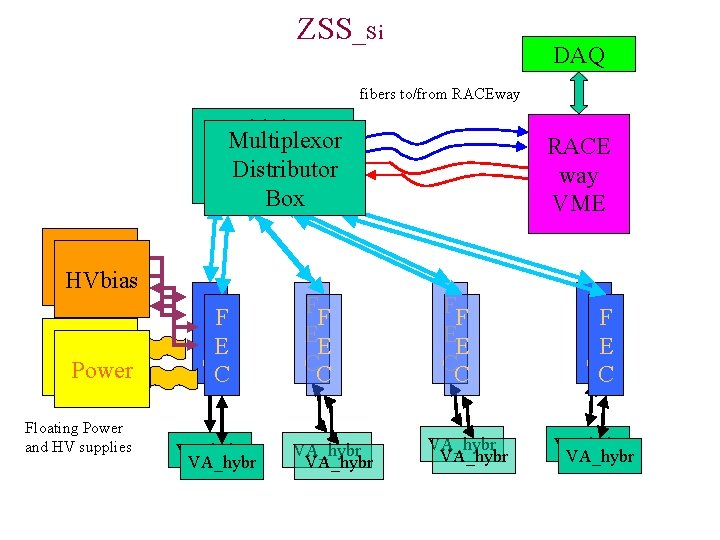

ZSS_Si DAQ fibers to/from RACEway Multiplexor Distributor Box HVbias Power Floating Power and HV supplies FF EE CC VA_hybr RACE way VME FF EE CC VA_hybr

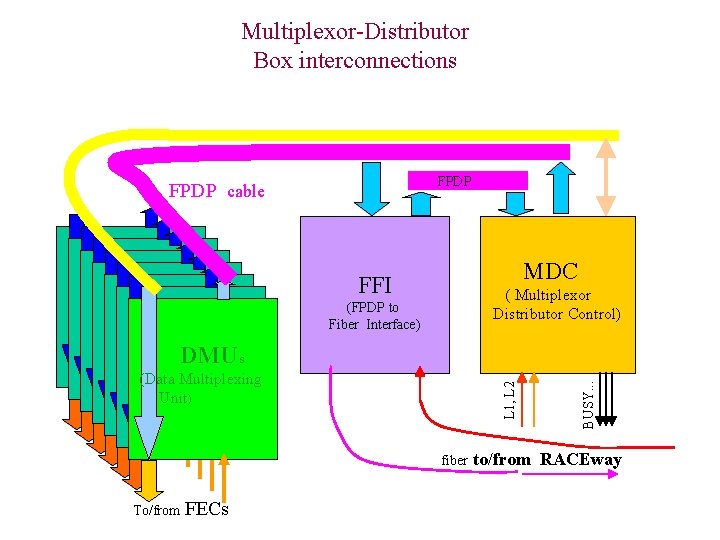

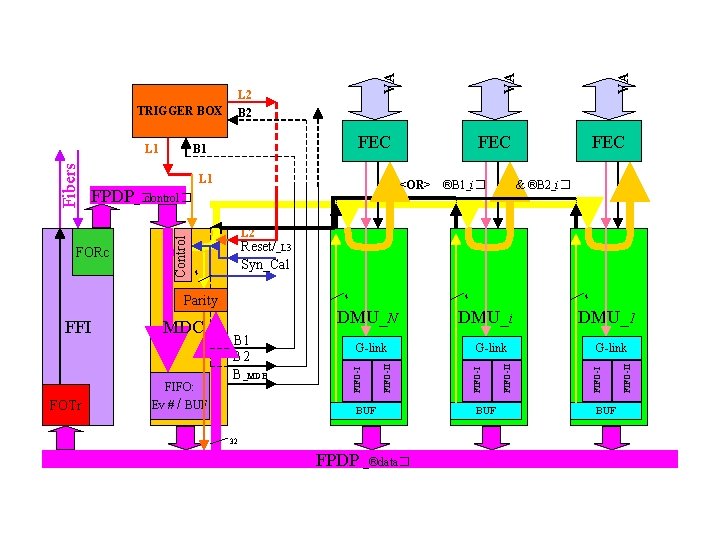

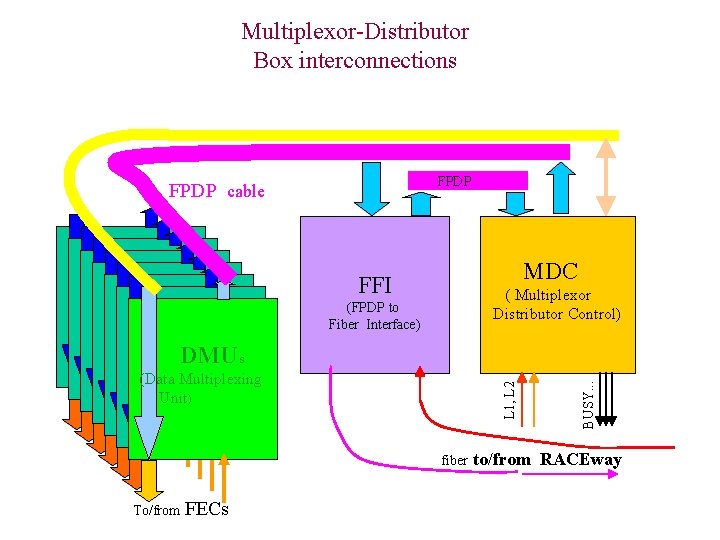

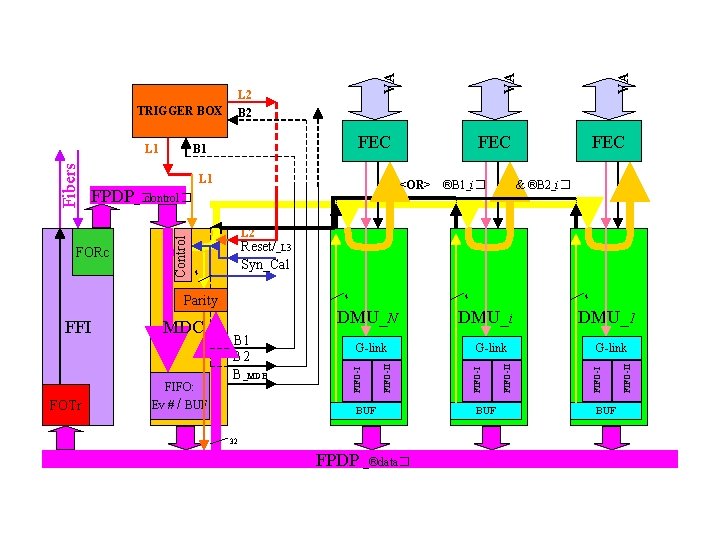

Multiplexor Distributor Box �Input: Data - from FECs, Control - from RACEway by fiber �Output: Data on fiber to Raceway Crate �Consists of three sub-modules (connected by FPDP interconnect) �DMU (one for each FEC) �MDC (currently 2) �FFI (currently 4), =2 pairs of fibers to the counting room

Now: � ~26 DMU tested � 3 MDC� s are available � 5 FFI� s are available. . .

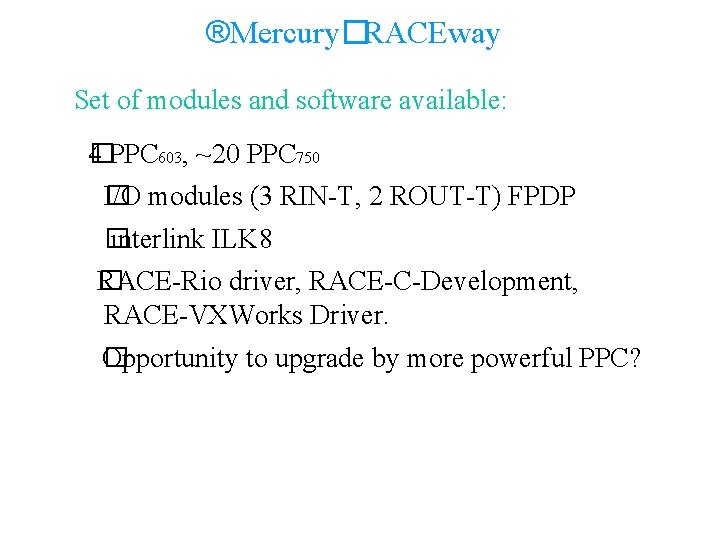

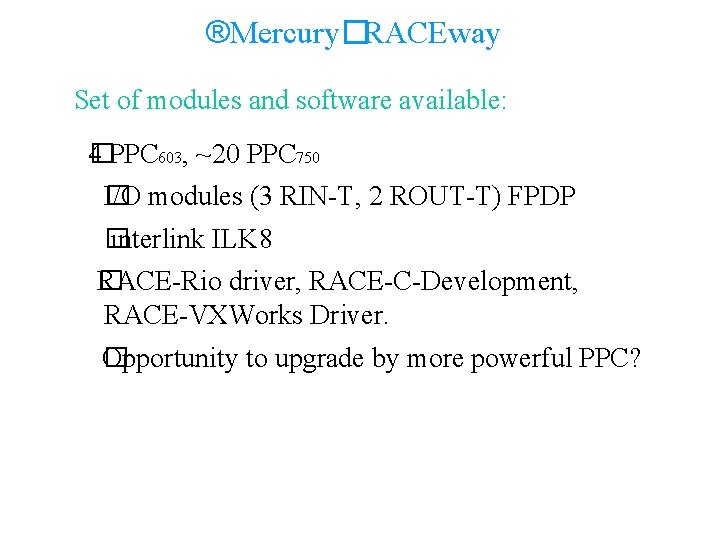

®Mercury�RACEway Set of modules and software available: 4 PPC 603, ~20 PPC 750 � I/O modules (3 RIN-T, 2 ROUT-T) FPDP � � interlink ILK 8 �ACE-Rio driver, RACE-C-Development, R RACE-VXWorks Driver. Opportunity to upgrade by more powerful PPC? �

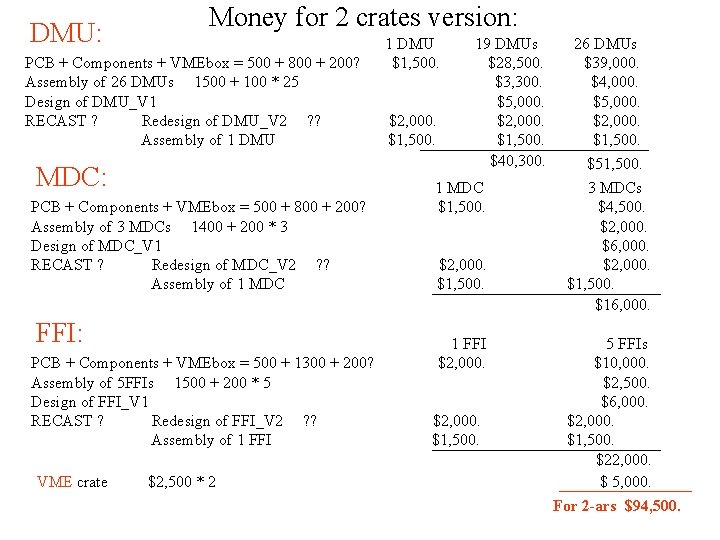

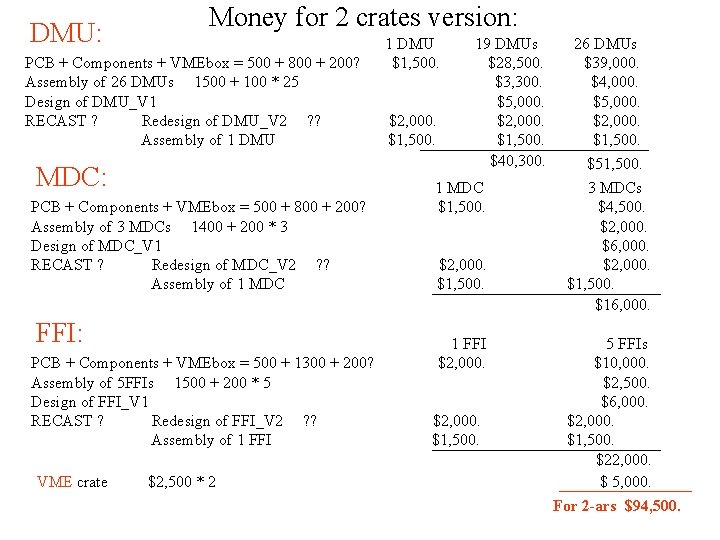

DMU: Money for 2 crates version: PCB + Components + VMEbox = 500 + 800 + 200? Assembly of 26 DMUs 1500 + 100 * 25 Design of DMU_V 1 RECAST ? Redesign of DMU_V 2 ? ? Assembly of 1 DMU MDC: PCB + Components + VMEbox = 500 + 800 + 200? Assembly of 3 MDCs 1400 + 200 * 3 Design of MDC_V 1 RECAST ? Redesign of MDC_V 2 ? ? Assembly of 1 MDC FFI: PCB + Components + VMEbox = 500 + 1300 + 200? Assembly of 5 FFIs 1500 + 200 * 5 Design of FFI_V 1 RECAST ? Redesign of FFI_V 2 ? ? Assembly of 1 FFI VME crate $2, 500 * 2 1 DMU $1, 500. $2, 000. $1, 500. 19 DMUs $28, 500. $3, 300. $5, 000. $2, 000. $1, 500. $40, 300. 1 MDC $1, 500. $2, 000. $1, 500. 1 FFI $2, 000. $1, 500. 26 DMUs $39, 000. $4, 000. $5, 000. $2, 000. $1, 500. $51, 500. 3 MDCs $4, 500. $2, 000. $6, 000. $2, 000. $1, 500. $16, 000. 5 FFIs $10, 000. $2, 500. $6, 000. $2, 000. $1, 500. $22, 000. $ 5, 000. For 2 -ars $94, 500.

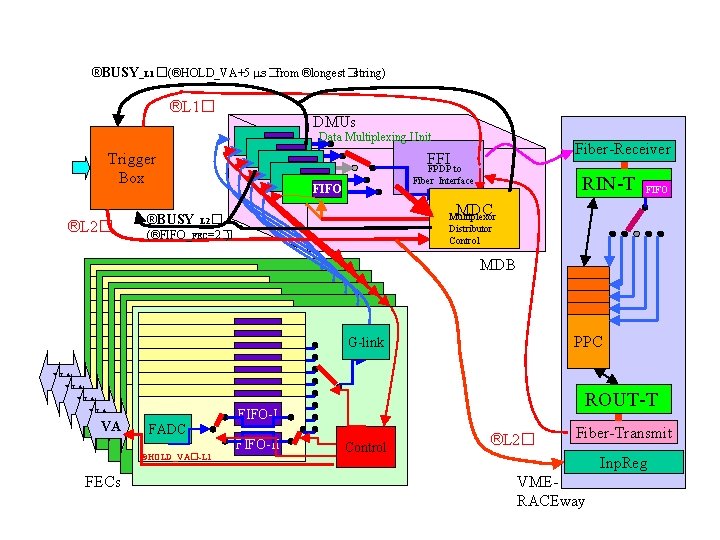

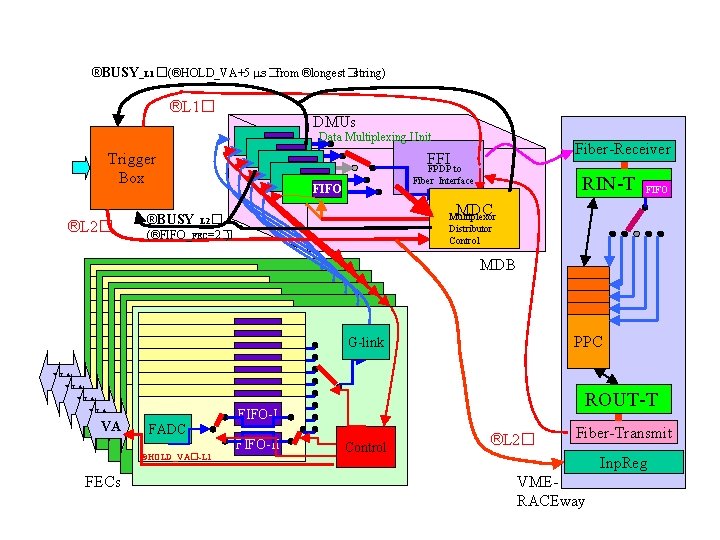

®BUSY_L 1�(®HOLD_VA+5 ms�from ®longest�string) . ®L 1� DMUs Data Multiplexing Unit ®L 2� Fiber-Receiver FFI FPDP to Trigger Box . RIN-T Fiber Interface FIFO MDC Multiplexor Distributor Control ®BUSY_L 2� (®FIFO_FEC=2� ) MDB FIFO-I FIFO-I FADC FADC FIFO-II FIFO-I FIFO-I FADC FIFO-II FIFO-II FIFO-I FIFO-I FIFO-I FADC FADC FADC FIFO-II FIFO-II FIFO-I FIFO-I FADC FADC FADC FIFO-II FIFO-II FIFO-II FIFO-I FIFO-I VA FADC FIFO-II FIFO-II FIFO-I VA FADC FIFO-II FIFO-I VA FADC FIFO-II FIFO-II ®HOLD_VA�~L 1 FECs PC PC PPC G-link G-link ROUT-T Control ®L 2� Fiber-Transmit Inp. Reg VMERACEway

Multiplexor-Distributor Box interconnections FPDP MDC FFI ( Multiplexor Distributor Control) (FPDP to Fiber Interface) L 1, L 2 F F I F I FF F O FI IF O F I O F s DMU G-link O (Data Multiplexing O G-link Unit ) G-link fiber To/from FECs BUSY. . . FPDP cable to/from RACEway

TRIGGER BOX L 1 VA VA & ®B 2_i� Reset/_L 3 Syn_Cal Ev # / BUF G-link BUF 32 FPDP _®data� DMU_i G-link BUF DMU_1 G-link BUF FIFO-II B 1 B 2 B_MDB 4 FIFO-I DMU_N FIFO-II MDC 4 FIFO-II 4 FIFO-I 4 FIFO: FOTr FEC L 2 Parity FFI FEC <OR> ®B 1_i� FIFO-I FPDP_�control� FORc FEC B 1 Control Fibers L 1 VA L 2 B 2

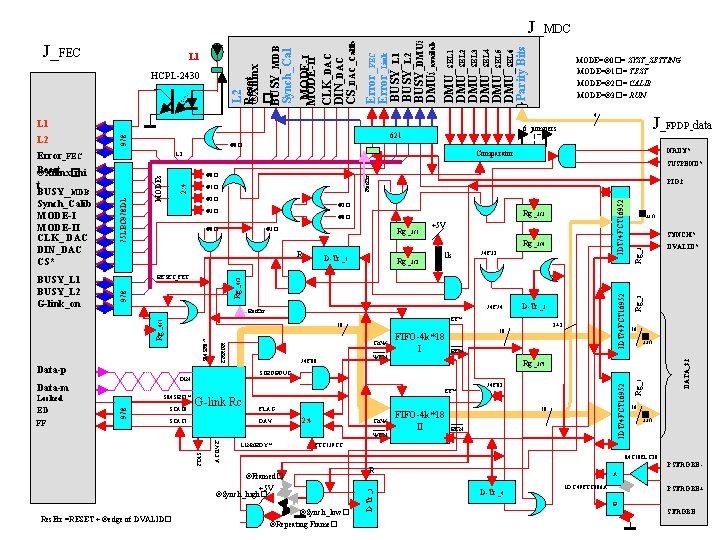

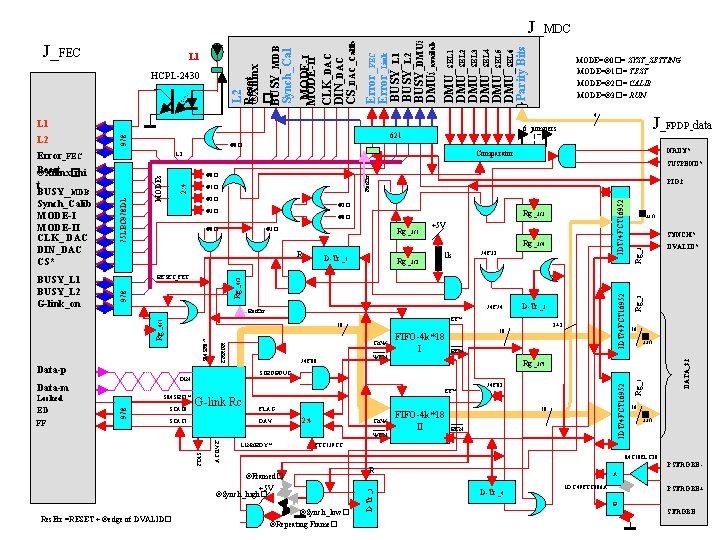

HCPL-2430 Error_FEC Error_Link BUSY_L 1 BUSY_L 2 BUSY_DMUi_availab DMU_SEL 1 DMU_SEL 2 DMU_SEL 3 DMU_SEL 4 DMU_SEL 5 DMU_SEL 6 Parity Bits L 1 MODEII CLK_DAC DIN_DAC CS_DAC_Calib J_FEC L 2 Reset ®Xilinx � BUSY_MDB Synch_Cal J_MDC 4 L 1 978 Res. Err PIO 2 ® 3� Rg _3/1 Rg _3/4 R Rg _3/2 1 k ERROR SMSR 0* 18 74 F 08 ____ REN 16 33 W Rg _3/5 ACTIVE LINKRDY* 2: 4 CKW ____ WEN FIFO-4 k*18 II 18 ____ REN Rg_1 74 F 02 IDT 74 FCT 16952 FLAG DAV 16 33 W FCT 139 CT MC 10 ELT 28 R ®Framed� +5 V ®Synch_high� ®Synch_low� ®Repeating Frame� D-Tr _2 G-link Rc FDIS 978 2+2 18 EF* STAT 1 Res. Err =RESET + ®edge of DVALID� CKW ____ WEN FIFO-4 k*18 I DVALID* STROBOUT DIN STAT 0 D-Tr _3 EF* SYNCH* IDT 74 FCT 16952 74 F 74 Res. Err SM SRT 1* 74 F 32 Rg _4/2 RESET_FEC D-Tr _1 33 W DATA_32 ® 0� +5 V Rg_3 Rg _3/3 ® 0� Rg_2 ® 2� ® 3� IDT 74 FCT 16952 2: 4 MODEs ® 1� ® 2� Data-m FF NRDY* SUSPEND* Data-p Locked ED _ Comparator ® 0� Rg _4/1 BUSY_L 2 G-link_on ® 0� L 2 75 LBC 978 DL Error_FEC Reset ini ®Xilinx� t BUSY_MDB Synch_Calib MODE-II CLK_ DAC DIN_DAC CS* J_FPDP data 6 jumpers 621 978 L 2 MODE=® 0�= SYST_SETTING MODE=® 1�= TEST MODE=® 2�= CALIB MODE=® 3�= RUN PSTROBE - A D-Tr _4 IDT 49 FCT 806 A PSTROBE+ B STROBE

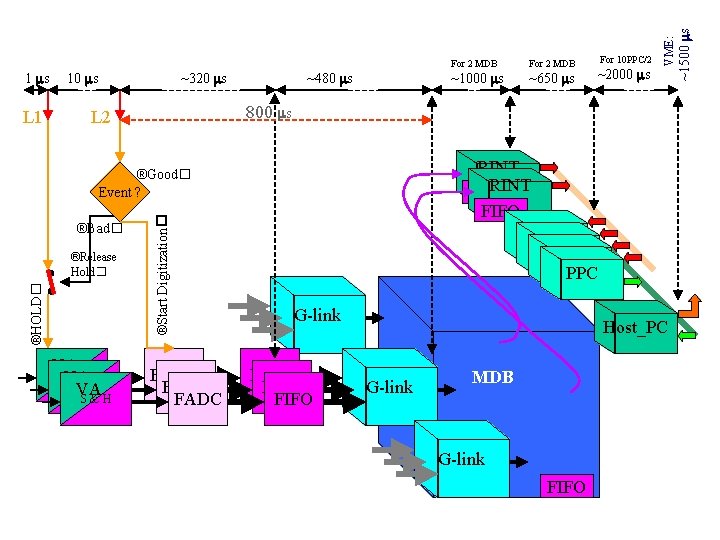

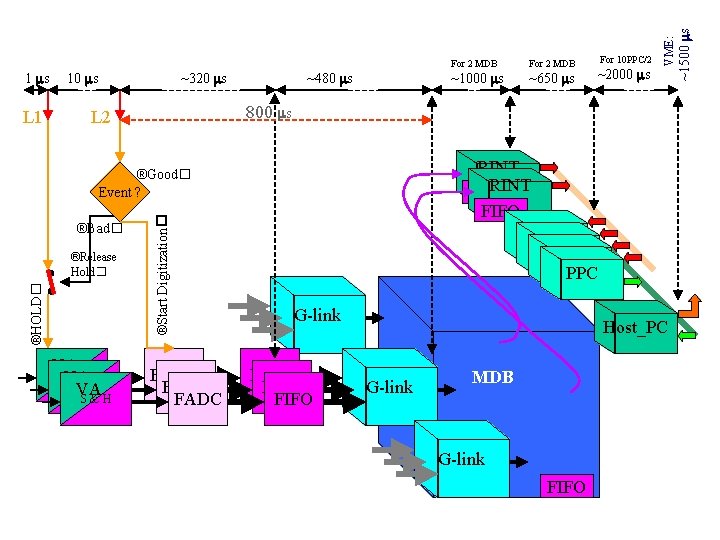

L 1 10 ms ~320 ms ~1000 ms ~480 ms ®Start Digitization� ®HOLD� VA S VA &H S&H VME: ~2000 ms RINT FIFO PPC PPC ®Good� Event ? ®Release Hold� ~650 ms For 10 PPC/2 800 ms L 2 ®Bad� For 2 MDB FADC G-link FIFO Host_PC G-link MDB G-link FIFO ~1500 ms 1 ms For 2 MDB

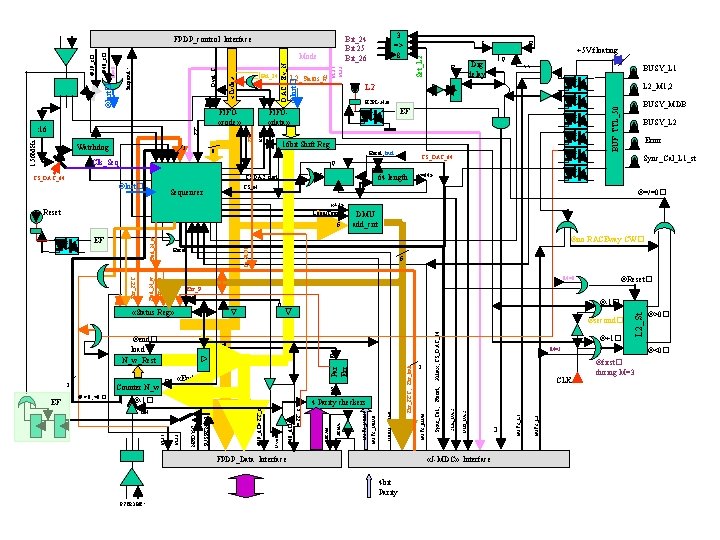

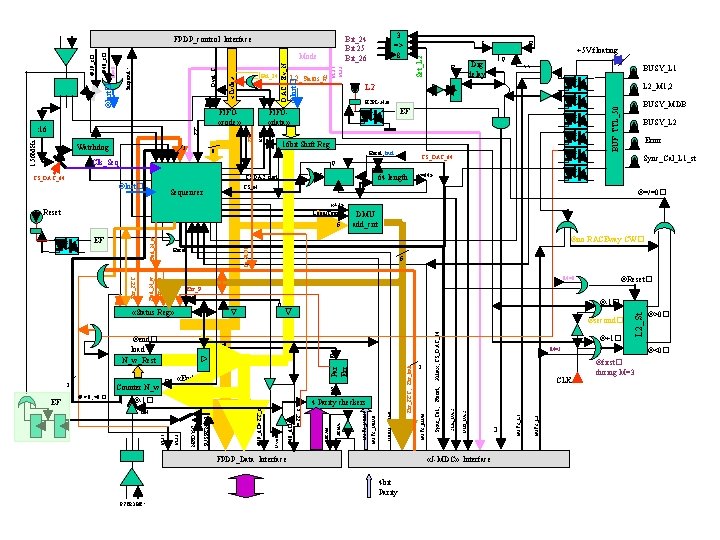

3 S Sequencer Sync_Cal_L 1_st «=64» DMU add_cnt Bad_N_w ®no RACEway CW� To PIO 1 Reset 6 Err_P FPDP_Data Interface «J-MDC» Interface 4 bit Parity BUSY_L 2 BUSY_L 1 L 2 CLK_DAC DMUi_availab BUSY_DMUi OEBA OEAB ® 40_d� = FF_c DValid NRDY* SUSPEND* PIO 2 PIO 1 ® 39_d�= EF_c 4 Parity checkers EN CLK DIN_DAC ®-1� ®+1� ®>0� ®<0� M=3 Reset, S 2 BUSY_MDB «End_Res» Err_FEC, Err_link R Par Err R Sync_Cal, ®end� load N_w_Rest Xilinx, CS_DAC_64 ®second� L 2_St ®-1� o o «Status Reg» Counter N_w ®Reset� M=0 Bad_N_w Err_Link Err_FEC Error ®=/=0� 6 PSTROBE, * BUSY_L 2 CS_DAC_64 64 length «+1» Load/Count ® >0, <0 � BUSY_MDB CS_64 Reset EF Set_L 2 PIO 1 PIO 2 DAC / Ev_N CLR Reset, Init CS_DAC_start 2 L 2_M 1, 2 Q EF BUSY_L 1 EF Clk_Seq ®Init� ? ? 16 bit Shift Reg 8 CS_DAC_64 R +5 V floating Q Dig delay BUF TTL_50 Watchdog R HCPL-2430 BUSY_DMUi 1. 56 MHz FF EF : 16 S L 2 FIFO «data» REN FIFO «code» L 2_Status_# ®Init� «Code» Dval_C Suspend ? ® 40_c� M=0 ®Init� ® 39_c� Mode Bit_24 3 => 8 Bit_24 Bit 25 Bit_26 FPDP_control Interface ®first� during M=3

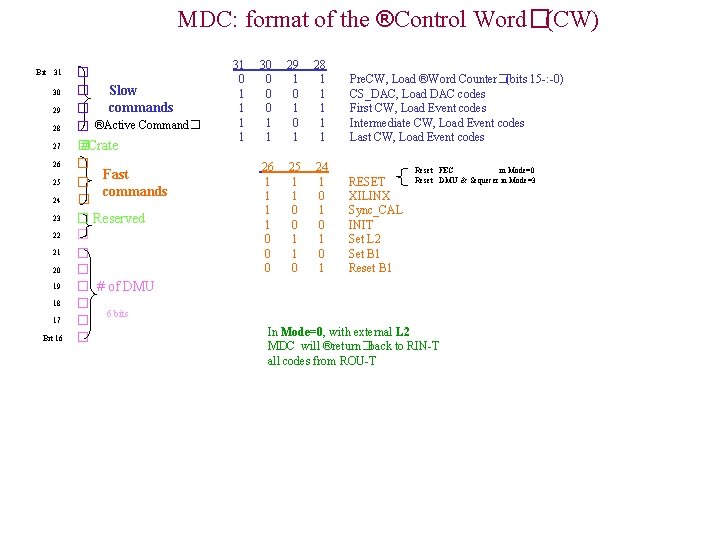

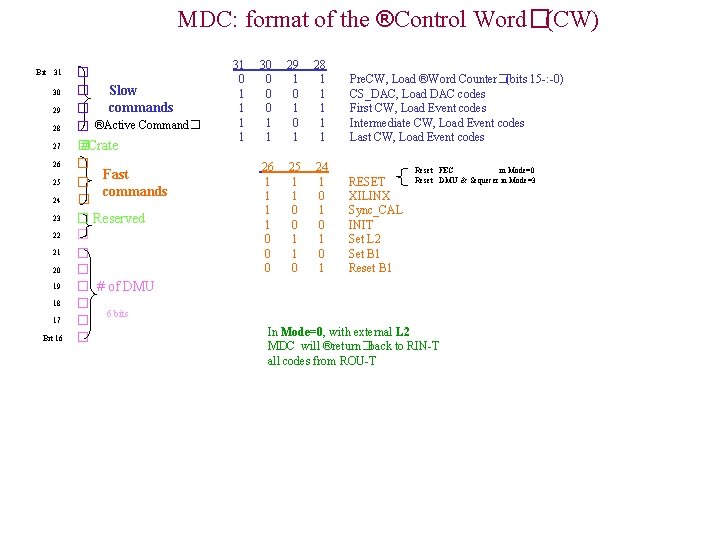

MDC: format of the ®Control Word�(CW) Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 Bit 16 � � Slow � commands � ®Active Command� � #Crate � Fast � commands � � Reserved � � # of DMU � 6 bits � � 31 0 1 1 30 0 1 1 29 1 0 1 28 1 1 1 Pre. CW, Load ®Word Counter�(bits 15 -: -0) CS_DAC, Load DAC codes First CW, Load Event codes Intermediate CW, Load Event codes Last CW, Load Event codes 26 1 1 0 0 0 25 1 1 0 0 1 1 0 24 1 0 1 0 1 RESET XILINX Sync_CAL INIT Set L 2 Set B 1 Reset FEC in Mode=0 Reset DMU & Sequecer in Mode=3 In Mode=0, with external L 2 MDC will ®return�back to RIN-T all codes from ROU-T

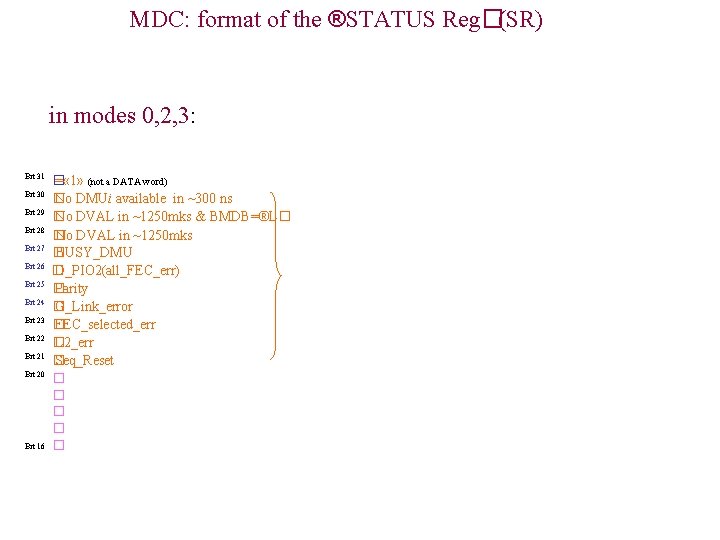

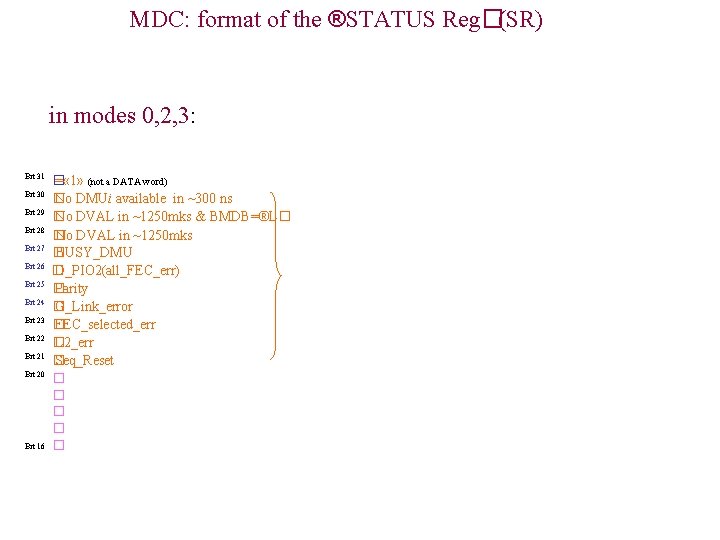

MDC: format of the ®STATUS Reg�(SR) in modes 0, 2, 3: Bit 31 Bit 30 Bit 29 Bit 28 Bit 27 Bit 26 Bit 25 Bit 24 Bit 23 Bit 22 Bit 21 Bit 20 Bit 16 � = « 1» (not a DATA word) � No DMUi available in ~300 ns � No DVAL in ~1250 mks & BMDB=®L� � No DVAL in ~1250 mks BUSY_DMU � � D_PIO 2(all_FEC_err) � Parity � G_Link_error � FEC_selected_err � L 2_err � Seq_Reset � � �

![Protocol for Mode0System to RACEway TIME from RACEway Ncodes 4NDACs Reset Xilinx 31 Protocol for ®Mode=0�(System) to RACEway TIME from RACEway N_codes= 4*N_DACs +[Reset_? +Xilinx_? ] 31](https://slidetodoc.com/presentation_image/829e20d6b1f57117fa67d2ad04f3c716/image-16.jpg)

Protocol for ®Mode=0�(System) to RACEway TIME from RACEway N_codes= 4*N_DACs +[Reset_? +Xilinx_? ] 31 8 Bytes Empty word if N_codes is ODD 16 Reset . �. . En_CS_DAC. . . � 0 15 . �. . DAC�. . . s code � NOT ®En_CS_DAC� ®Pre_CW� CW Adr Bit of ®Last Command Word� N_words expect # of Event 31 Each DAC_i requires 64_bit strings = 4 ®Command� 16 15 0

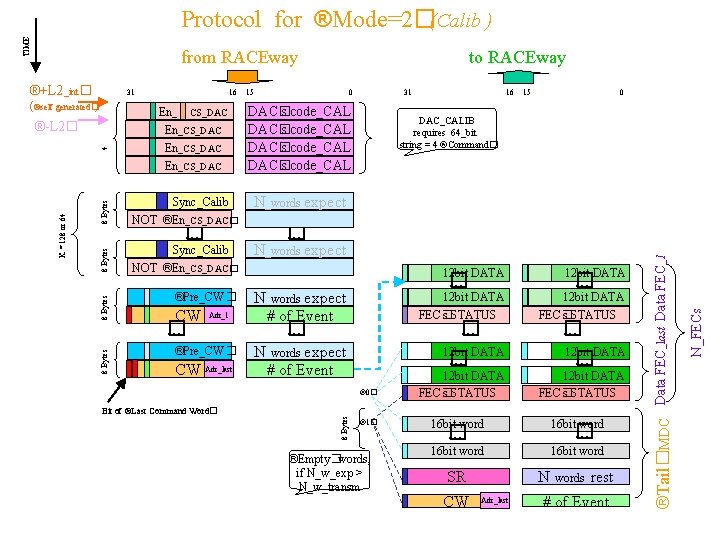

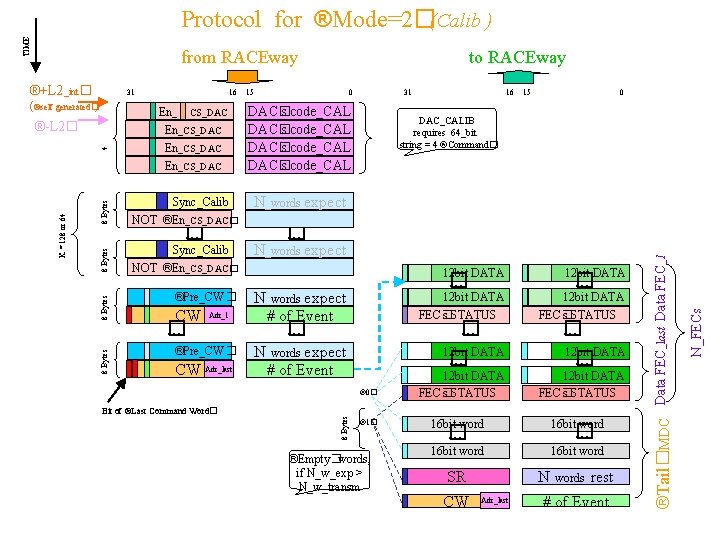

from RACEway (®self generated�) 8 Bytes En_ CS_DAC En_CS_DAC Sync_Calib NOT ®En_CS_DAC� . . . � Sync_Calib 0 15 31 DAC� s code_CAL CW . . . � Adr_1 ®Pre_CW� CW Adr_last . . . � N_words expect 12 bit DATA N_words expect # of Event 12 bit DATA FEC� s STATUS N_words expect # of Event 12 bit DATA FEC� s STATUS . . . � ® 0� Bit of ®Last Command Word� 0 15 DAC_CALIB requires 64_bit string = 4 ®Command� NOT ®En_CS_DAC� ®Pre_CW� 16 N_words expect 8 Bytes K * 128 or 64 4 ®-L 2� 16 ® 1� ®Empty�words, if N_w_exp > N_w_transm . . . � 16 bit word SR N_words_rest CW Adr_last . . . � # of Event N_FECs 31 Data FEC_last Data FEC_1 ®+L 2_int� to RACEway ®Tail�MDC TIME Protocol for ®Mode=2�(Calib )

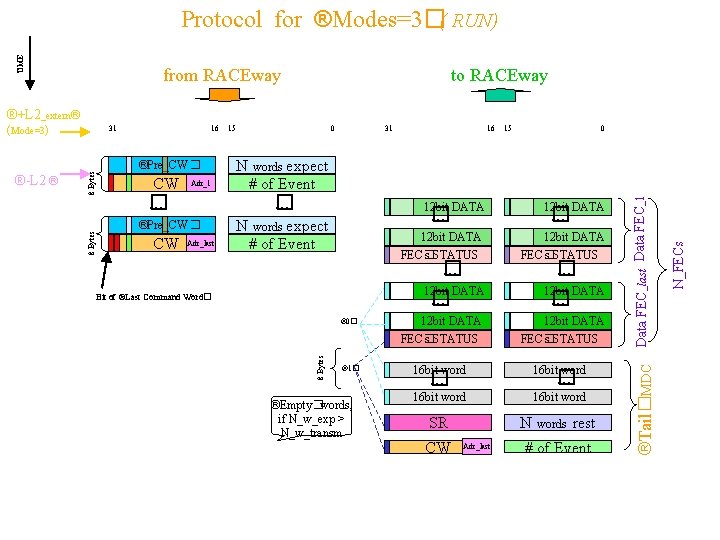

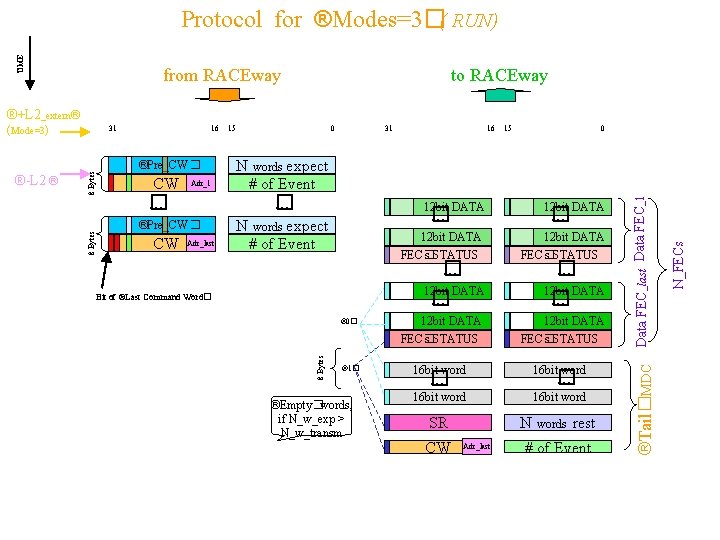

TIME Protocol for ®Modes=3�( RUN) from RACEway to RACEway ®+L 2_extern® ®Pre_CW� CW Adr_1 . . . � ®Pre_CW� CW Adr_last 0 15 31 16 0 15 N_words expect # of Event . . . � 12 bit DATA N_words expect # of Event 12 bit DATA . . . � FEC� s STATUS . . . � 12 bit DATA ® 0� 12 bit DATA FEC� s STATUS ® 1� 16 bit word . . . � 16 bit word SR N_words_rest . . . � Bit of ®Last Command Word� 8 Bytes . . . � ®Empty�words, if N_w_exp > N_w_transm CW Adr_last . . . � # of Event N_FECs 16 Data FEC_last Data FEC_1 8 Bytes ®-L 2 ® 31 ®Tail�MDC (Mode=3)