Silicon Tungsten Calorimeters The WIZARD experiments PART II

- Slides: 20

Silicon Tungsten Calorimeters The WIZARD experiments – PART II – G. Zampa, M. Boezio, V. Bonvicini, E. Mocchiutti, A. Vacchi, N. Zampa (INFN-Sezione di Trieste, Italy) OUTLINE • The PAMELA Si-W calorimeter electronics • Developments for future space calorimeters • FE electronics for the NCC: considerations Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

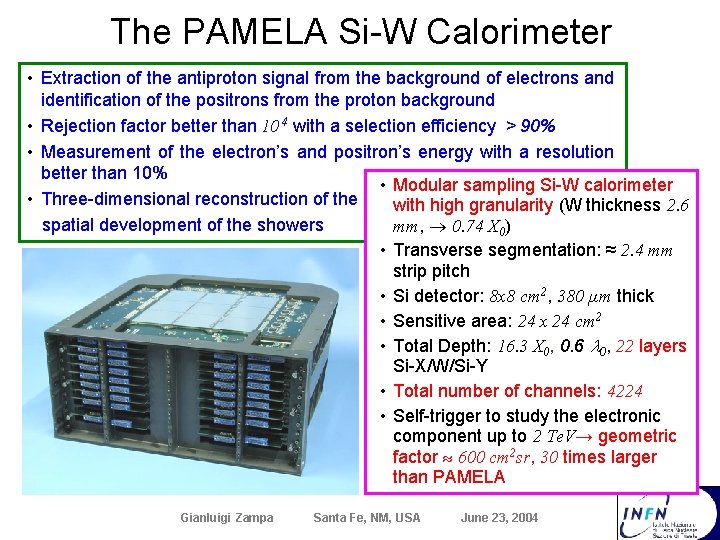

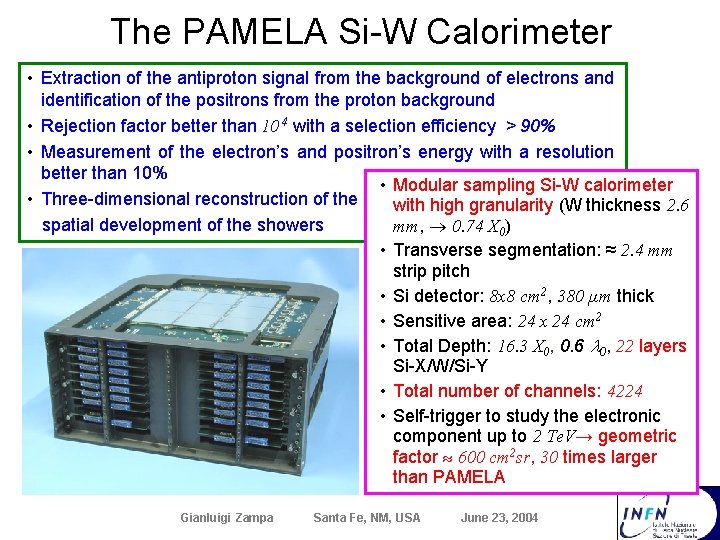

The PAMELA Si-W Calorimeter • Extraction of the antiproton signal from the background of electrons and identification of the positrons from the proton background • Rejection factor better than 10 4 with a selection efficiency > 90% • Measurement of the electron’s and positron’s energy with a resolution better than 10% • Modular sampling Si-W calorimeter • Three-dimensional reconstruction of the with high granularity (W thickness 2. 6 spatial development of the showers mm, ® 0. 74 X 0) • Transverse segmentation: ≈ 2. 4 mm strip pitch • Si detector: 8 x 8 cm 2, 380 µm thick • Sensitive area: 24 x 24 cm 2 • Total Depth: 16. 3 X 0, 0. 6 l 0, 22 layers Si-X/W/Si-Y • Total number of channels: 4224 • Self-trigger to study the electronic component up to 2 Te. V→ geometric factor » 600 cm 2 sr, 30 times larger than PAMELA Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

Calorimeter electronics: requirements The calorimeter will operate in orbit ® radiation environment: – Total Ionizing Dose: 3 krad inside the PAMELA container – Possible Single Event Effects: LATCH-UP and UPSET (digital logic) Therefore: ® commercial electronic devices tested up to 30 krad ® fault tolerant design and use of redundancy Data storage allocated for PAMELA: 10 G byte per day – expected average trigger rate of 12 Hz – more than 40000 read-out channels > 80 G byte every day Digital processing to: – Compress the event data – Reduce the trigger rate discarding non interesting events Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

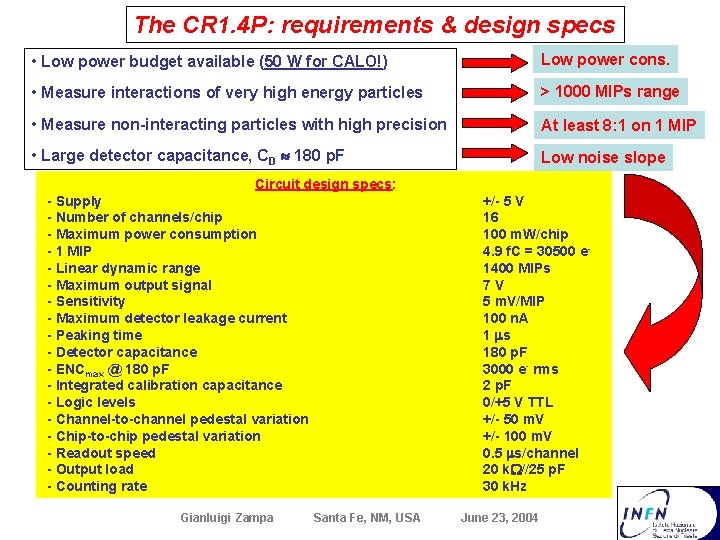

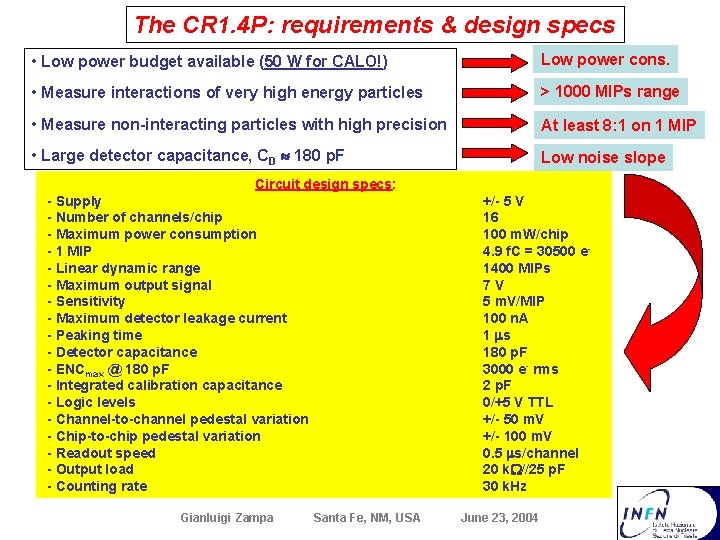

The CR 1. 4 P: requirements & design specs • Low power budget available (50 W for CALO!) Low power cons. • Measure interactions of very high energy particles > 1000 MIPs range • Measure non-interacting particles with high precision At least 8: 1 on 1 MIP • Large detector capacitance, CD 180 p. F Low noise slope Circuit design specs: - Supply - Number of channels/chip - Maximum power consumption - 1 MIP - Linear dynamic range - Maximum output signal - Sensitivity - Maximum detector leakage current - Peaking time - Detector capacitance - ENCmax @ 180 p. F - Integrated calibration capacitance - Logic levels - Channel-to-channel pedestal variation - Chip-to-chip pedestal variation - Readout speed - Output load - Counting rate Gianluigi Zampa +/- 5 V 16 100 m. W/chip 4. 9 f. C = 30500 e 1400 MIPs 7 V 5 m. V/MIP 100 n. A 1 ms 180 p. F 3000 e- rms 2 p. F 0/+5 V TTL +/- 50 m. V +/- 100 m. V 0. 5 ms/channel 20 k. W//25 p. F 30 k. Hz Santa Fe, NM, USA June 23, 2004

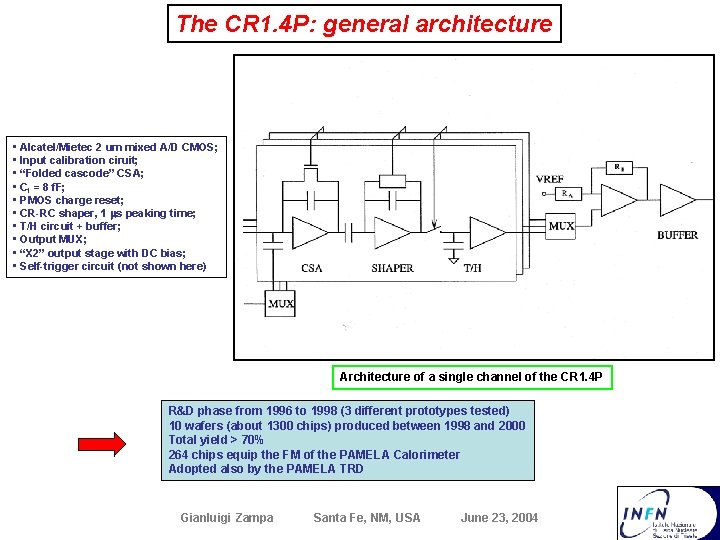

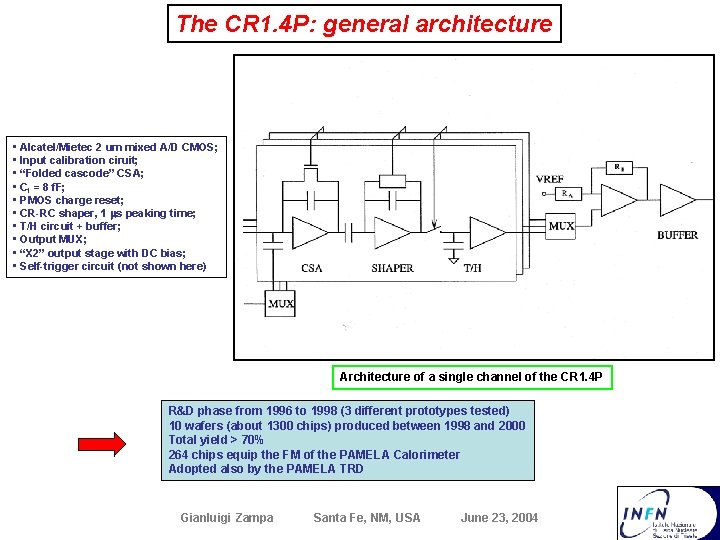

The CR 1. 4 P: general architecture • Alcatel/Mietec 2 um mixed A/D CMOS; • Input calibration ciruit; • “Folded cascode” CSA; • Cf = 8 f. F; • PMOS charge reset; • CR-RC shaper, 1 ms peaking time; • T/H circuit + buffer; • Output MUX; • “X 2” output stage with DC bias; • Self-trigger circuit (not shown here) Architecture of a single channel of the CR 1. 4 P R&D phase from 1996 to 1998 (3 different prototypes tested) 10 wafers (about 1300 chips) produced between 1998 and 2000 Total yield > 70% 264 chips equip the FM of the PAMELA Calorimeter Adopted also by the PAMELA TRD Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

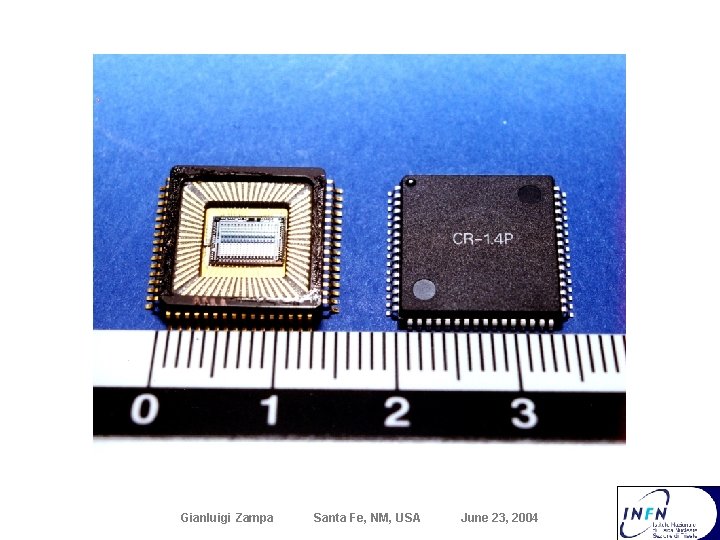

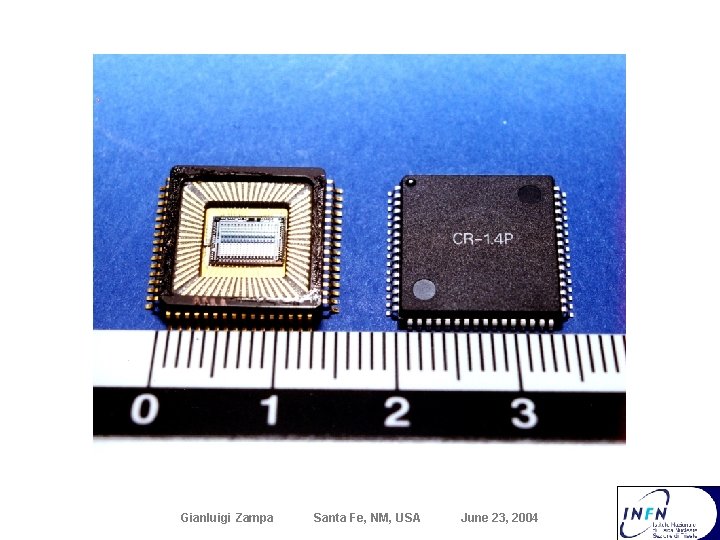

Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

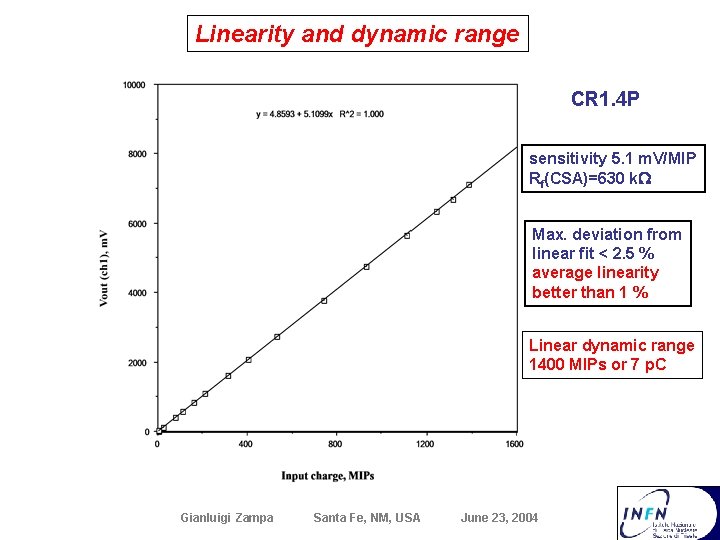

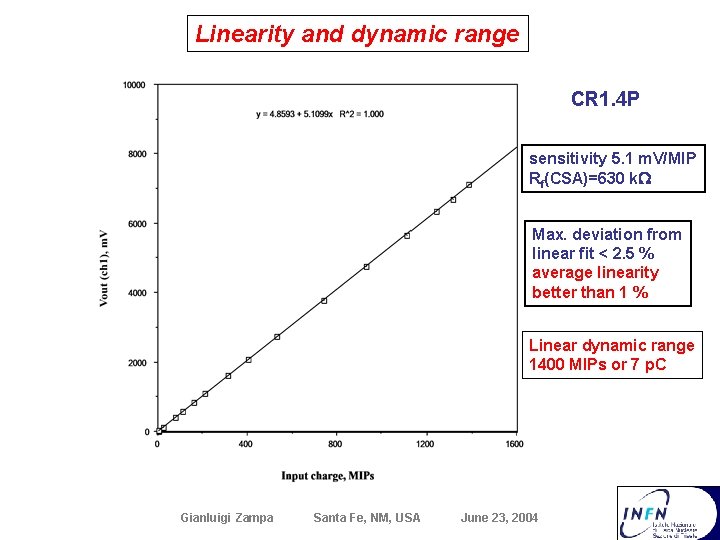

Linearity and dynamic range CR 1. 4 P sensitivity 5. 1 m. V/MIP Rf(CSA)=630 k. W Max. deviation from linear fit < 2. 5 % average linearity better than 1 % Linear dynamic range 1400 MIPs or 7 p. C Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

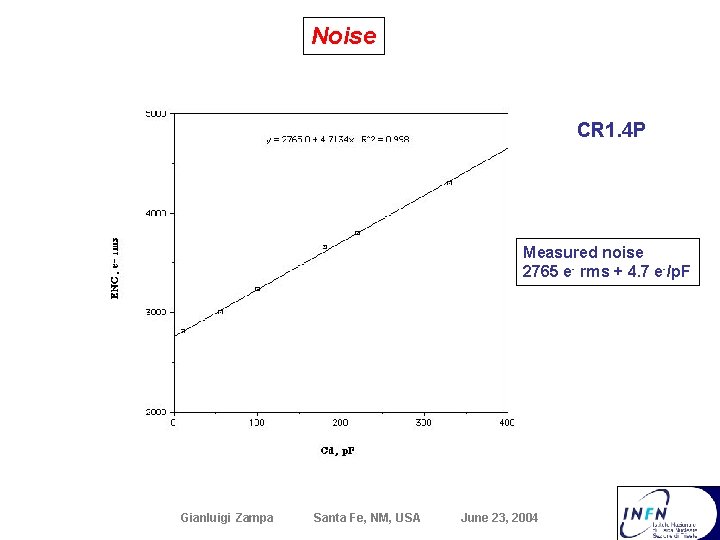

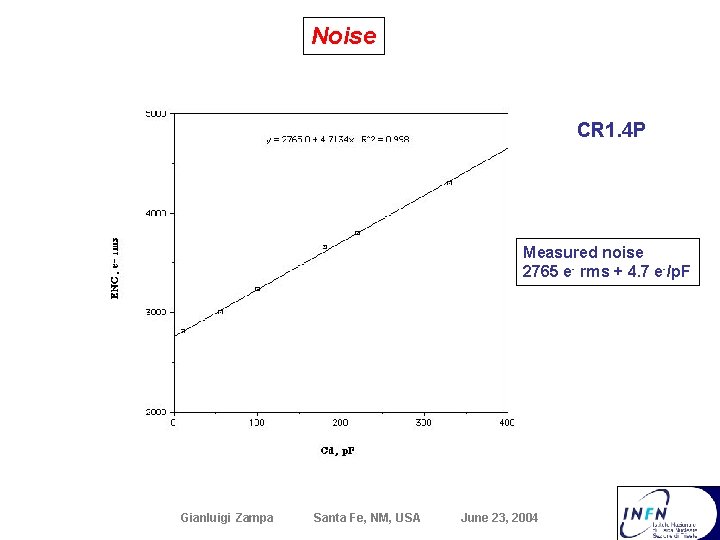

Noise CR 1. 4 P Measured noise 2765 e- rms + 4. 7 e-/p. F Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

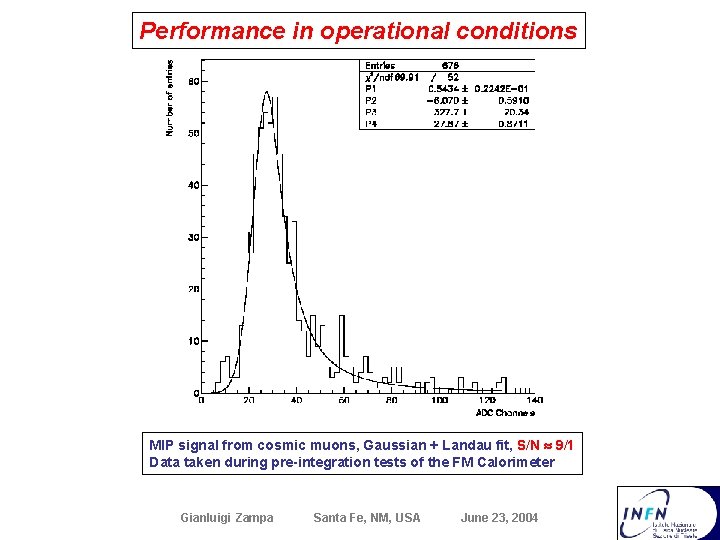

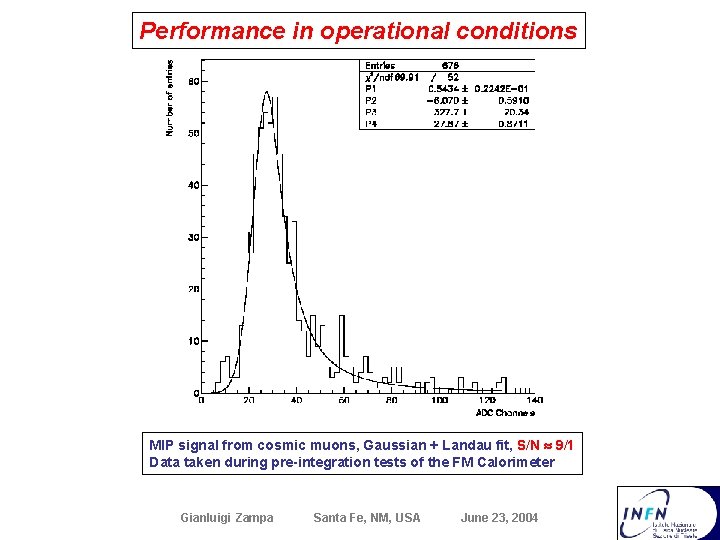

Performance in operational conditions MIP signal from cosmic muons, Gaussian + Landau fit, S/N 9/1 Data taken during pre-integration tests of the FM Calorimeter Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

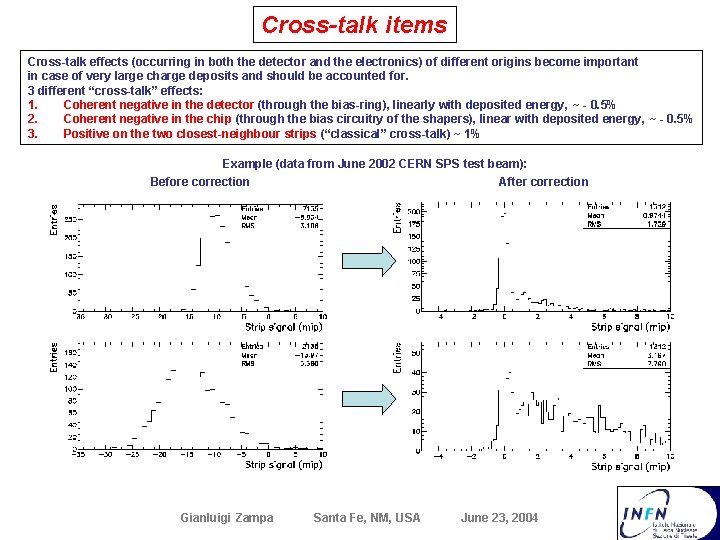

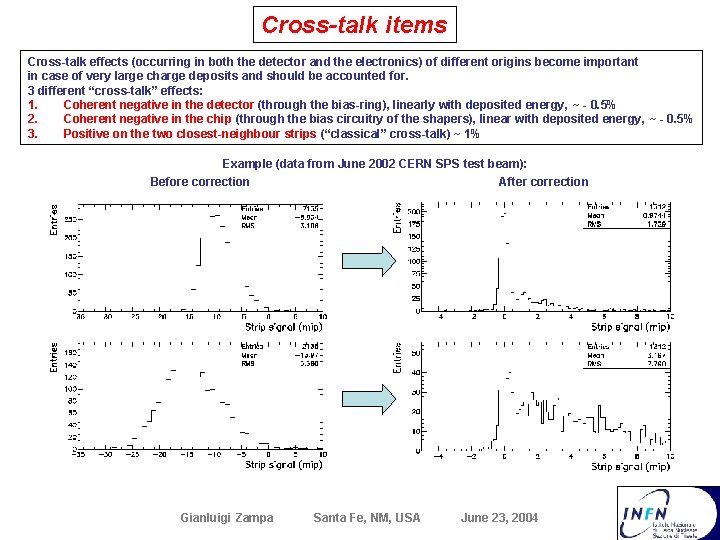

Cross-talk items Cross-talk effects (occurring in both the detector and the electronics) of different origins become important in case of very large charge deposits and should be accounted for. 3 different “cross-talk” effects: 1. Coherent negative in the detector (through the bias-ring), linearly with deposited energy, ~ - 0. 5% 2. Coherent negative in the chip (through the bias circuitry of the shapers), linear with deposited energy, ~ - 0. 5% 3. Positive on the two closest-neighbour strips (“classical” cross-talk) ~ 1% Example (data from June 2002 CERN SPS test beam): Before correction After correction Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

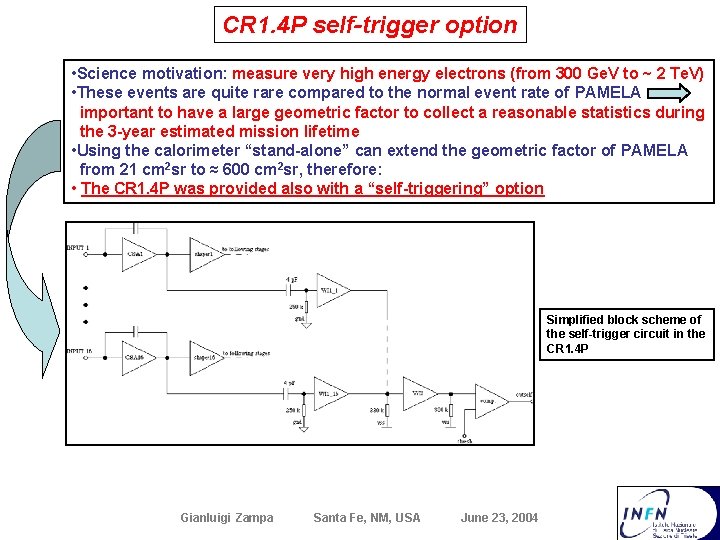

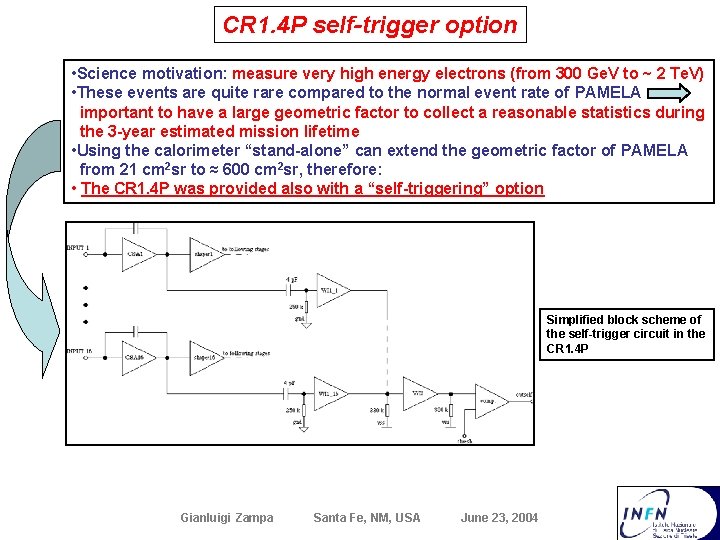

CR 1. 4 P self-trigger option • Science motivation: measure very high energy electrons (from 300 Ge. V to ~ 2 Te. V) • These events are quite rare compared to the normal event rate of PAMELA important to have a large geometric factor to collect a reasonable statistics during the 3 -year estimated mission lifetime • Using the calorimeter “stand-alone” can extend the geometric factor of PAMELA from 21 cm 2 sr to ≈ 600 cm 2 sr, therefore: • The CR 1. 4 P was provided also with a “self-triggering” option Simplified block scheme of the self-trigger circuit in the CR 1. 4 P Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

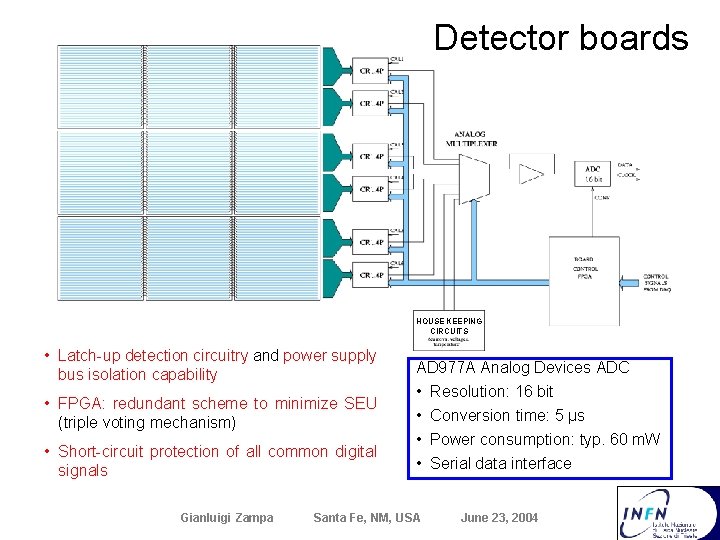

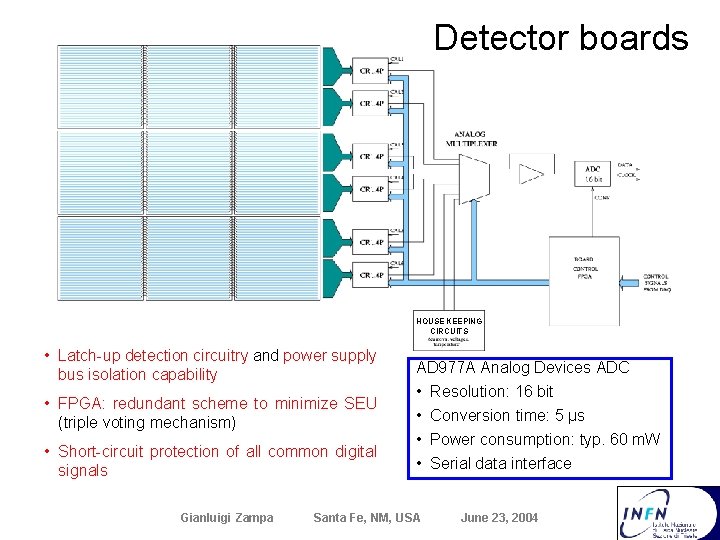

Detector boards HOUSE KEEPING CIRCUITS • Latch-up detection circuitry and power supply bus isolation capability • FPGA: redundant scheme to minimize SEU (triple voting mechanism) • Short-circuit protection of all common digital signals Gianluigi Zampa AD 977 A Analog Devices ADC • • Santa Fe, NM, USA Resolution: 16 bit Conversion time: 5 μs Power consumption: typ. 60 m. W Serial data interface June 23, 2004

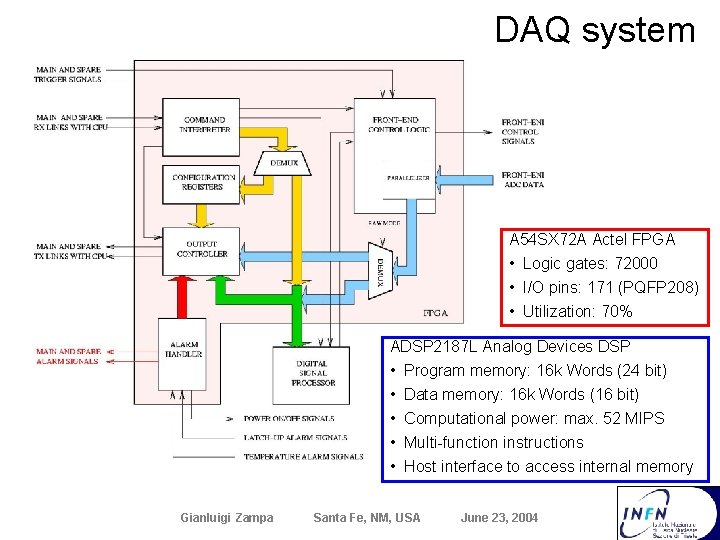

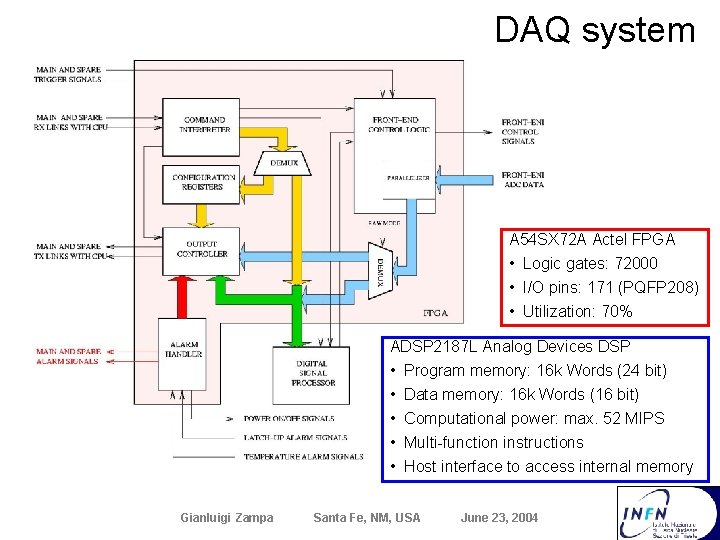

DAQ system A 54 SX 72 A Actel FPGA • Logic gates: 72000 • I/O pins: 171 (PQFP 208) • Utilization: 70% ADSP 2187 L Analog Devices DSP • • • Gianluigi Zampa Program memory: 16 k Words (24 bit) Data memory: 16 k Words (16 bit) Computational power: max. 52 MIPS Multi-function instructions Host interface to access internal memory Santa Fe, NM, USA June 23, 2004

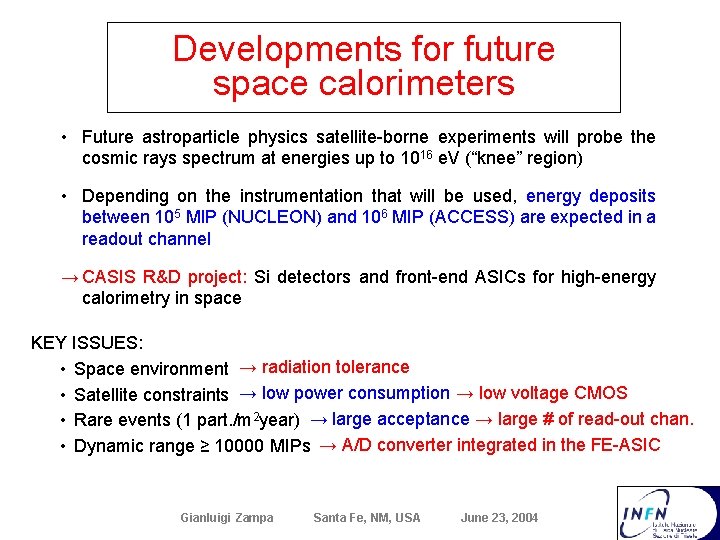

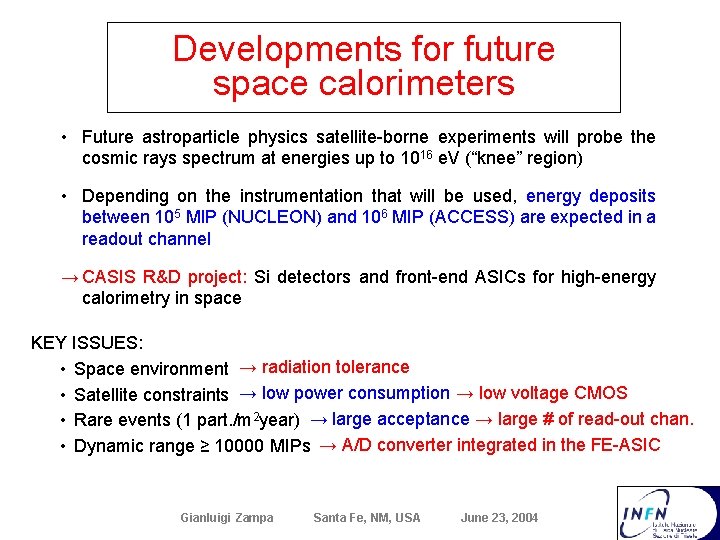

Developments for future space calorimeters • Future astroparticle physics satellite-borne experiments will probe the cosmic rays spectrum at energies up to 1016 e. V (“knee” region) • Depending on the instrumentation that will be used, energy deposits between 105 MIP (NUCLEON) and 106 MIP (ACCESS) are expected in a readout channel → CASIS R&D project: Si detectors and front-end ASICs for high-energy calorimetry in space KEY ISSUES: • Space environment → radiation tolerance • Satellite constraints → low power consumption → low voltage CMOS • Rare events (1 part. /m 2 year) → large acceptance → large # of read-out chan. • Dynamic range ≥ 10000 MIPs → A/D converter integrated in the FE-ASIC Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

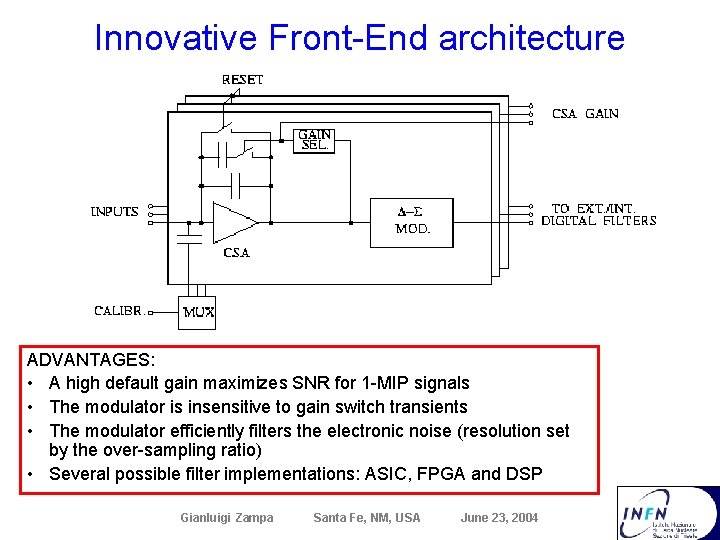

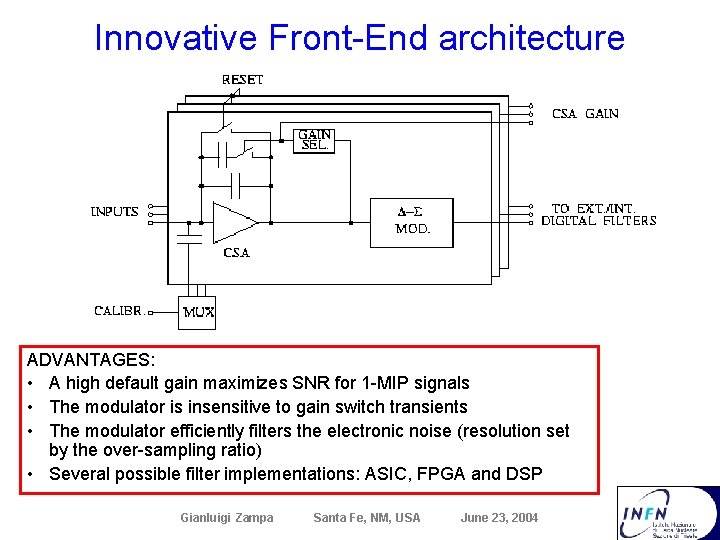

Innovative Front-End architecture ADVANTAGES: • A high default gain maximizes SNR for 1 -MIP signals • The modulator is insensitive to gain switch transients • The modulator efficiently filters the electronic noise (resolution set by the over-sampling ratio) • Several possible filter implementations: ASIC, FPGA and DSP Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

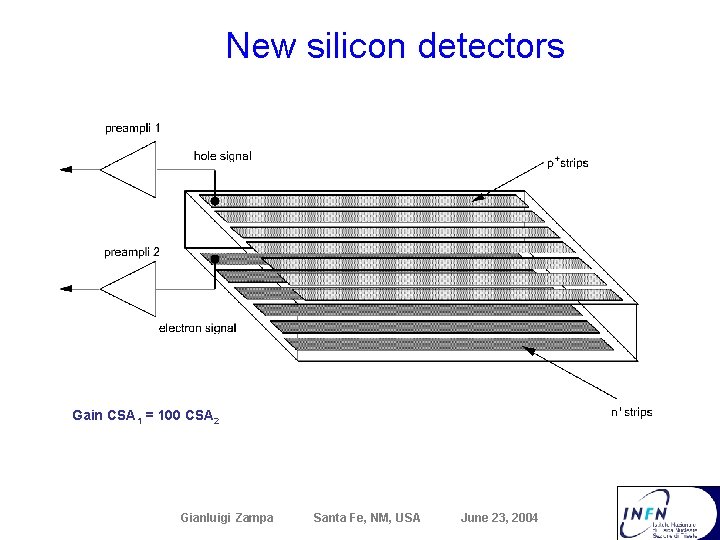

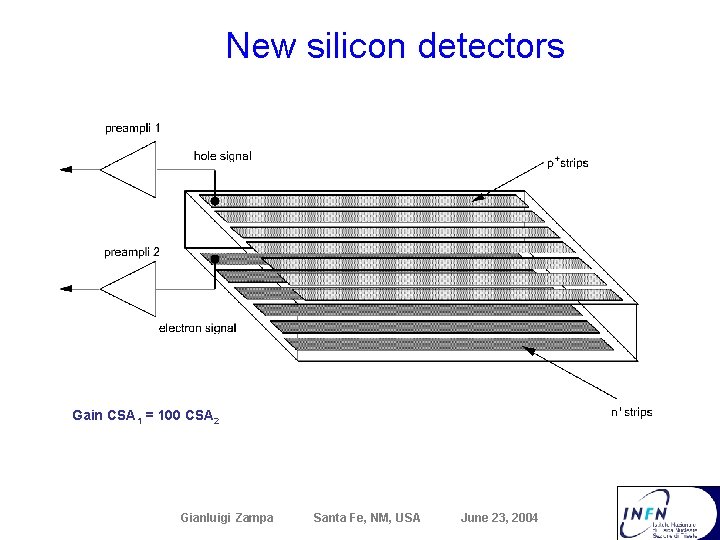

New silicon detectors Gain CSA 1 = 100 CSA 2 Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

FE electronics for the NCC: considerations FE electronics requirements Is CR 1. 4 P suitable? Possible alternative solution Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

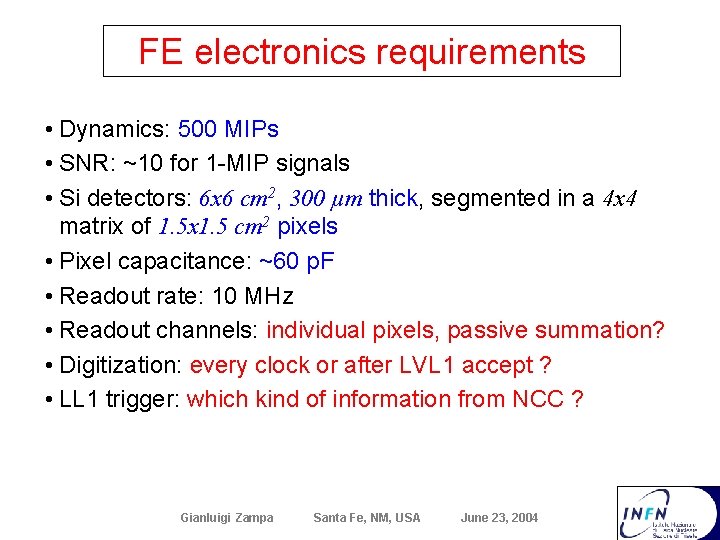

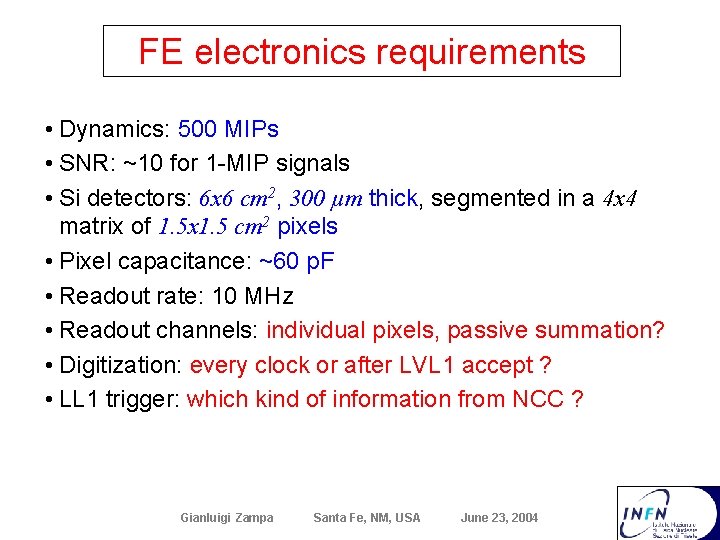

FE electronics requirements • Dynamics: 500 MIPs • SNR: ~10 for 1 -MIP signals • Si detectors: 6 x 6 cm 2, 300 µm thick, segmented in a 4 x 4 matrix of 1. 5 x 1. 5 cm 2 pixels • Pixel capacitance: ~60 p. F • Readout rate: 10 MHz • Readout channels: individual pixels, passive summation? • Digitization: every clock or after LVL 1 accept ? • LL 1 trigger: which kind of information from NCC ? Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

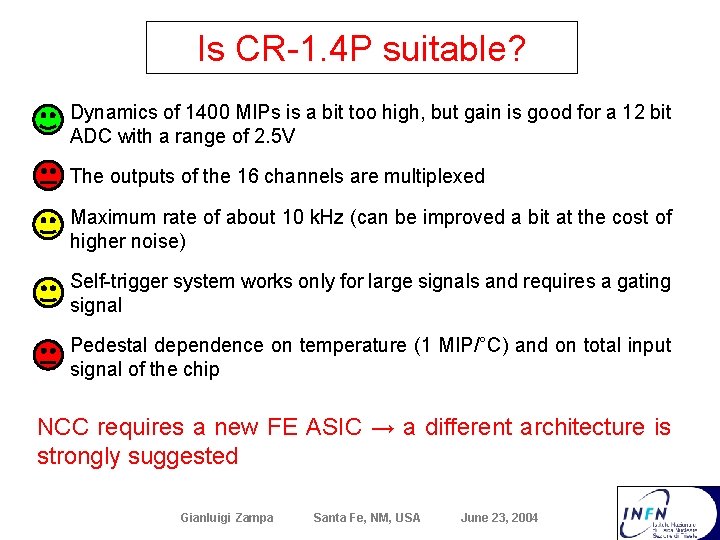

Is CR-1. 4 P suitable? • Dynamics of 1400 MIPs is a bit too high, but gain is good for a 12 bit ADC with a range of 2. 5 V • The outputs of the 16 channels are multiplexed • Maximum rate of about 10 k. Hz (can be improved a bit at the cost of higher noise) • Self-trigger system works only for large signals and requires a gating signal • Pedestal dependence on temperature (1 MIP/°C) and on total input signal of the chip NCC requires a new FE ASIC → a different architecture is strongly suggested Gianluigi Zampa Santa Fe, NM, USA June 23, 2004

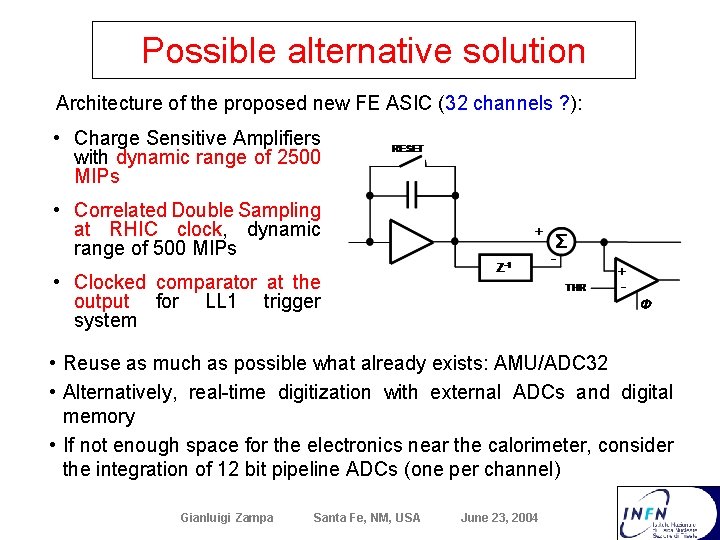

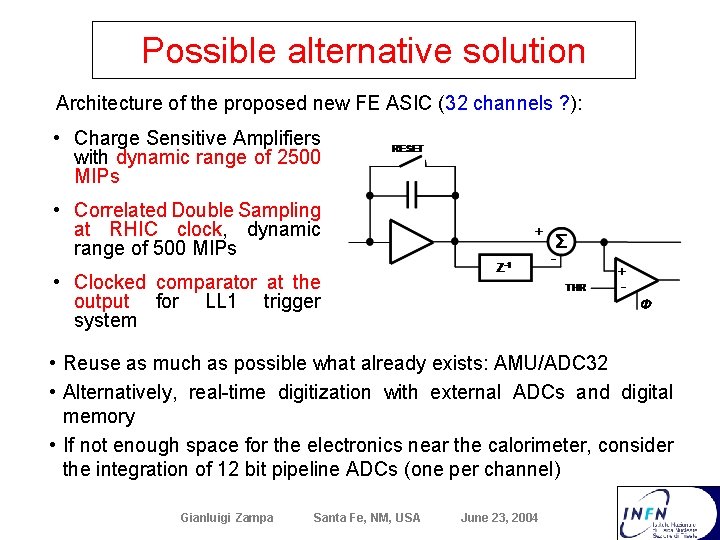

Possible alternative solution Architecture of the proposed new FE ASIC (32 channels ? ): • Charge Sensitive Amplifiers with dynamic range of 2500 MIPs • Correlated Double Sampling at RHIC clock, dynamic range of 500 MIPs • Clocked comparator at the output for LL 1 trigger system • Reuse as much as possible what already exists: AMU/ADC 32 • Alternatively, real-time digitization with external ADCs and digital memory • If not enough space for the electronics near the calorimeter, consider the integration of 12 bit pipeline ADCs (one per channel) Gianluigi Zampa Santa Fe, NM, USA June 23, 2004