Silicon TD 5102 MIPS Instruction Set Architecture Henk

![Instructions n n Load and store instructions Example: C code: A[8] = h + Instructions n n Load and store instructions Example: C code: A[8] = h +](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-11.jpg)

![Our First C Example n Can we figure out the code? swap(int v[], int Our First C Example n Can we figure out the code? swap(int v[], int](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-12.jpg)

![While statement while (save[i] == k) i=i+j; Loop: muli add lw bne add j While statement while (save[i] == k) i=i+j; Loop: muli add lw bne add j](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-35.jpg)

![Arrays versus pointers Array version: clear 1 (int array[], int size) { int i; Arrays versus pointers Array version: clear 1 (int array[], int size) { int i;](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-46.jpg)

- Slides: 49

Silicon TD 5102 MIPS Instruction Set Architecture Henk Corporaal http: //www. ics. ele. tue. nl/~heco/courses/Emb. Systems Technical University Eindhoven DTI / NUS Singapore 2005/2006 H. C. TD 5102

Topics n n n Instructions & MIPS instruction set Where are the operands ? Machine language Assembler Translating C statements into Assembler More complex stuff, like: u u u H. C. TD 5102 while statement switch statement procedure / function (leaf and nested) stack linking object files 2

Main Types of Instructions n Arithmetic u u n Memory access instructions u n Load & Store Control flow u u u H. C. TD 5102 Integer Floating Point Jump Conditional Branch Call & Return 3

MIPS arithmetic n n Most instructions have 3 operands Operand order is fixed (destination first) Example: C code: A = B + C MIPS code: add $s 0, $s 1, $s 2 ($s 0, $s 1 and $s 2 are associated with variables by compiler) H. C. TD 5102 4

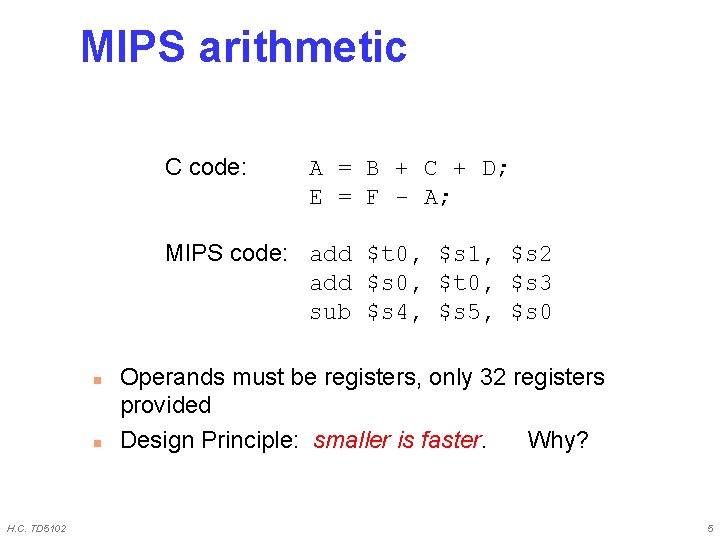

MIPS arithmetic C code: A = B + C + D; E = F - A; MIPS code: add $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3 sub $s 4, $s 5, $s 0 n n H. C. TD 5102 Operands must be registers, only 32 registers provided Design Principle: smaller is faster. Why? 5

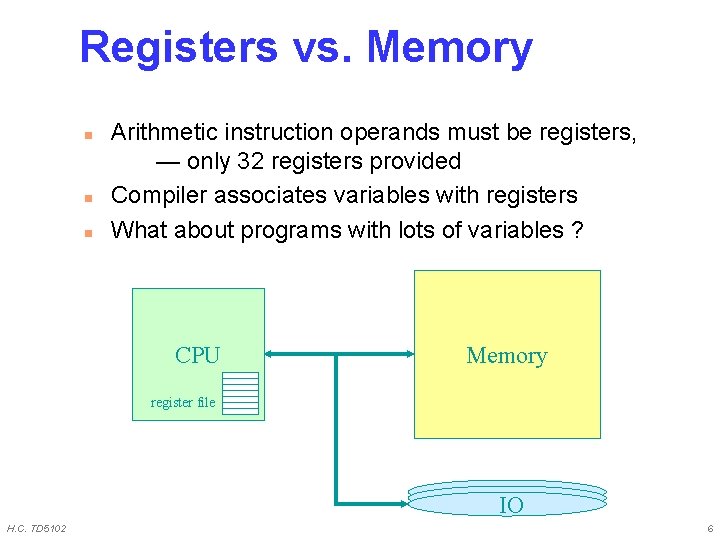

Registers vs. Memory n n n Arithmetic instruction operands must be registers, — only 32 registers provided Compiler associates variables with registers What about programs with lots of variables ? CPU Memory register file IO H. C. TD 5102 6

Register allocation n n Compiler tries to keep as many variables in registers as possible Some variables can not be allocated u u u n H. C. TD 5102 large arrays (too few registers) aliased variables (variables accessible through pointers in C) dynamic allocated variables F heap F stack Compiler may run out of registers => spilling 7

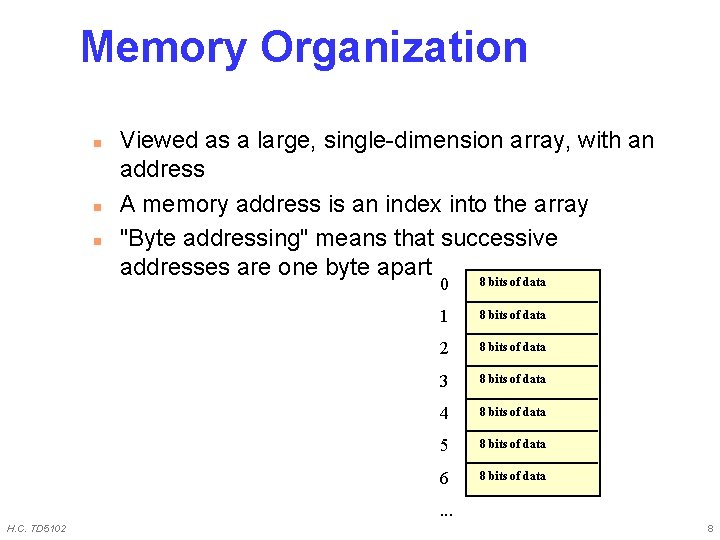

Memory Organization n Viewed as a large, single-dimension array, with an address A memory address is an index into the array "Byte addressing" means that successive addresses are one byte apart 8 bits of data 0 1 8 bits of data 2 8 bits of data 3 8 bits of data 4 8 bits of data 5 8 bits of data 6 8 bits of data . . . H. C. TD 5102 8

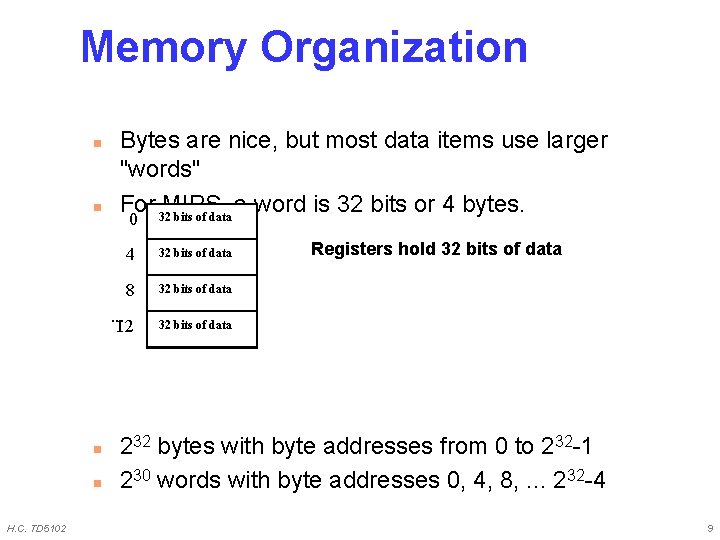

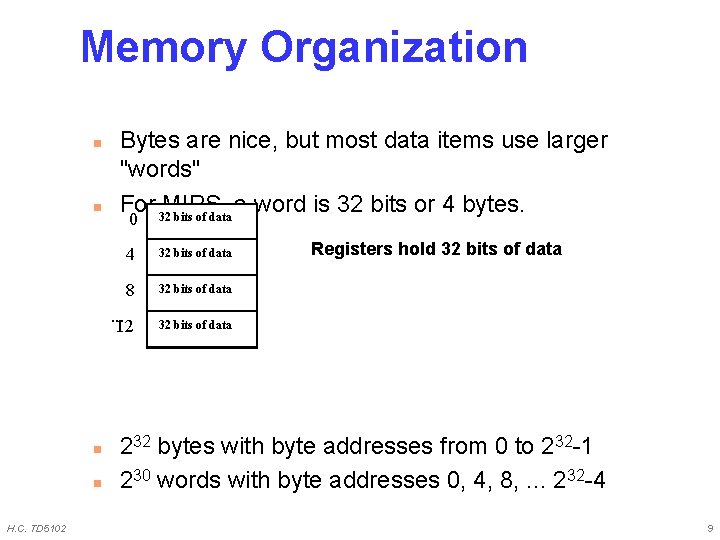

Memory Organization n n H. C. TD 5102 Bytes are nice, but most data items use larger "words" For 32 MIPS, a word is 32 bits or 4 bytes. bits of data 0 4 32 bits of data 8 32 bits of data . . . 12 32 bits of data Registers hold 32 bits of data 232 bytes with byte addresses from 0 to 232 -1 230 words with byte addresses 0, 4, 8, . . . 232 -4 9

Memory layout: Alignment address 0 31 23 15 7 0 this word is aligned; the others are not! 4 8 12 16 20 24 Words are aligned n What are the least 2 significant bits of a word address? H. C. TD 5102 10

![Instructions n n Load and store instructions Example C code A8 h Instructions n n Load and store instructions Example: C code: A[8] = h +](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-11.jpg)

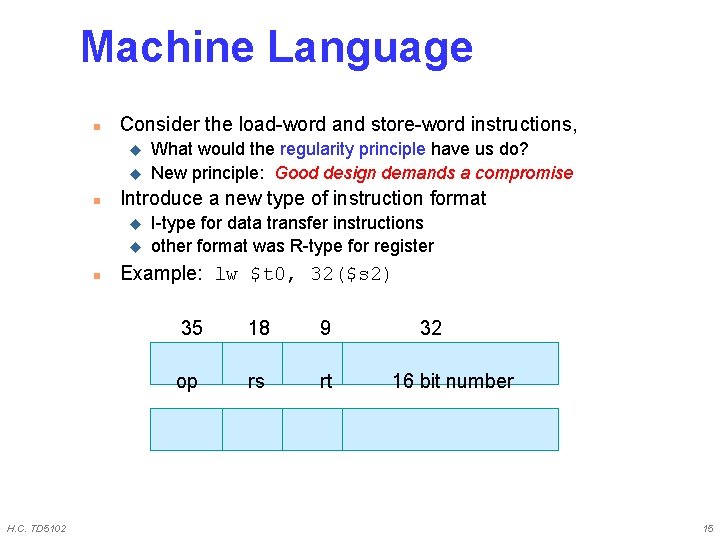

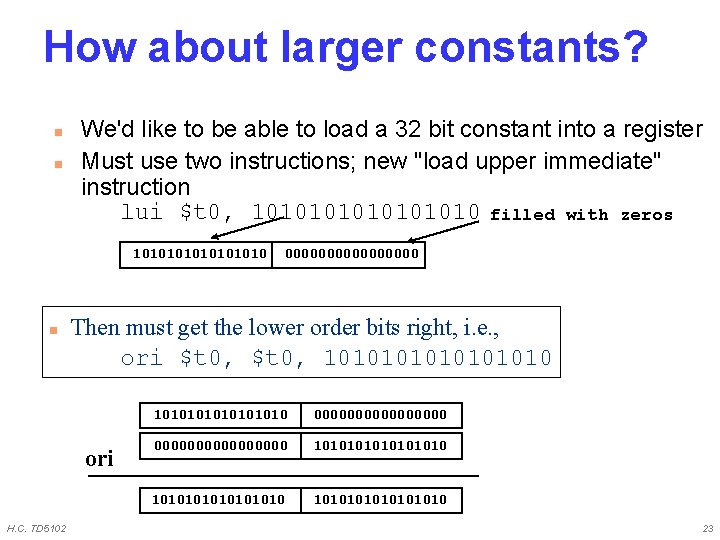

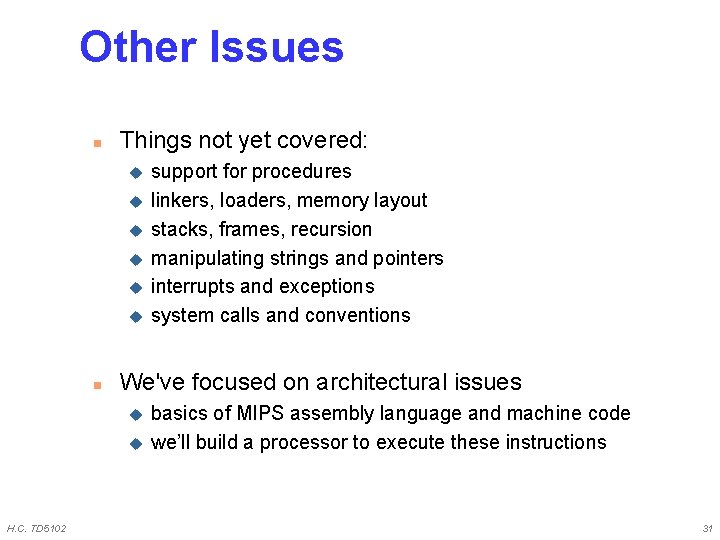

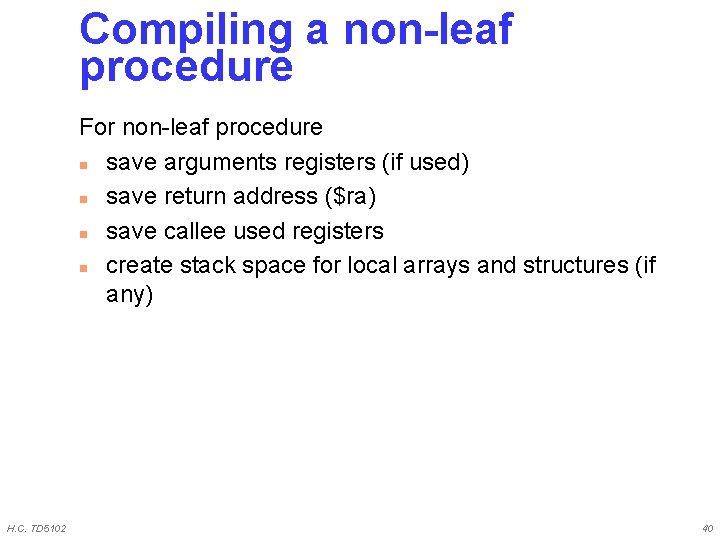

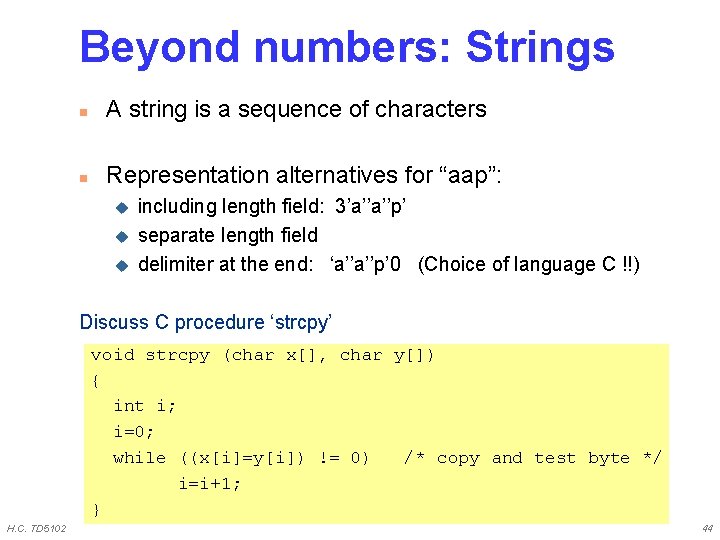

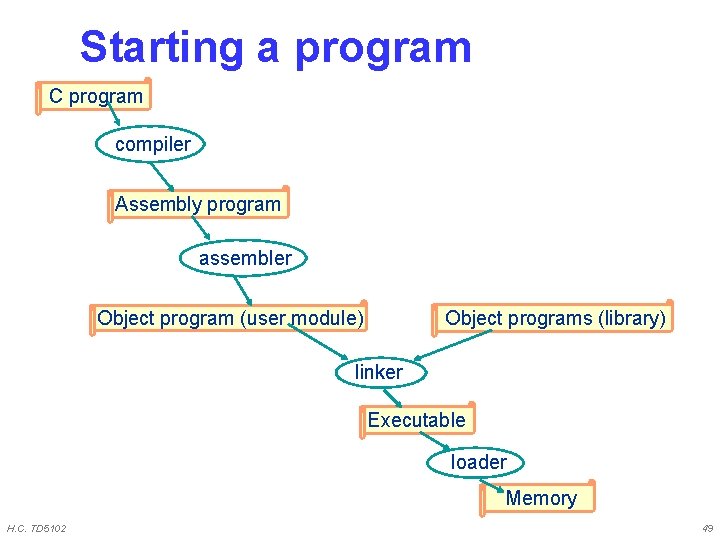

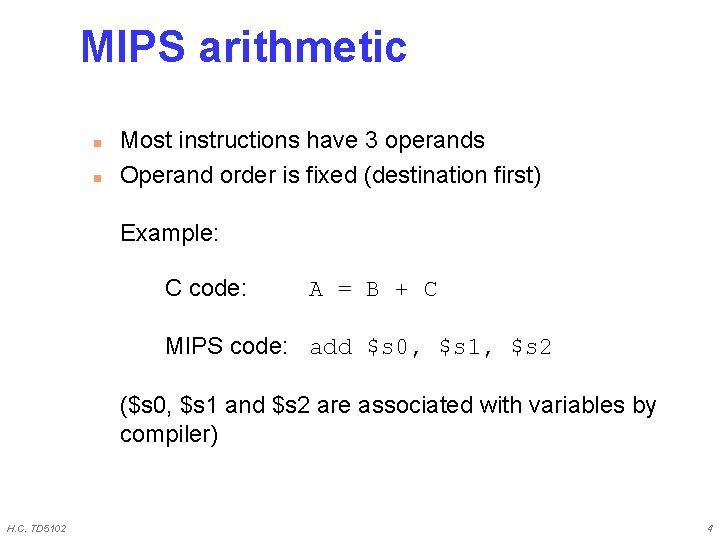

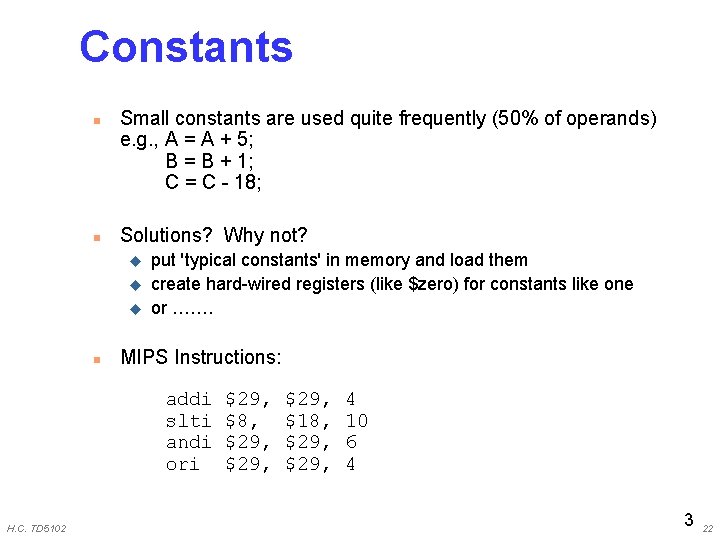

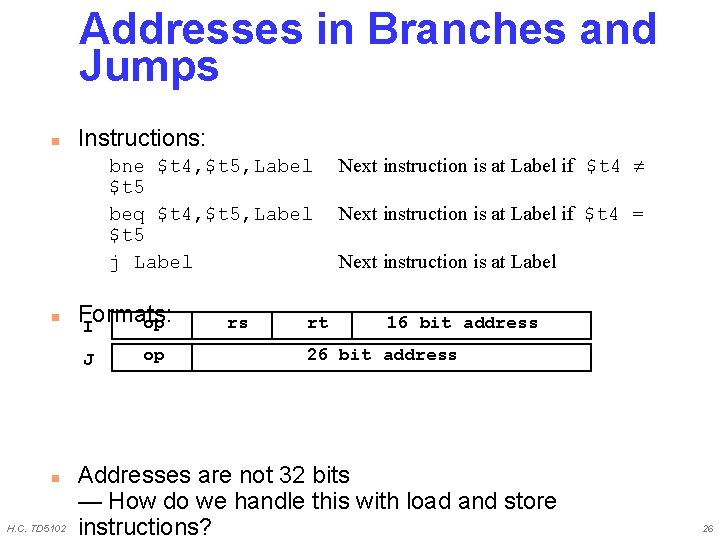

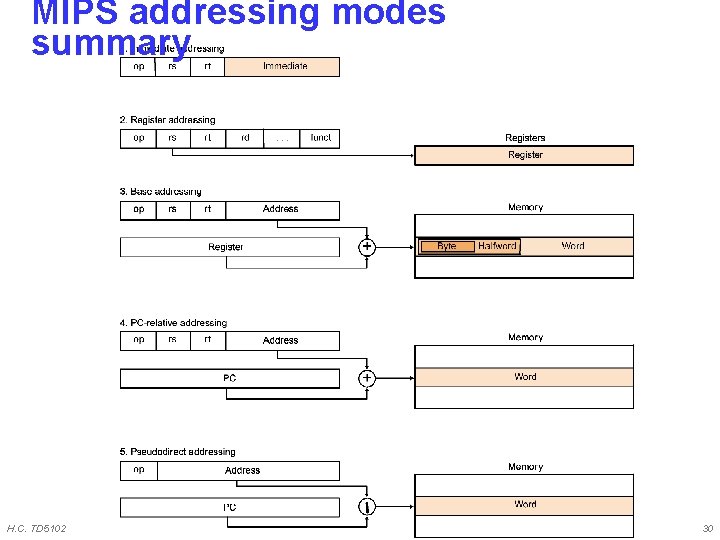

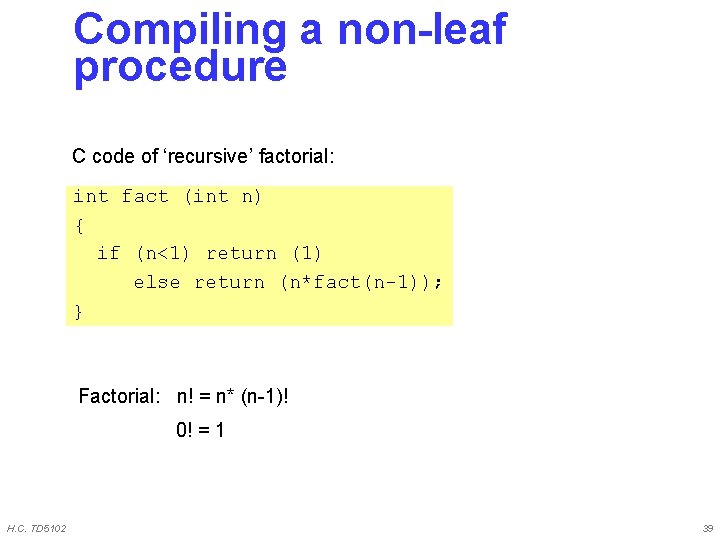

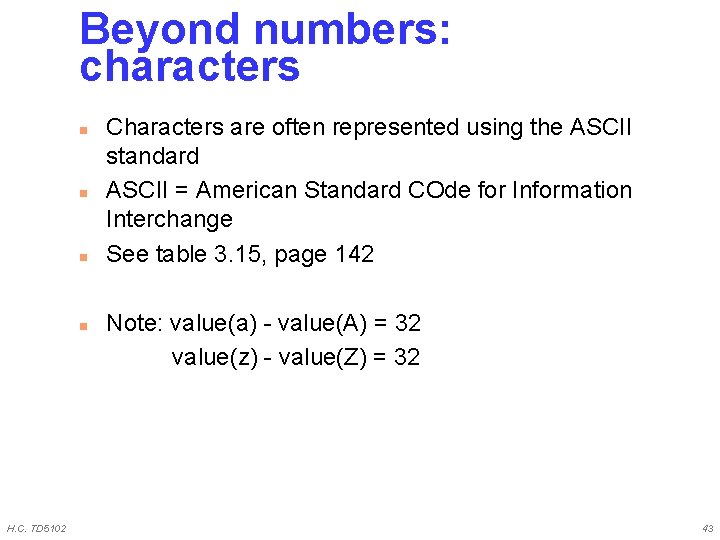

Instructions n n Load and store instructions Example: C code: A[8] = h + A[8]; MIPS code: lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 32($s 3) n n H. C. TD 5102 Store word operation has no destination (reg) operand Remember arithmetic operands are registers, not memory! 11

![Our First C Example n Can we figure out the code swapint v int Our First C Example n Can we figure out the code? swap(int v[], int](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-12.jpg)

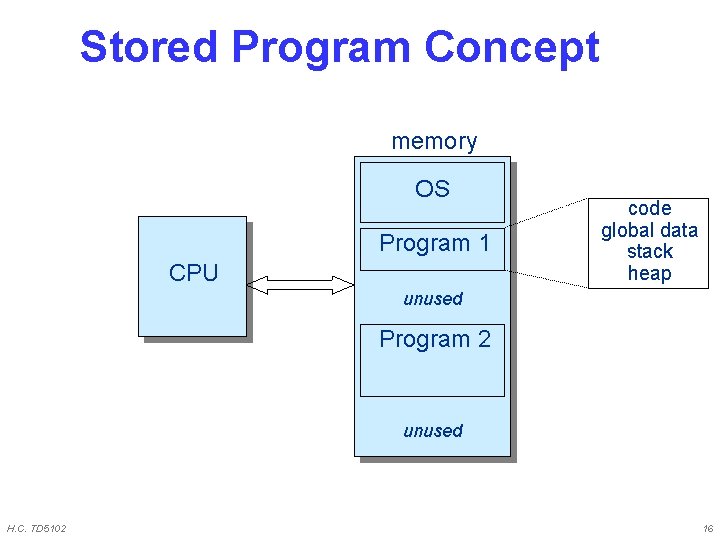

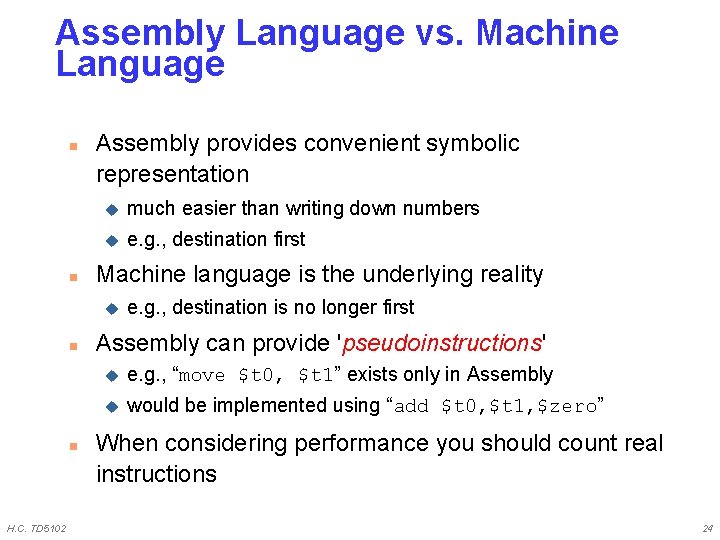

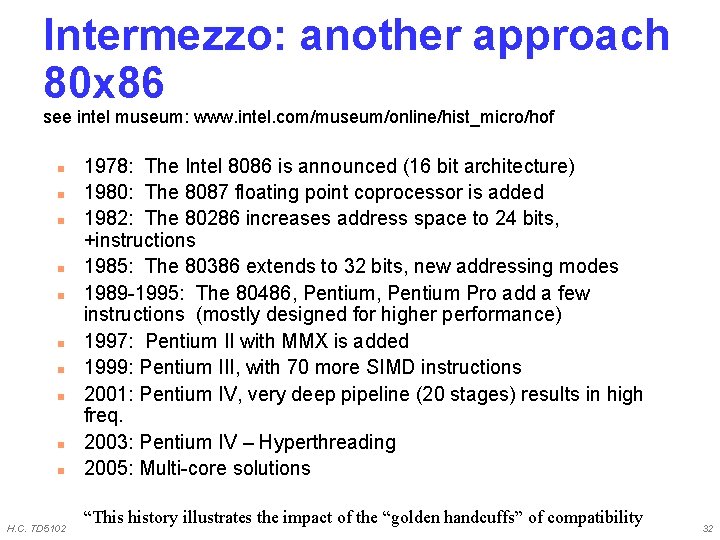

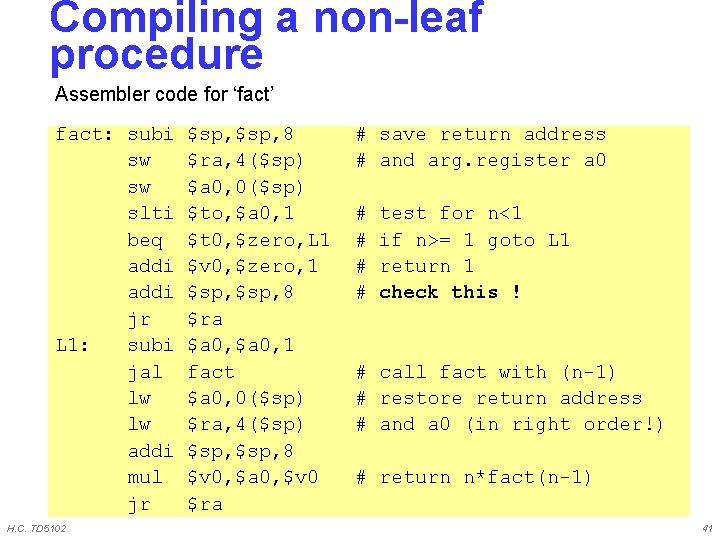

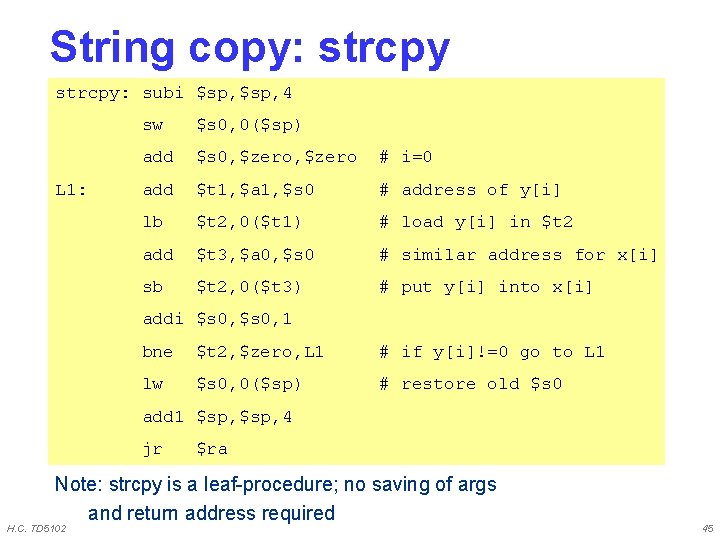

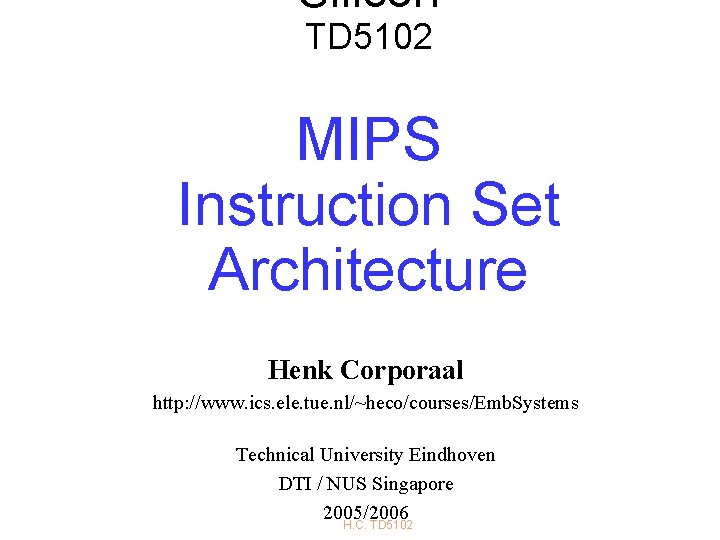

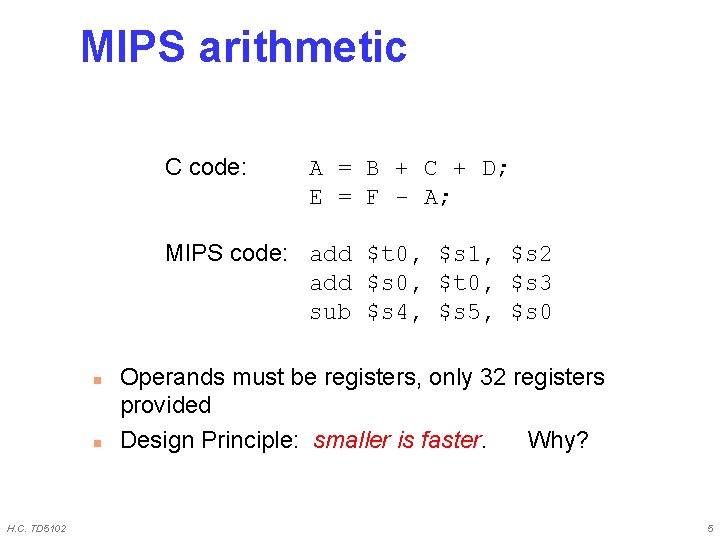

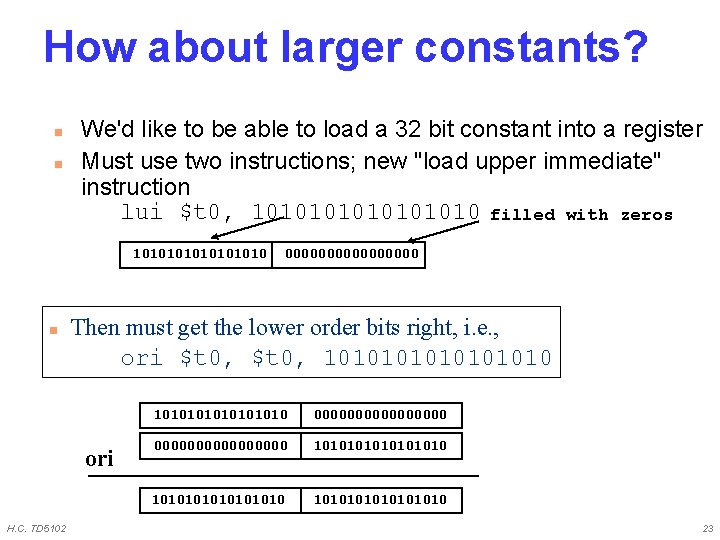

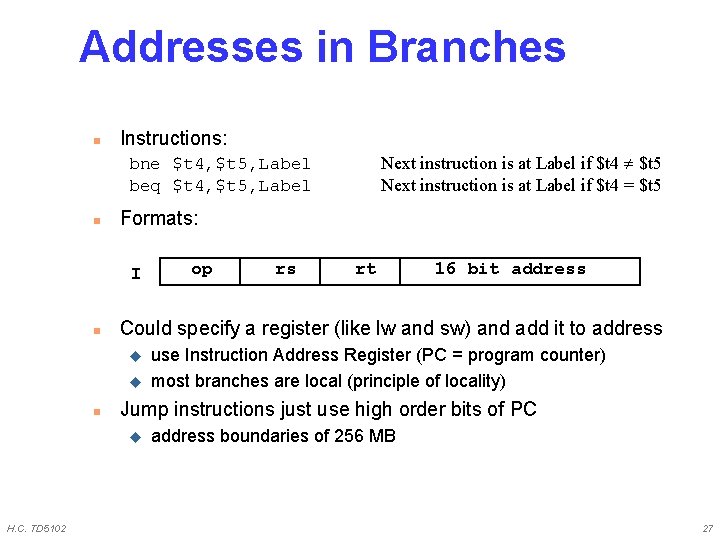

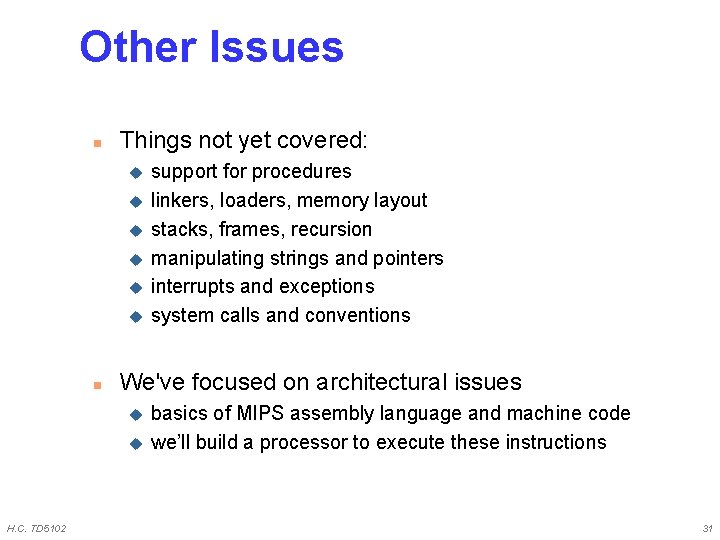

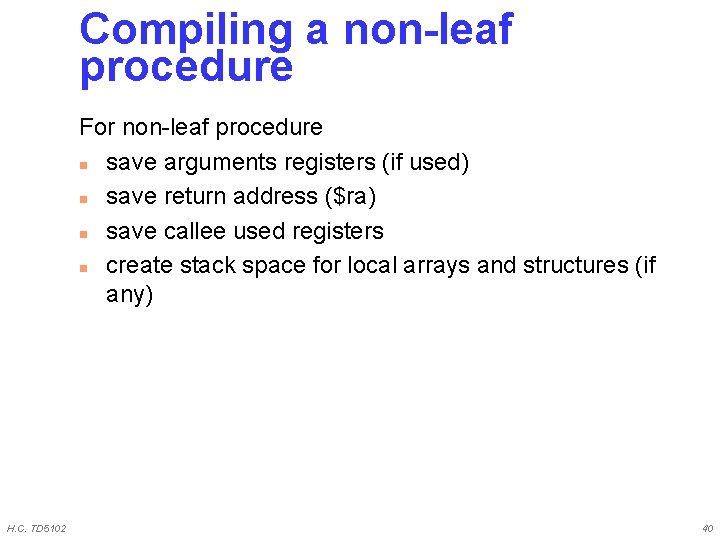

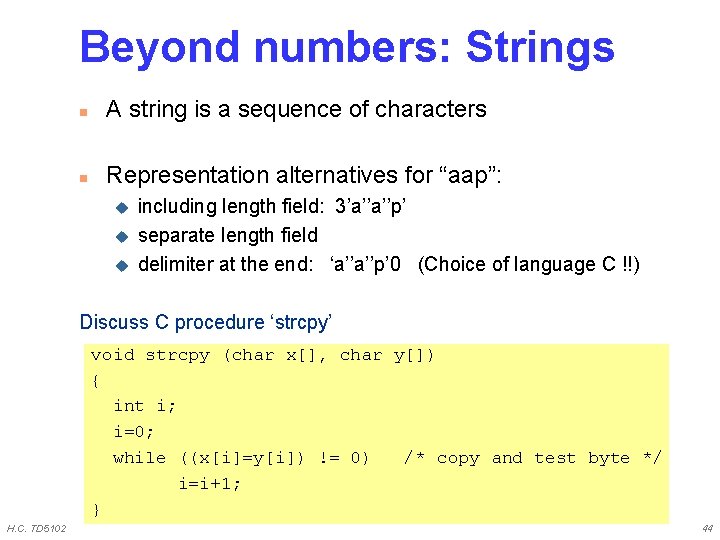

Our First C Example n Can we figure out the code? swap(int v[], int k); { int temp; temp = v[k] = v[k+1]; v[k+1] = temp; } swap: muli add lw lw sw sw jr $2 , $15, $16, $15, $31 $5, 4 $4, $2 0($2) 4($2) Explanation: index k : $5 base address of v: $4 address of v[k] is $4 + 4. $5 H. C. TD 5102 12

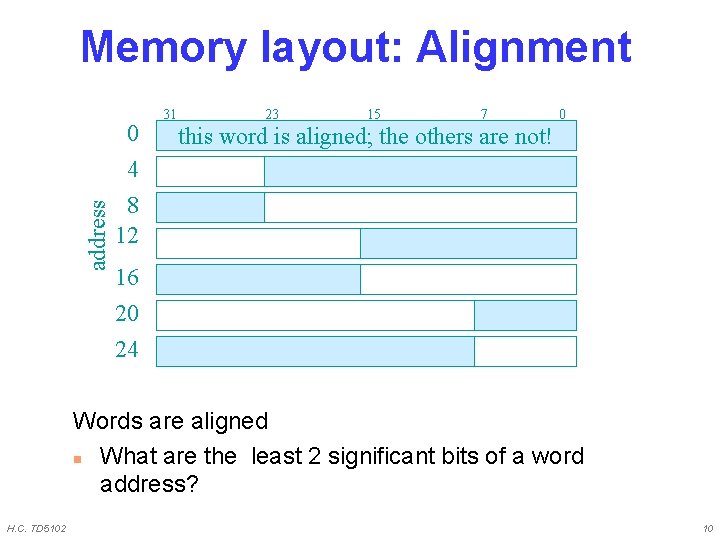

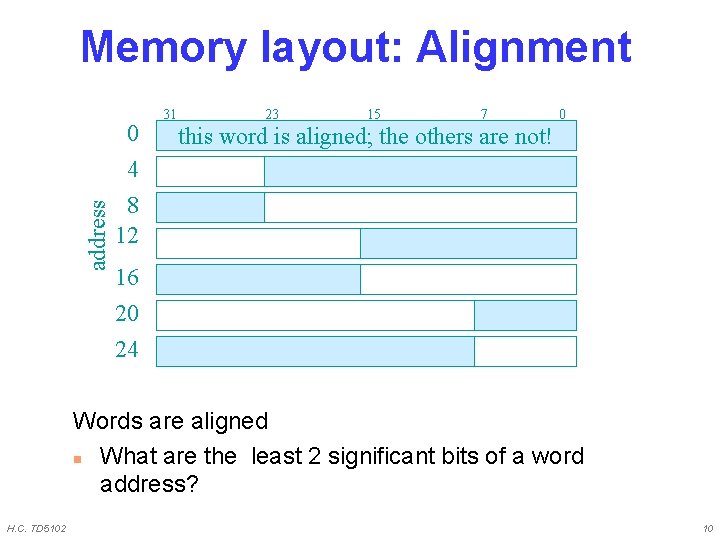

So far we’ve learned: n n H. C. TD 5102 MIPS — loading words but addressing bytes — arithmetic on registers only Instruction Meaning add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) Memory[$s 2+100] sw $s 1, 100($s 2) $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = 13

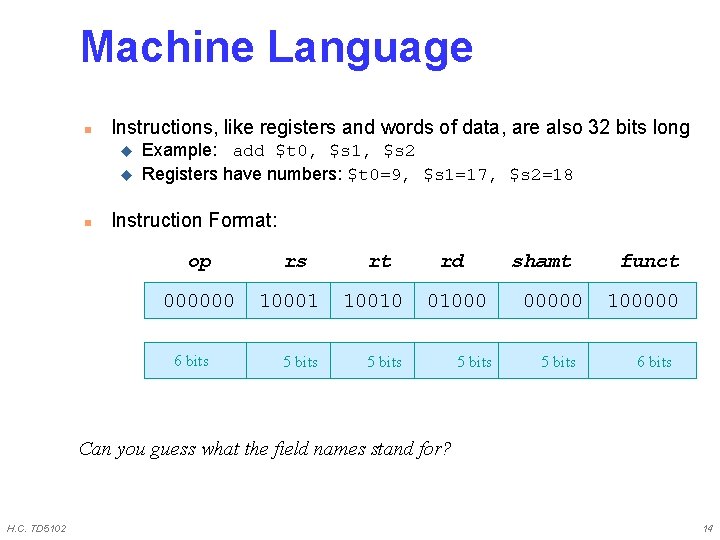

Machine Language n Instructions, like registers and words of data, are also 32 bits long u u n Example: add $t 0, $s 1, $s 2 Registers have numbers: $t 0=9, $s 1=17, $s 2=18 Instruction Format: op rs rt 000000 10001 10010 5 bits 6 bits rd 01000 5 bits shamt 00000 5 bits funct 100000 6 bits Can you guess what the field names stand for? H. C. TD 5102 14

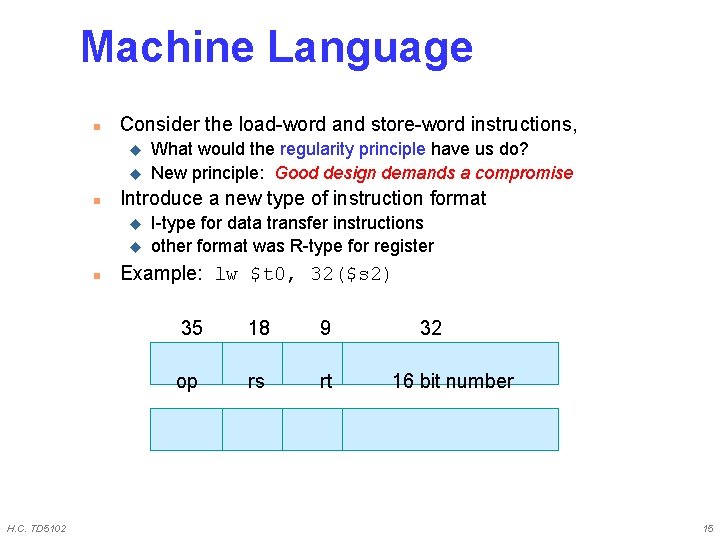

Machine Language n Consider the load-word and store-word instructions, u u n Introduce a new type of instruction format u u n H. C. TD 5102 What would the regularity principle have us do? New principle: Good design demands a compromise I-type for data transfer instructions other format was R-type for register Example: lw $t 0, 32($s 2) 35 18 9 op rs rt 32 16 bit number 15

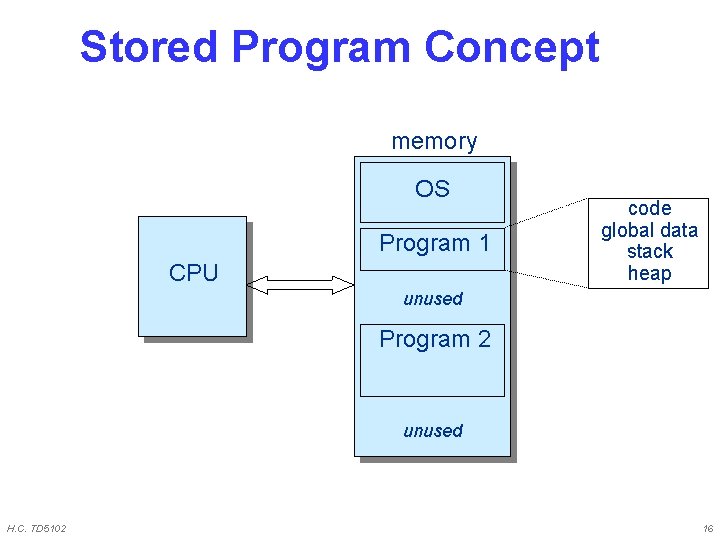

Stored Program Concept memory OS Program 1 CPU code global data stack heap unused Program 2 unused H. C. TD 5102 16

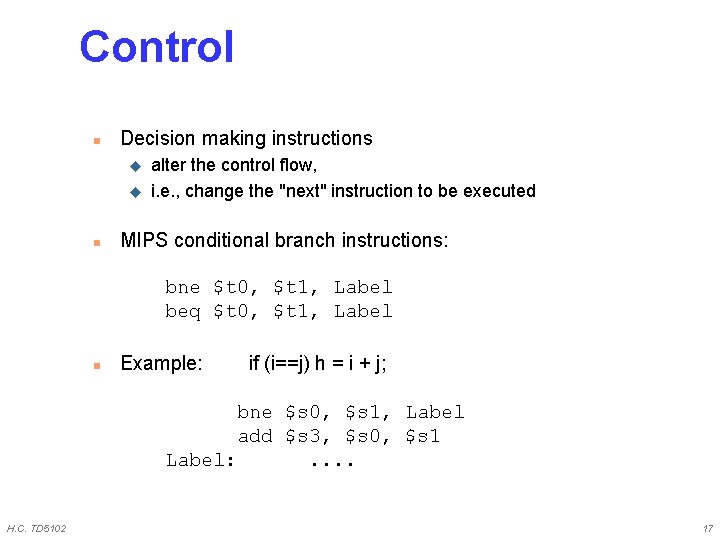

Control n Decision making instructions u u n alter the control flow, i. e. , change the "next" instruction to be executed MIPS conditional branch instructions: bne $t 0, $t 1, Label beq $t 0, $t 1, Label n Example: if (i==j) h = i + j; bne $s 0, $s 1, Label add $s 3, $s 0, $s 1 Label: . . H. C. TD 5102 17

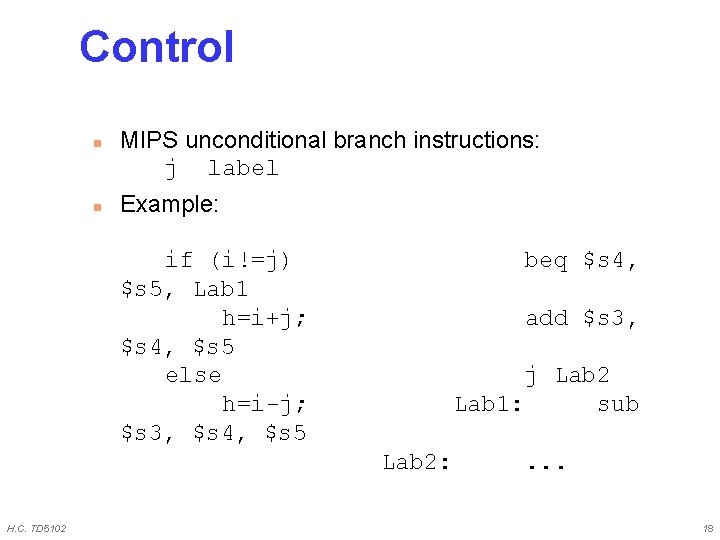

Control n n MIPS unconditional branch instructions: j label Example: if (i!=j) $s 5, Lab 1 h=i+j; $s 4, $s 5 else h=i-j; $s 3, $s 4, $s 5 beq $s 4, add $s 3, j Lab 2 Lab 1: sub Lab 2: H. C. TD 5102 . . . 18

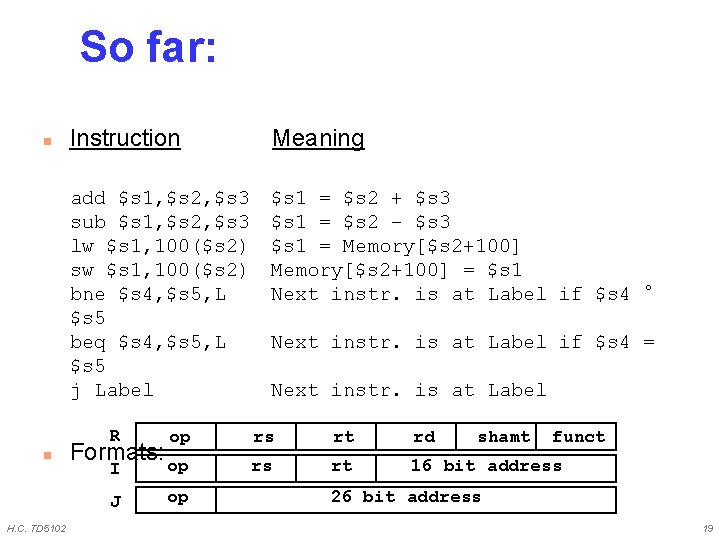

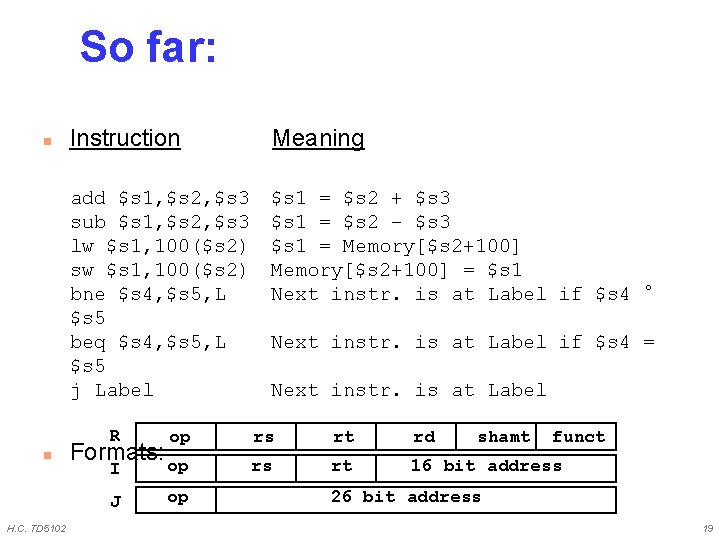

So far: n Instruction Meaning add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) bne $s 4, $s 5, L $s 5 beq $s 4, $s 5, L $s 5 j Label $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 Next instr. is at Label if $s 4 ° R n Formats: op I J H. C. TD 5102 op op Next instr. is at Label if $s 4 = Next instr. is at Label rs rt rd shamt funct rs rt 16 bit address 26 bit address 19

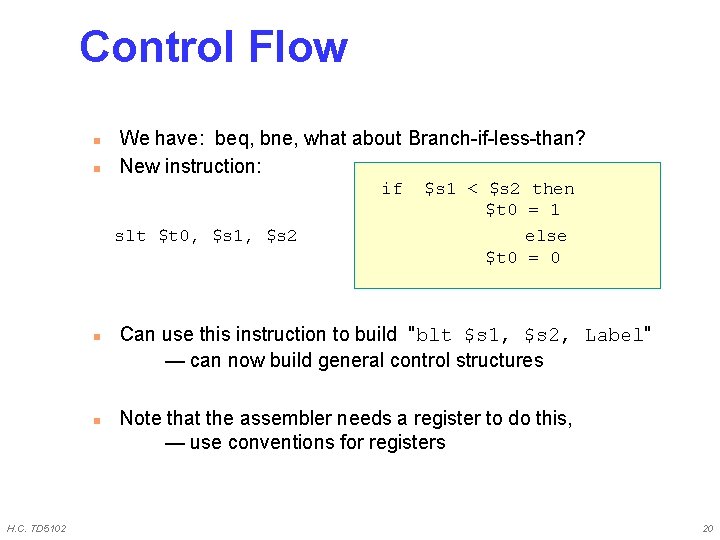

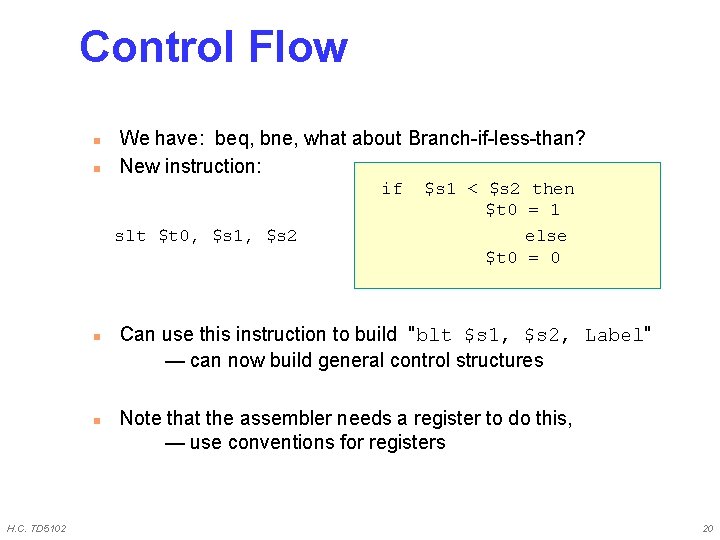

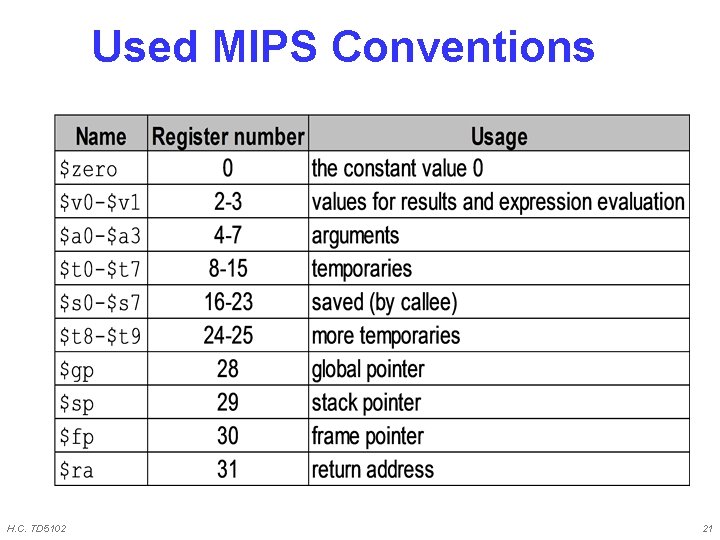

Control Flow n n We have: beq, bne, what about Branch-if-less-than? New instruction: if slt $t 0, $s 1, $s 2 n n H. C. TD 5102 $s 1 < $s 2 then $t 0 = 1 else $t 0 = 0 Can use this instruction to build "blt $s 1, $s 2, Label" — can now build general control structures Note that the assembler needs a register to do this, — use conventions for registers 20

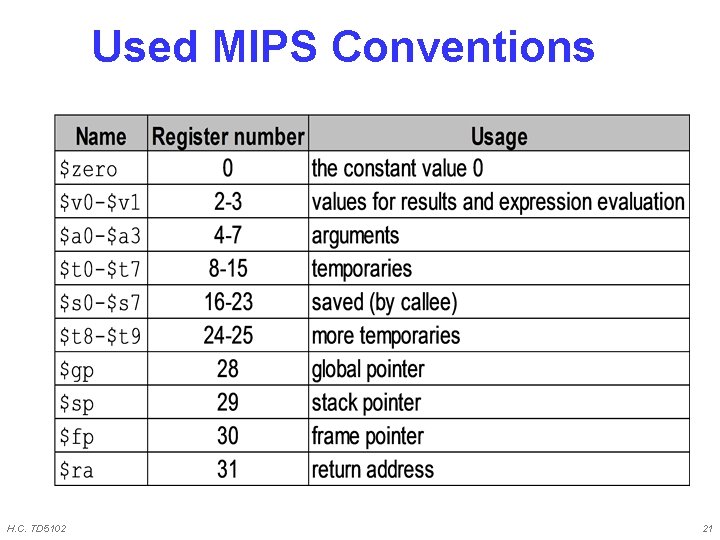

Used MIPS Conventions H. C. TD 5102 21

Constants n n Small constants are used quite frequently (50% of operands) e. g. , A = A + 5; B = B + 1; C = C - 18; Solutions? Why not? u u u n put 'typical constants' in memory and load them create hard-wired registers (like $zero) for constants like one or ……. MIPS Instructions: addi slti andi ori H. C. TD 5102 $29, $8, $29, $18, $29, 4 10 6 4 3 22

How about larger constants? n n We'd like to be able to load a 32 bit constant into a register Must use two instructions; new "load upper immediate" instruction lui $t 0, 10101010 filled with zeros 10101010 n Then must get the lower order bits right, i. e. , ori $t 0, 10101010 ori H. C. TD 5102 00000000 10101010 0000000000000000 1010101010101010 23

Assembly Language vs. Machine Language n n Assembly provides convenient symbolic representation u much easier than writing down numbers u e. g. , destination first Machine language is the underlying reality u n n H. C. TD 5102 e. g. , destination is no longer first Assembly can provide 'pseudoinstructions' u e. g. , “move $t 0, $t 1” exists only in Assembly u would be implemented using “add $t 0, $t 1, $zero” When considering performance you should count real instructions 24

Overview of MIPS n n n R op rs rt rd I op rs rt 16 bit address J op n n H. C. TD 5102 simple instructions all 32 bits wide very structured, no unnecessary baggage only three instruction formats shamt funct 26 bit address rely on compiler to achieve performance — what are the compiler's goals? help compiler where we can 25

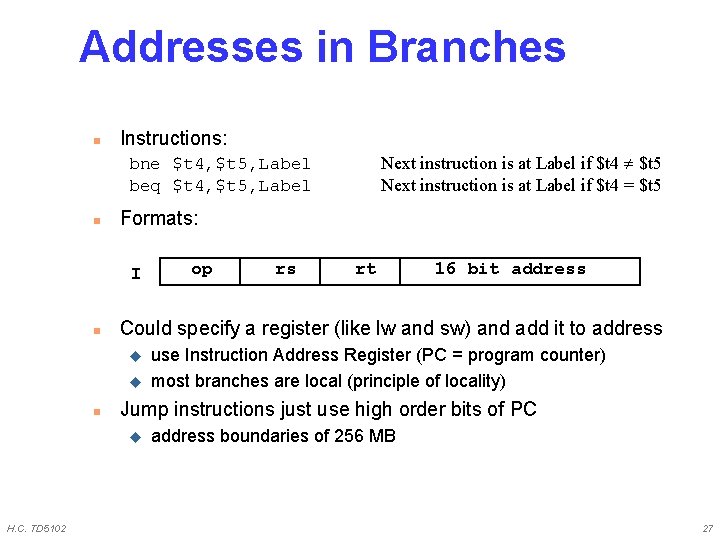

Addresses in Branches and Jumps n Instructions: bne $t 4, $t 5, Label $t 5 beq $t 4, $t 5, Label $t 5 j Label n Formats: op I J n H. C. TD 5102 op rs rt Next instruction is at Label if $t 4 = Next instruction is at Label 16 bit address 26 bit address Addresses are not 32 bits — How do we handle this with load and store instructions? 26

Addresses in Branches n Instructions: Next instruction is at Label if $t 4 $t 5 Next instruction is at Label if $t 4 = $t 5 bne $t 4, $t 5, Label beq $t 4, $t 5, Label n Formats: I n u rt 16 bit address use Instruction Address Register (PC = program counter) most branches are local (principle of locality) Jump instructions just use high order bits of PC u H. C. TD 5102 rs Could specify a register (like lw and sw) and add it to address u n op address boundaries of 256 MB 27

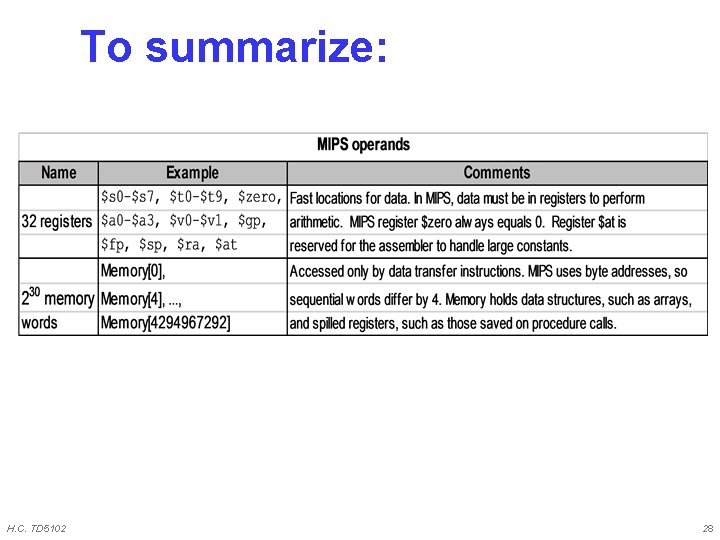

To summarize: H. C. TD 5102 28

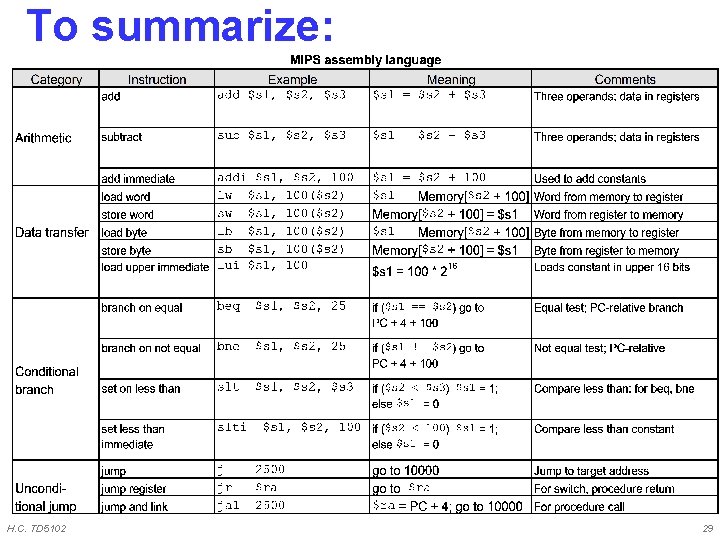

To summarize: H. C. TD 5102 29

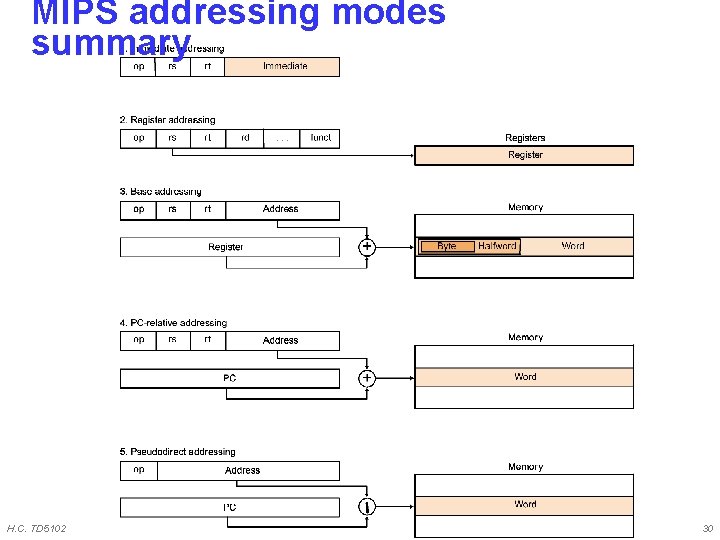

MIPS addressing modes summary H. C. TD 5102 30

Other Issues n Things not yet covered: u u u n We've focused on architectural issues u u H. C. TD 5102 support for procedures linkers, loaders, memory layout stacks, frames, recursion manipulating strings and pointers interrupts and exceptions system calls and conventions basics of MIPS assembly language and machine code we’ll build a processor to execute these instructions 31

Intermezzo: another approach 80 x 86 see intel museum: www. intel. com/museum/online/hist_micro/hof n n n n n H. C. TD 5102 1978: The Intel 8086 is announced (16 bit architecture) 1980: The 8087 floating point coprocessor is added 1982: The 80286 increases address space to 24 bits, +instructions 1985: The 80386 extends to 32 bits, new addressing modes 1989 -1995: The 80486, Pentium Pro add a few instructions (mostly designed for higher performance) 1997: Pentium II with MMX is added 1999: Pentium III, with 70 more SIMD instructions 2001: Pentium IV, very deep pipeline (20 stages) results in high freq. 2003: Pentium IV – Hyperthreading 2005: Multi-core solutions “This history illustrates the impact of the “golden handcuffs” of compatibility 32

A dominant architecture: 80 x 86 n See your textbook for a more detailed description n Complexity: u u n Saving grace: u u H. C. TD 5102 Instructions from 1 to 17 bytes long one operand must act as both a source and destination one operand can come from memory complex addressing modes e. g. , “base or scaled index with 8 or 32 bit displacement” the most frequently used instructions are not too difficult to build compilers avoid the portions of the architecture that are slow 33

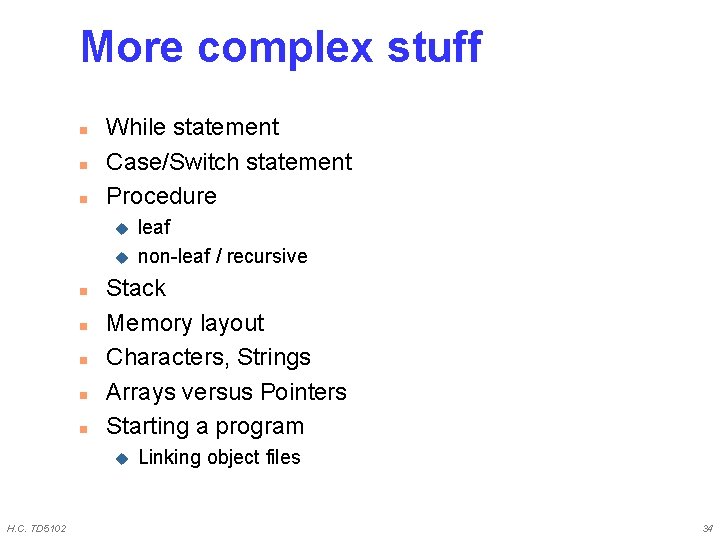

More complex stuff n n n While statement Case/Switch statement Procedure u u n n n Stack Memory layout Characters, Strings Arrays versus Pointers Starting a program u H. C. TD 5102 leaf non-leaf / recursive Linking object files 34

![While statement while savei k iij Loop muli add lw bne add j While statement while (save[i] == k) i=i+j; Loop: muli add lw bne add j](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-35.jpg)

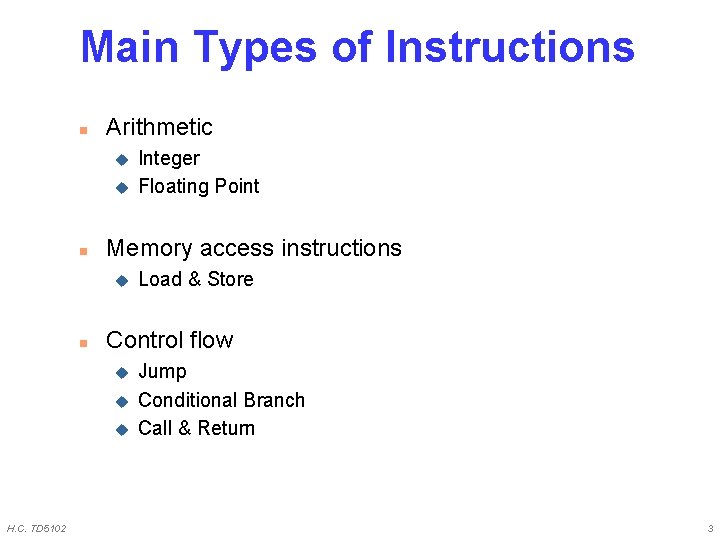

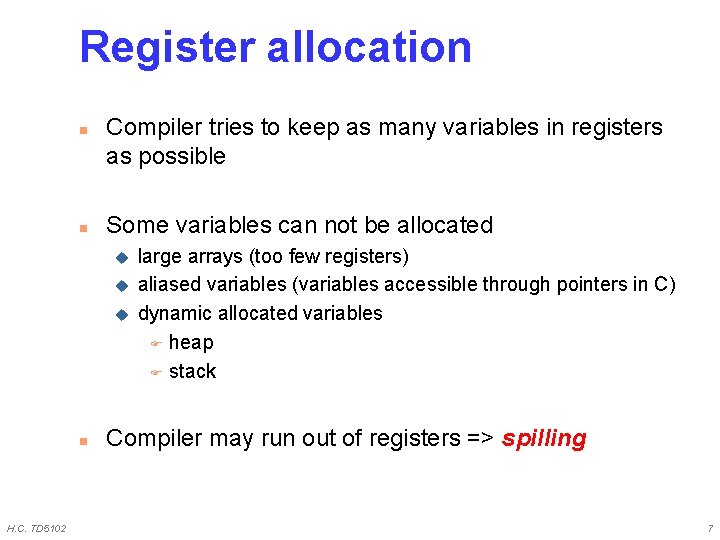

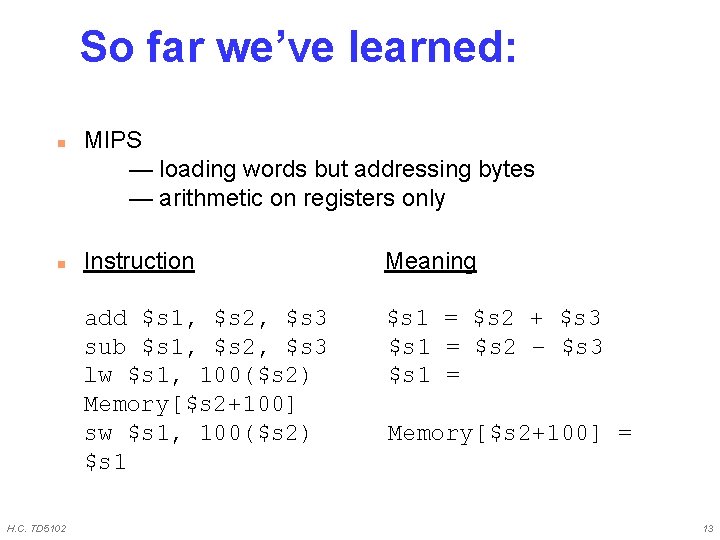

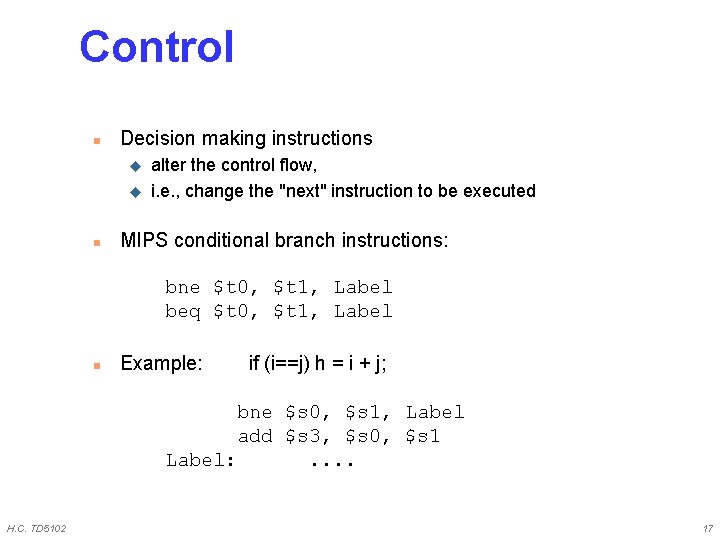

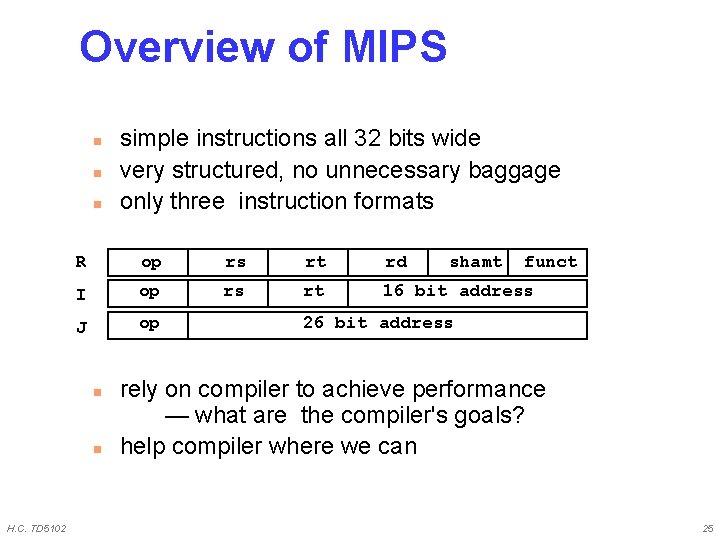

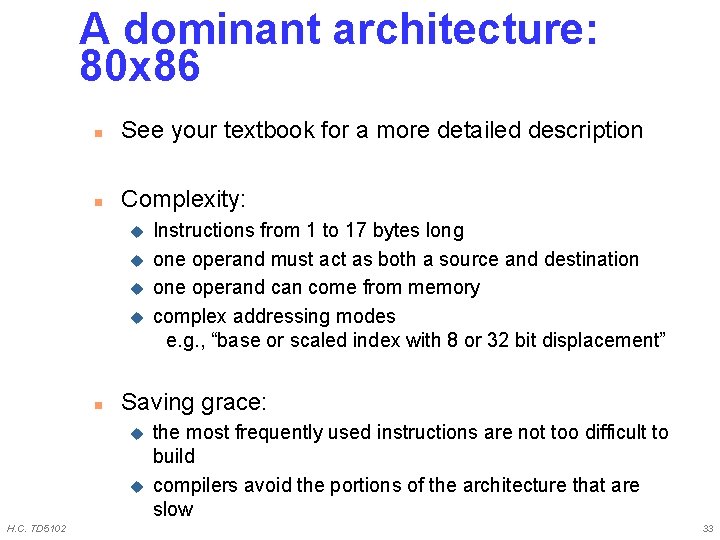

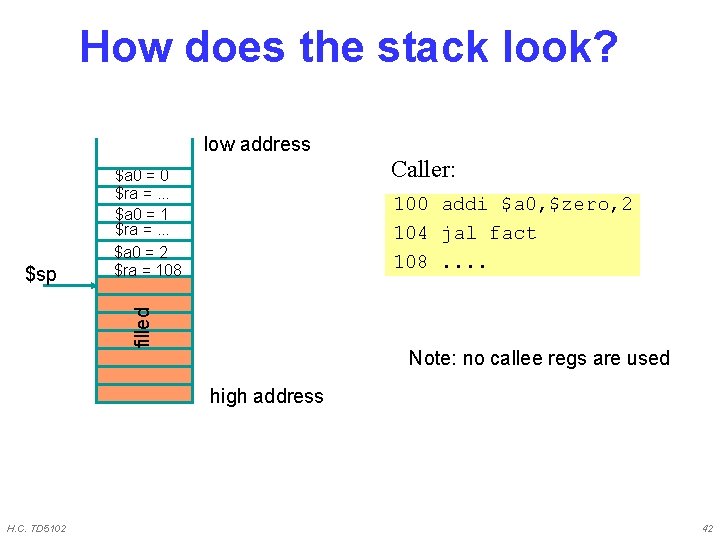

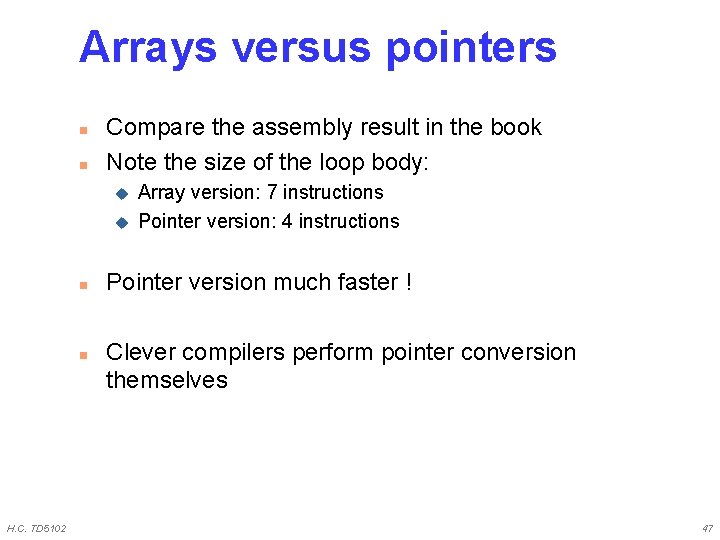

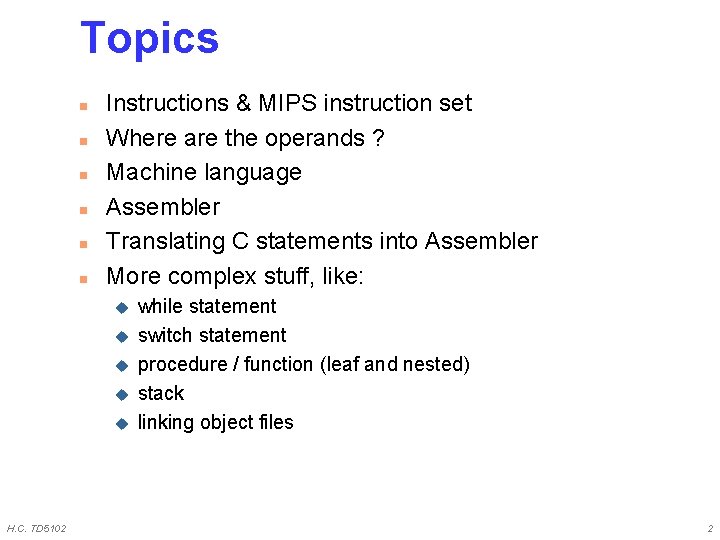

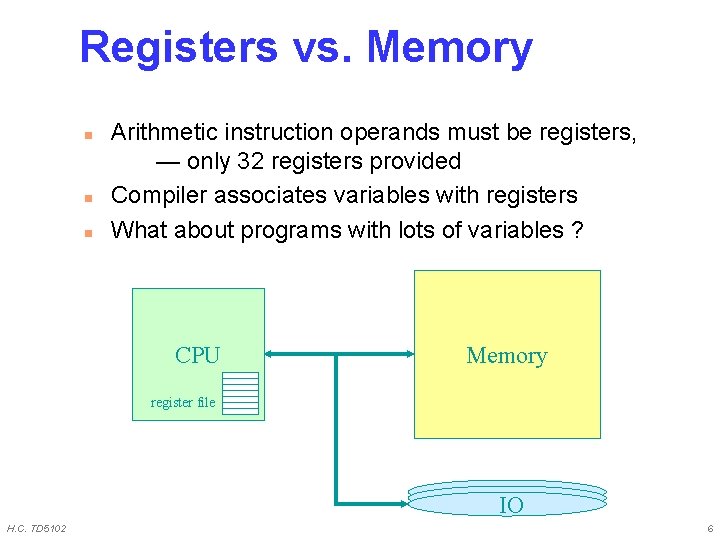

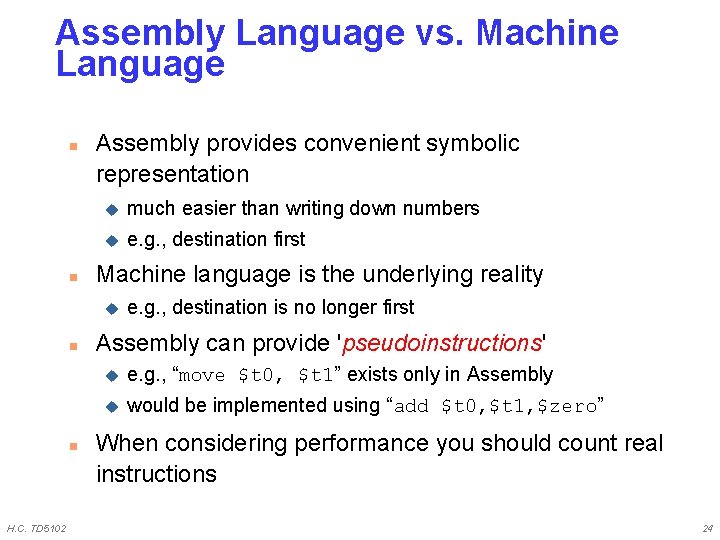

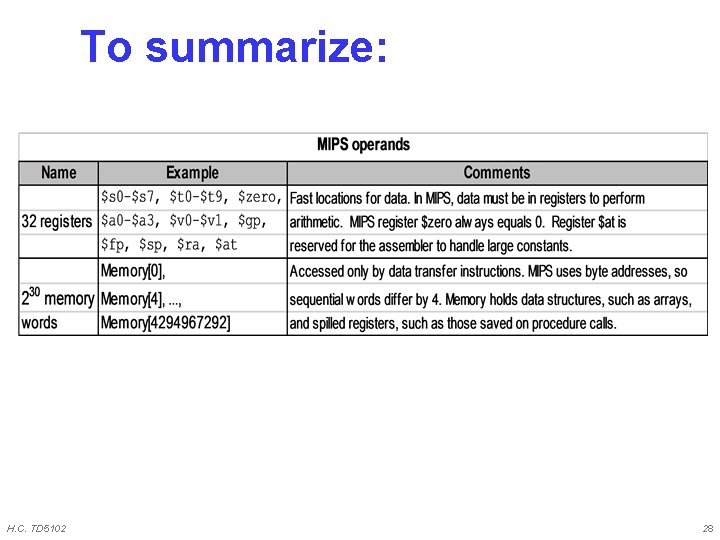

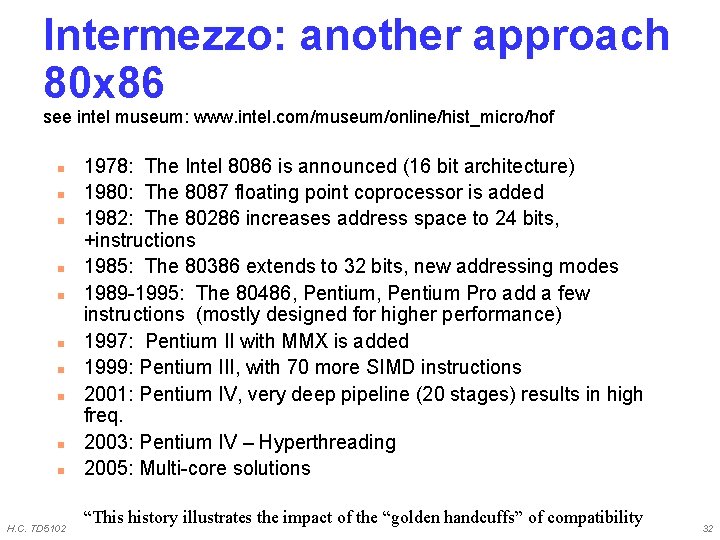

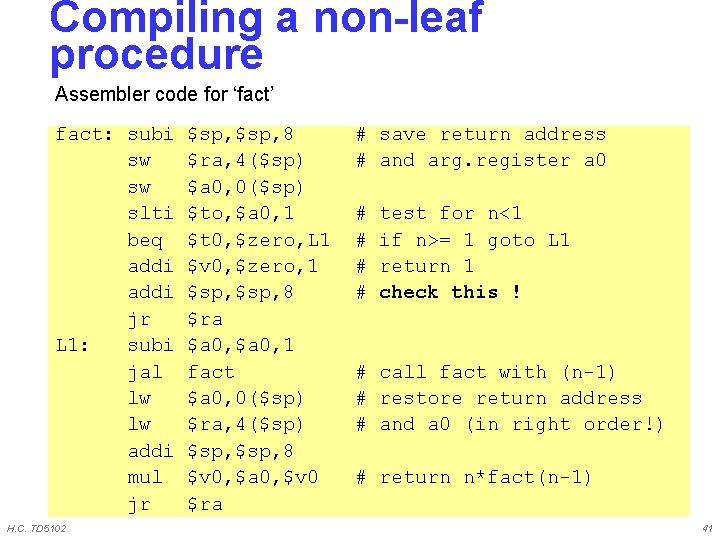

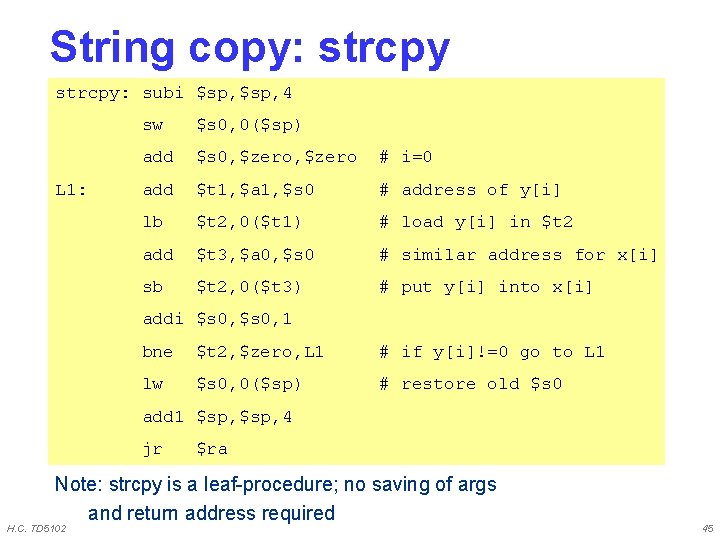

While statement while (save[i] == k) i=i+j; Loop: muli add lw bne add j $t 1, $s 3, 4 $t 1, $s 6 $t 0, 0($t 1) $t 0, $s 5, Exit $s 3, $s 4 Loop # calculate address of # save[i] Exit: H. C. TD 5102 35

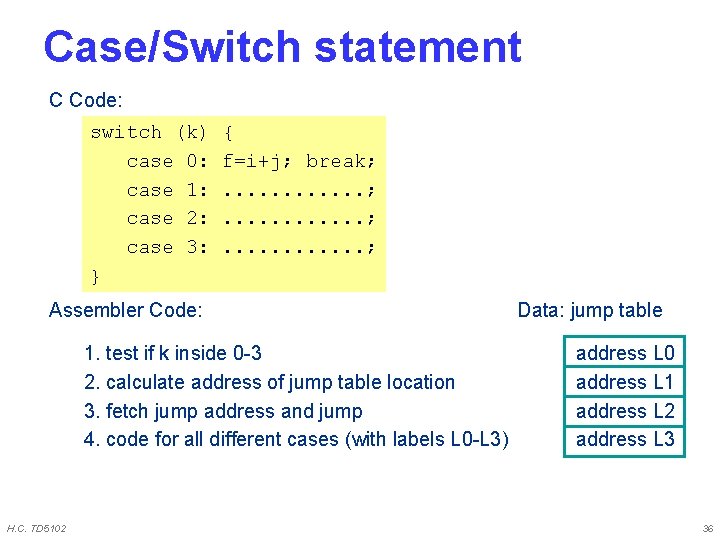

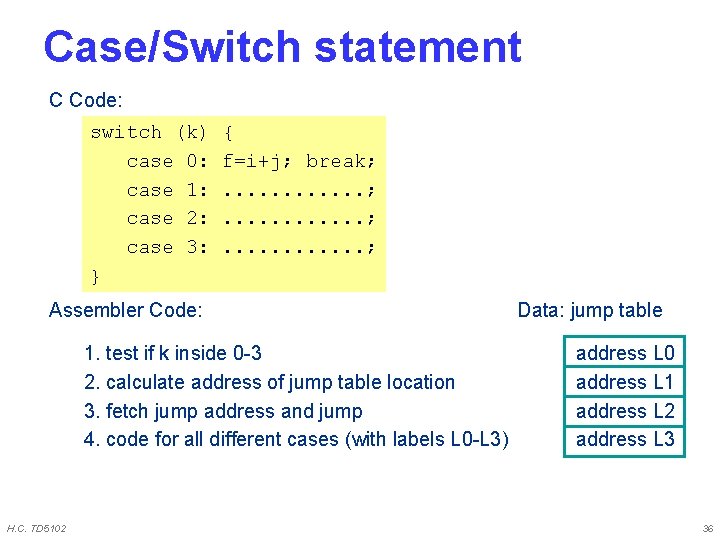

Case/Switch statement C Code: switch (k) case 0: case 1: case 2: case 3: } { f=i+j; break; . . . ; Assembler Code: 1. test if k inside 0 -3 2. calculate address of jump table location 3. fetch jump address and jump 4. code for all different cases (with labels L 0 -L 3) H. C. TD 5102 Data: jump table address L 0 address L 1 address L 2 address L 3 36

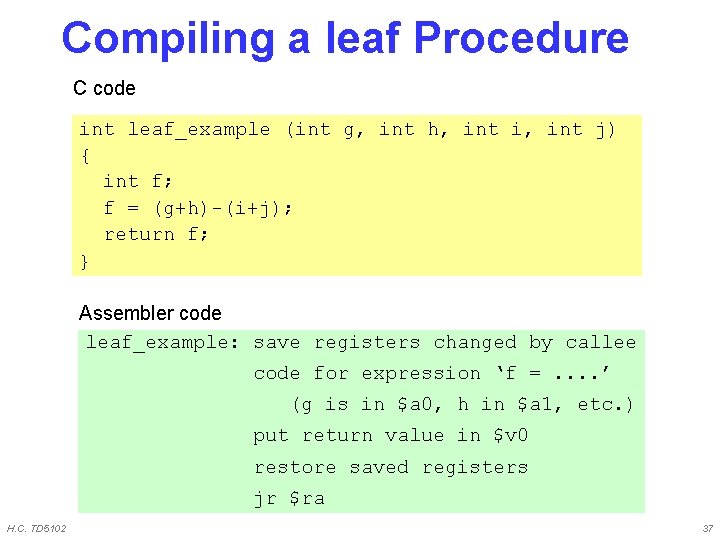

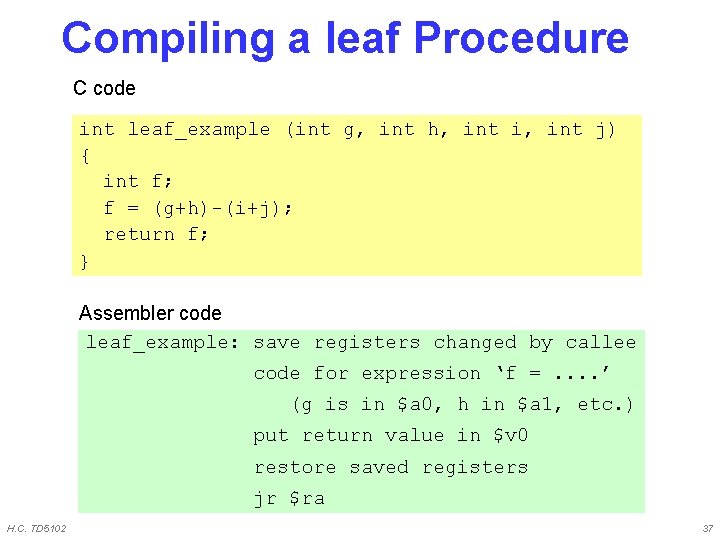

Compiling a leaf Procedure C code int leaf_example (int g, int h, int i, int j) { int f; f = (g+h)-(i+j); return f; } Assembler code leaf_example: save registers changed by callee code for expression ‘f =. . ’ (g is in $a 0, h in $a 1, etc. ) put return value in $v 0 restore saved registers jr $ra H. C. TD 5102 37

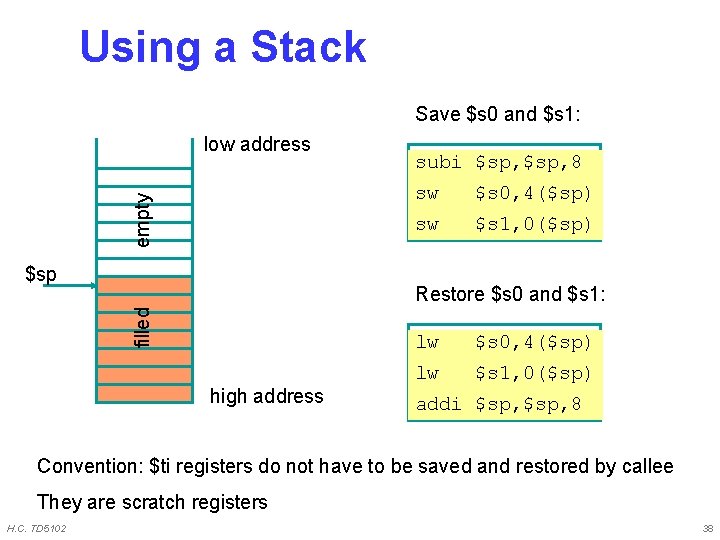

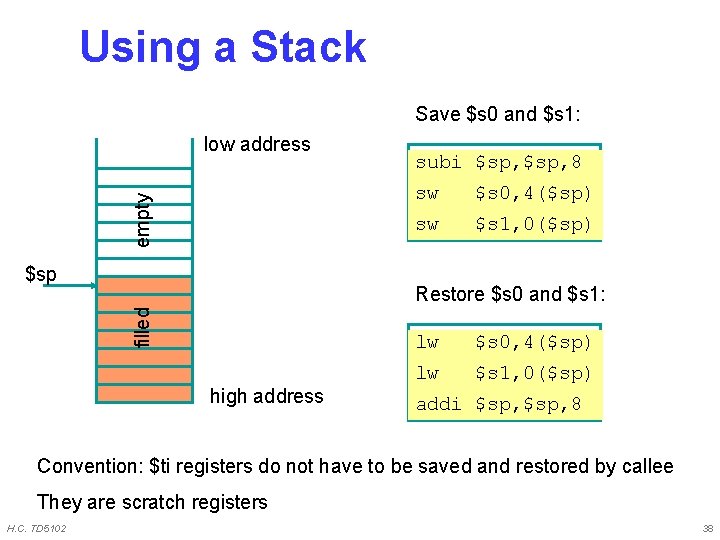

Using a Stack Save $s 0 and $s 1: empty low address $sp subi $sp, 8 sw $s 0, 4($sp) sw $s 1, 0($sp) filled Restore $s 0 and $s 1: high address lw $s 0, 4($sp) lw $s 1, 0($sp) addi $sp, 8 Convention: $ti registers do not have to be saved and restored by callee They are scratch registers H. C. TD 5102 38

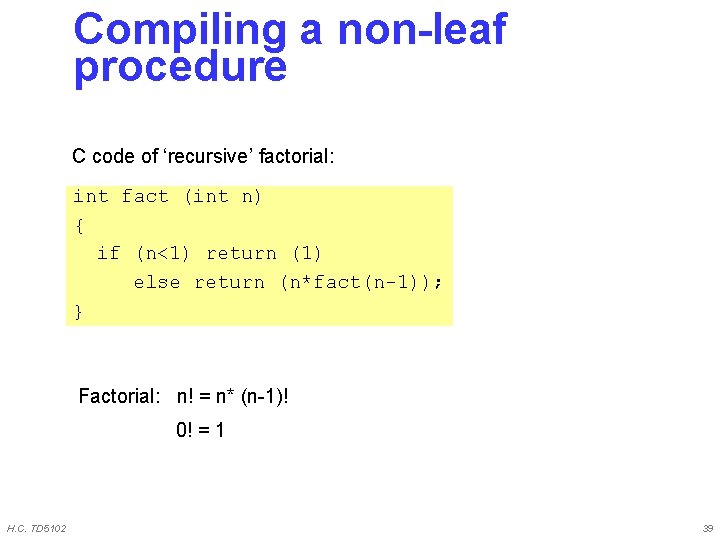

Compiling a non-leaf procedure C code of ‘recursive’ factorial: int fact (int n) { if (n<1) return (1) else return (n*fact(n-1)); } Factorial: n! = n* (n-1)! 0! = 1 H. C. TD 5102 39

Compiling a non-leaf procedure For non-leaf procedure n save arguments registers (if used) n save return address ($ra) n save callee used registers n create stack space for local arrays and structures (if any) H. C. TD 5102 40

Compiling a non-leaf procedure Assembler code for ‘fact’ fact: subi sw sw slti beq addi jr L 1: subi jal lw lw addi mul jr H. C. TD 5102 $sp, 8 $ra, 4($sp) $a 0, 0($sp) $to, $a 0, 1 $t 0, $zero, L 1 $v 0, $zero, 1 $sp, 8 $ra $a 0, 1 fact $a 0, 0($sp) $ra, 4($sp) $sp, 8 $v 0, $a 0, $v 0 $ra # save return address # and arg. register a 0 # # test for n<1 if n>= 1 goto L 1 return 1 check this ! # call fact with (n-1) # restore return address # and a 0 (in right order!) # return n*fact(n-1) 41

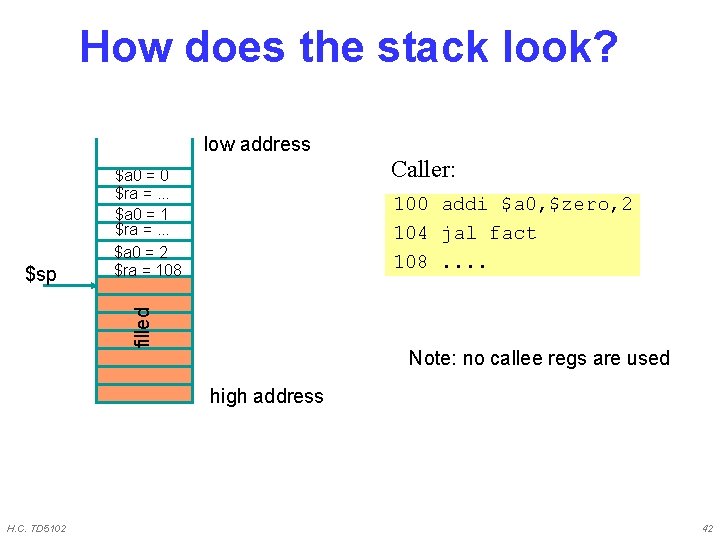

How does the stack look? low address Caller: 100 addi $a 0, $zero, 2 104 jal fact 108. . filled $sp $a 0 = 0 $ra =. . . $a 0 = 1 $ra =. . . $a 0 = 2 $ra = 108 Note: no callee regs are used high address H. C. TD 5102 42

Beyond numbers: characters n n H. C. TD 5102 Characters are often represented using the ASCII standard ASCII = American Standard COde for Information Interchange See table 3. 15, page 142 Note: value(a) - value(A) = 32 value(z) - value(Z) = 32 43

Beyond numbers: Strings n A string is a sequence of characters n Representation alternatives for “aap”: u u u including length field: 3’a’’a’’p’ separate length field delimiter at the end: ‘a’’a’’p’ 0 (Choice of language C !!) Discuss C procedure ‘strcpy’ void strcpy (char x[], char y[]) { int i; i=0; while ((x[i]=y[i]) != 0) /* copy and test byte */ i=i+1; } H. C. TD 5102 44

String copy: strcpy: subi $sp, 4 L 1: sw $s 0, 0($sp) add $s 0, $zero # i=0 add $t 1, $a 1, $s 0 # address of y[i] lb $t 2, 0($t 1) # load y[i] in $t 2 add $t 3, $a 0, $s 0 # similar address for x[i] sb $t 2, 0($t 3) # put y[i] into x[i] addi $s 0, 1 bne $t 2, $zero, L 1 # if y[i]!=0 go to L 1 lw $s 0, 0($sp) # restore old $s 0 add 1 $sp, 4 jr $ra Note: strcpy is a leaf-procedure; no saving of args and return address required H. C. TD 5102 45

![Arrays versus pointers Array version clear 1 int array int size int i Arrays versus pointers Array version: clear 1 (int array[], int size) { int i;](https://slidetodoc.com/presentation_image/3d8e34d4ee945c986279f51234fd9006/image-46.jpg)

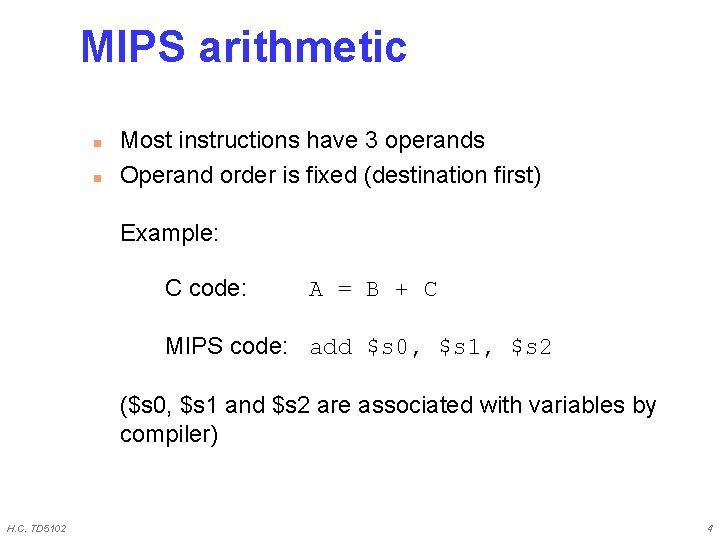

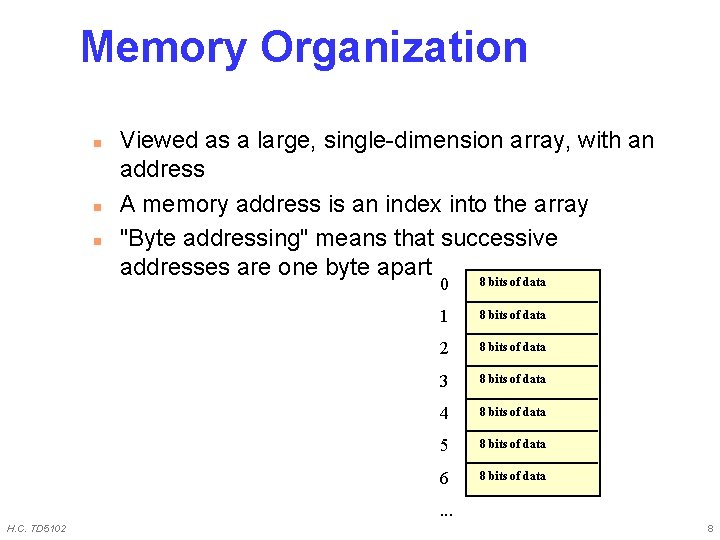

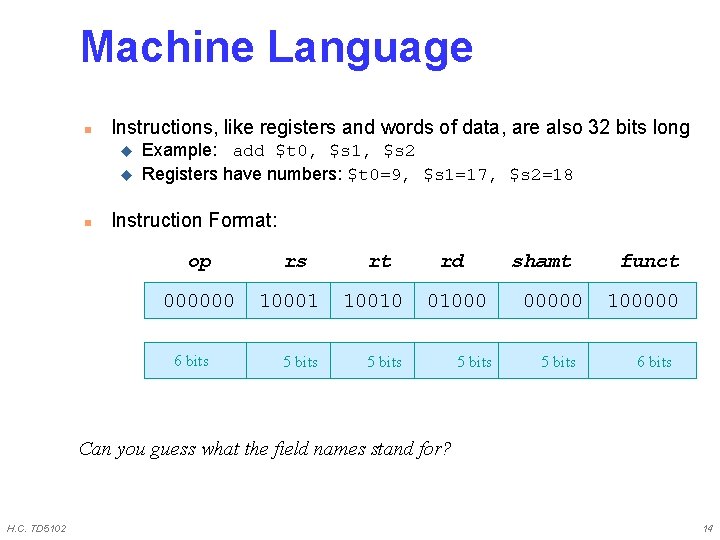

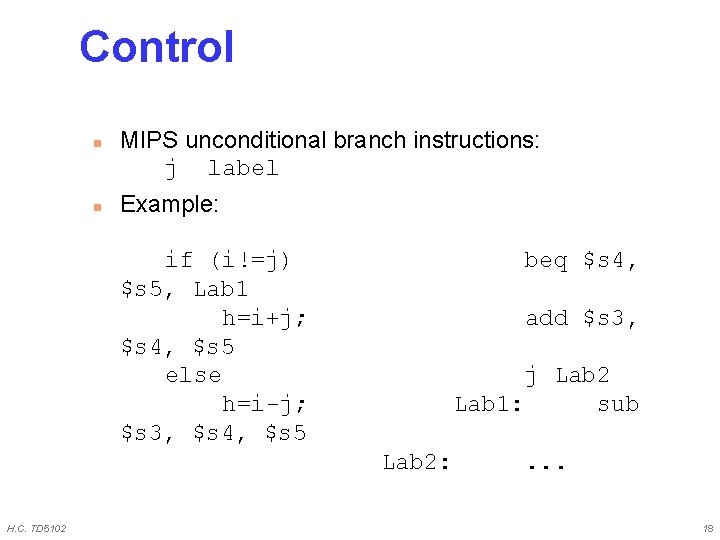

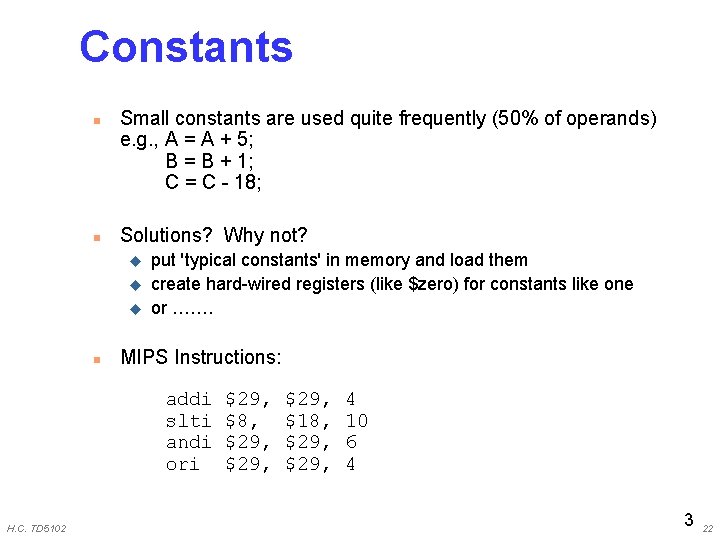

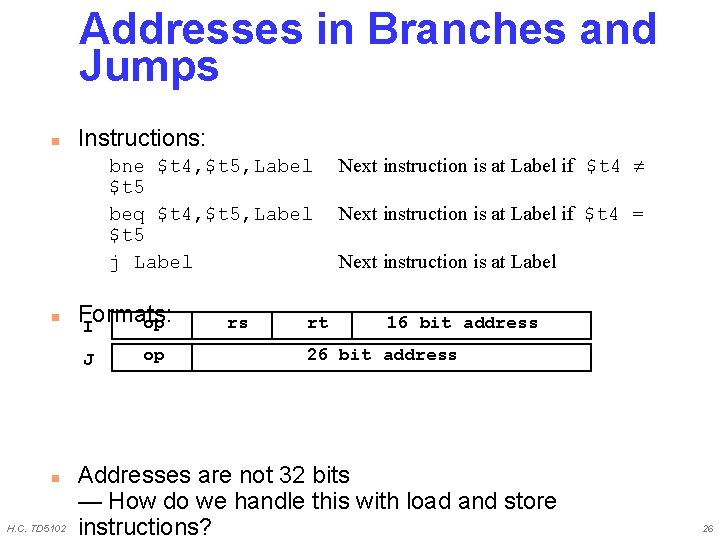

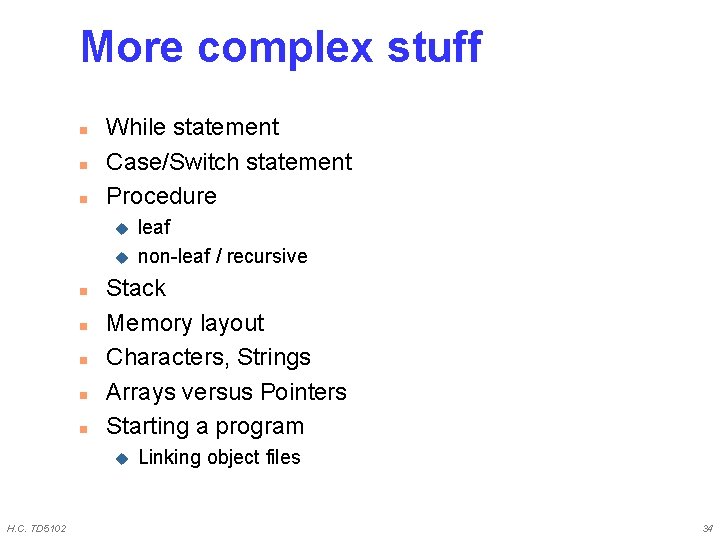

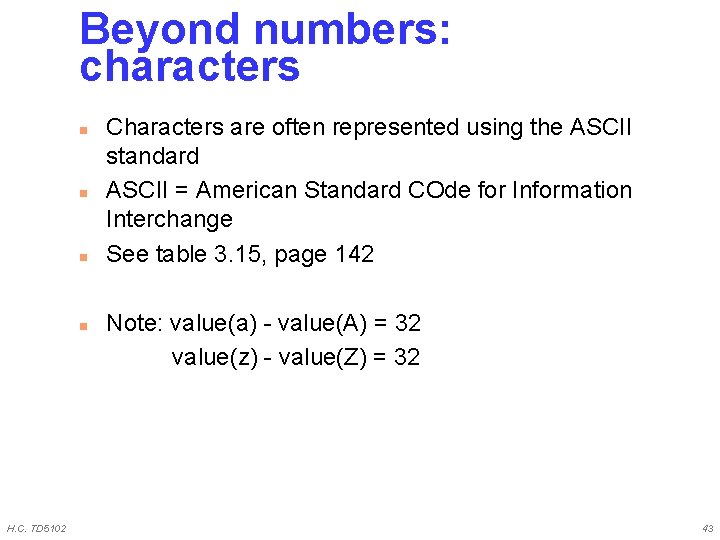

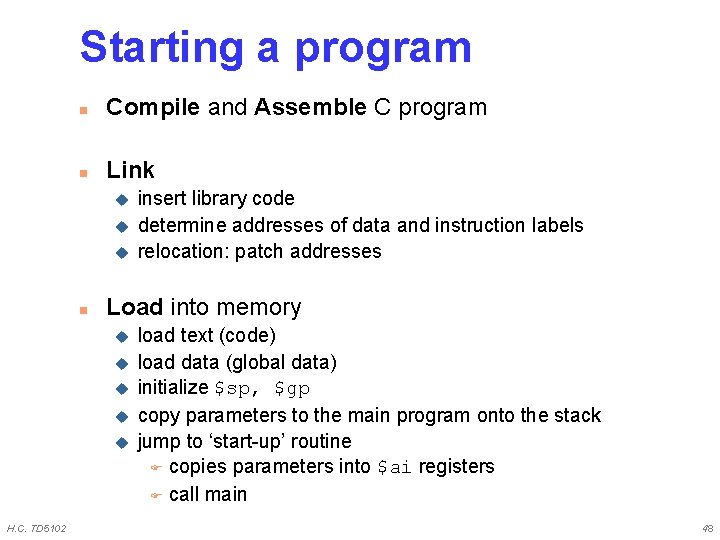

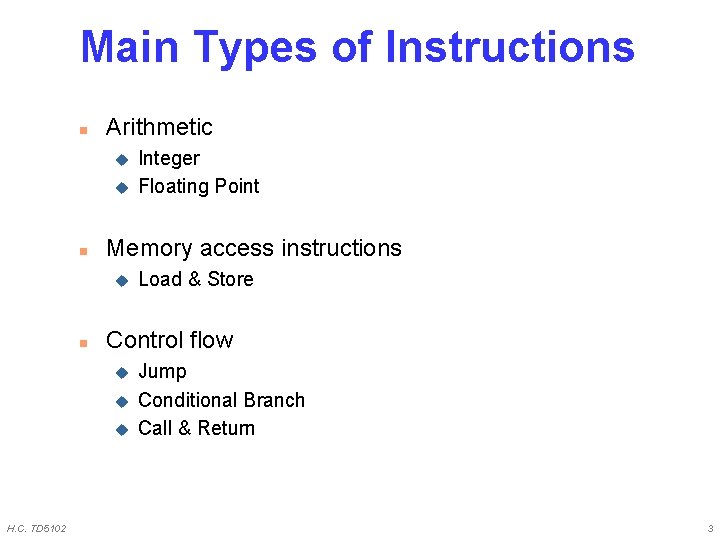

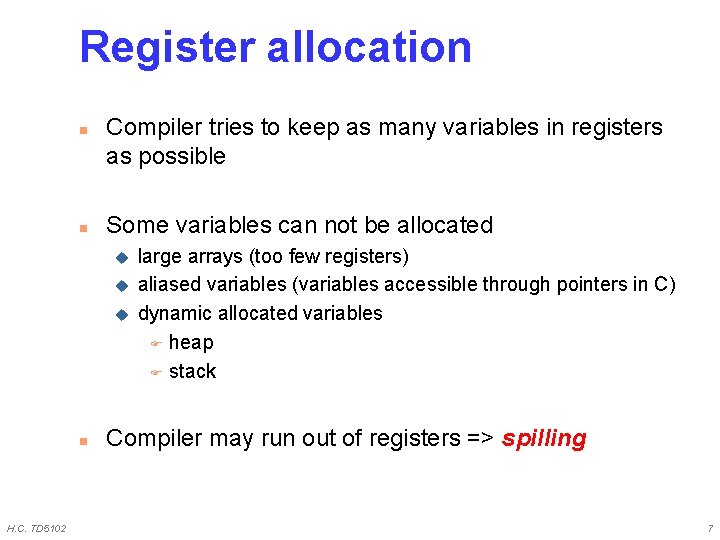

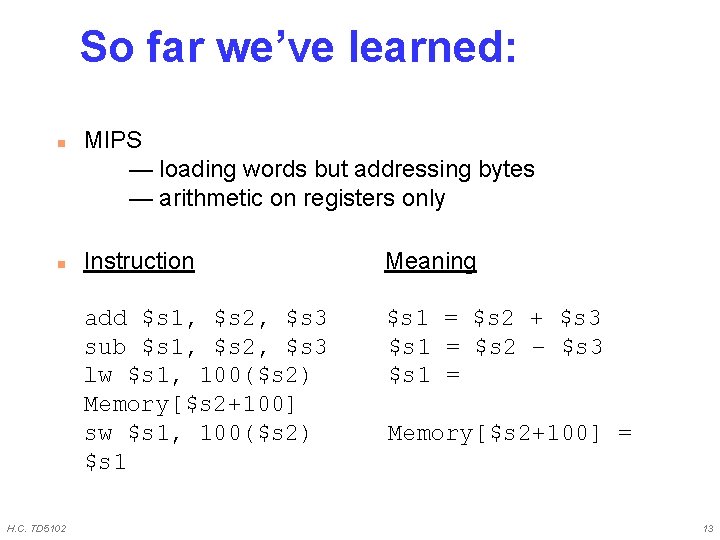

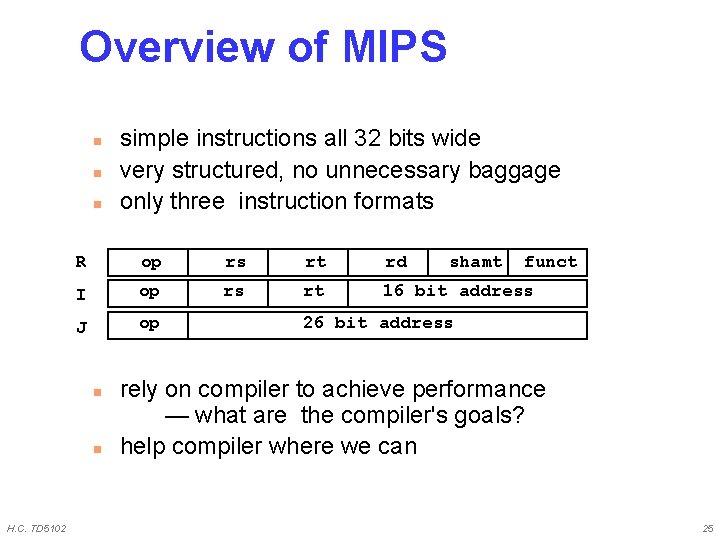

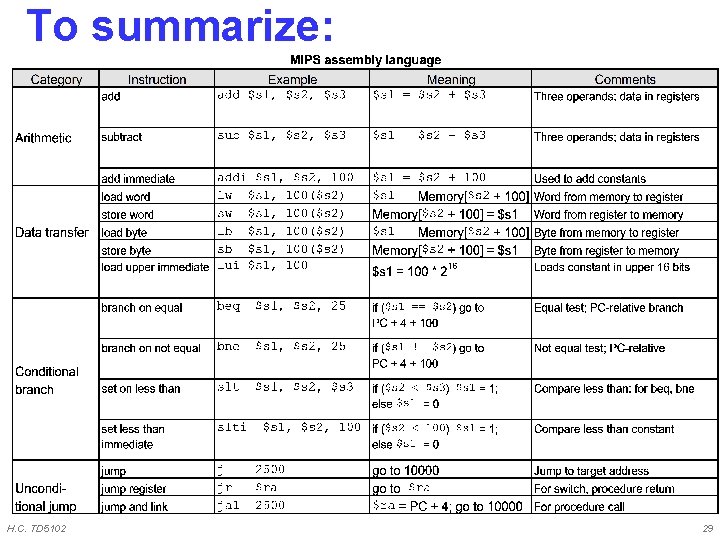

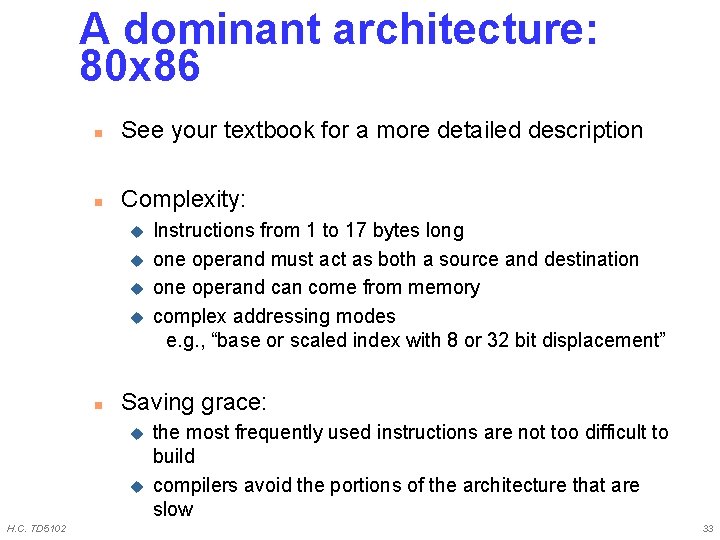

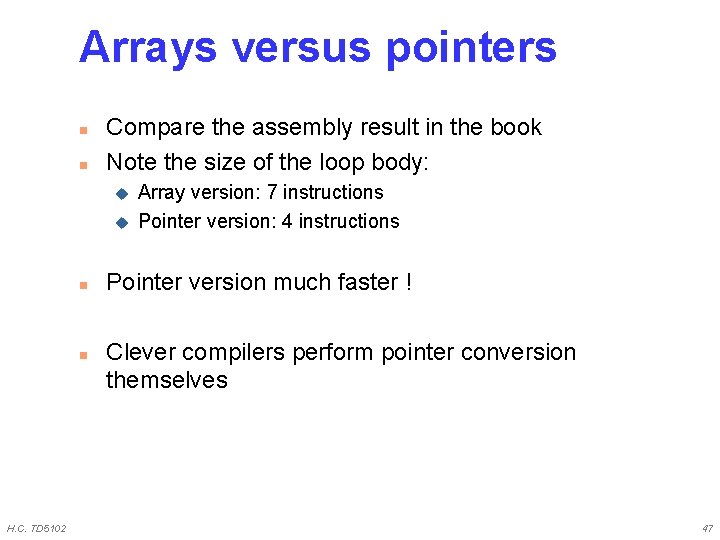

Arrays versus pointers Array version: clear 1 (int array[], int size) { int i; for (i=0; i<size; i=i+1) array[i]=0; } Two programs which initialize an array to zero Pointer version: clear 2 (int *array, int size) { int *p; for (p=&array[0]; p<&array[size]; p=p+1) *p=0; } H. C. TD 5102 46

Arrays versus pointers n n Compare the assembly result in the book Note the size of the loop body: u u n n H. C. TD 5102 Array version: 7 instructions Pointer version: 4 instructions Pointer version much faster ! Clever compilers perform pointer conversion themselves 47

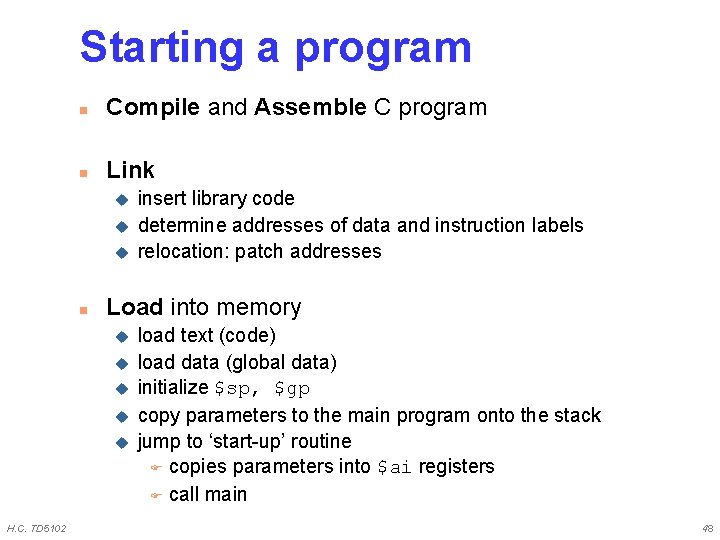

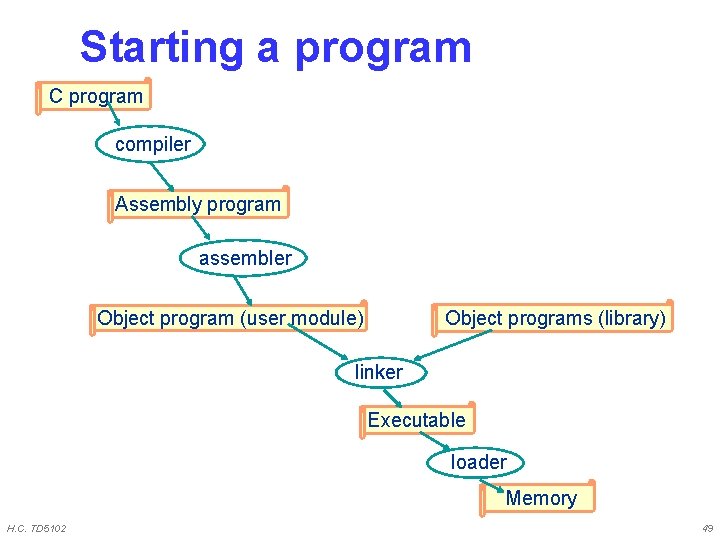

Starting a program n Compile and Assemble C program n Link u u u n Load into memory u u u H. C. TD 5102 insert library code determine addresses of data and instruction labels relocation: patch addresses load text (code) load data (global data) initialize $sp, $gp copy parameters to the main program onto the stack jump to ‘start-up’ routine F copies parameters into $ai registers F call main 48

Starting a program C program compiler Assembly program assembler Object program (user module) Object programs (library) linker Executable loader Memory H. C. TD 5102 49