Silicon MOS 8255 Silicon Mos 8255 interfaccia di

- Slides: 42

Silicon MOS 8255 Silicon Mos 8255 interfaccia di I/O al bus di sistema Il data sheet completo è reperibile al http: //www. intel. com/design/periphrl/datashts/ 10/16/2021 1

Silicon Mos 8255 • L’ 8255 è un dispositivo, programmabile, di I/O progettato inizialmente per essere usato con i microprocessori 8008 e 8080, ma ancora utilizzato. • La sua funzione è quella di interfacciare i dispositivi periferici al bus di sistema. • L’ 8255 è disponibile a 40 -pin DIP o a 44 -pin plastic leaded chip carrier (PLCC) package. Noi esamineremo quello a 40 pin. 10/16/2021 2

Caratteristiche del 8255 • 24 Pins di I/O programmabili. • Completamente TTL compatibile. • Completamente compatibile con le famiglie dei microprocessori MCSTM-8 e MCSTM-80. • Bit Set/Reset diretto • 40 -Pin Dual In-Line Package. 10/16/2021 3

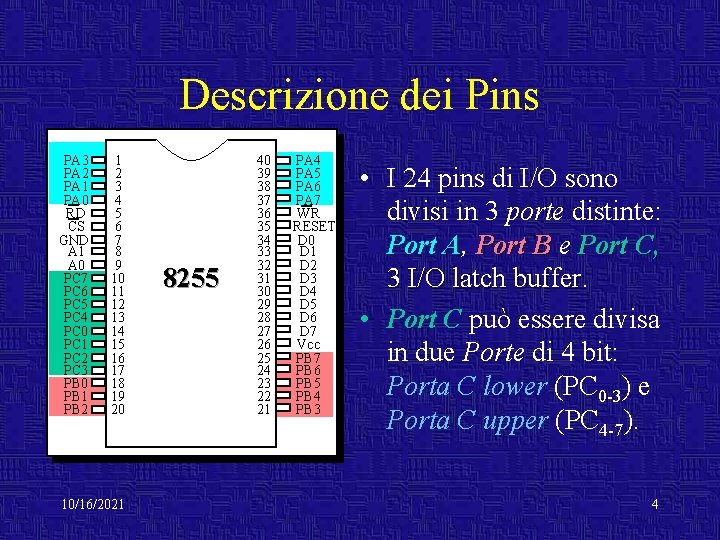

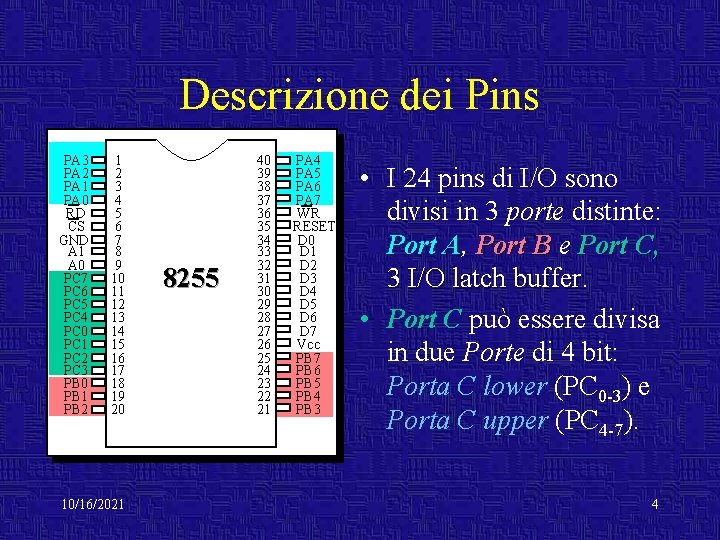

Descrizione dei Pins PA 3 PA 2 PA 1 PA 0 RD CS GND A 1 A 0 PC 7 PC 6 PC 5 PC 4 PC 0 PC 1 PC 2 PC 3 PB 0 PB 1 PB 2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10/16/2021 8255 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 PA 4 PA 5 PA 6 PA 7 WR RESET D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Vcc PB 7 PB 6 PB 5 PB 4 PB 3 • I 24 pins di I/O sono divisi in 3 porte distinte: Port A, A Port B e Port C, 3 I/O latch buffer • Port C può essere divisa in due Porte di 4 bit: Porta C lower (PC 0 -3) e Porta C upper (PC 4 -7). 4

Descrizione dei Pins PA 3 PA 2 PA 1 PA 0 RD CS GND A 1 A 0 PC 7 PC 6 PC 5 PC 4 PC 0 PC 1 PC 2 PC 3 PB 0 PB 1 PB 2 RD 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10/16/2021 8255 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 • RD (Read Control) : Si tratta di un input che assume WR il valore basso quando la CPU effettua una operazione di lettura. PA 4 PA 5 PA 6 PA 7 WR RESET D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Vcc PB 7 PB 6 PB 5 PB 4 PB 3 • WR (Write Control): Input che assume un valore basso quando la CPU effettua una operazione di scrittura. 5

Descrizione dei pins PA 3 PA 2 PA 1 PA 0 RD CS GND A 1 A 0 PC 7 PC 6 PC 5 PC 4 PC 0 PC 1 PC 2 PC 3 PB 0 PB 1 PB 2 CS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10/16/2021 8255 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 PA 4 PA 5 PA 6 PA 7 WR RESET D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Vcc PB 7 PB 6 PB 5 PB 4 PB 3 • CS (Chip Select): Un valore basso su questo input attiva l’ 8255 per rispondere ai segnali di RD e WR. Altrimenti tali segnali vengono ignorati. 6

Descrizone di Pins PA 3 PA 2 PA 1 PA 0 RD CS GND 1 A 1 A 0 PC 7 0 PC 6 PC 5 PC 4 PC 0 PC 1 PC 2 PC 3 PB 0 PB 1 PB 2 A A 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10/16/2021 8255 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 PA 4 PA 5 PA 6 PA 7 WR RESET D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Vcc PB 7 PB 6 PB 5 PB 4 PB 3 • A 1 -0 (Address): questi input, in concomitanza con i segnali RD e WR, seleziona una delle tre Porte oppure il Control Word Registers. 7

Descrizione dei Pins A 1 0 0 1 1 A 1 X X 10/16/2021 A 2 0 1 0 1 A 2 X X RD 0 0 RD 1 1 RD X 1 WR 1 1 WR 0 0 WR X 1 CS Input Operation(Read) 0 Port A - Data Bus 0 Port B - Data Bus 0 Port C - Data Bus Control Word - Data Bus 0 CS Output Operation(Write) 0 Data Bus - Port A 0 Data Bus - Port B 0 Data Bus - Port C Data Bus - Control Word 0 Funzioni disabilitate CS 1 Data Bus - 3° stato 0 Data Bus - 3° stato 8

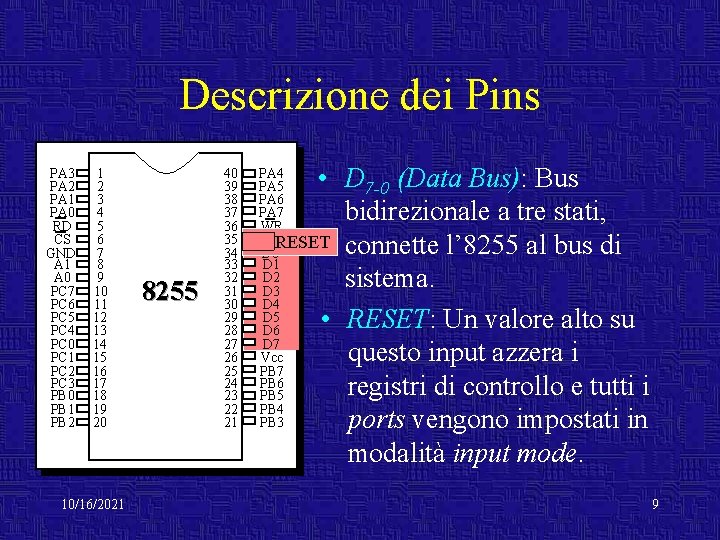

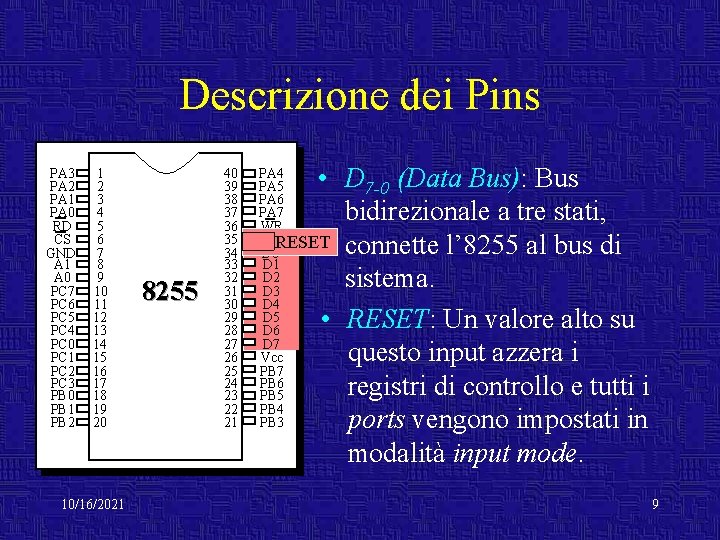

Descrizione dei Pins PA 3 PA 2 PA 1 PA 0 RD CS GND A 1 A 0 PC 7 PC 6 PC 5 PC 4 PC 0 PC 1 PC 2 PC 3 PB 0 PB 1 PB 2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 10/16/2021 8255 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 • D 7 -0 (Data Bus): Bus bidirezionale a tre stati, connette l’ 8255 al bus di sistema. • RESET: Un valore alto su questo input azzera i registri di controllo e tutti i ports vengono impostati in modalità input mode. PA 4 PA 5 PA 6 PA 7 WR RESET D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Vcc PB 7 PB 6 PB 5 PB 4 PB 3 9

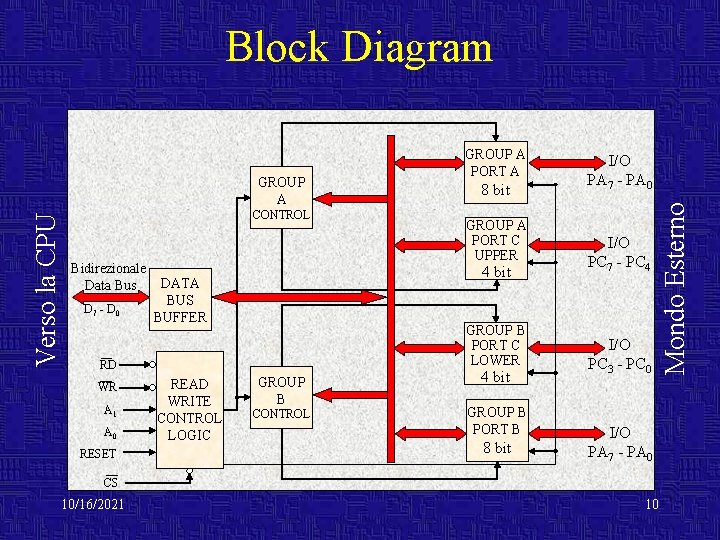

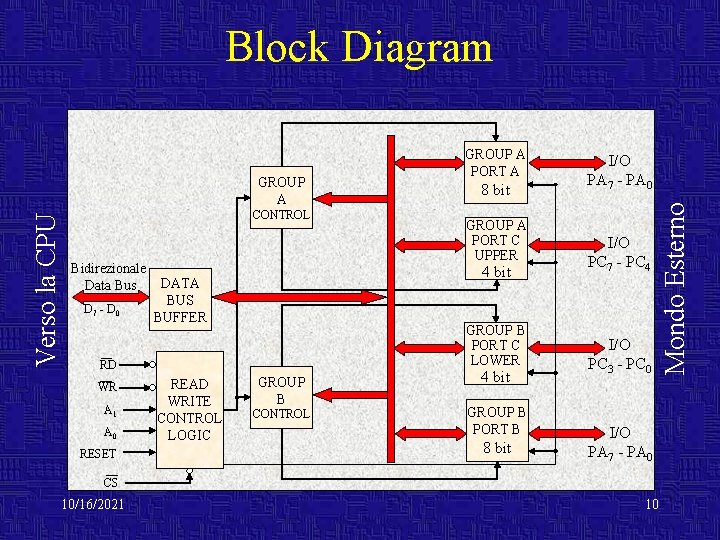

Block Diagram CONTROL Bidirezionale Data Bus D 7 - D 0 A 1 A 0 RESET READ WRITE CONTROL LOGIC GROUP A PORT C UPPER 4 bit DATA BUS BUFFER GROUP B PORT C LOWER RD WR 8 bit GROUP B CONTROL 4 bit GROUP B PORT B 8 bit I/O PA 7 - PA 0 I/O PC 7 - PC 4 I/O PC 3 - PC 0 Mondo Esterno Verso la CPU GROUP A PORT A I/O PA 7 - PA 0 CS 10/16/2021 10

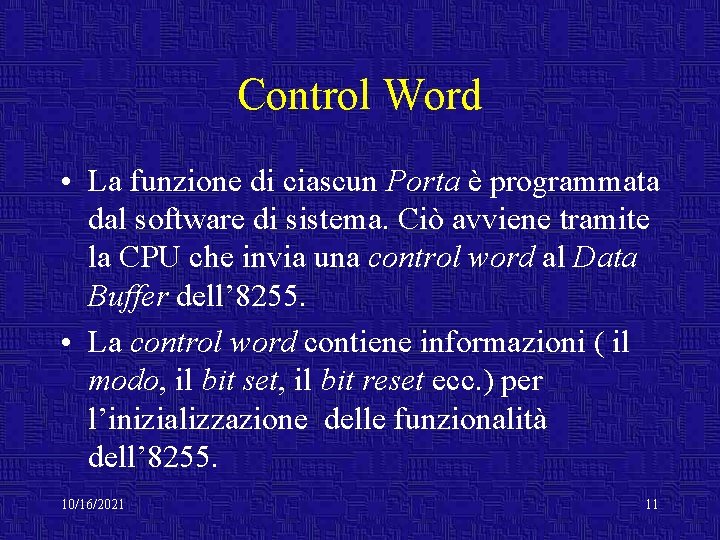

Control Word • La funzione di ciascun Porta è programmata dal software di sistema. Ciò avviene tramite la CPU che invia una control word al Data Buffer dell’ 8255. • La control word contiene informazioni ( il modo, il bit set, il bit reset ecc. ) per l’inizializzazione delle funzionalità dell’ 8255. 10/16/2021 11

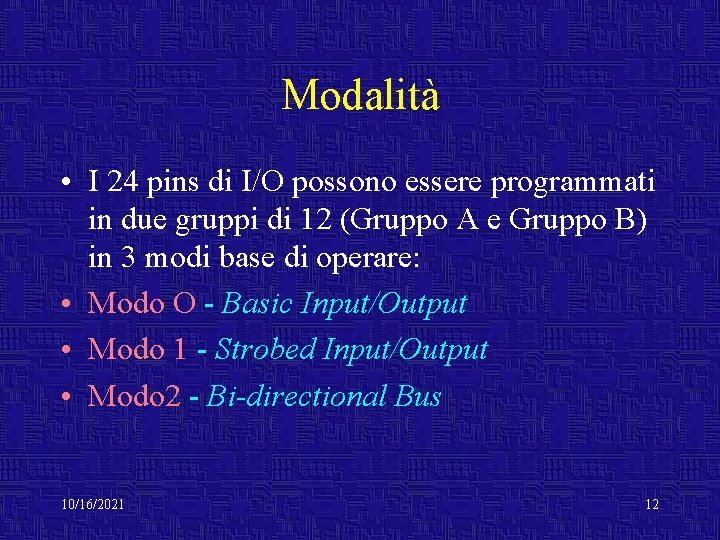

Modalità • I 24 pins di I/O possono essere programmati in due gruppi di 12 (Gruppo A e Gruppo B) in 3 modi base di operare: • Modo O - Basic Input/Output • Modo 1 - Strobed Input/Output • Modo 2 - Bi-directional Bus 10/16/2021 12

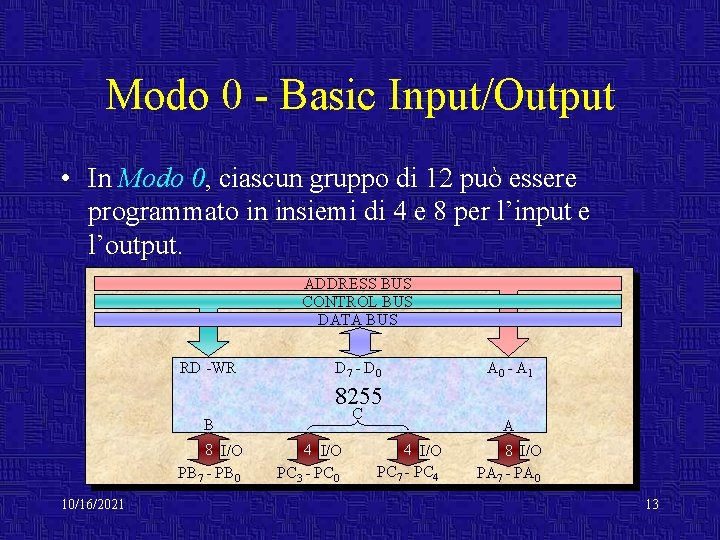

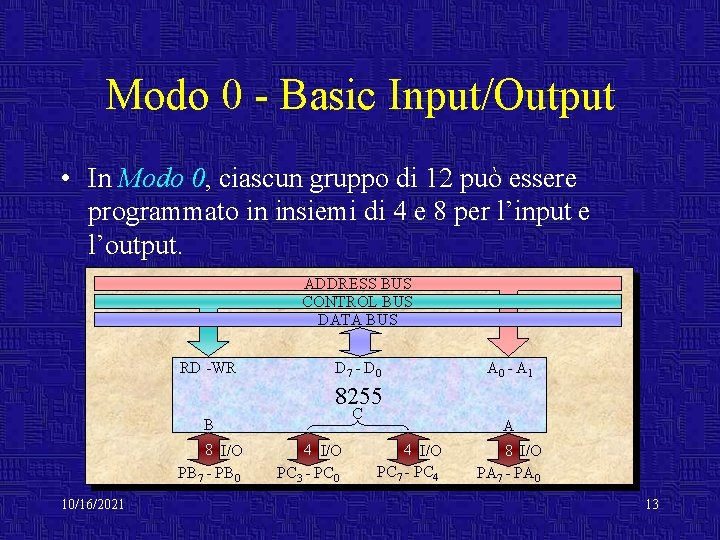

Modo 0 - Basic Input/Output • In Modo 0, ciascun gruppo di 12 può essere programmato in insiemi di 4 e 8 per l’input e l’output. ADDRESS BUS CONTROL BUS DATA BUS RD -WR D 7 - D 0 A 0 - A 1 8255 C B 8 I/O PB 7 - PB 0 10/16/2021 4 I/O PC 3 - PC 0 A 4 I/O PC 7 - PC 4 8 I/O PA 7 - PA 0 13

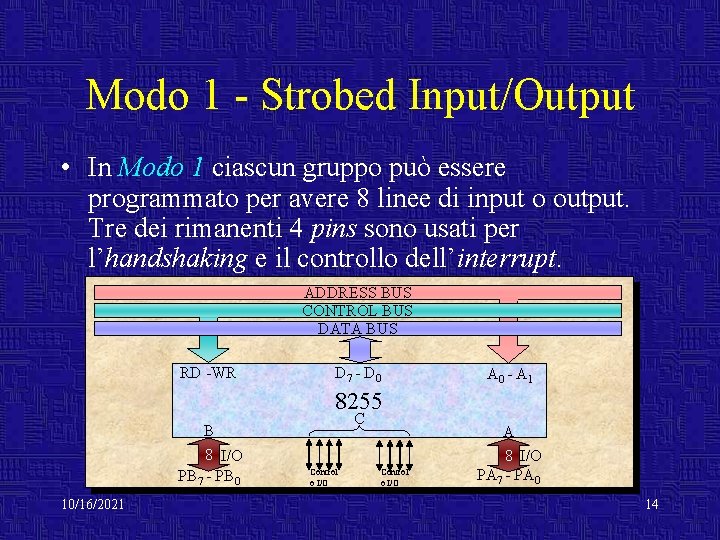

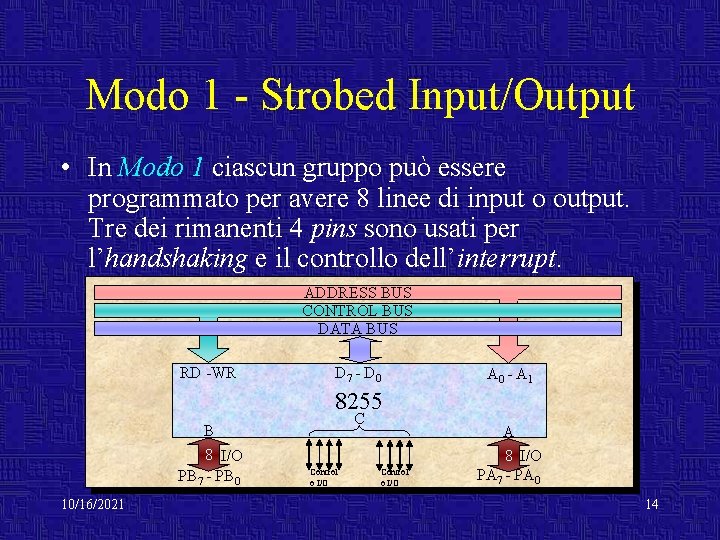

Modo 1 - Strobed Input/Output • In Modo 1 ciascun gruppo può essere programmato per avere 8 linee di input o output. Tre dei rimanenti 4 pins sono usati per l’handshaking e il controllo dell’interrupt. ADDRESS BUS CONTROL BUS DATA BUS RD -WR D 7 - D 0 A 0 - A 1 8255 C B 8 I/O PB 7 - PB 0 10/16/2021 Control o I/O A Control o I/O 8 I/O PA 7 - PA 0 14

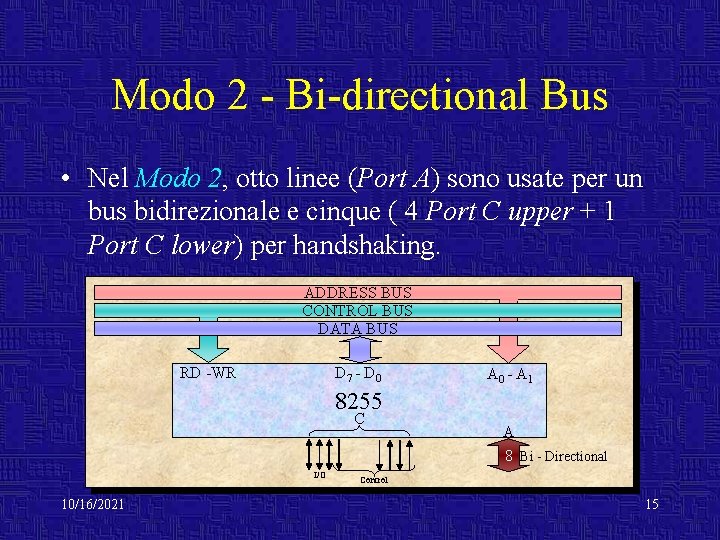

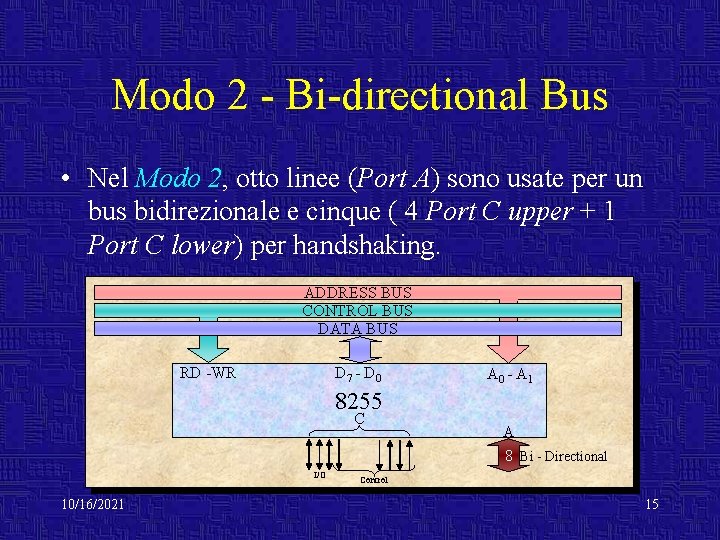

Modo 2 - Bi-directional Bus • Nel Modo 2, otto linee (Port A) sono usate per un bus bidirezionale e cinque ( 4 Port C upper + 1 Port C lower) per handshaking. ADDRESS BUS CONTROL BUS DATA BUS D 7 - D 0 RD -WR A 0 - A 1 8255 C A 8 Bi - Directional I/O 10/16/2021 Control 15

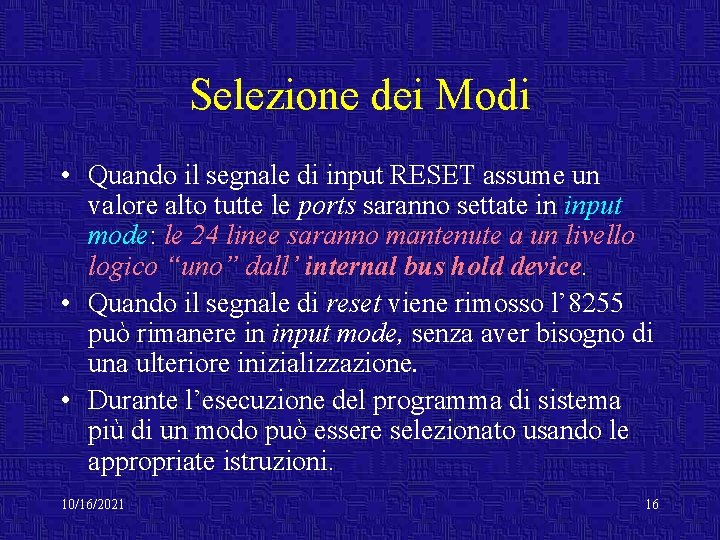

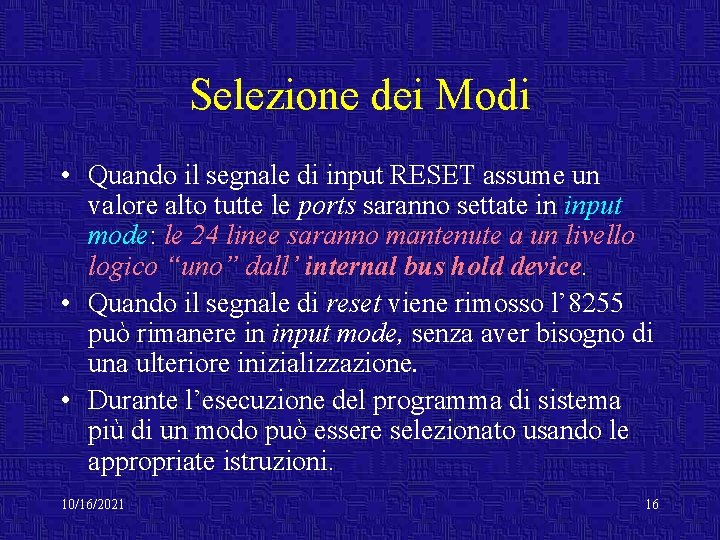

Selezione dei Modi • Quando il segnale di input RESET assume un valore alto tutte le ports saranno settate in input mode: le 24 linee saranno mantenute a un livello logico “uno” dall’ internal bus hold device. • Quando il segnale di reset viene rimosso l’ 8255 può rimanere in input mode, senza aver bisogno di una ulteriore inizializzazione. • Durante l’esecuzione del programma di sistema più di un modo può essere selezionato usando le appropriate istruzioni. 10/16/2021 16

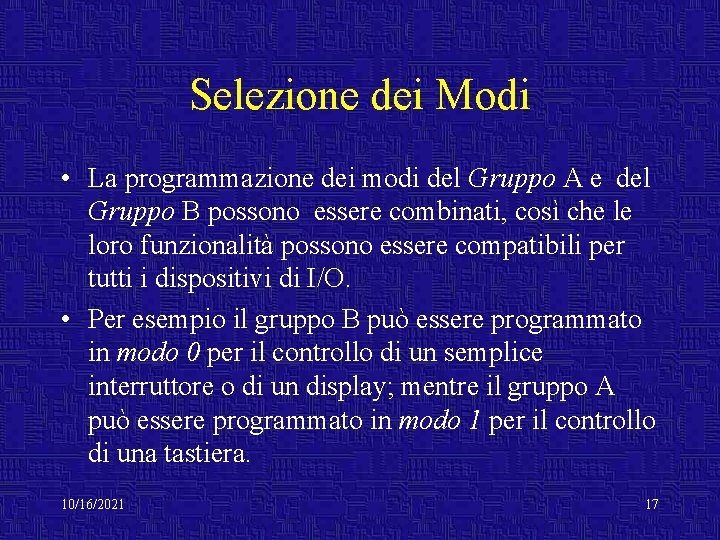

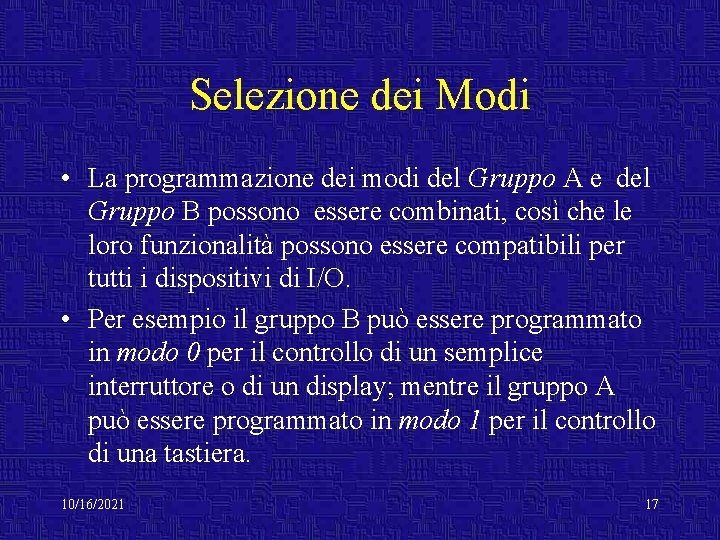

Selezione dei Modi • La programmazione dei modi del Gruppo A e del Gruppo B possono essere combinati, così che le loro funzionalità possono essere compatibili per tutti i dispositivi di I/O. • Per esempio il gruppo B può essere programmato in modo 0 per il controllo di un semplice interruttore o di un display; mentre il gruppo A può essere programmato in modo 1 per il controllo di una tastiera. 10/16/2021 17

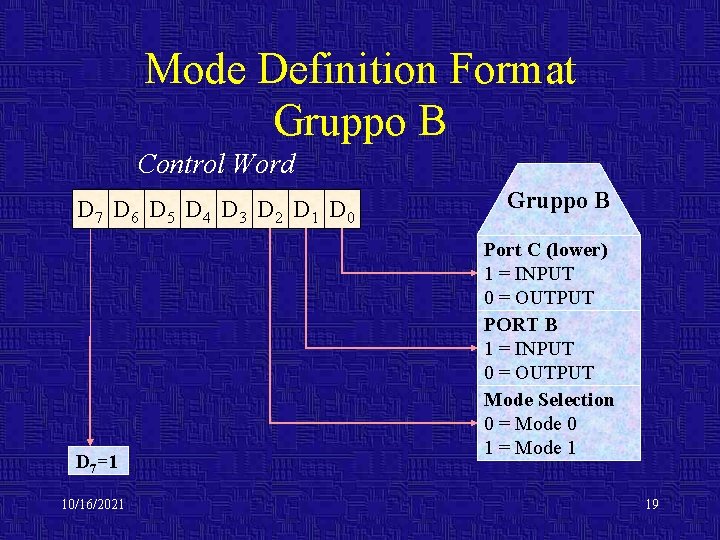

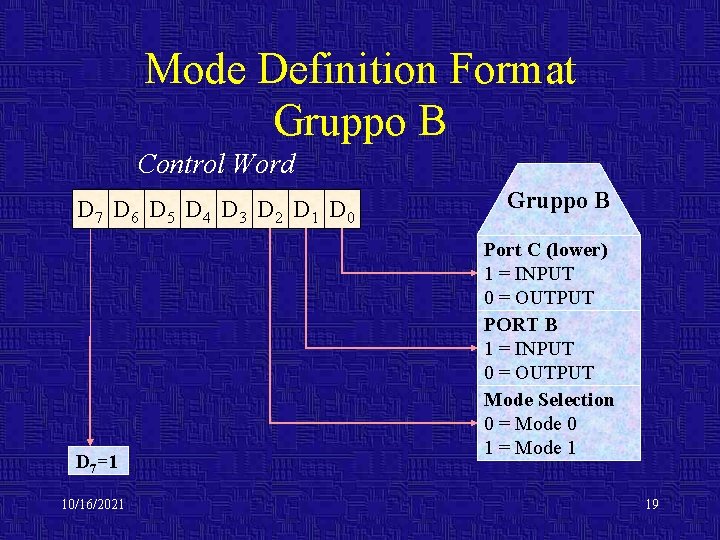

Mode Definition Format • Le funzionalità del gruppo B vengono programmate attraverso i primi tre bit della control word (bit 0, 1, 2). 10/16/2021 18

Mode Definition Format Gruppo B Control Word D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 D 7=1 10/16/2021 Gruppo B Port C (lower) 1 = INPUT 0 = OUTPUT PORT B 1 = INPUT 0 = OUTPUT Mode Selection 0 = Mode 0 1 = Mode 1 19

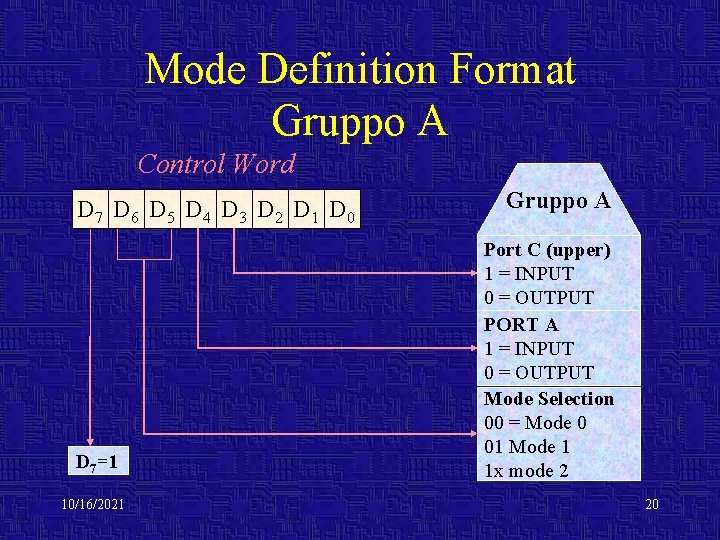

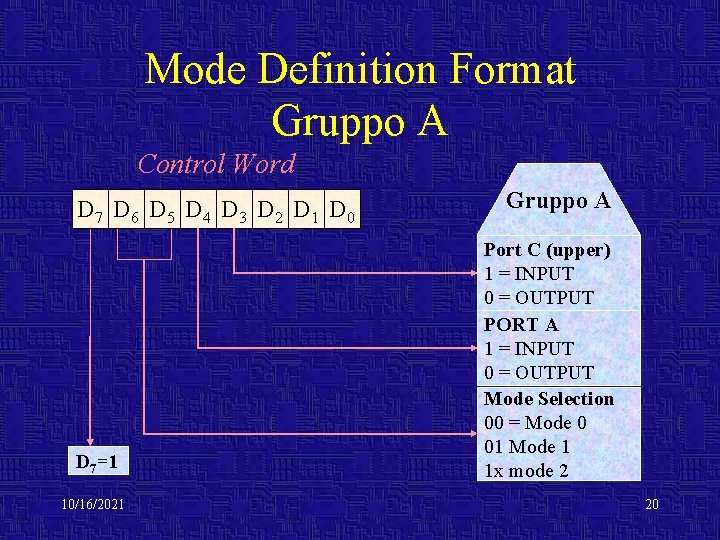

Mode Definition Format Gruppo A Control Word D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 D 7=1 10/16/2021 Gruppo A Port C (upper) 1 = INPUT 0 = OUTPUT PORT A 1 = INPUT 0 = OUTPUT Mode Selection 00 = Mode 0 01 Mode 1 1 x mode 2 20

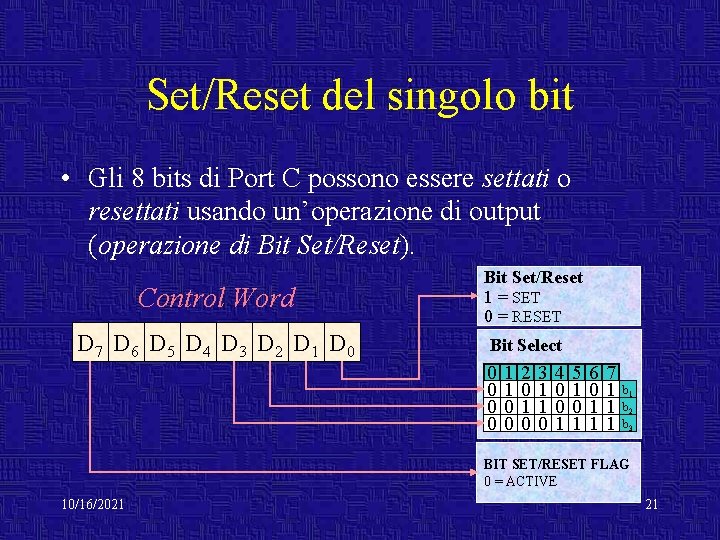

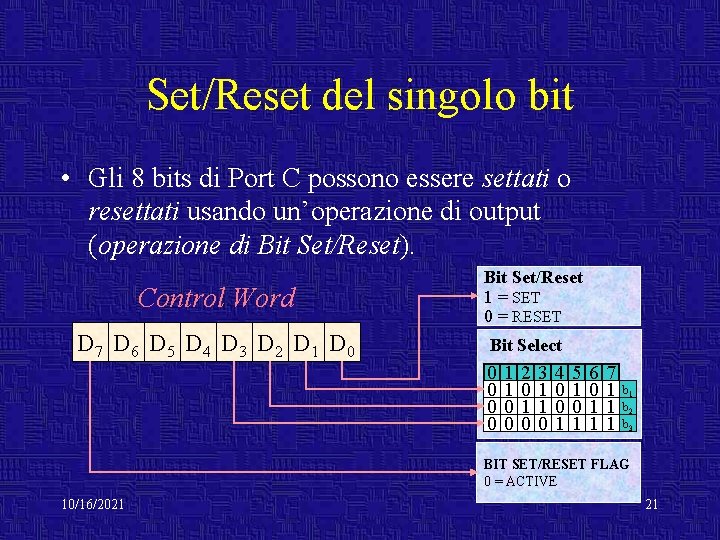

Set/Reset del singolo bit • Gli 8 bits di Port C possono essere settati o resettati usando un’operazione di output (operazione di Bit Set/Reset). Control Word D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 Bit Set/Reset 1 = SET 0 = RESET Bit Select 0 0 1 1 0 0 2 0 1 0 3 1 1 0 4 0 0 1 5 1 0 1 6 0 1 1 7 1 1 1 b 2 b 3 BIT SET/RESET FLAG 0 = ACTIVE 10/16/2021 21

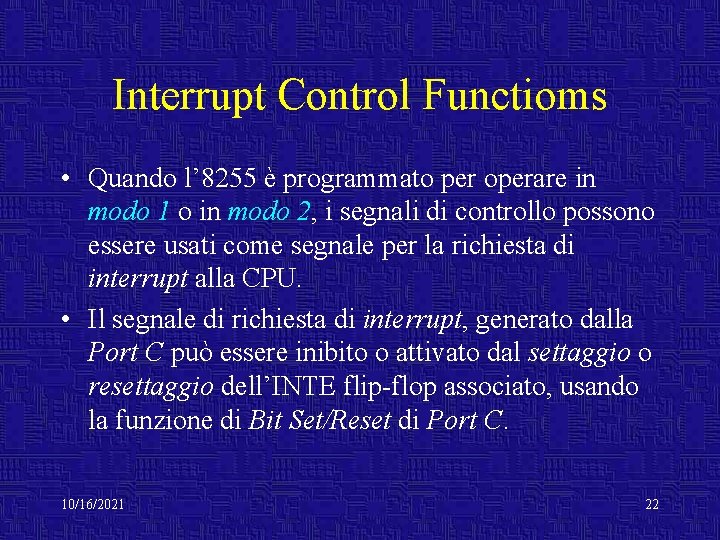

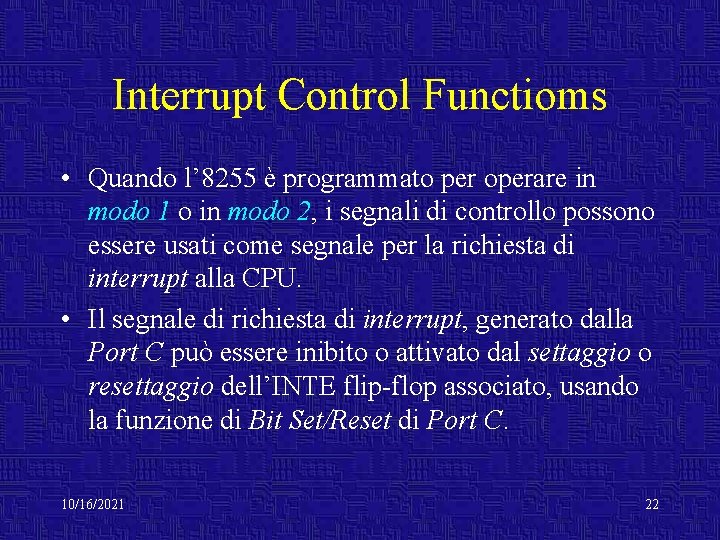

Interrupt Control Functioms • Quando l’ 8255 è programmato per operare in modo 1 o in modo 2, i segnali di controllo possono essere usati come segnale per la richiesta di interrupt alla CPU. • Il segnale di richiesta di interrupt, generato dalla Port C può essere inibito o attivato dal settaggio o resettaggio dell’INTE flip-flop associato, usando la funzione di Bit Set/Reset di Port C. 10/16/2021 22

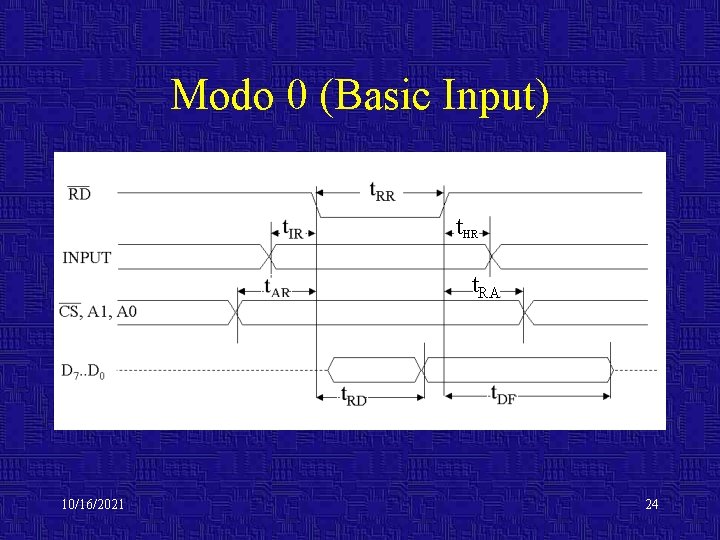

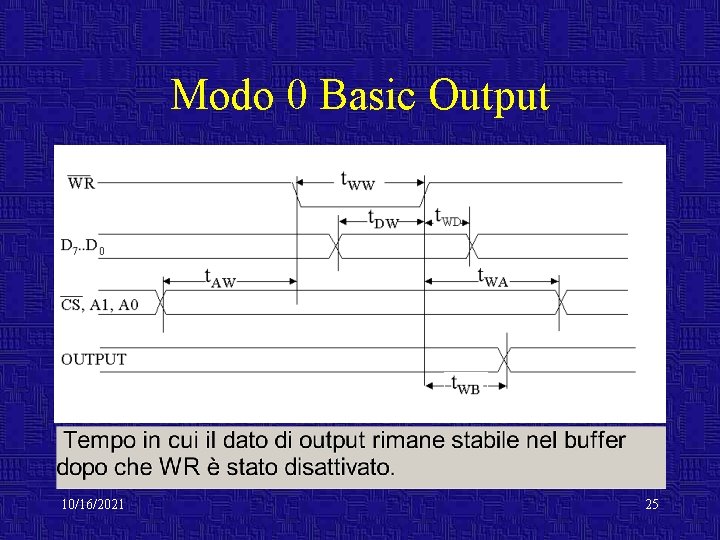

Mode 0 - Basic I/O • Il modo 0 prevede semplici operazioni di input e output per ciascuna delle tre porte. • Non è richiesto l’handshaking, il dato è semplicemente scritto o letto da una specifica porta. 10/16/2021 23

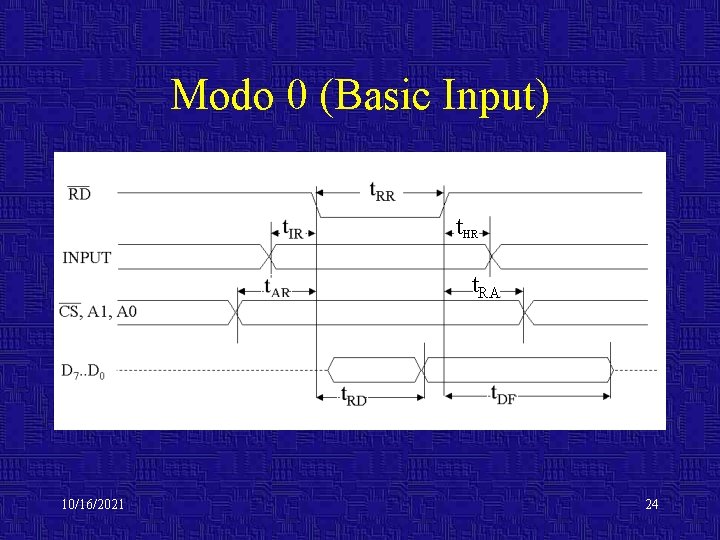

Modo 0 (Basic Input) t. HR t. RA 10/16/2021 24

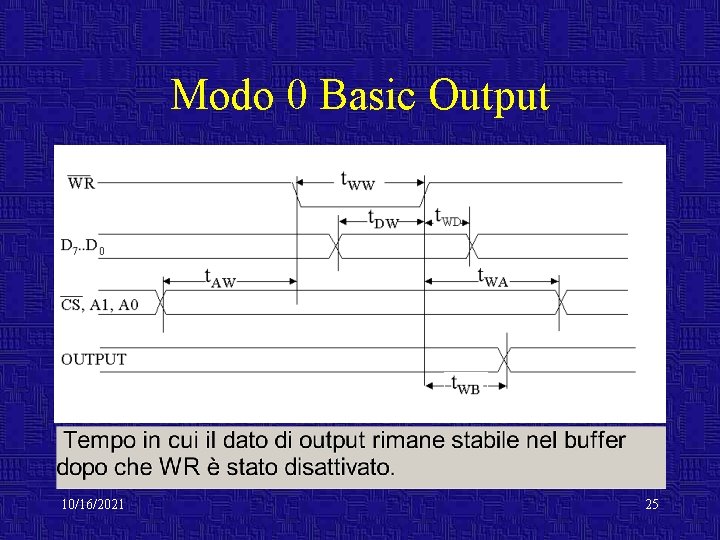

Modo 0 Basic Output 10/16/2021 25

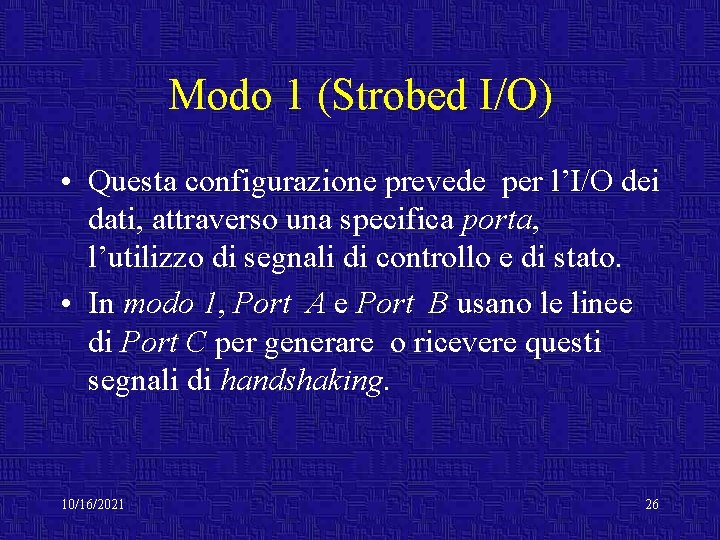

Modo 1 (Strobed I/O) • Questa configurazione prevede per l’I/O dei dati, attraverso una specifica porta, l’utilizzo di segnali di controllo e di stato. • In modo 1, Port A e Port B usano le linee di Port C per generare o ricevere questi segnali di handshaking. 10/16/2021 26

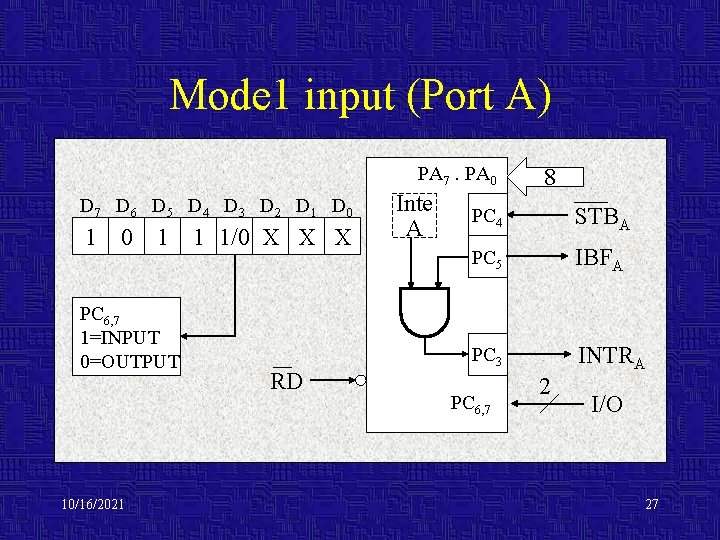

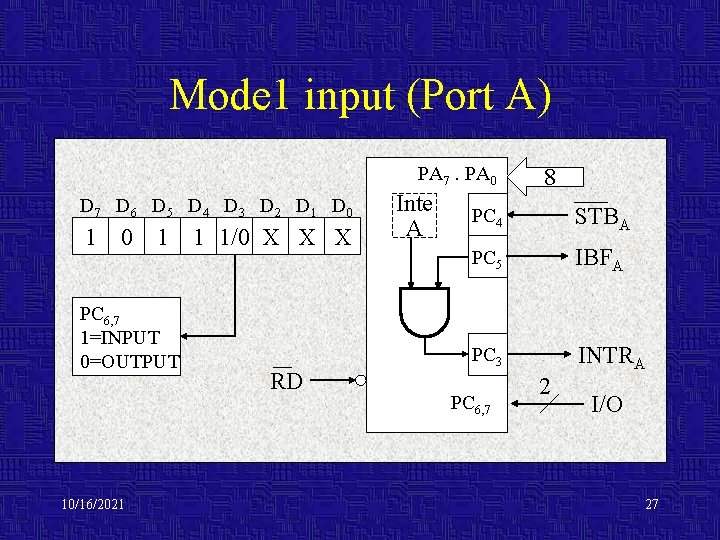

Mode 1 input (Port A) PA 7. PA 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 PC 6, 7 1=INPUT 0=OUTPUT 10/16/2021 1 1/0 X X X RD Inte A 8 PC 4 STBA PC 5 IBFA PC 3 INTRA PC 6, 7 2 I/O 27

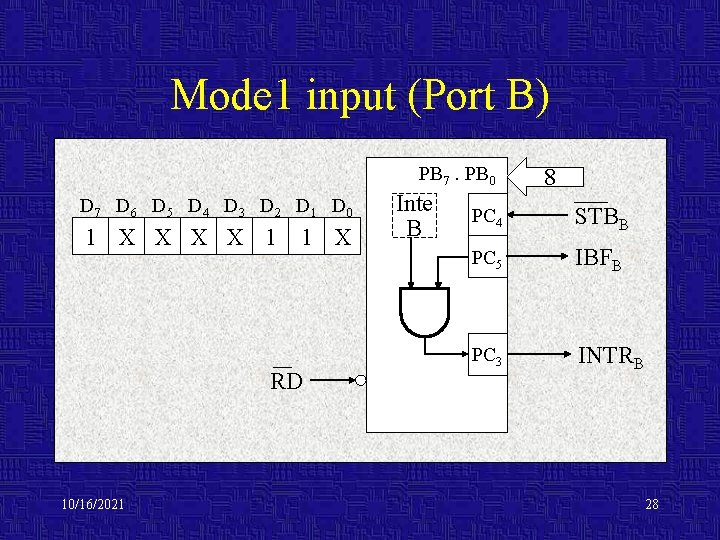

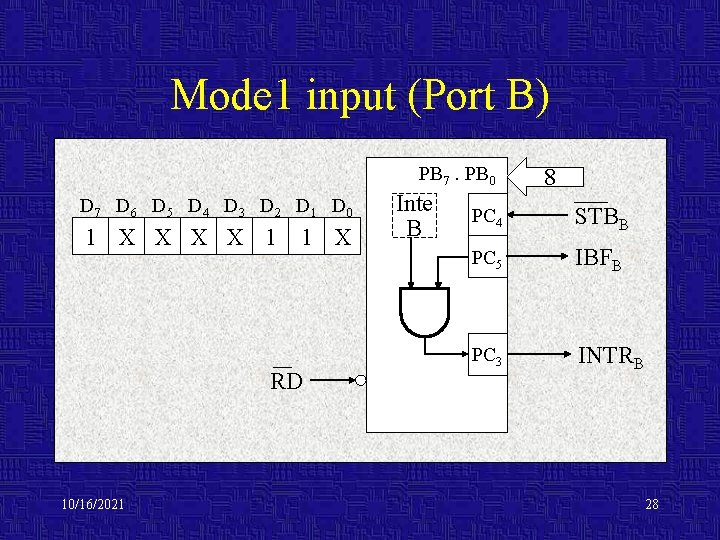

Mode 1 input (Port B) PB 7. PB 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 X X 1 1 X RD 10/16/2021 Inte B 8 PC 4 STBB PC 5 IBFB PC 3 INTRB 28

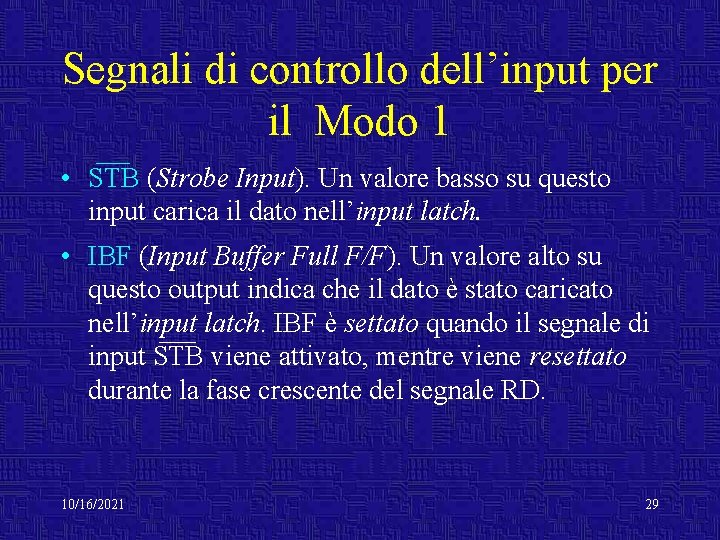

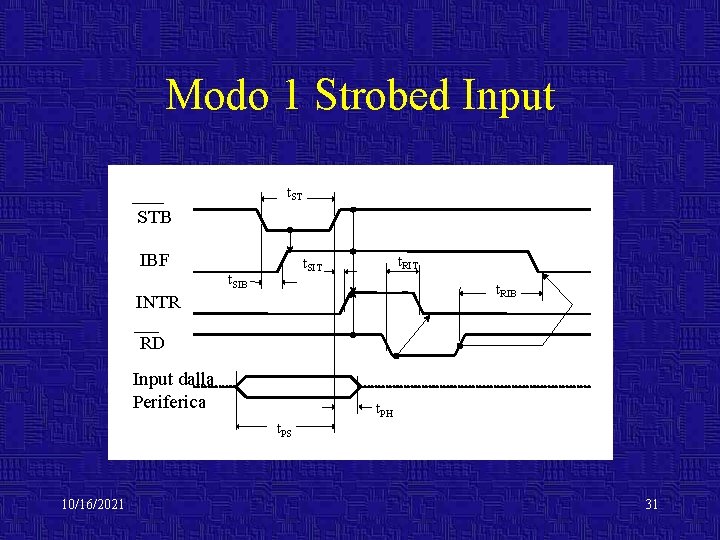

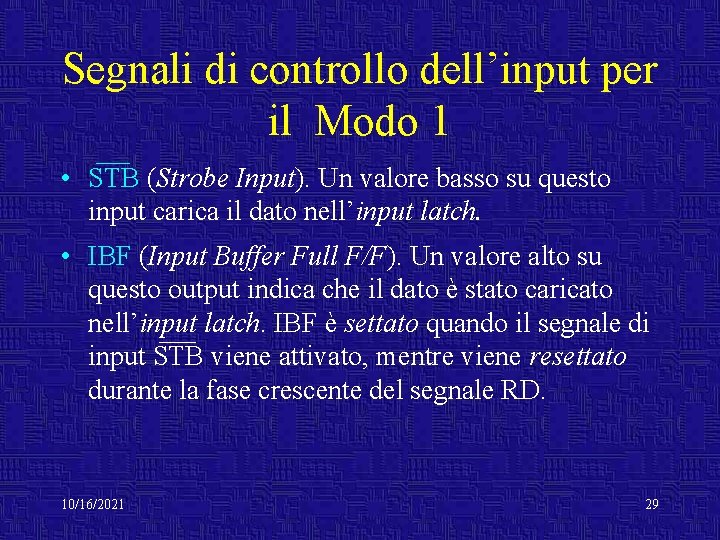

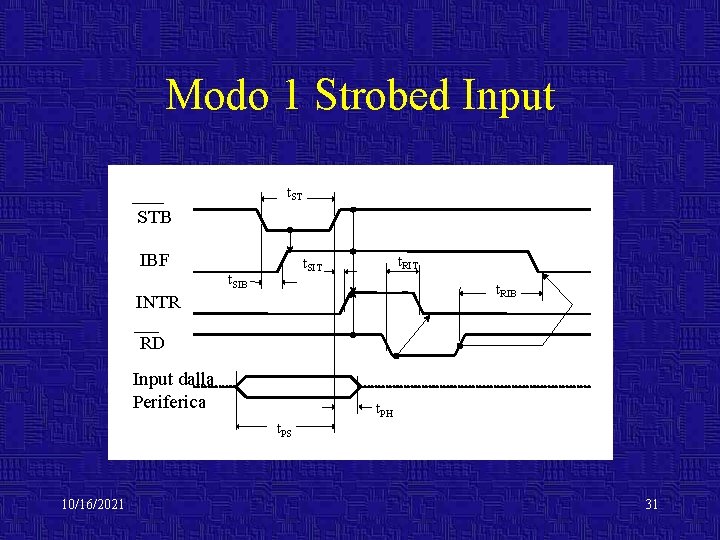

Segnali di controllo dell’input per il Modo 1 • STB (Strobe Input). Un valore basso su questo input carica il dato nell’input latch. • IBF (Input Buffer Full F/F). Un valore alto su questo output indica che il dato è stato caricato nell’input latch. IBF è settato quando il segnale di input STB viene attivato, mentre viene resettato durante la fase crescente del segnale RD. 10/16/2021 29

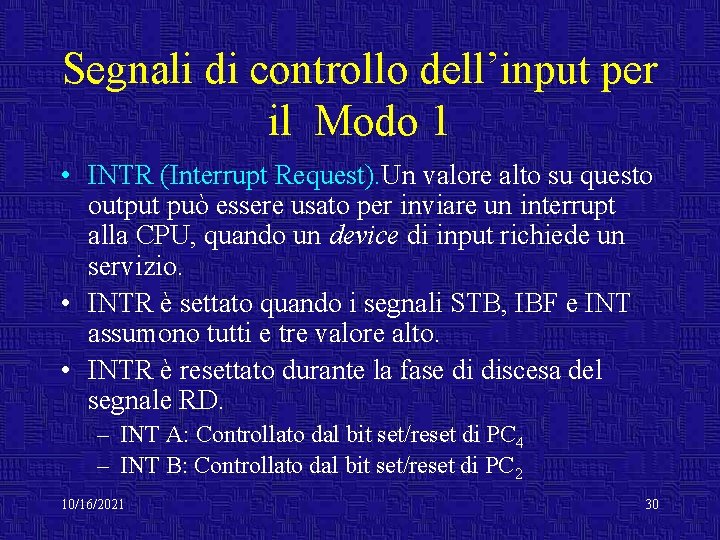

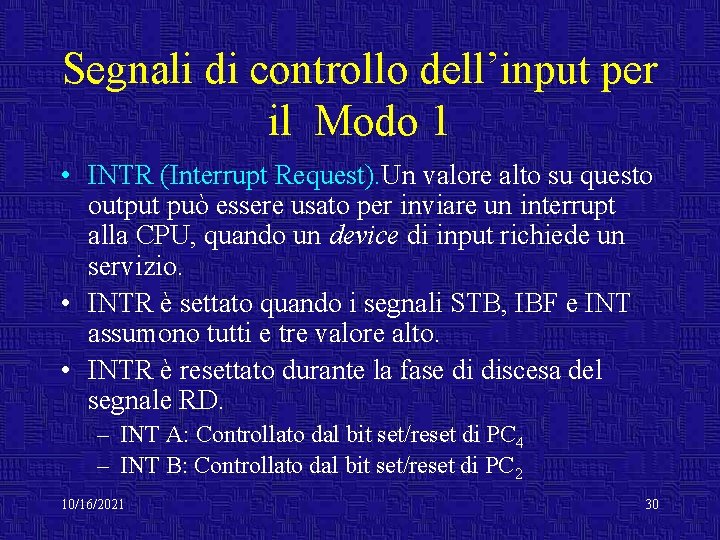

Segnali di controllo dell’input per il Modo 1 • INTR (Interrupt Request). Un valore alto su questo output può essere usato per inviare un interrupt alla CPU, quando un device di input richiede un servizio. • INTR è settato quando i segnali STB, IBF e INT assumono tutti e tre valore alto. • INTR è resettato durante la fase di discesa del segnale RD. – INT A: Controllato dal bit set/reset di PC 4 – INT B: Controllato dal bit set/reset di PC 2 10/16/2021 30

Modo 1 Strobed Input t. ST STB IBF t. RIT t. SIB t. RIB INTR RD Input dalla Periferica t. PH t. PS 10/16/2021 31

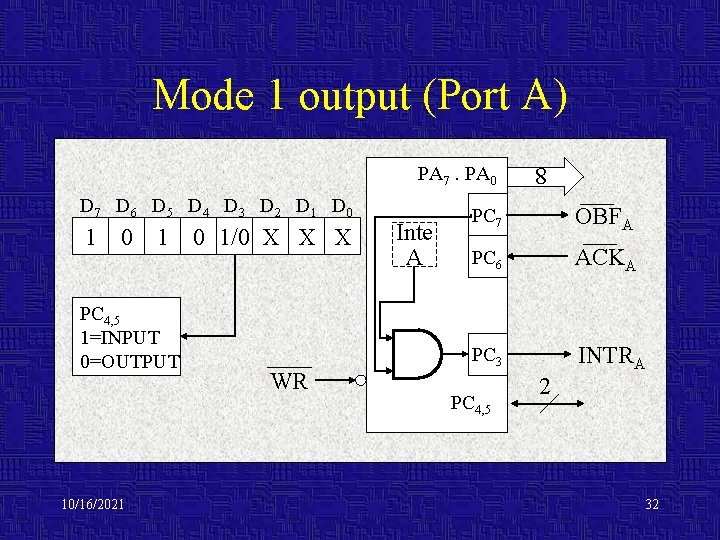

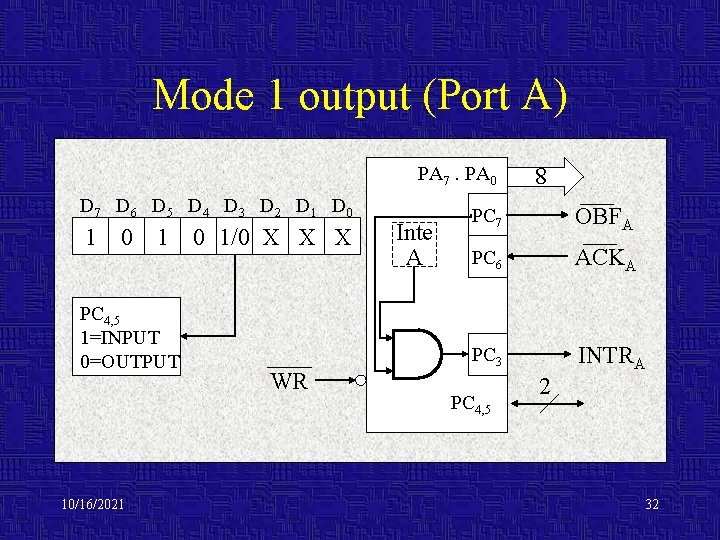

Mode 1 output (Port A) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 PC 4, 5 1=INPUT 0=OUTPUT 10/16/2021 0 1/0 X X X WR Inte A 8 PA 7. PA 0 PC 7 OBFA PC 6 ACKA PC 3 INTRA PC 4, 5 2 32

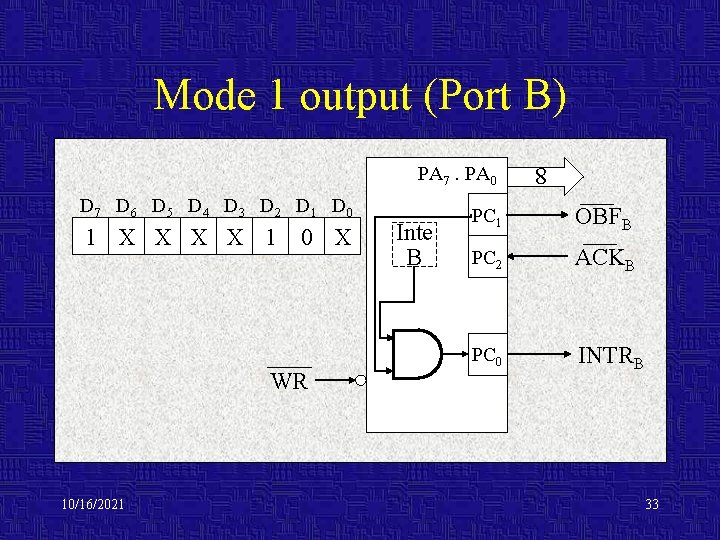

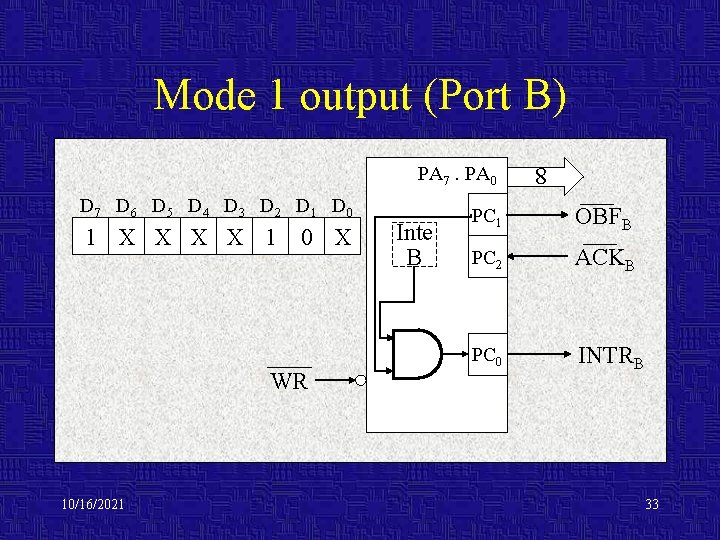

Mode 1 output (Port B) D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 X X 1 0 X WR 10/16/2021 Inte B 8 PA 7. PA 0 PC 1 OBFB PC 2 ACKB PC 0 INTRB 33

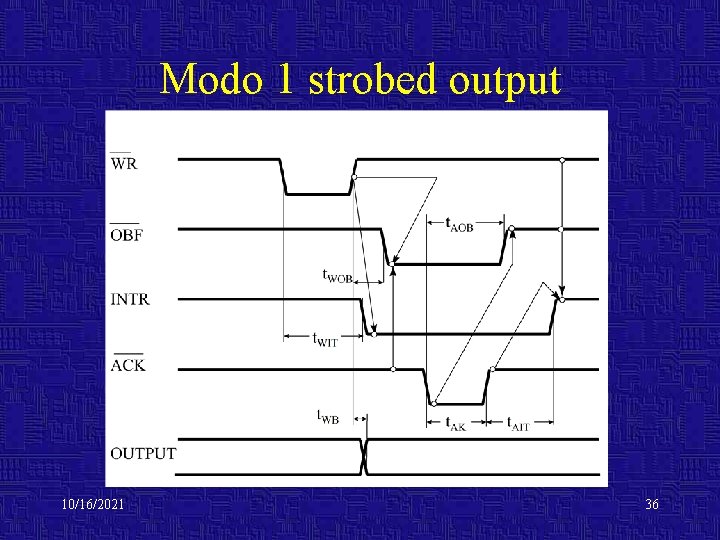

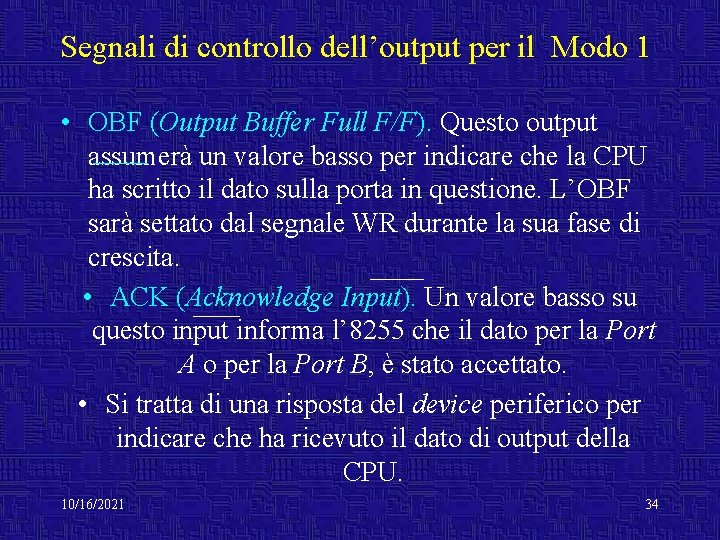

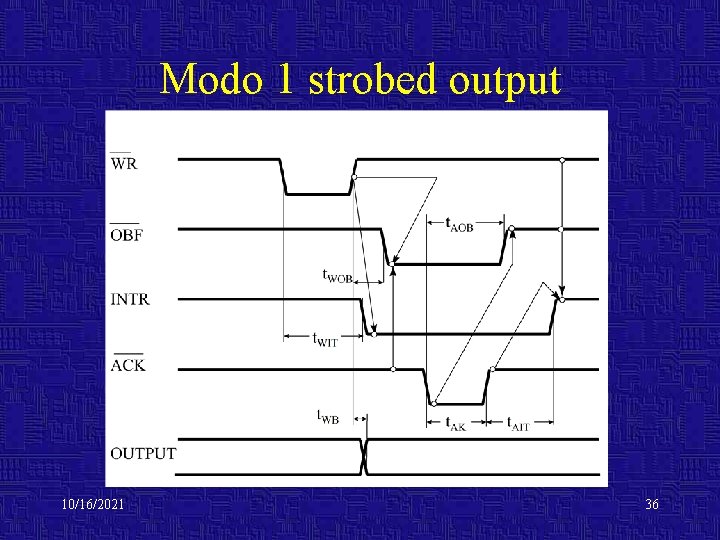

Segnali di controllo dell’output per il Modo 1 • OBF (Output Buffer Full F/F). Questo output assumerà un valore basso per indicare che la CPU ha scritto il dato sulla porta in questione. L’OBF sarà settato dal segnale WR durante la sua fase di crescita. • ACK (Acknowledge Input). Un valore basso su questo input informa l’ 8255 che il dato per la Port A o per la Port B, è stato accettato. • Si tratta di una risposta del device periferico per indicare che ha ricevuto il dato di output della CPU. 10/16/2021 34

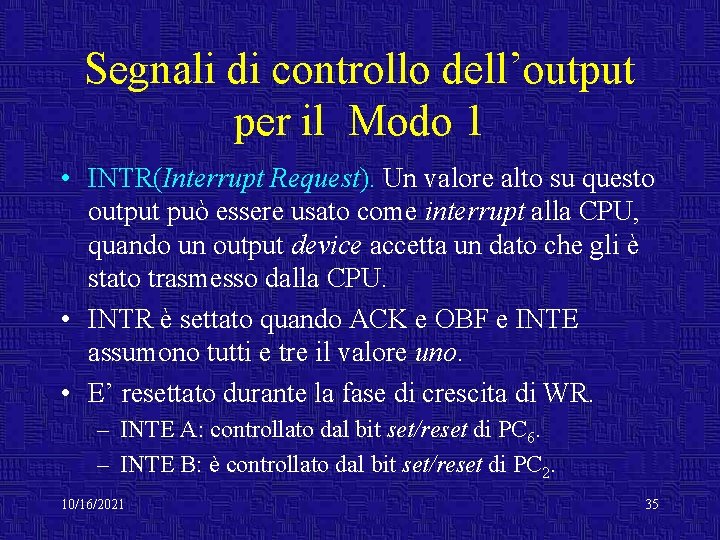

Segnali di controllo dell’output per il Modo 1 • INTR(Interrupt Request). Un valore alto su questo output può essere usato come interrupt alla CPU, quando un output device accetta un dato che gli è stato trasmesso dalla CPU. • INTR è settato quando ACK e OBF e INTE assumono tutti e tre il valore uno. • E’ resettato durante la fase di crescita di WR. – INTE A: controllato dal bit set/reset di PC 6. – INTE B: è controllato dal bit set/reset di PC 2. 10/16/2021 35

Modo 1 strobed output 10/16/2021 36

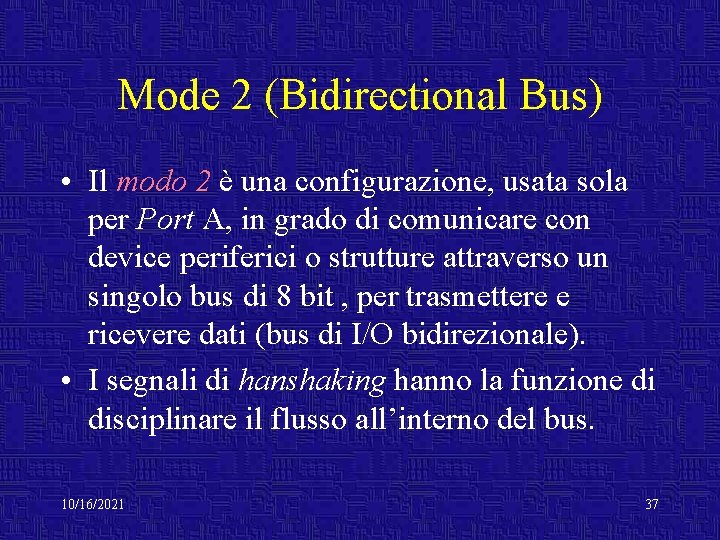

Mode 2 (Bidirectional Bus) • Il modo 2 è una configurazione, usata sola per Port A, in grado di comunicare con device periferici o strutture attraverso un singolo bus di 8 bit , per trasmettere e ricevere dati (bus di I/O bidirezionale). • I segnali di hanshaking hanno la funzione di disciplinare il flusso all’interno del bus. 10/16/2021 37

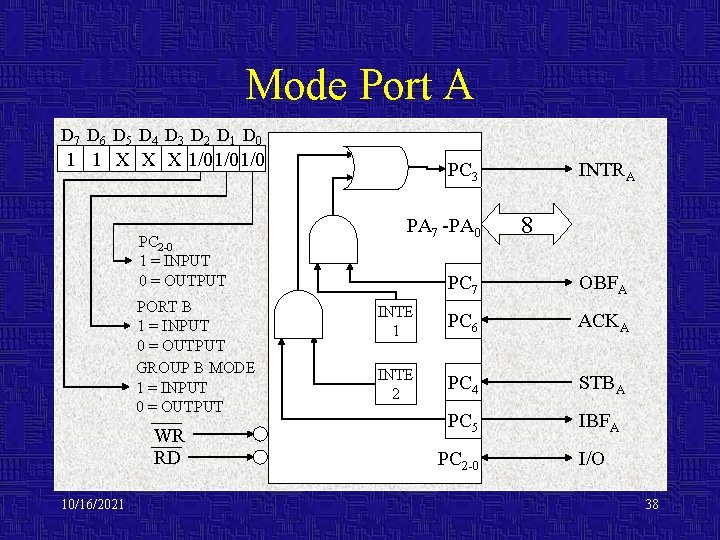

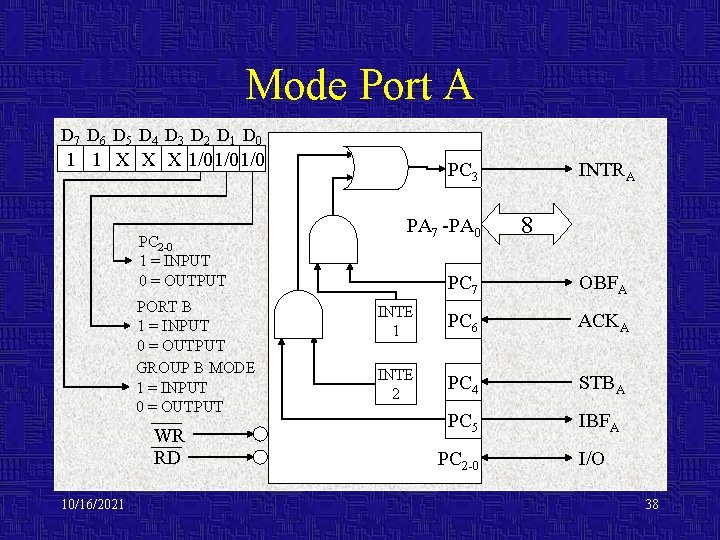

Mode Port A D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 1 1 X X X 1/01/01/0 PC 2 -0 1 = INPUT 0 = OUTPUT PORT B 1 = INPUT 0 = OUTPUT GROUP B MODE 1 = INPUT 0 = OUTPUT WR RD 10/16/2021 INTRA PC 3 PA 7 -PA 0 8 PC 7 OBFA INTE 1 PC 6 ACKA INTE 2 PC 4 STBA PC 5 IBFA PC 2 -0 I/O 38

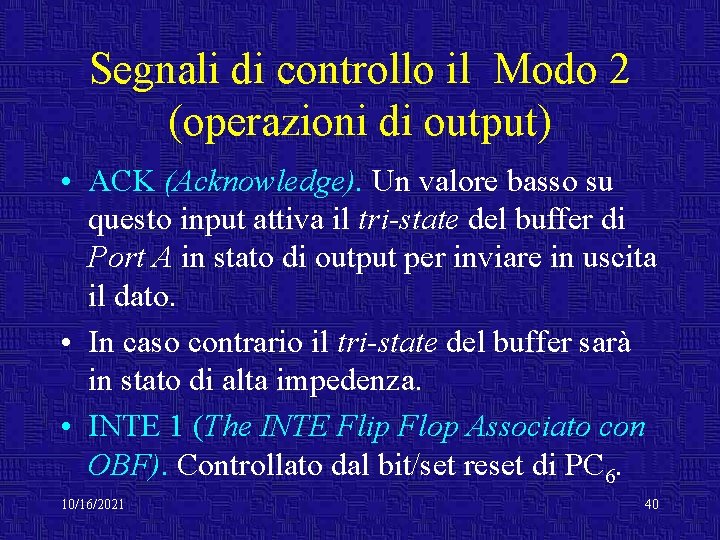

Segnali di controllo il Modo 2 (operazioni di output) • INTR (Interrupt request). Un valore alto su questo output può essere usato per inviare un interrupt alla CPU per richiedere operazioni di input o di output. • OBF (Output Butter Full). Un valore basso su questo input indica che la CPU ha scritto il dato sulla Port A 10/16/2021 39

Segnali di controllo il Modo 2 (operazioni di output) • ACK (Acknowledge). Un valore basso su questo input attiva il tri-state del buffer di Port A in stato di output per inviare in uscita il dato. • In caso contrario il tri-state del buffer sarà in stato di alta impedenza. • INTE 1 (The INTE Flip Flop Associato con OBF). Controllato dal bit/set reset di PC 6. 10/16/2021 40

Segnali di controllo il Modo 2 (operazioni di input) • STB (Strobe Input). Un valore basso su questo input carica il dato nel input latch. • IBF (Input Buffer Full F/F). Un valore alto su questo output indica che il dato è stato caricato sul latch di input. • INTE 2 (The INTE Flip-Flop Associato with IBF). Controllato dal bit set/reset di PC 4. 10/16/2021 41

Modo 2 10/16/2021 42