Signal Processing Using Digital Technology Jeremy Barsten Jeremy

Signal Processing Using Digital Technology Jeremy Barsten Jeremy Stockwell December 10, 2002 Advisors: Dr. Thomas Stewart Dr. Vinod Prasad

Digital Signal Processor n n Project Description Preliminary Work n n n Research Design Standards and Patents Goals Schedule

Project Description n n All purpose digital signal processor using FPGA/VHDL and ASIC/VLSI technology. Useable for a variety of applications: n n n Audio and Video Cellular Technology Adapted depending on the application.

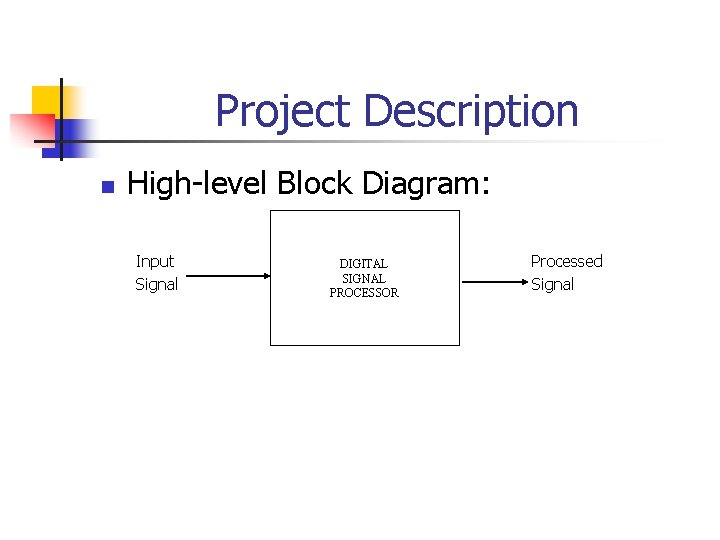

Project Description n High-level Block Diagram: Input Signal DIGITAL SIGNAL PROCESSOR Processed Signal

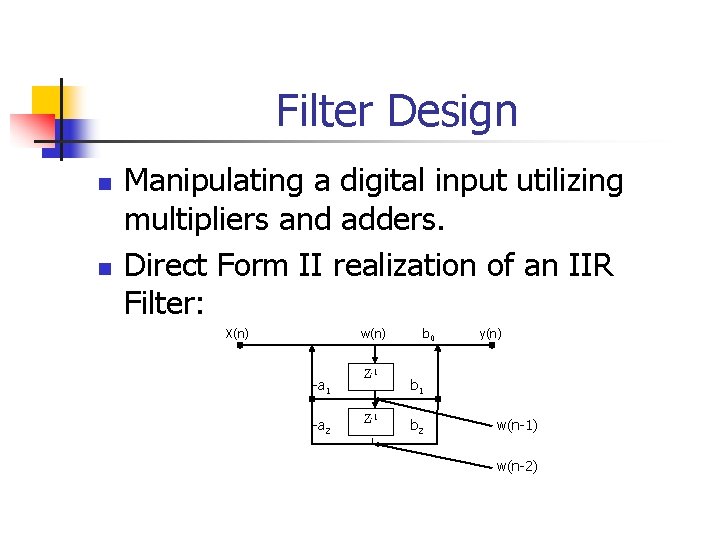

Filter Design n n Manipulating a digital input utilizing multipliers and adders. Direct Form II realization of an IIR Filter: X(n) w(n) -a 1 -a 2 Z-1 b 0 y(n) b 1 b 2 w(n-1) w(n-2)

Signal Converters n n n Each signal will be analog in nature. Requires an analog-to-digital converter at the input stage and a digital-toanalog converter at the output stage. Type of converter will be determined later.

Adder and Multiplier n n n Any basic signal processor consists of different stages of addition and multiplication. A n-bit by n-bit multiplication will take place and result in a 2*n-bit value. This answer will be added to previous values stored in a data register (discussed later).

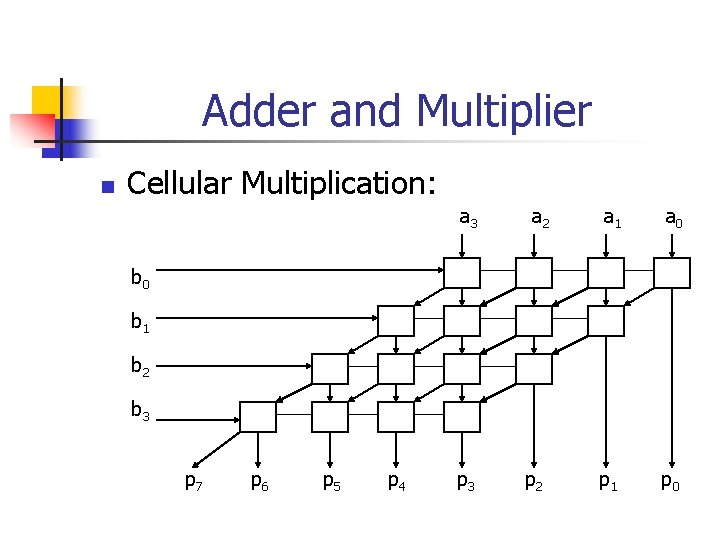

Adder and Multiplier n Cellular Multiplication: a 3 a 2 a 1 a 0 p 1 p 0 b 1 b 2 b 3 p 7 p 6 p 5 p 4 p 3 p 2

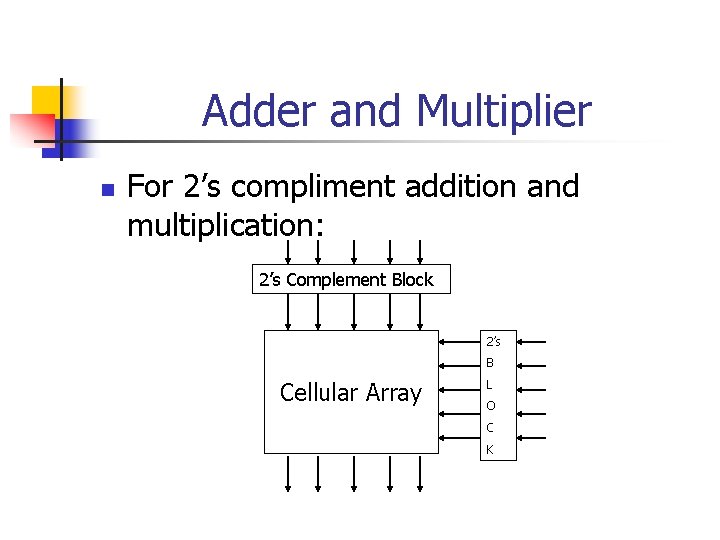

Adder and Multiplier n For 2’s compliment addition and multiplication: 2’s Complement Block 2’s B Cellular Array L O C K

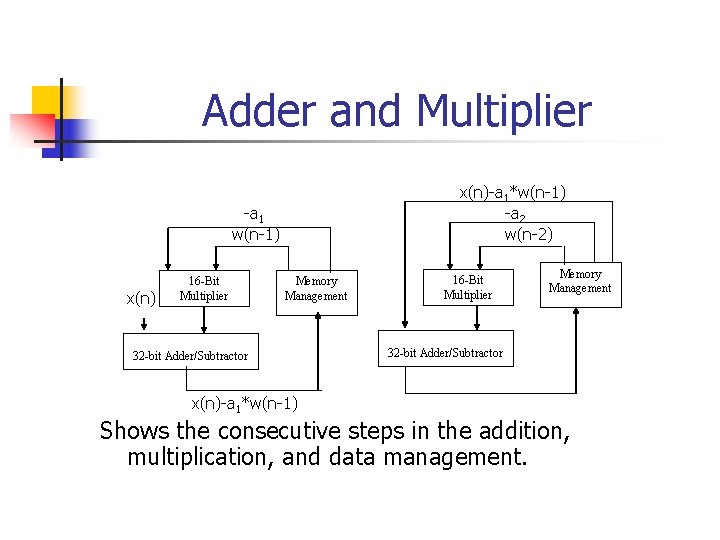

Adder and Multiplier x(n)-a 1*w(n-1) -a 2 w(n-2) -a 1 w(n-1) x(n) 16 -Bit Multiplier Memory Management 32 -bit Adder/Subtractor x(n)-a 1*w(n-1) Shows the consecutive steps in the addition, multiplication, and data management.

Data Management n n n Need to store old calculated values for later use. Need a “shift-and-store” type of data management. Will deliver the correct data at the appropriate time.

Data Management n n n The possibility of overflow exists in the addition and multiplication stage. For this reason, a truncation circuit is needed to control and adjust the value of the adder/multiplier circuit. Will also use truncation before sending out the final signal.

Preliminary Work Investigation of Xilinx compiler. n Ripple carry adder v. Carry look ahead adder. n Parallel multiplier v. Serial multiplier. n

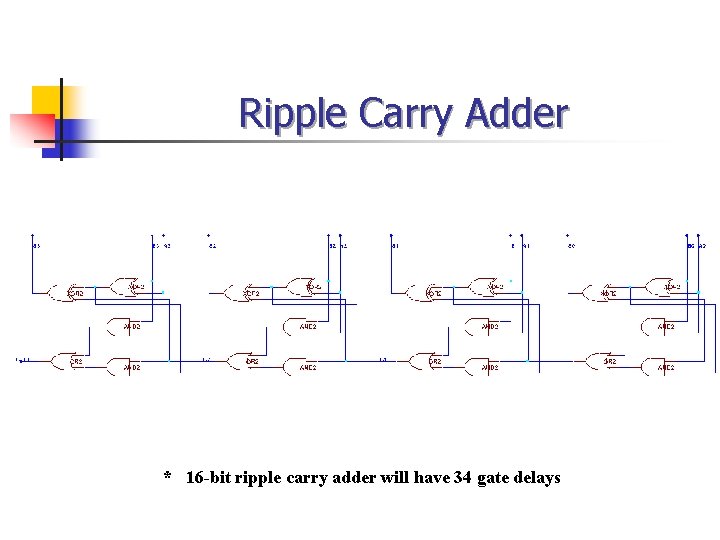

Ripple Carry Adder * 16 -bit ripple carry adder will have 34 gate delays

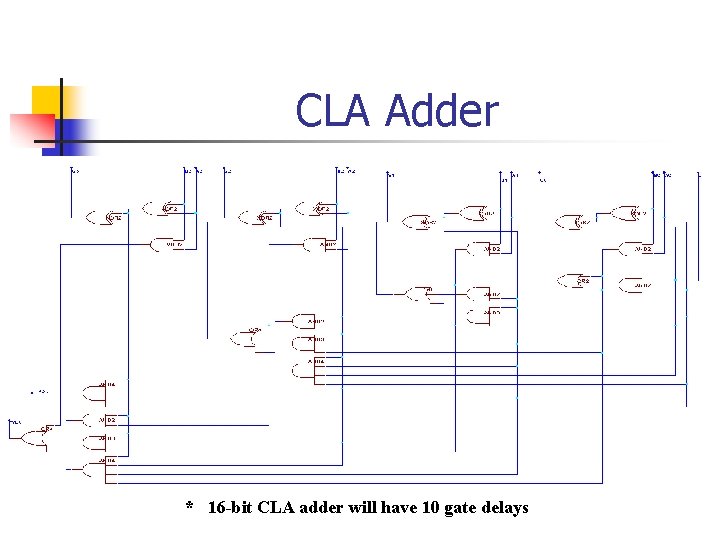

CLA Adder * 16 -bit CLA adder will have 10 gate delays

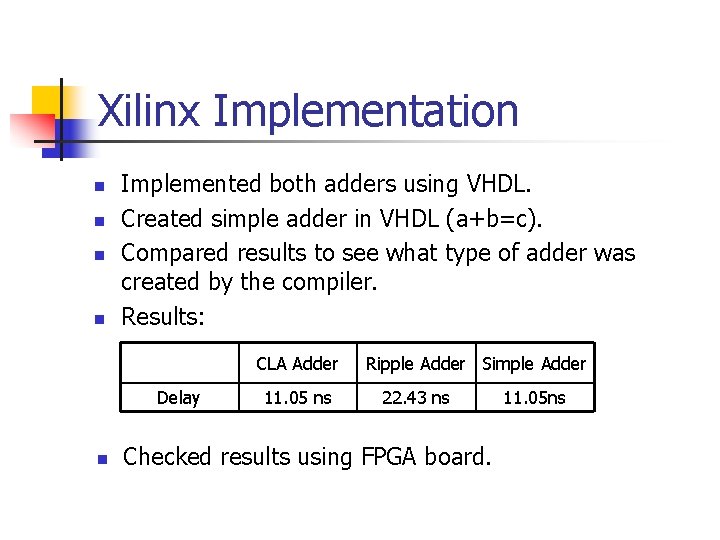

Xilinx Implementation n n Implemented both adders using VHDL. Created simple adder in VHDL (a+b=c). Compared results to see what type of adder was created by the compiler. Results: CLA Adder Delay n 11. 05 ns Ripple Adder Simple Adder 22. 43 ns Checked results using FPGA board. 11. 05 ns

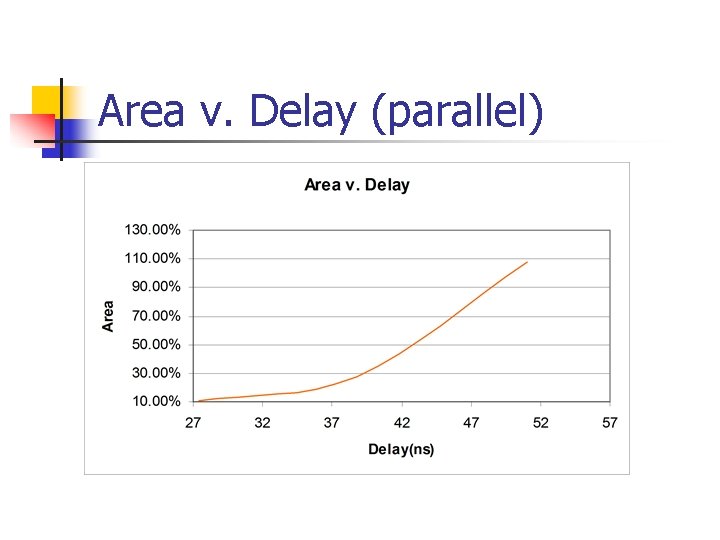

Multiplier Advantages and disadvantages of using a parallel multiplier v. a serial multiplier. n Investigate the feasibility of using a Parallel Multiplier. n Speed v. Area n

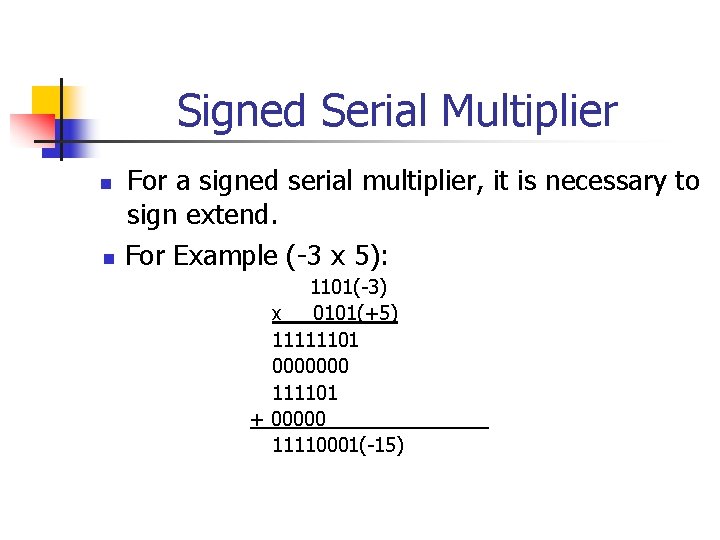

Signed Serial Multiplier n n For a signed serial multiplier, it is necessary to sign extend. For Example (-3 x 5): 1101(-3) x 0101(+5) 11111101 0000000 111101 + 00000 11110001(-15)

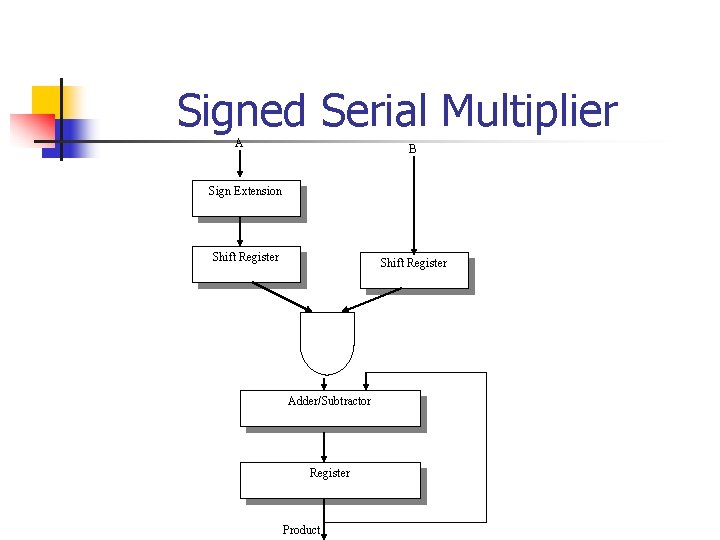

Signed Serial Multiplier A B Sign Extension Shift Register Adder/Subtractor Register Product

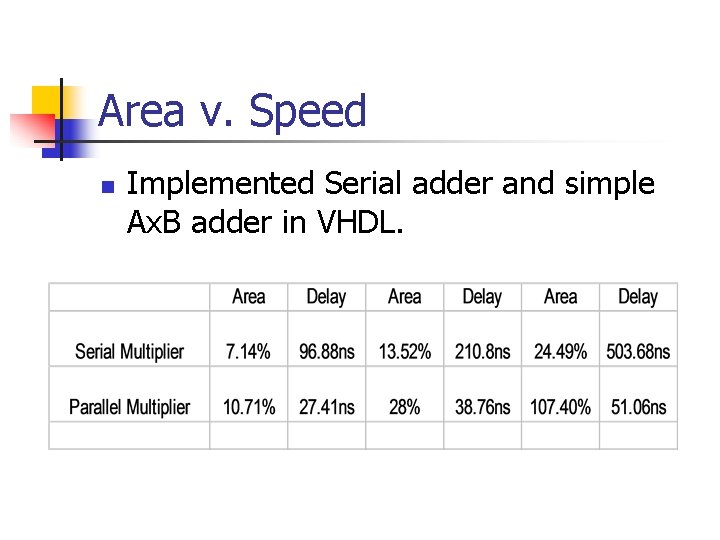

Area v. Speed n Implemented Serial adder and simple Ax. B adder in VHDL.

Area v. Delay (serial)

Area v. Delay (parallel)

Other Multiplier Options n n It is possible to use a combination of parallel and serial multipliers. For example it is possible to use two 8 bit parallel multipliers in series which will double the delay but will save space.

Standards and Patents n n n Searched the Internet for standards and patents on digital signal processors. Many of the standards were application specific. Could not really find specific standards on digital signal processors.

Hardware and Software Programs n n n Xilinx Foundation Software Leonardo Spectrum L-Edit Pro v 8. 2 PSpice Circuit Simulation Xilinx XC 4005 e. PC 84 FPGA Board A/D and D/A converters

Project Goals n n n Determine best trade-off between size and speed for the adder/multiplier circuit. VLSI implementation of a 4 -bit adder and multiplier. Determine the number of bits used in our processor to ensure stability. Complete data management and truncation block of the processor. Decide on specific application.

Project Schedule n January/February: n n n March: n n Determine specific application and design the appropriate filter. April: n n n Complete adder/multiplier in VHDL and implement on the FPGA board. Complete VLSI design of adder/multiplier circuit. Complete data management and truncation block. Implement entire design on FPGA board and troubleshoot any errors that arise. May: n Prepare final presentation and possibly present at Student Expo.

Signal Processing Using Digital Technology Jeremy Barsten Jeremy Stockwell December 10, 2002 Advisors: Dr. Thomas Stewart Dr. Vinod Prasad

- Slides: 28