Signal Processing for Nuclear Detectors Dipartimento di Fisica

- Slides: 27

Signal Processing for Nuclear Detectors Dipartimento di Fisica Generale M. P. Bussa, L. Ferrero, A. Grasso, M. Greco, M. Maggiora, Diego ALBERTO D. Alberto Bavarian Forest, 24 April 2009

Outline Introduction Simulated Transmission Chain Simulated WGN Noise SNR and Peak Distortion Simulation Filtering Results Towards FPGA Our Real Transmission Chain Future works D. Alberto Bavarian Forest, 24 April 2009

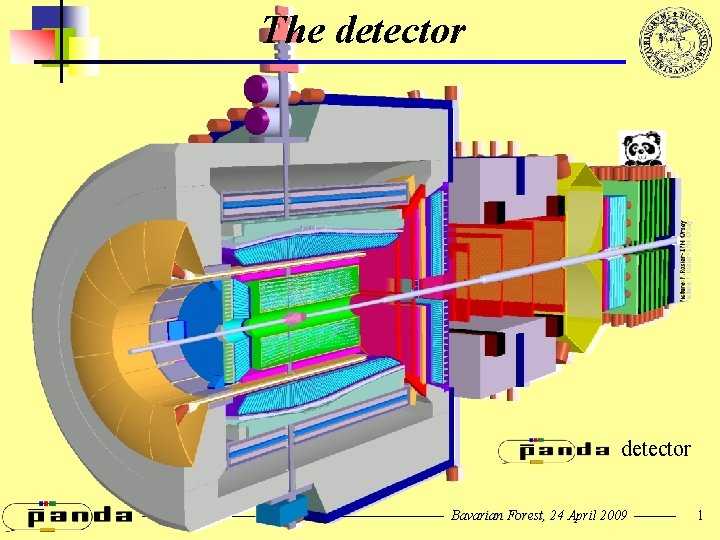

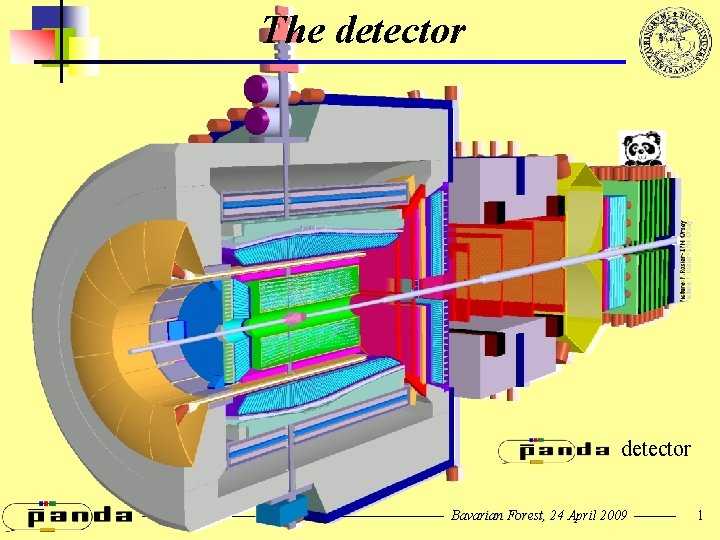

The detector D. Alberto Bavarian Forest, 24 April 2009 1

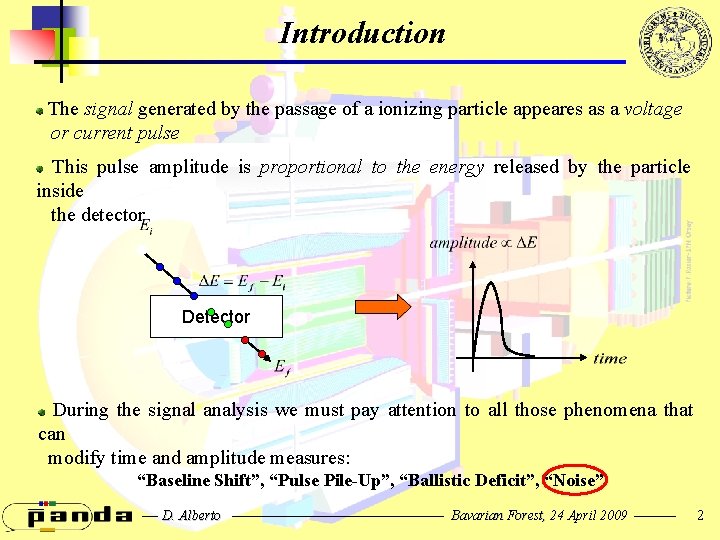

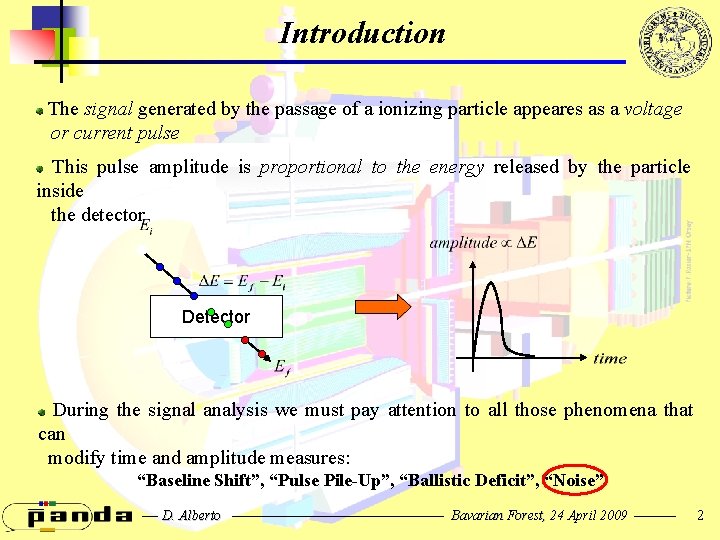

Introduction The signal generated by the passage of a ionizing particle appeares as a voltage or current pulse This pulse amplitude is proportional to the energy released by the particle inside the detector During the signal analysis we must pay attention to all those phenomena that can modify time and amplitude measures: “Baseline Shift”, “Pulse Pile-Up”, “Ballistic Deficit”, “Noise” D. Alberto Bavarian Forest, 24 April 2009 2

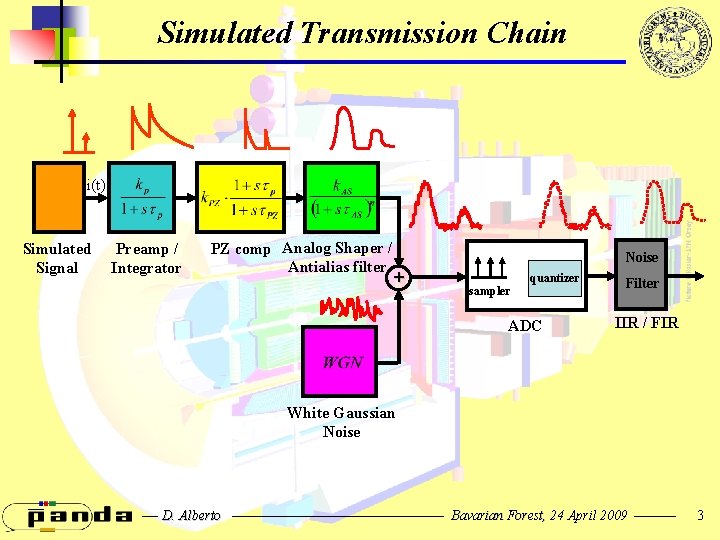

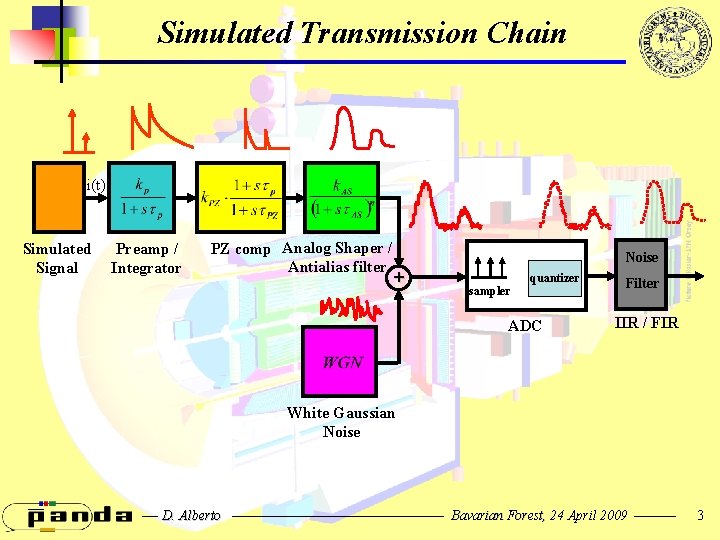

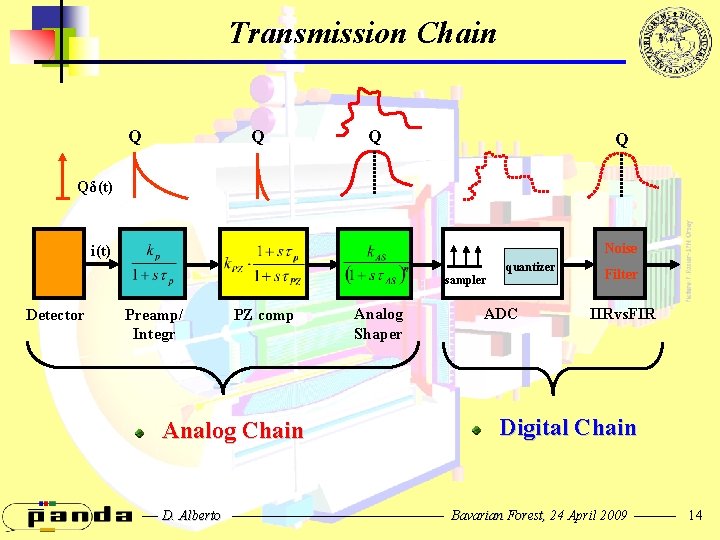

Simulated Transmission Chain i(t) Simulated Signal Preamp / Integrator PZ comp Analog Shaper / Antialias filter Noise + sampler quantizer ADC Filter IIR / FIR White Gaussian Noise D. Alberto Bavarian Forest, 24 April 2009 3

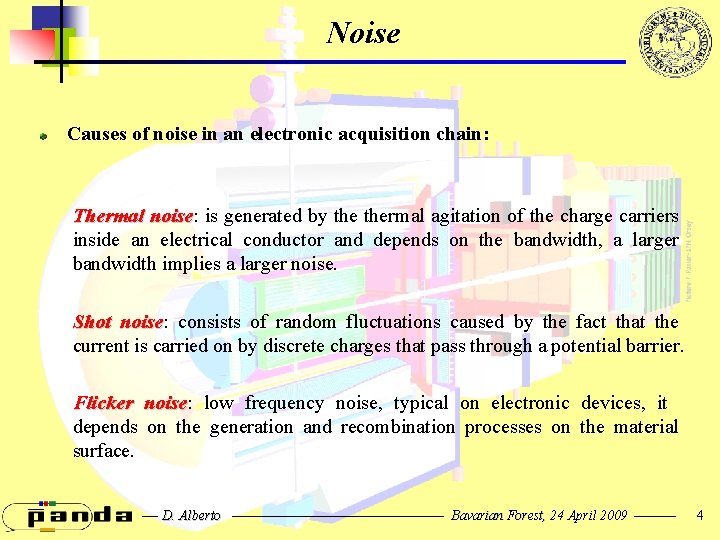

Noise Causes of noise in an electronic acquisition chain: Thermal noise: noise is generated by thermal agitation of the charge carriers inside an electrical conductor and depends on the bandwidth, a larger bandwidth implies a larger noise. Shot noise: noise consists of random fluctuations caused by the fact that the current is carried on by discrete charges that pass through a potential barrier. Flicker noise: noise low frequency noise, typical on electronic devices, it depends on the generation and recombination processes on the material surface. D. Alberto Bavarian Forest, 24 April 2009 4

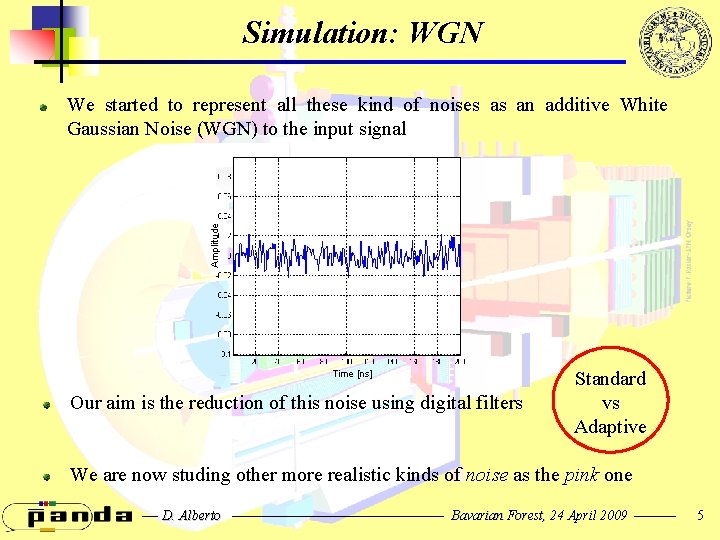

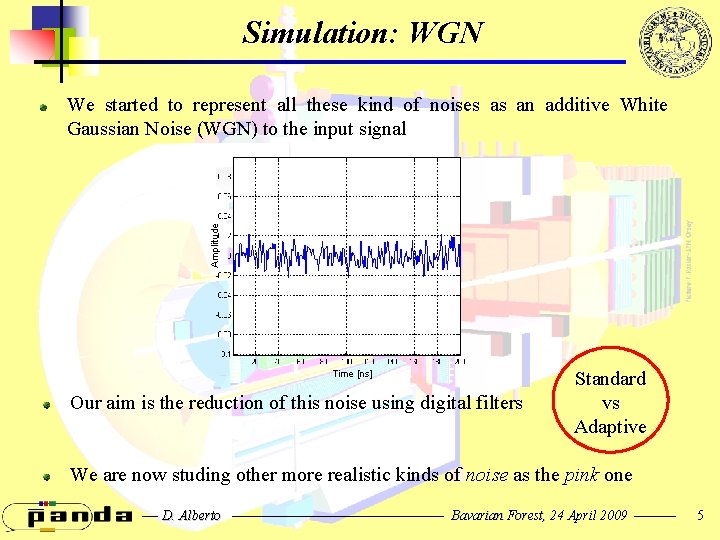

Simulation: WGN Amplitude We started to represent all these kind of noises as an additive White Gaussian Noise (WGN) to the input signal Time [ns] Our aim is the reduction of this noise using digital filters Standard vs Adaptive We are now studing other more realistic kinds of noise as the pink one D. Alberto Bavarian Forest, 24 April 2009 5

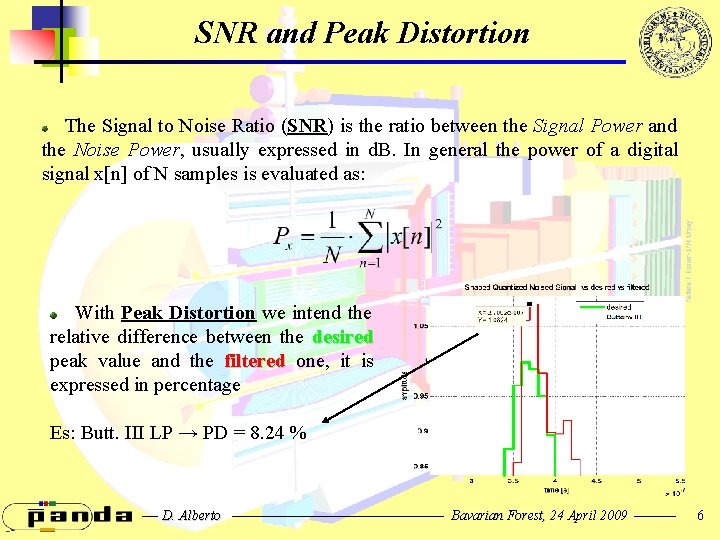

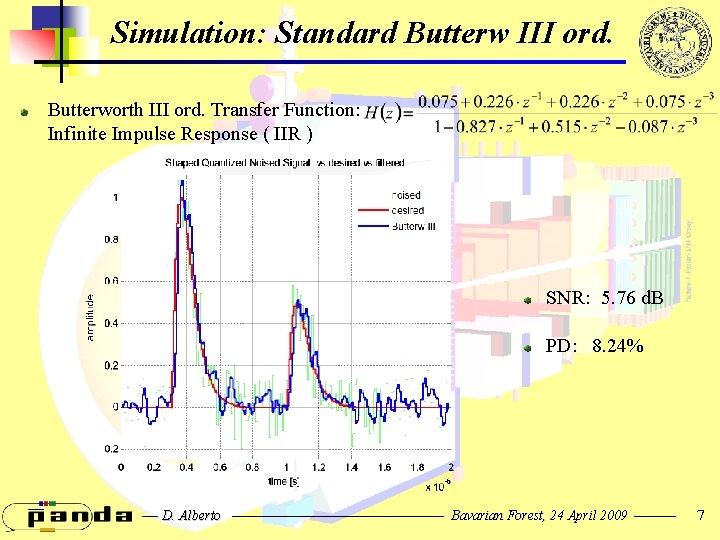

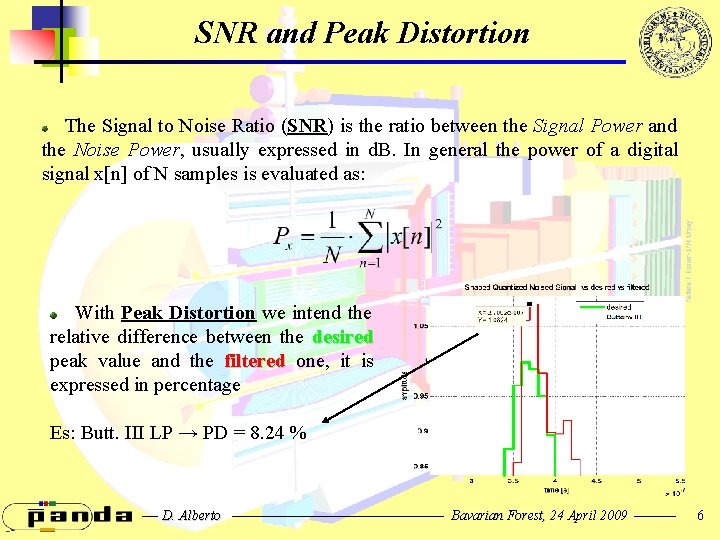

SNR and Peak Distortion The Signal to Noise Ratio (SNR) is the ratio between the Signal Power and the Noise Power, usually expressed in d. B. In general the power of a digital signal x[n] of N samples is evaluated as: With Peak Distortion we intend the relative difference between the desired peak value and the filtered one, it is expressed in percentage Es: Butt. III LP → PD = 8. 24 % D. Alberto Bavarian Forest, 24 April 2009 6

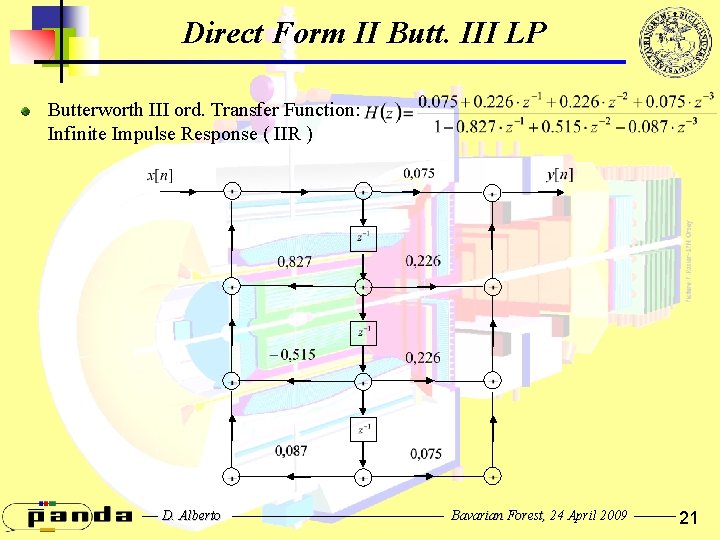

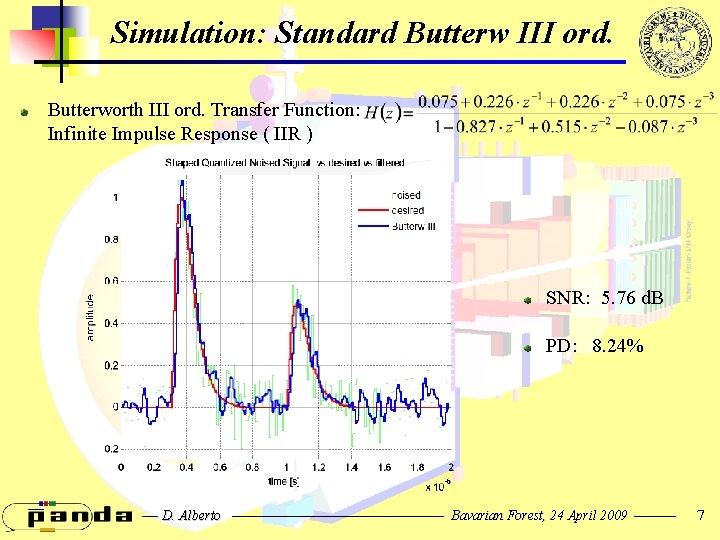

Simulation: Standard Butterw III ord. Butterworth III ord. Transfer Function: Infinite Impulse Response ( IIR ) SNR: 5. 76 d. B PD: 8. 24% D. Alberto Bavarian Forest, 24 April 2009 7

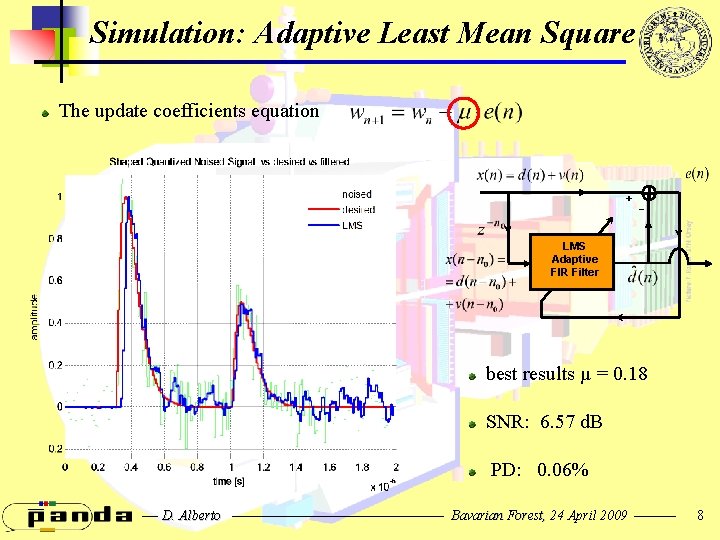

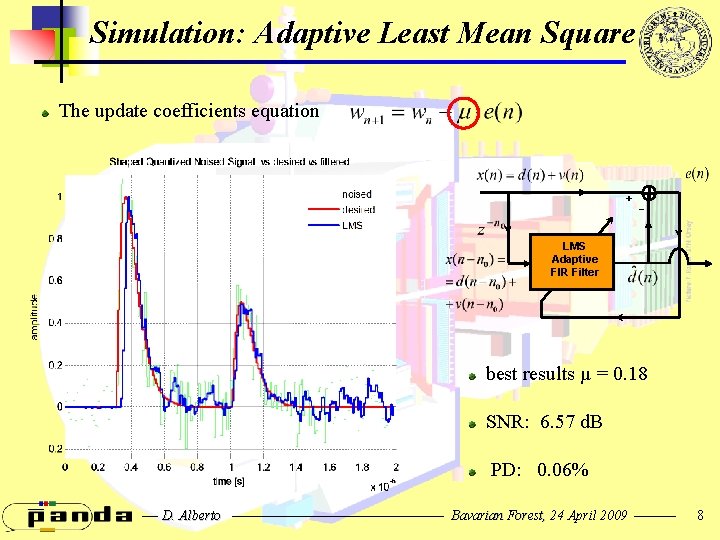

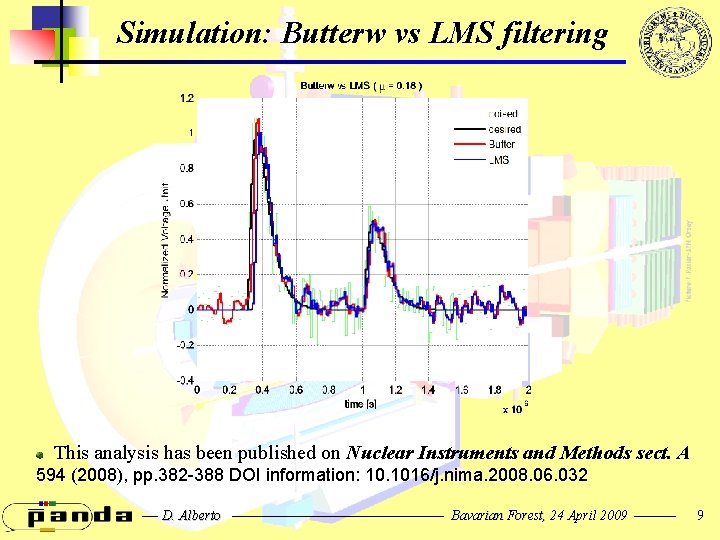

Simulation: Adaptive Least Mean Square The update coefficients equation + - LMS Adaptive FIR Filter best results µ = 0. 18 SNR: 6. 57 d. B PD: 0. 06% D. Alberto Bavarian Forest, 24 April 2009 8

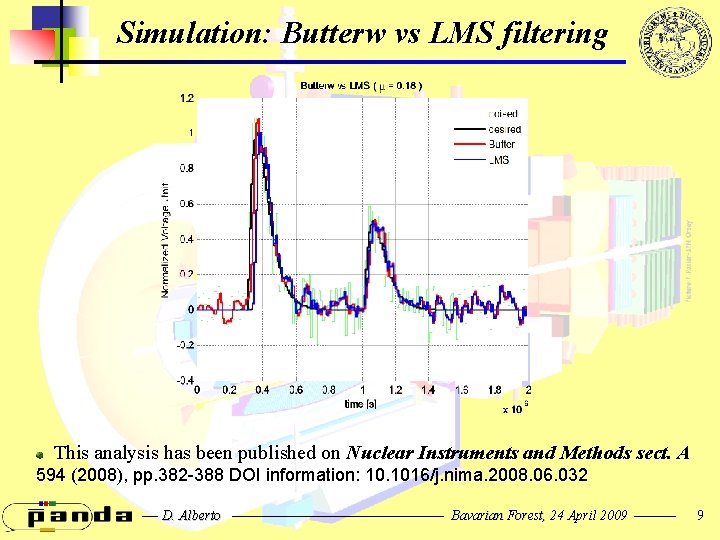

Simulation: Butterw vs LMS filtering This analysis has been published on Nuclear Instruments and Methods sect. A 594 (2008), pp. 382 -388 DOI information: 10. 1016/j. nima. 2008. 06. 032 D. Alberto Bavarian Forest, 24 April 2009 9

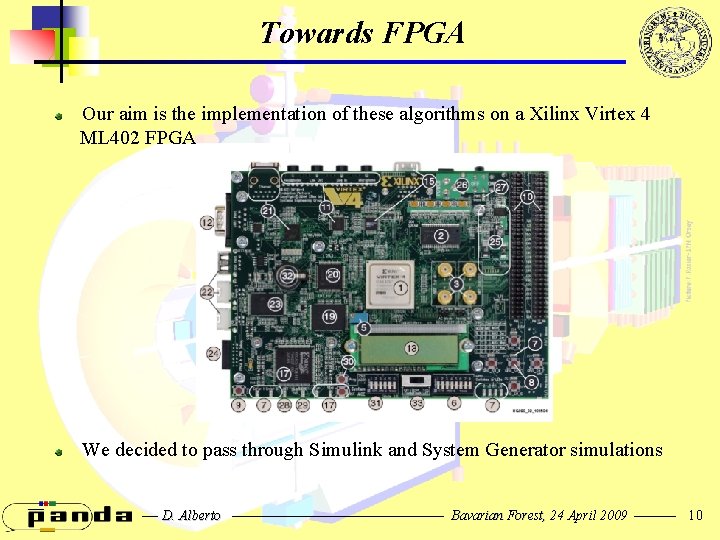

Towards FPGA Our aim is the implementation of these algorithms on a Xilinx Virtex 4 ML 402 FPGA We decided to pass through Simulink and System Generator simulations D. Alberto Bavarian Forest, 24 April 2009 10

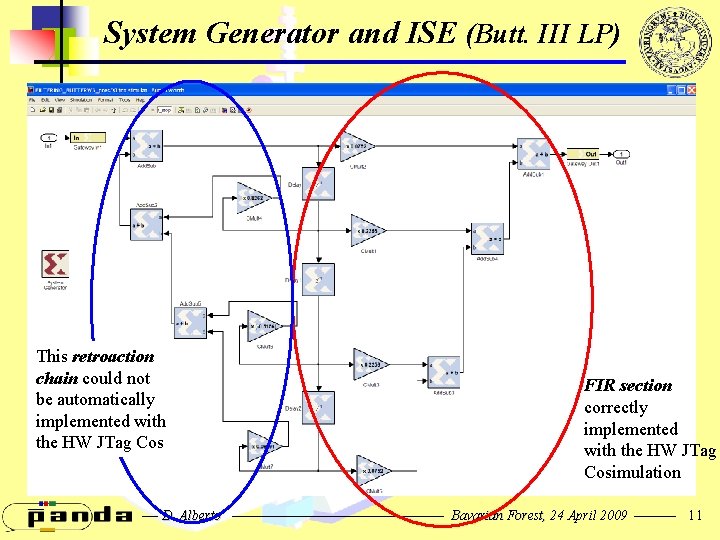

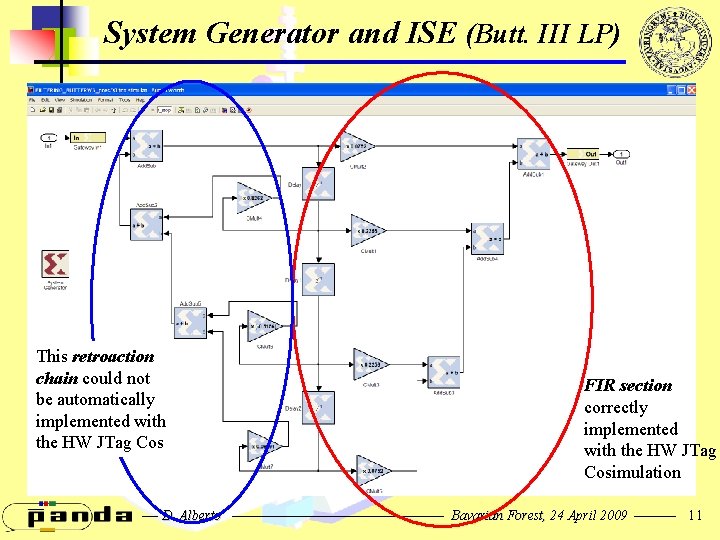

System Generator and ISE (Butt. III LP) This retroaction bits not chain 12 could 10 bits for the be automatically binary point implemented with the HW JTag Cos D. Alberto FIR section correctly implemented with the HW JTag Cosimulation Bavarian Forest, 24 April 2009 11

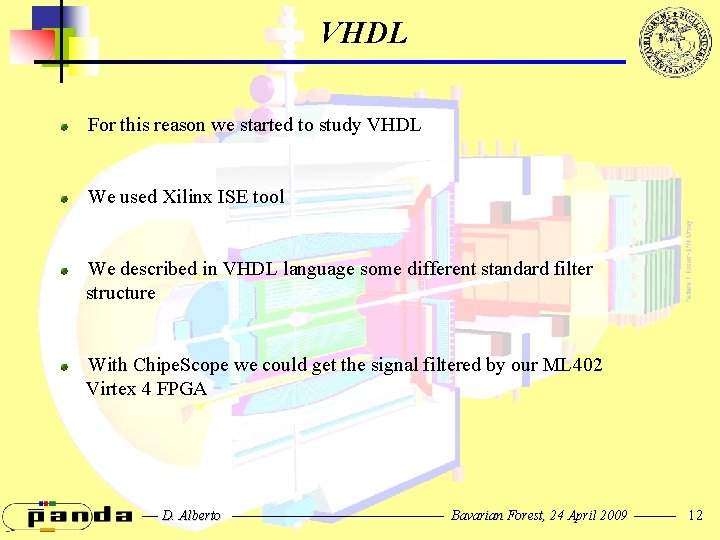

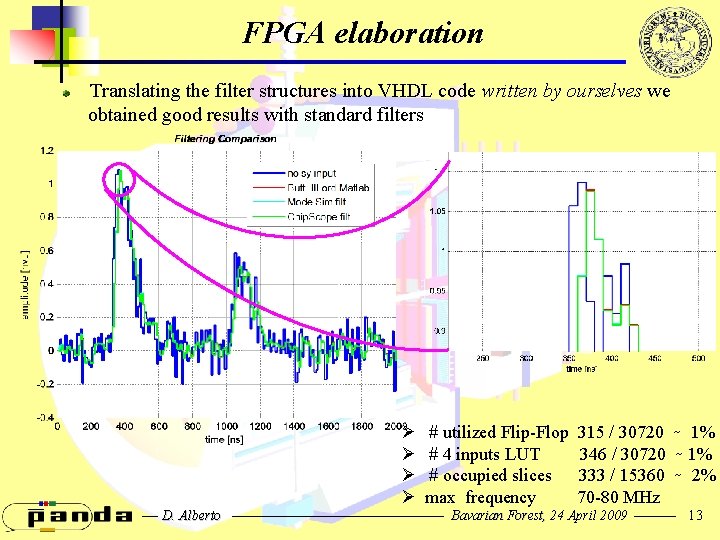

VHDL For this reason we started to study VHDL We used Xilinx ISE tool We described in VHDL language some different standard filter structure With Chipe. Scope we could get the signal filtered by our ML 402 Virtex 4 FPGA D. Alberto Bavarian Forest, 24 April 2009 12

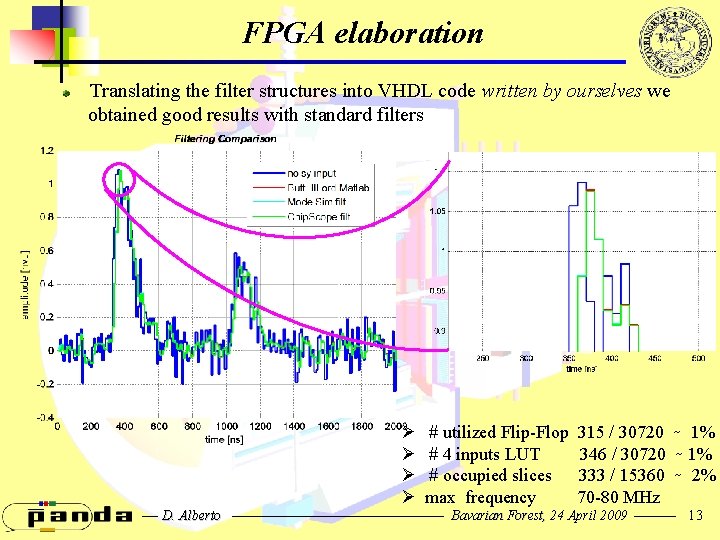

FPGA elaboration Translating the filter structures into VHDL code written by ourselves we obtained good results with standard filters Ø Ø D. Alberto # utilized Flip-Flop # 4 inputs LUT # occupied slices max frequency 315 / 30720 1% 346 / 30720 1% 333 / 15360 2% 70 -80 MHz Bavarian Forest, 24 April 2009 13

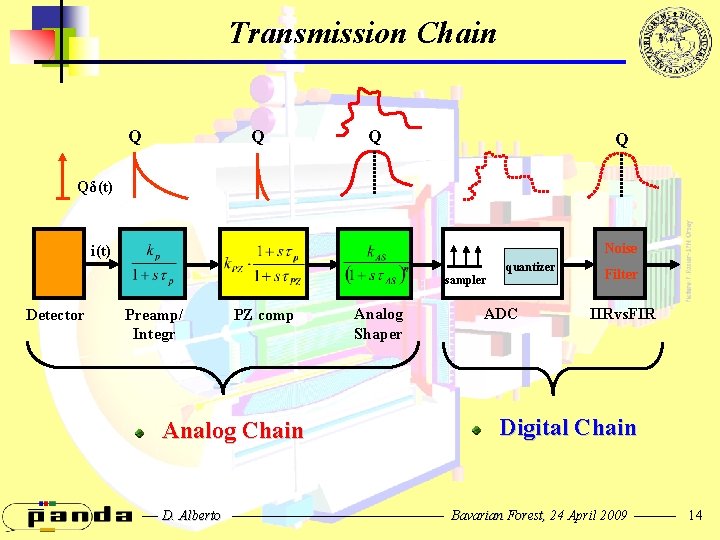

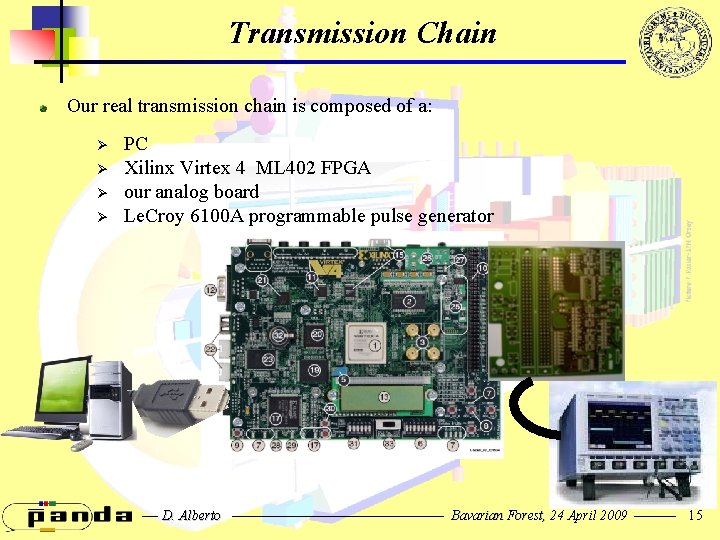

Transmission Chain Q Q Qδ(t) Noise i(t) sampler Detector Preamp/ Integr PZ comp Analog Chain D. Alberto Analog Shaper quantizer ADC Filter IIRvs. FIR Digital Chain Bavarian Forest, 24 April 2009 14

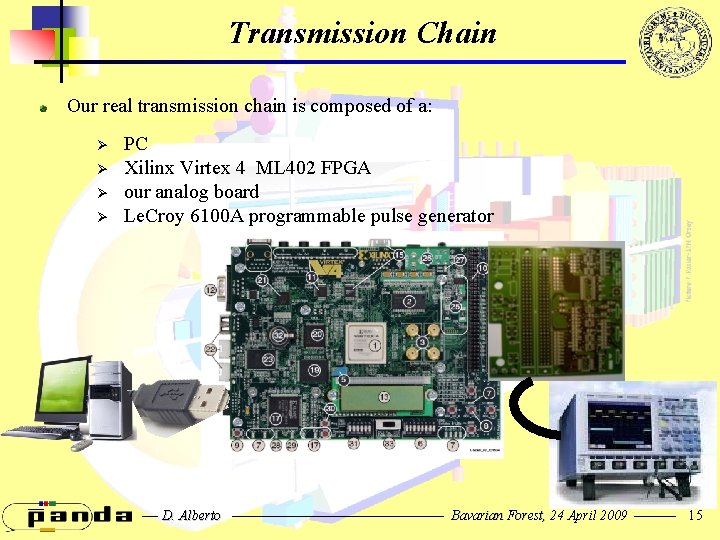

Transmission Chain Our real transmission chain is composed of a: Ø Ø PC Xilinx Virtex 4 ML 402 FPGA our analog board Le. Croy 6100 A programmable pulse generator D. Alberto Bavarian Forest, 24 April 2009 15

Future Works To cope with the implementation of LMS algorithms on FPGA Take into account faster algorithms (as the sign LMS ) To study different and more realistic kinds of noise D. Alberto Bavarian Forest, 24 April 2009 16

Thank you for the Attention !! D. Alberto Bavarian Forest, 24 April 2009

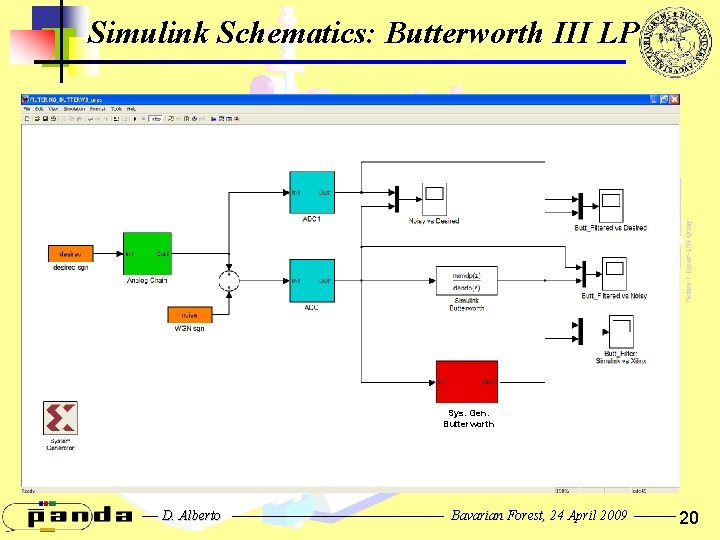

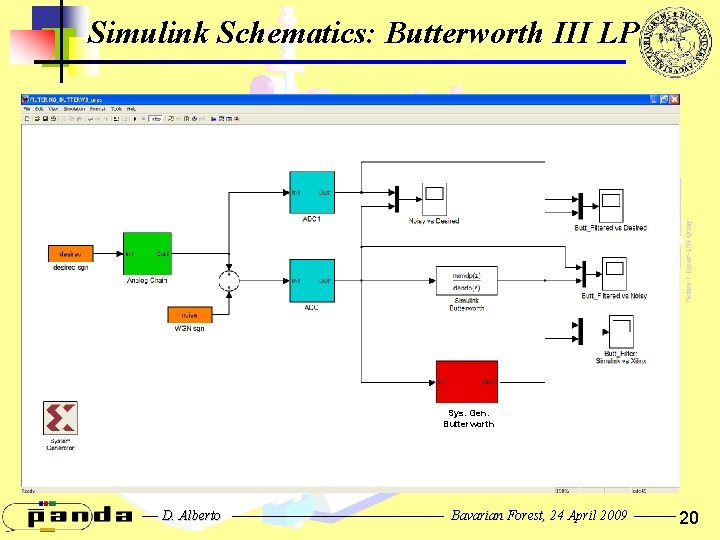

Simulink Schematics: Butterworth III LP Sys. Gen. Butterworth D. Alberto Bavarian Forest, 24 April 2009 20

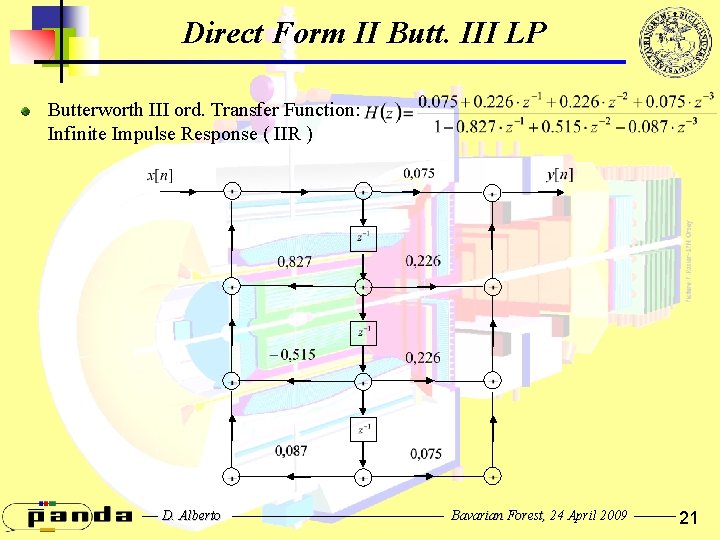

Direct Form II Butt. III LP Butterworth III ord. Transfer Function: Infinite Impulse Response ( IIR ) D. Alberto Bavarian Forest, 24 April 2009 21

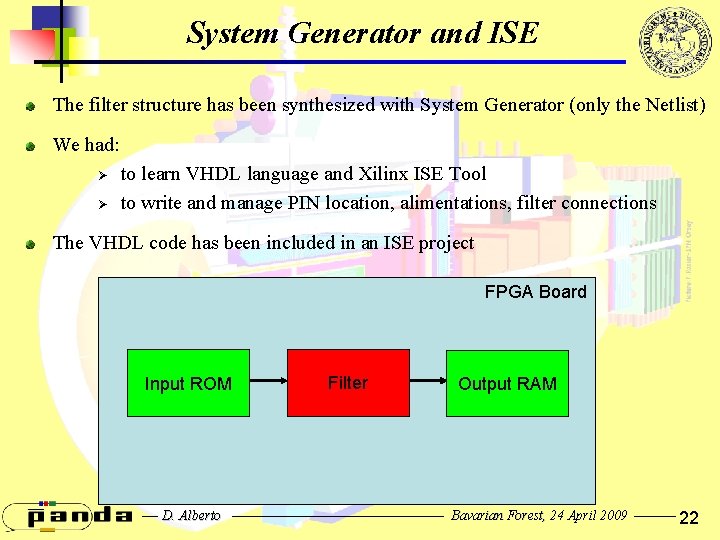

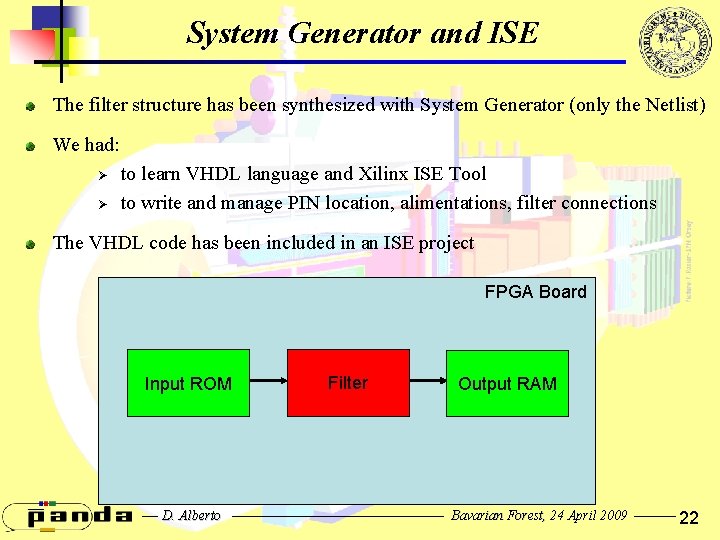

System Generator and ISE The filter structure has been synthesized with System Generator (only the Netlist) We had: Ø Ø to learn VHDL language and Xilinx ISE Tool to write and manage PIN location, alimentations, filter connections The VHDL code has been included in an ISE project FPGA Board Input ROM D. Alberto Filter Output RAM Bavarian Forest, 24 April 2009 22

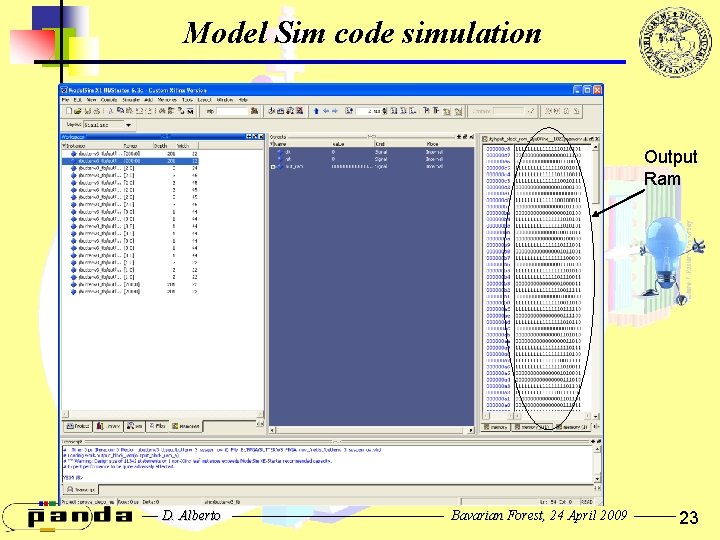

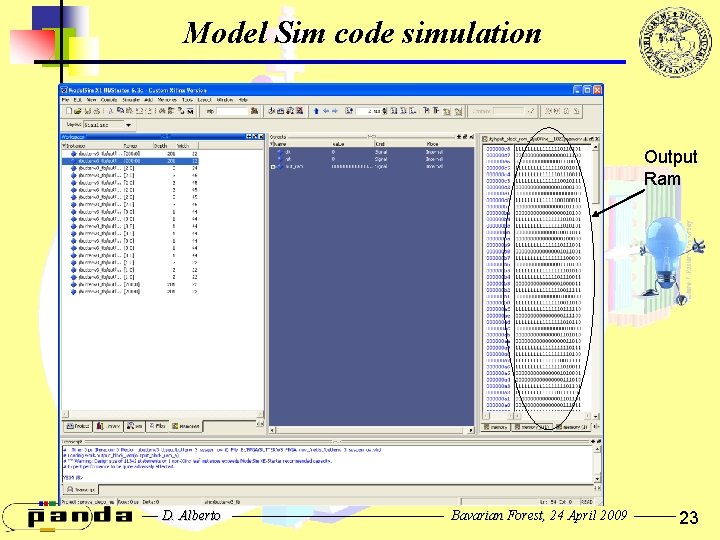

Model Sim code simulation Output Ram D. Alberto Bavarian Forest, 24 April 2009 23

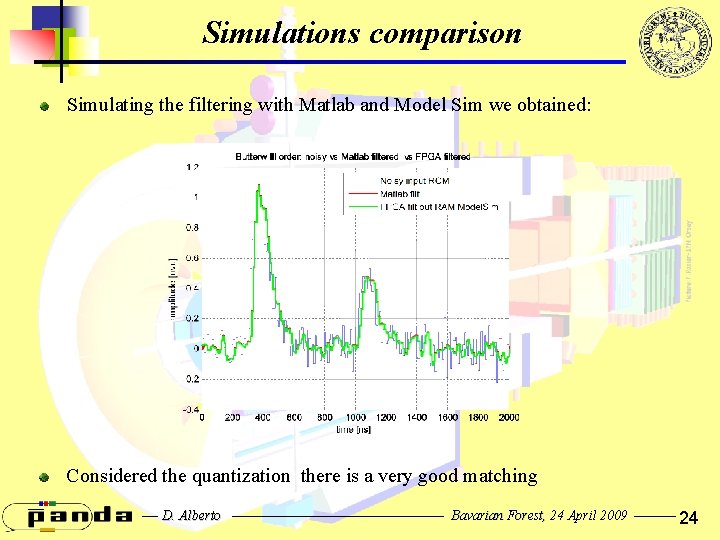

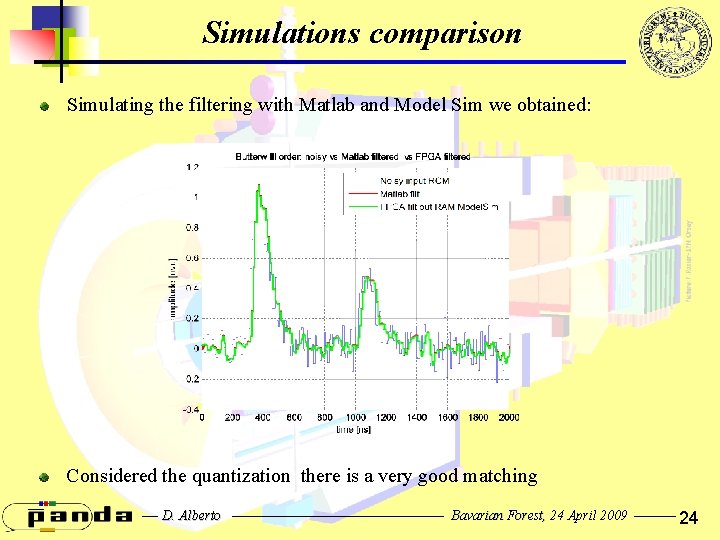

Simulations comparison Simulating the filtering with Matlab and Model Sim we obtained: Considered the quantization there is a very good matching D. Alberto Bavarian Forest, 24 April 2009 24

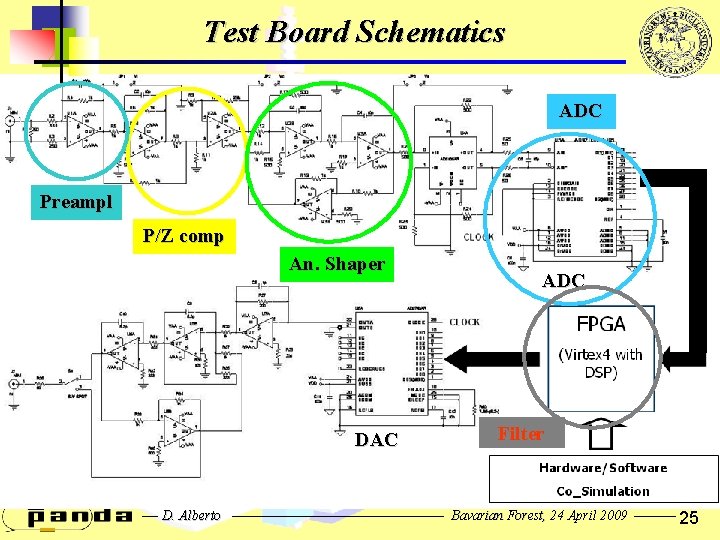

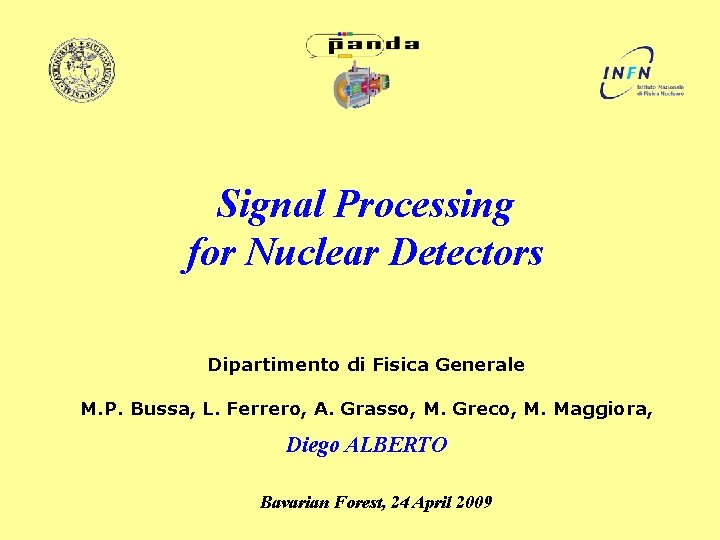

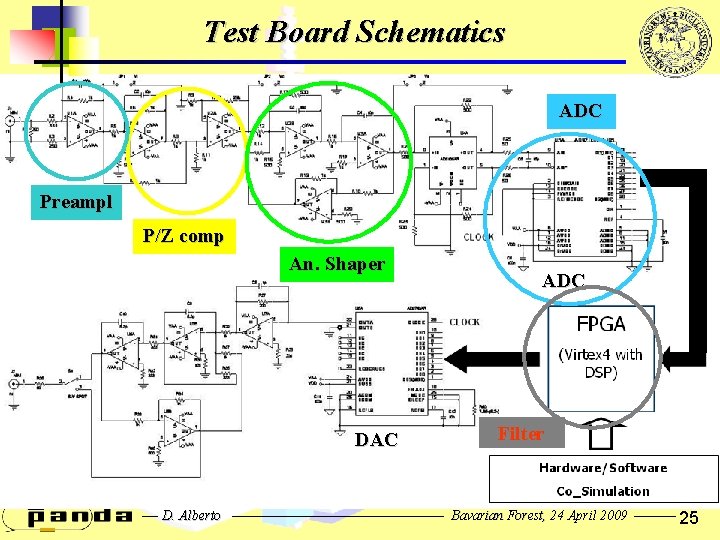

Test Board Schematics ADC Preampl P/Z comp An. Shaper DAC D. Alberto ADC Filter Bavarian Forest, 24 April 2009 25

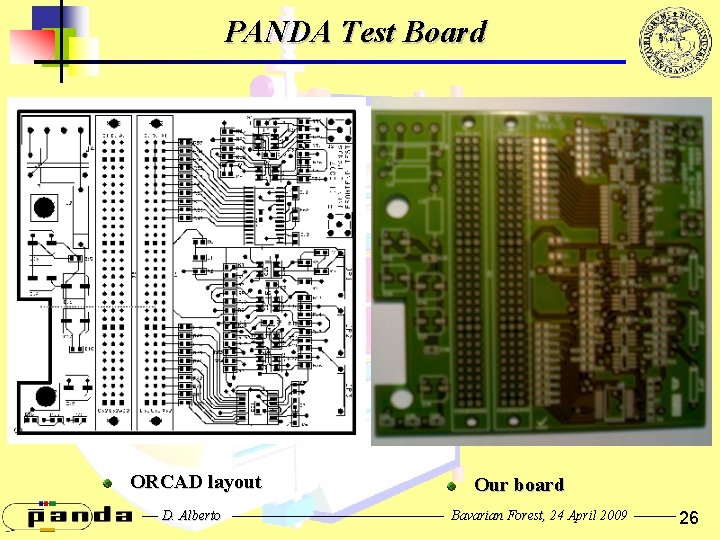

PANDA Test Board ORCAD layout D. Alberto Our board Bavarian Forest, 24 April 2009 26

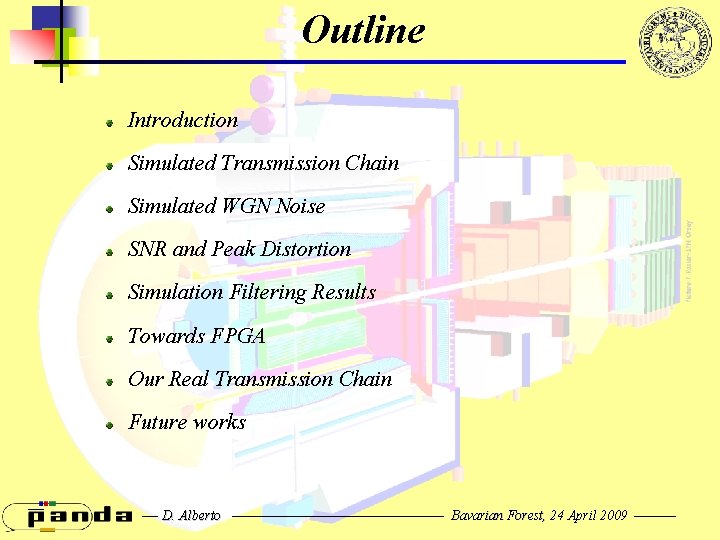

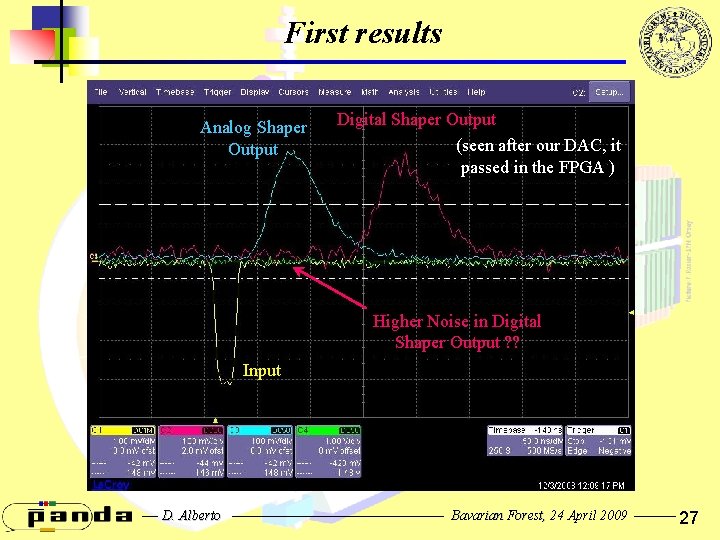

First results Analog Shaper Output Digital Shaper Output (seen after our DAC, it passed in the FPGA ) Higher Noise in Digital Shaper Output ? ? Input D. Alberto Bavarian Forest, 24 April 2009 27