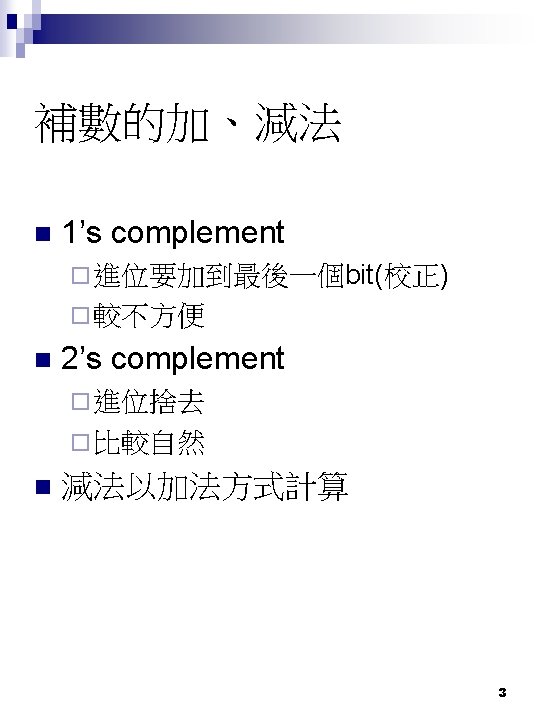

sign magnitude n 11s complement n 22s complement

![指令長度 n n n C=A+B C [A] + [B] Three operands ¨ Add n 指令長度 n n n C=A+B C [A] + [B] Three operands ¨ Add n](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-14.jpg)

![saved [R 1] 堆疊指標 saved [R 0] localvar 3 Move SP, FP New FP saved [R 1] 堆疊指標 saved [R 0] localvar 3 Move SP, FP New FP](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-36.jpg)

![低記憶體位址 [R 1] from SUB 1 [R 0] from SUB 1 [FP] from SUB 低記憶體位址 [R 1] from SUB 1 [R 0] from SUB 1 [FP] from SUB](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-38.jpg)

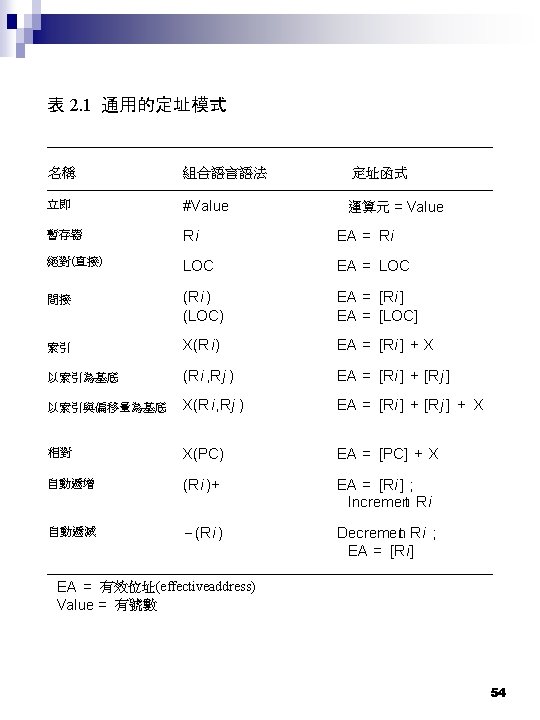

- Slides: 54

數值表示法 符號大小值(sign magnitude) n 1補數(1’s complement) n 2補數(2’s complement) n 2

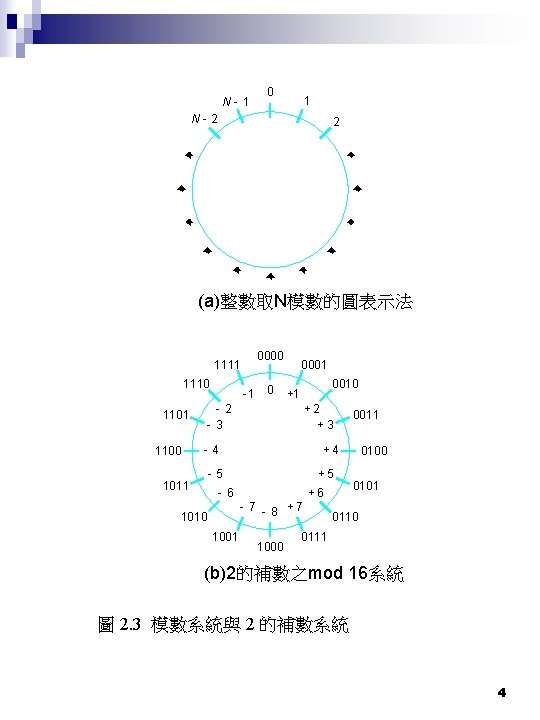

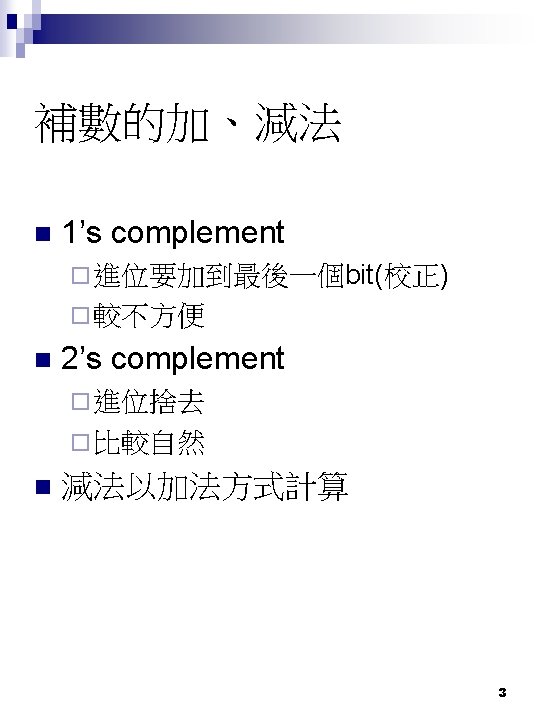

N- 1 0 1 N-2 2 (a)整數取N模數的圓表示法 0000 1111 1110 1101 1100 -1 0 0001 0010 +1 - 2 - 3 +2 +3 -4 +4 -5 1011 +5 - 6 +6 - 7 - 8 +7 1010 1001 0011 1000 0101 0110 0111 (b)2的補數之mod 16系統 圖 2. 3 模數系統與 2 的補數系統 4

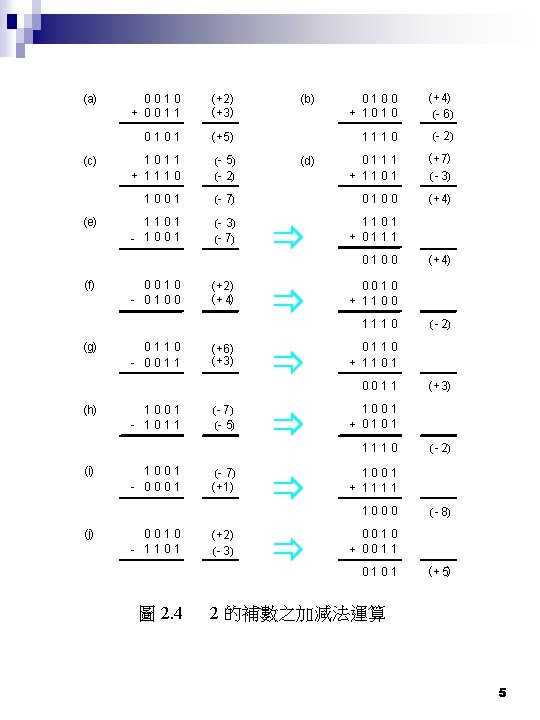

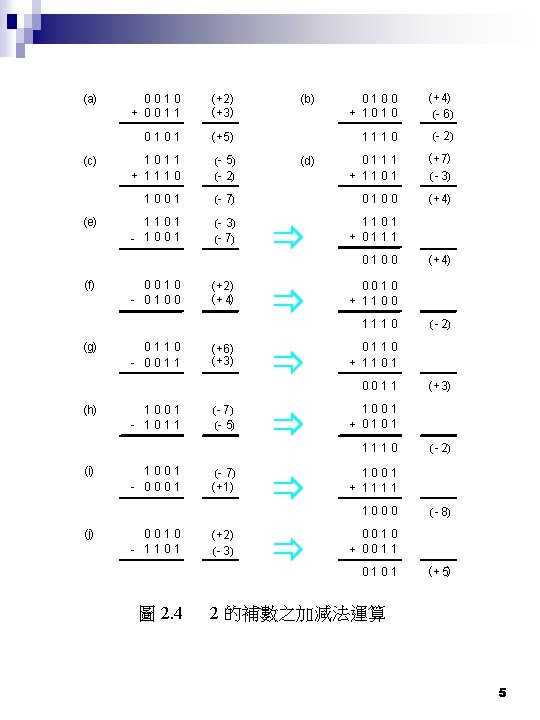

(a) (c) (e) 0100 + 1010 ( + 4) (- 6) 1110 (- 2) 0111 + 1101 ( + 7) ( - 3) (- 7) 0100 ( + 4) (- 3) (- 7) 1101 + 0111 0010 + 0011 ( + 2) ( + 3) 0101 ( + 5) 1011 + 1110 (- 5) (- 2) 1001 1101 - 1001 (b) (d) 0100 (f) 0010 - 0100 ( + 2) ( + 4) 0010 + 1100 1110 (g) 0110 - 0011 ( + 6) ( + 3) 1001 - 1011 ( - 7) (- 5) 1001 - 0001 (- 7) ( + 1) 0010 - 1101 ( + 2) ( - 3) ( - 8) 0010 + 0011 0101 圖 2. 4 ( - 2) 1001 + 1111 1000 (j) ( + 3) 1001 + 0101 1110 (i) ( - 2) 0110 + 1101 0011 (h) ( + 4) ( + 5) 2 的補數之加減法運算 5

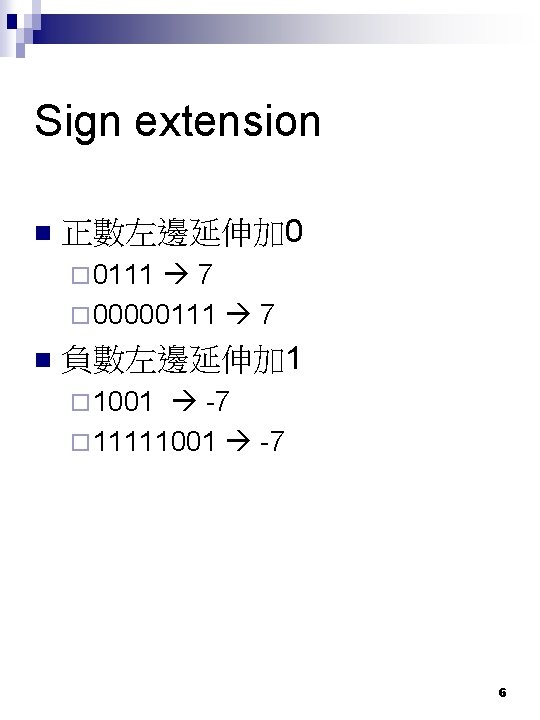

Sign extension n 正數左邊延伸加 0 ¨ 0111 7 ¨ 00000111 7 n 負數左邊延伸加 1 ¨ 1001 -7 ¨ 11111001 -7 6

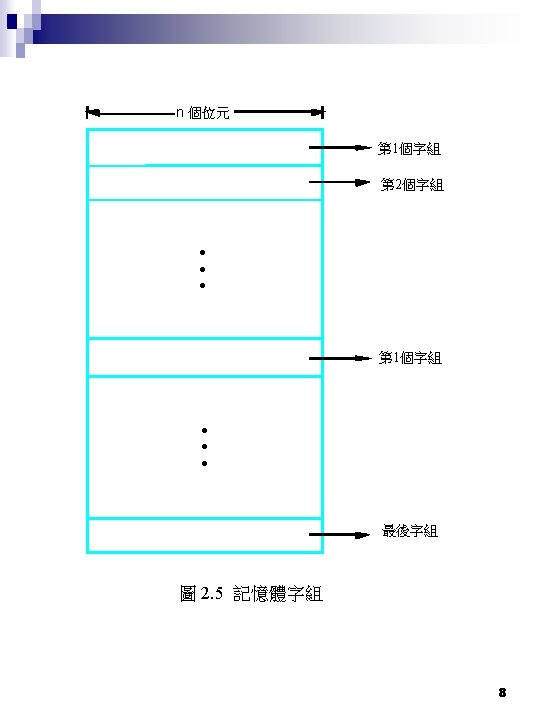

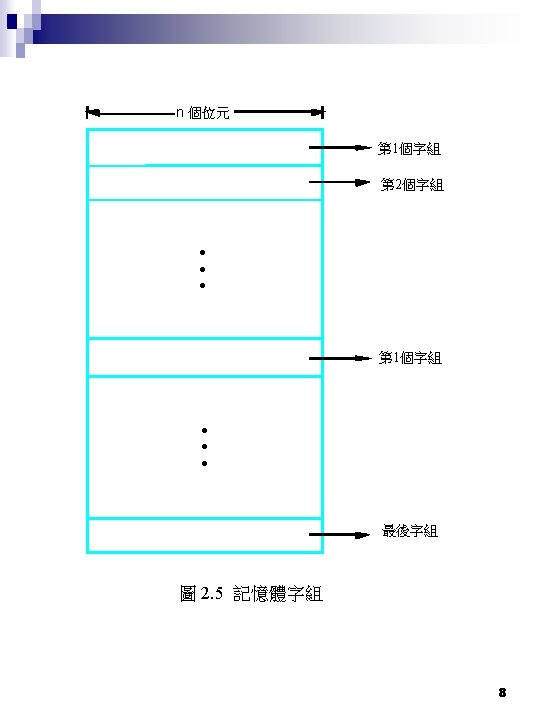

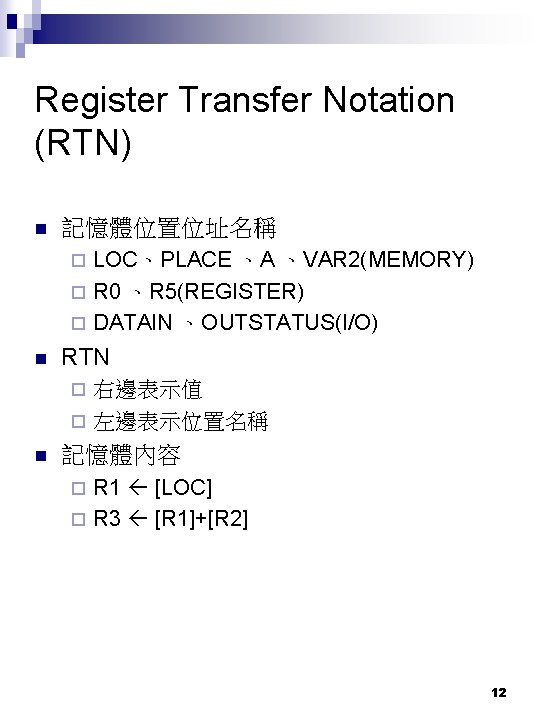

Address space(位址空間) CPU有24條定址線則有224 (16 M) Address space n 位元組(byte) n ¨ 固定 8 n 字組(word) ¨ 16~64 n bits 定址基本單位為位元組(byte) ¨ Byte-addressable memory(可定 址位元組的記憶體) 9

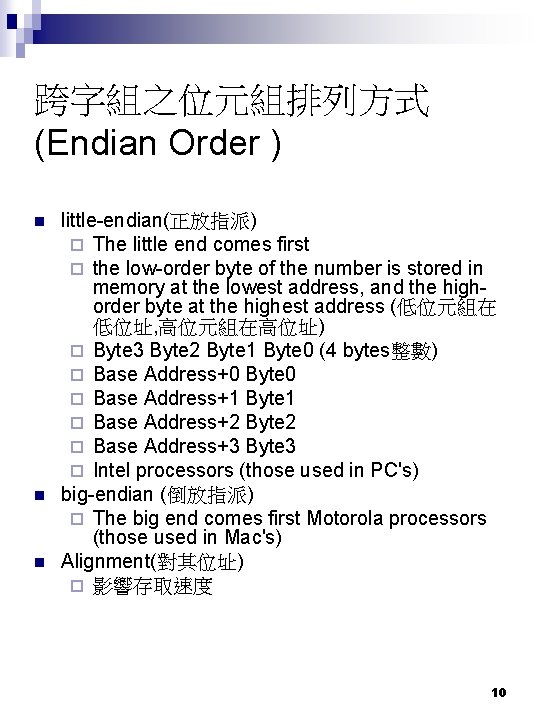

跨字組之位元組排列方式 (Endian Order ) n n n little-endian(正放指派) ¨ The little end comes first ¨ the low-order byte of the number is stored in memory at the lowest address, and the highorder byte at the highest address (低位元組在 低位址, 高位元組在高位址) ¨ Byte 3 Byte 2 Byte 1 Byte 0 (4 bytes整數) ¨ Base Address+0 Byte 0 ¨ Base Address+1 Byte 1 ¨ Base Address+2 Byte 2 ¨ Base Address+3 Byte 3 ¨ Intel processors (those used in PC's) big-endian (倒放指派) ¨ The big end comes first Motorola processors (those used in Mac's) Alignment(對其位址) ¨ 影響存取速度 10

Register Transfer Notation (RTN) n 記憶體位置位址名稱 LOC、PLACE 、A 、VAR 2(MEMORY) ¨ R 0 、R 5(REGISTER) ¨ DATAIN 、OUTSTATUS(I/O) ¨ n RTN 右邊表示值 ¨ 左邊表示位置名稱 ¨ n 記憶體內容 R 1 [LOC] ¨ R 3 [R 1]+[R 2] ¨ 12

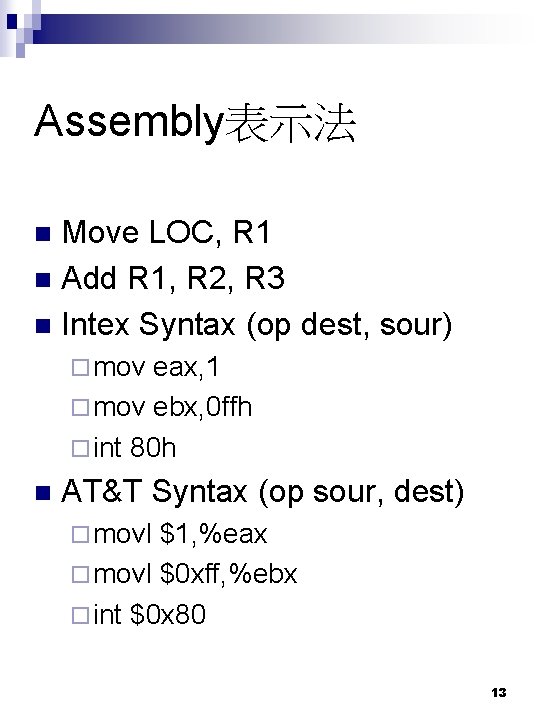

Assembly表示法 Move LOC, R 1 n Add R 1, R 2, R 3 n Intex Syntax (op dest, sour) n ¨ mov eax, 1 ¨ mov ebx, 0 ffh ¨ int 80 h n AT&T Syntax (op sour, dest) ¨ movl $1, %eax ¨ movl $0 xff, %ebx ¨ int $0 x 80 13

![指令長度 n n n CAB C A B Three operands Add n 指令長度 n n n C=A+B C [A] + [B] Three operands ¨ Add n](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-14.jpg)

指令長度 n n n C=A+B C [A] + [B] Three operands ¨ Add n A, B, C Two operands ¨ Move B, C ¨ Add A, C n Single operand (accumulator register implied) ¨ Load A ¨ Add A ¨ Store C 14

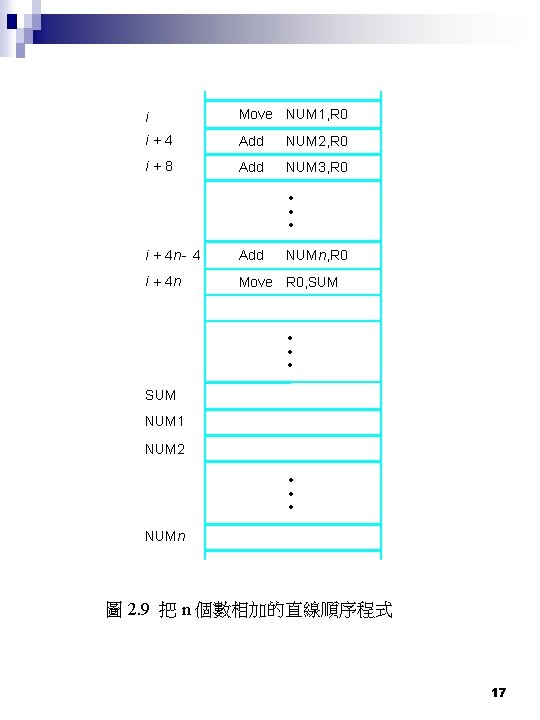

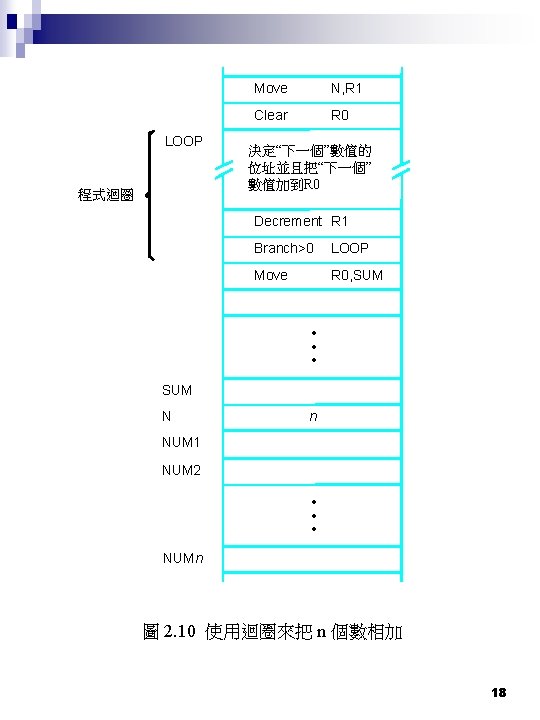

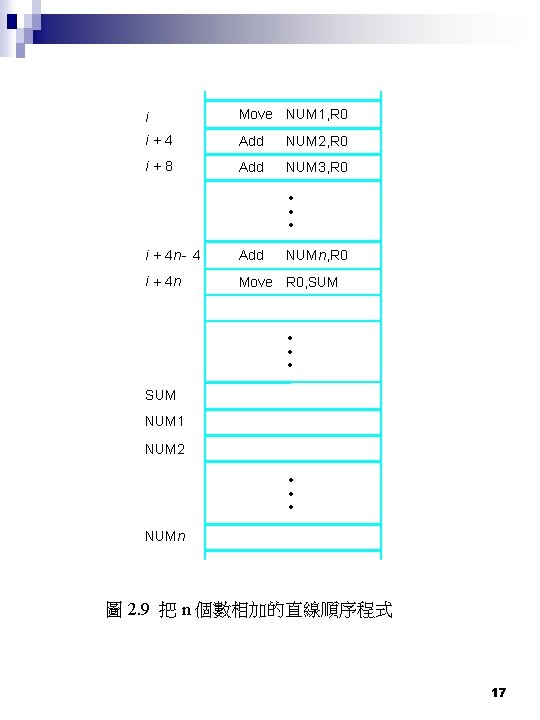

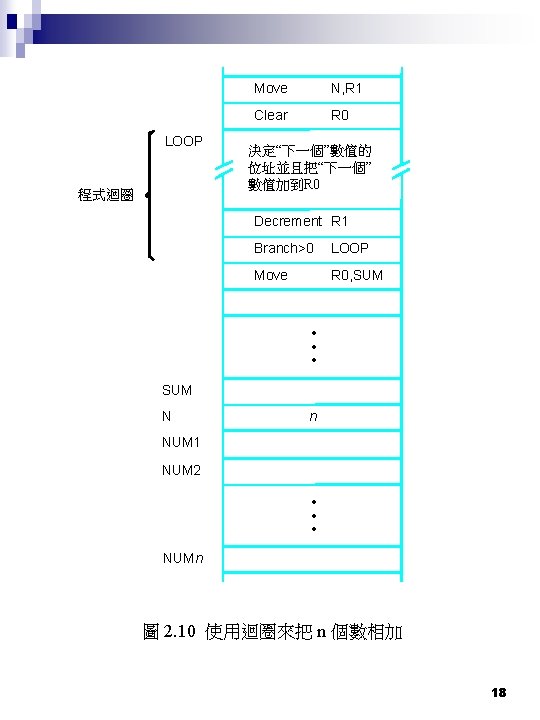

i Move NUM 1, R 0 i+4 Add NUM 2, R 0 i+8 Add NUM 3, R 0 • • • i + 4 n - 4 Add NUMn, R 0 i + 4 n Move R 0, SUM • • • SUM NUM 1 NUM 2 • • • NUMn 圖 2. 9 把 n 個數相加的直線順序程式 17

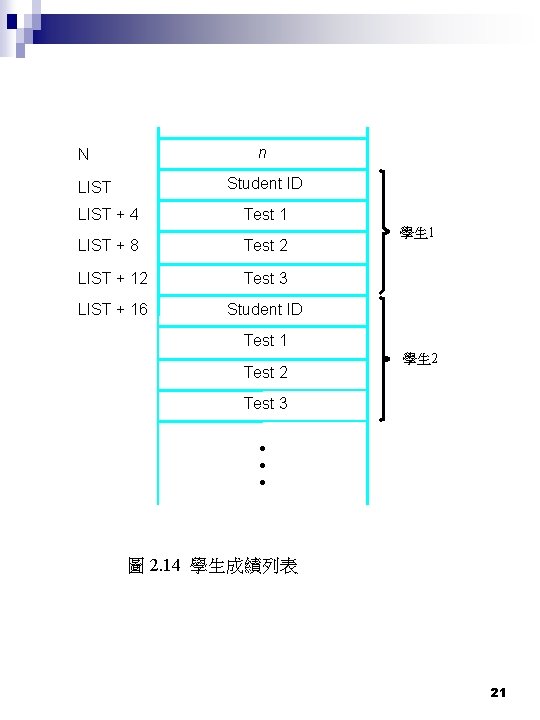

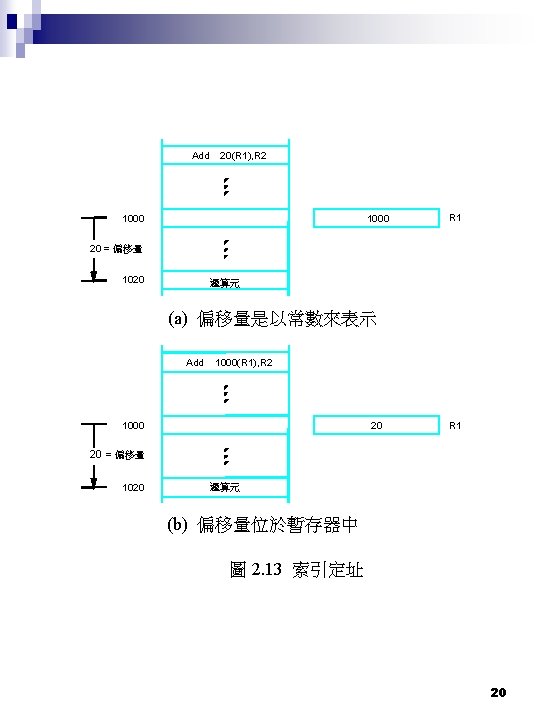

n N Student ID LIST + 4 Test 1 LIST + 8 Test 2 LIST + 12 Test 3 LIST + 16 Student ID 學生 1 Test 2 學生 2 Test 3 • • • 圖 2. 14 學生成績列表 21

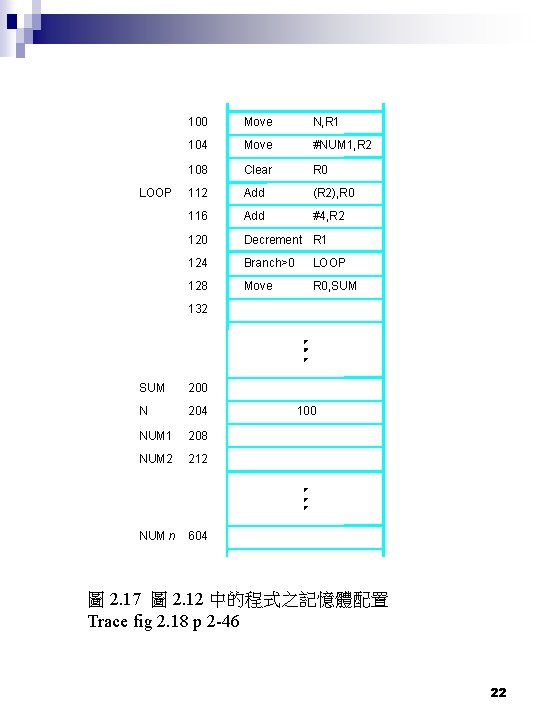

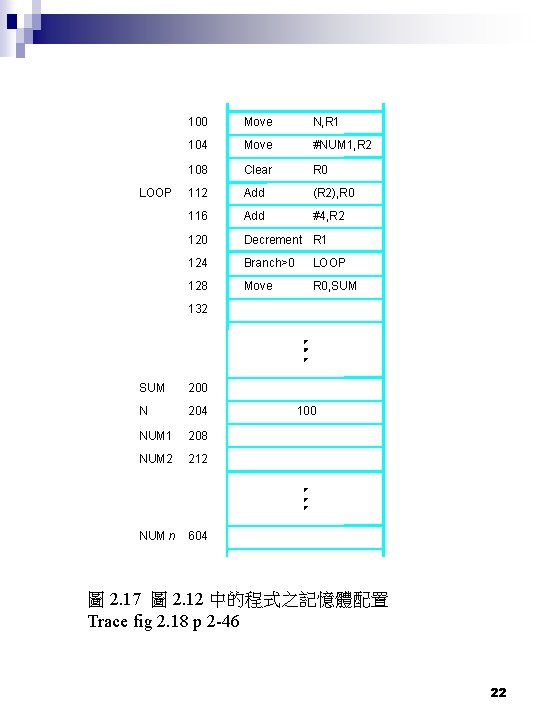

LOOP 100 Move N, R 1 104 Move #NUM 1, R 2 108 Clear R 0 112 Add (R 2), R 0 116 Add #4, R 2 120 Decrement R 1 124 Branch>0 LOOP 128 Move R 0, SUM 132 SUM 200 N 204 NUM 1 208 NUM 2 212 NUMn 604 100 圖 2. 17 圖 2. 12 中的程式之記憶體配置 Trace fig 2. 18 p 2 -46 22

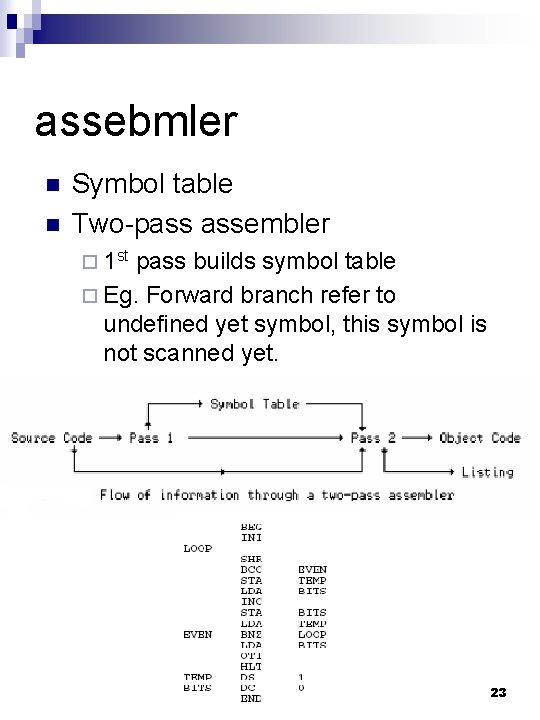

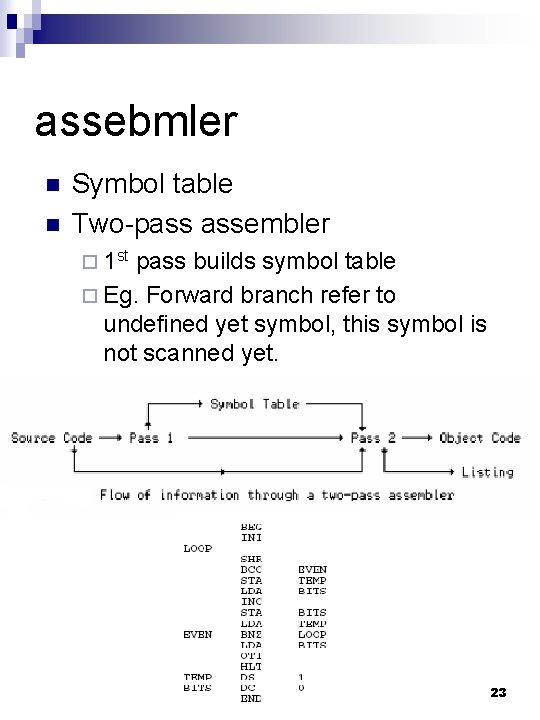

assebmler n n Symbol table Two-pass assembler ¨ 1 st pass builds symbol table ¨ Eg. Forward branch refer to undefined yet symbol, this symbol is not scanned yet. 23

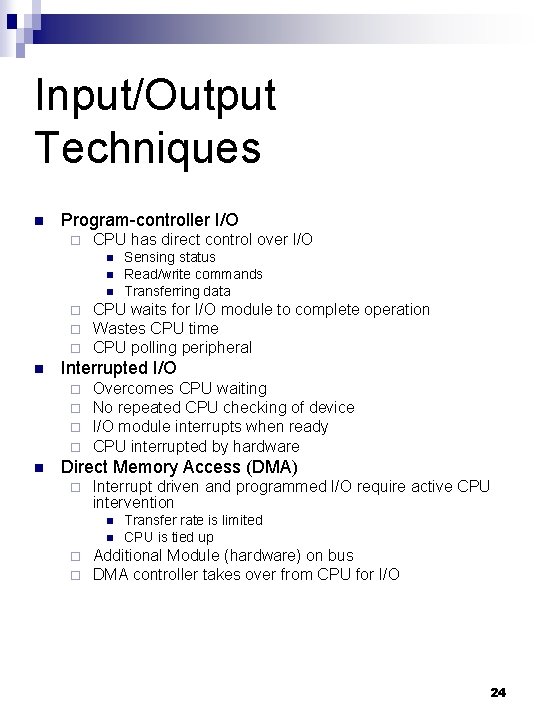

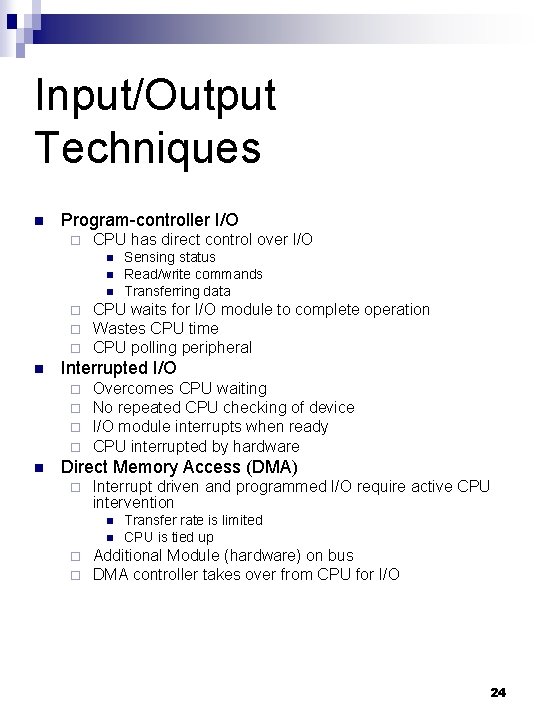

Input/Output Techniques n Program-controller I/O ¨ CPU has direct control over I/O n n n ¨ ¨ ¨ n CPU waits for I/O module to complete operation Wastes CPU time CPU polling peripheral Interrupted I/O ¨ ¨ n Sensing status Read/write commands Transferring data Overcomes CPU waiting No repeated CPU checking of device I/O module interrupts when ready CPU interrupted by hardware Direct Memory Access (DMA) ¨ Interrupt driven and programmed I/O require active CPU intervention n n ¨ ¨ Transfer rate is limited CPU is tied up Additional Module (hardware) on bus DMA controller takes over from CPU for I/O 24

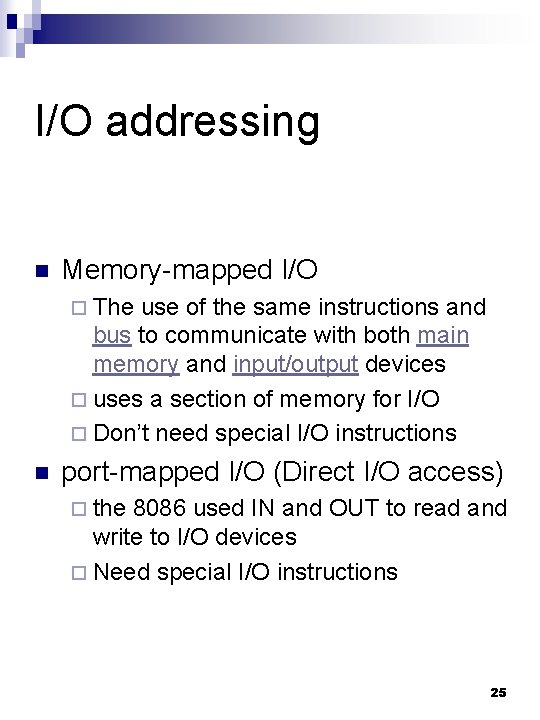

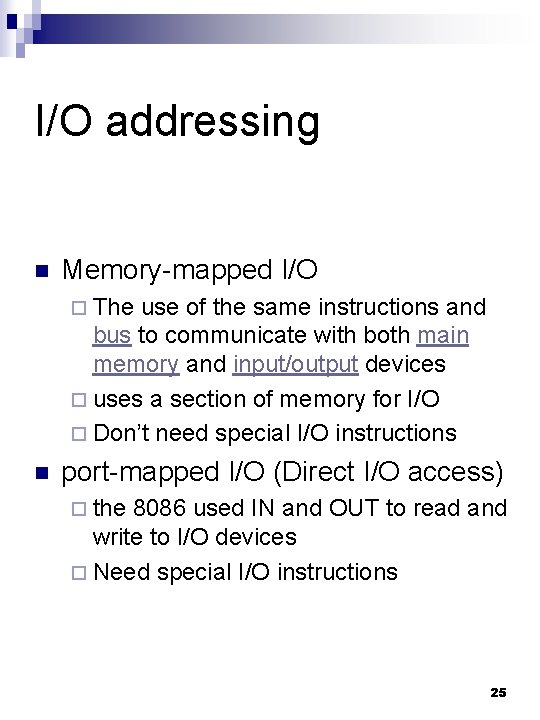

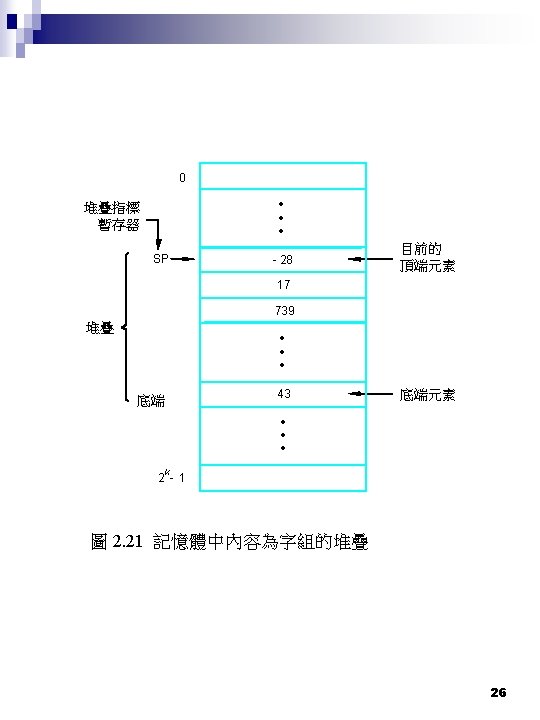

I/O addressing n Memory-mapped I/O ¨ The use of the same instructions and bus to communicate with both main memory and input/output devices ¨ uses a section of memory for I/O ¨ Don’t need special I/O instructions n port-mapped I/O (Direct I/O access) ¨ the 8086 used IN and OUT to read and write to I/O devices ¨ Need special I/O instructions 25

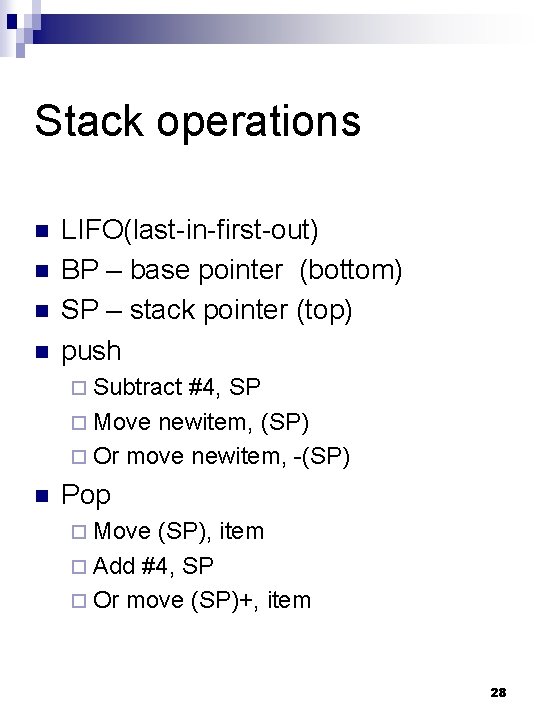

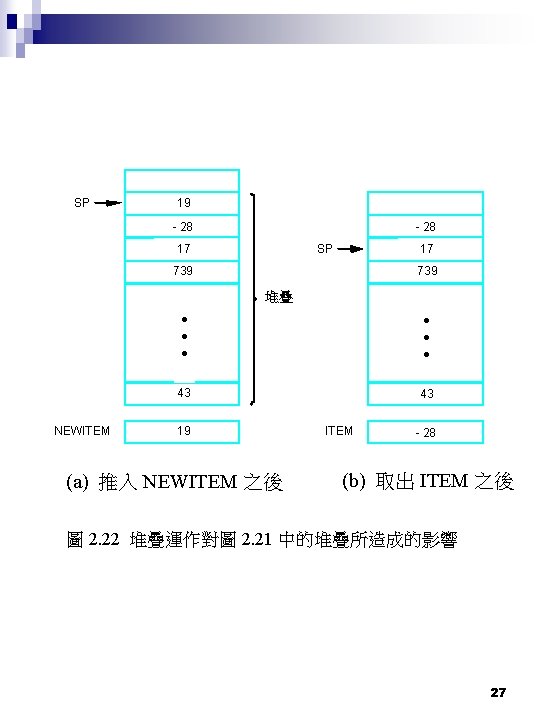

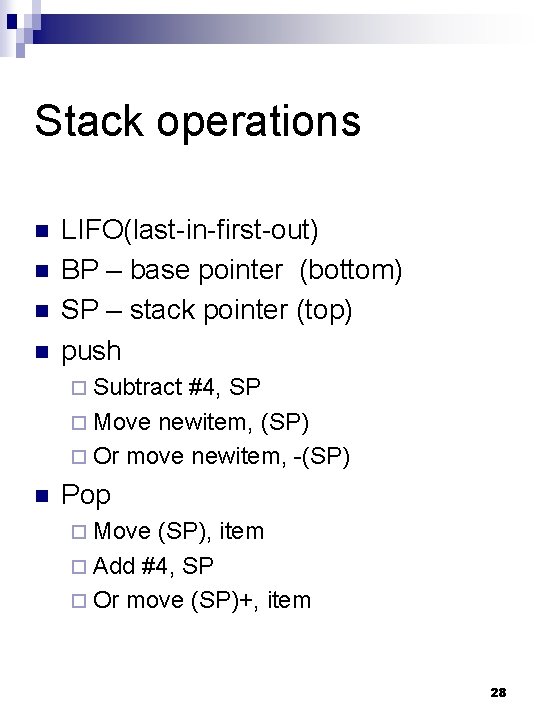

Stack operations n n LIFO(last-in-first-out) BP – base pointer (bottom) SP – stack pointer (top) push ¨ Subtract #4, SP ¨ Move newitem, (SP) ¨ Or move newitem, -(SP) n Pop ¨ Move (SP), item ¨ Add #4, SP ¨ Or move (SP)+, item 28

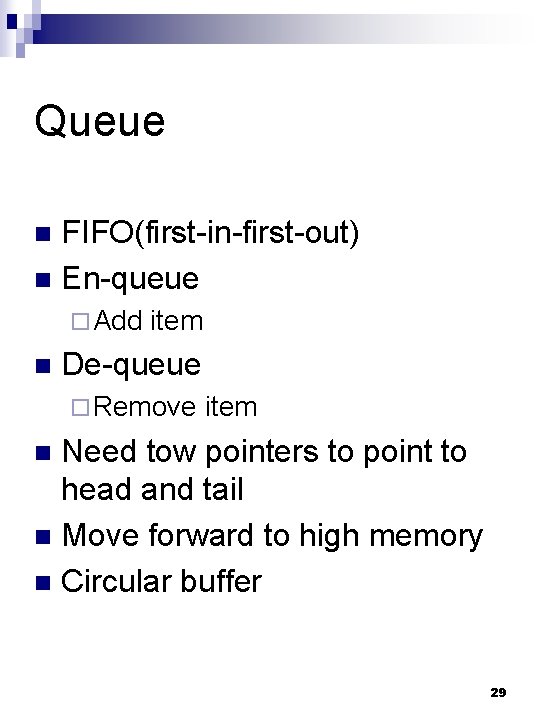

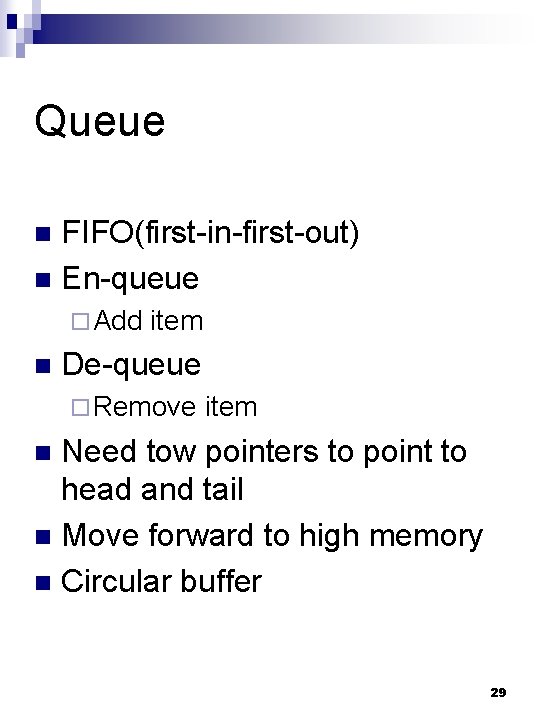

Queue FIFO(first-in-first-out) n En-queue n ¨ Add n item De-queue ¨ Remove item Need tow pointers to point to head and tail n Move forward to high memory n Circular buffer n 29

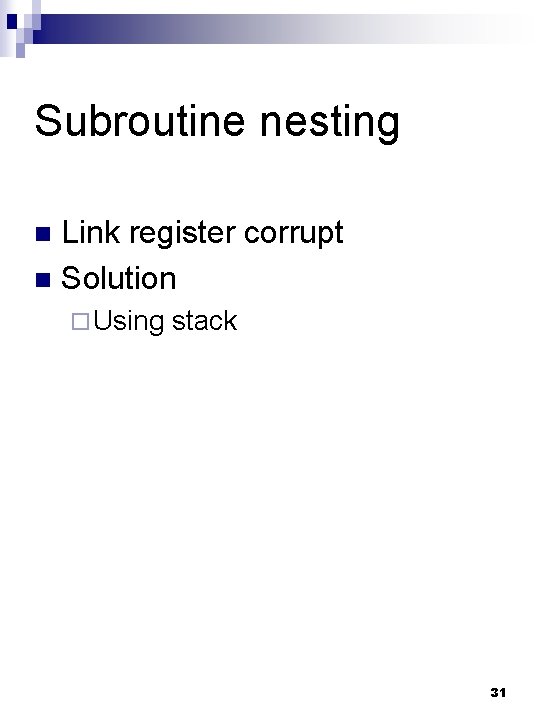

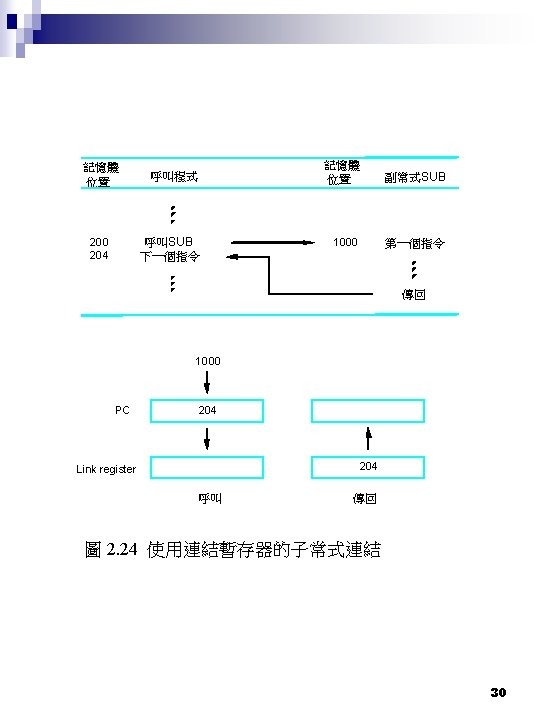

Subroutine nesting Link register corrupt n Solution n ¨ Using stack 31

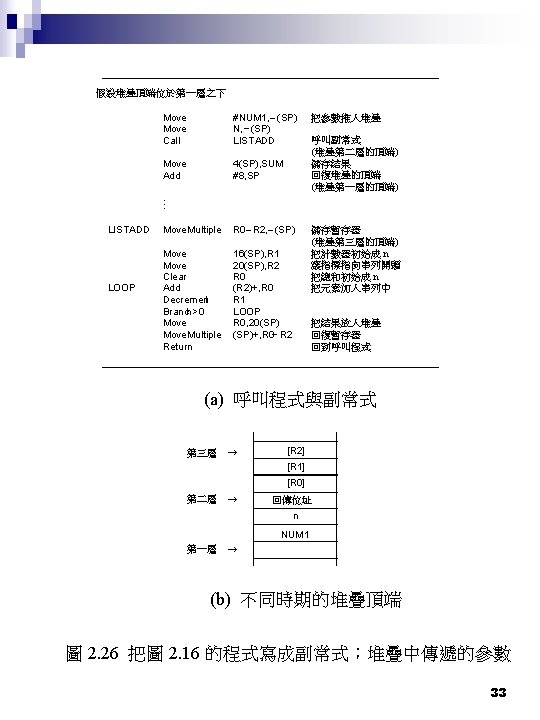

Parameter passing Using registers to accept argument n Trace fig 2. 25 p 2 -63 n Drawback n ¨ How n to handle many parameter? Solution ¨ Using stack 32

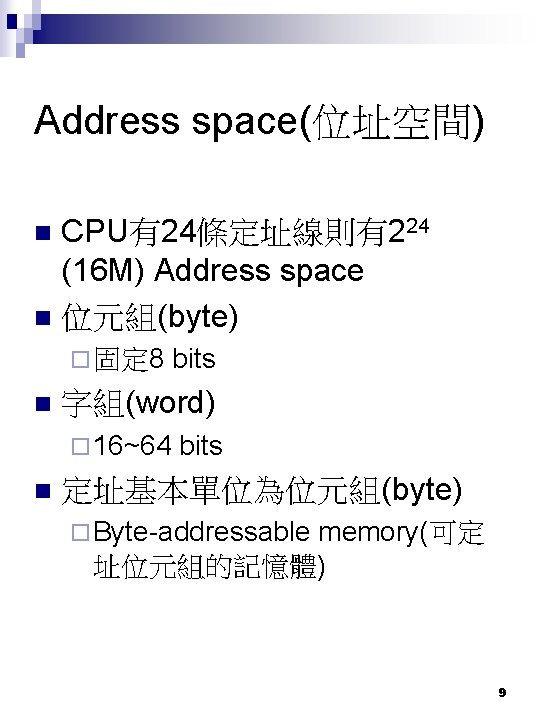

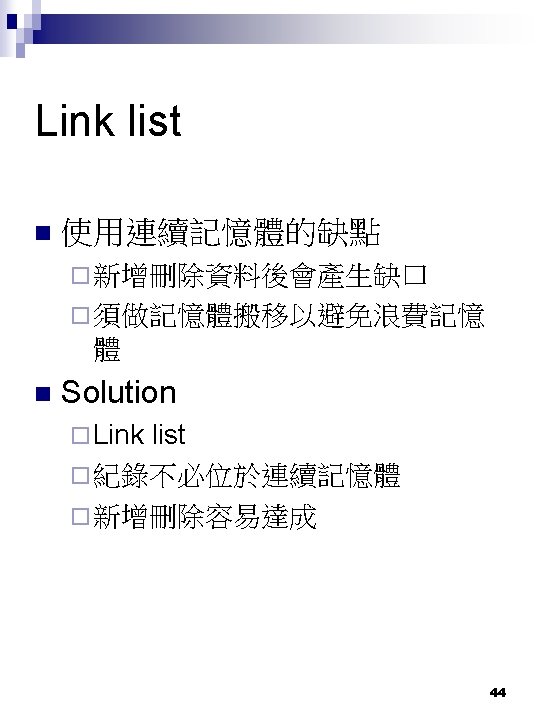

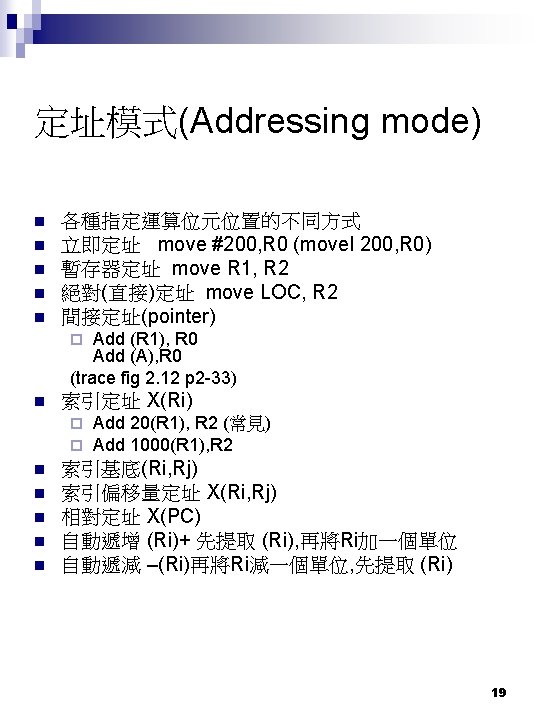

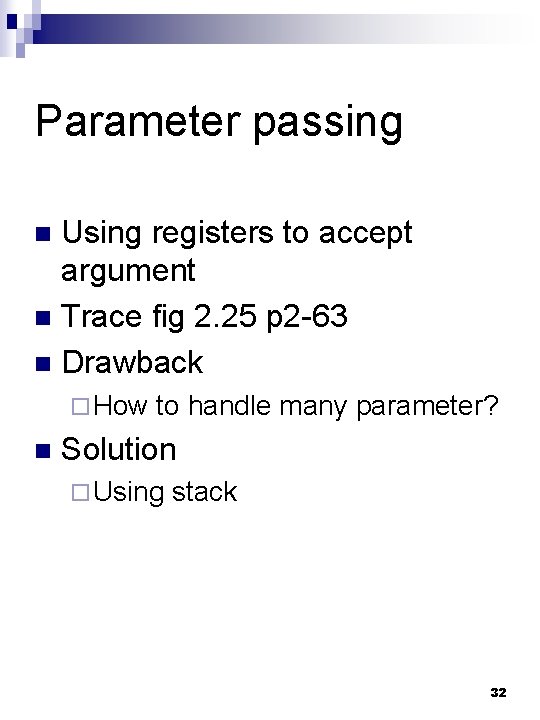

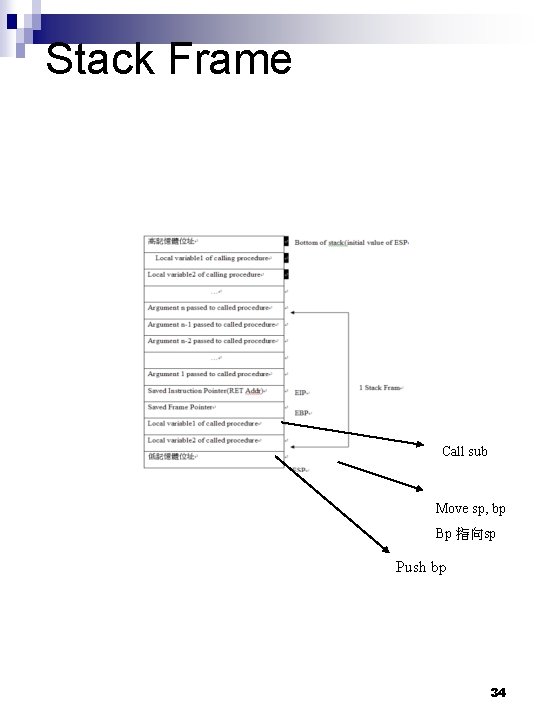

Stack Frame Call sub Move sp, bp Bp 指向sp Push bp 34

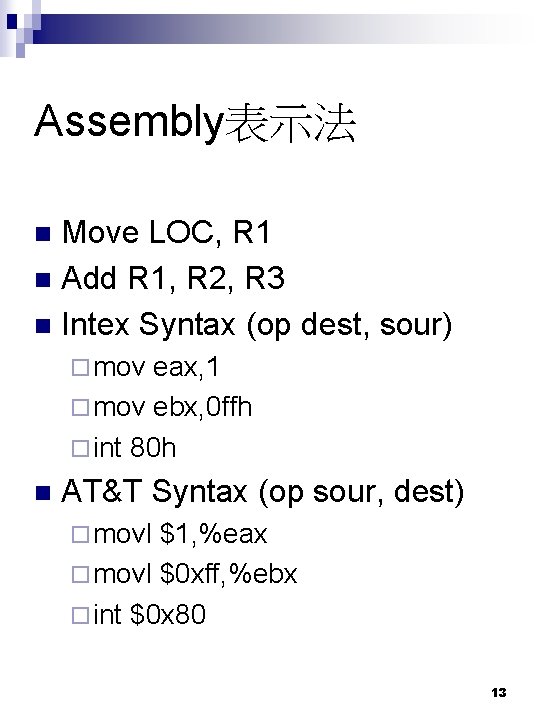

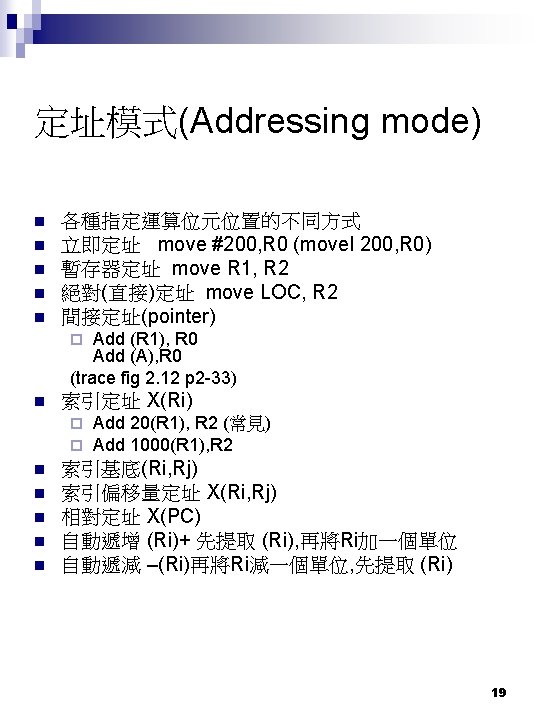

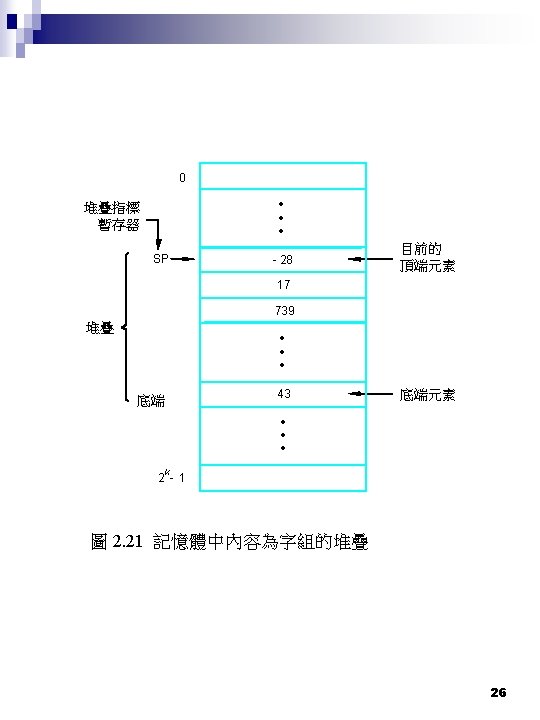

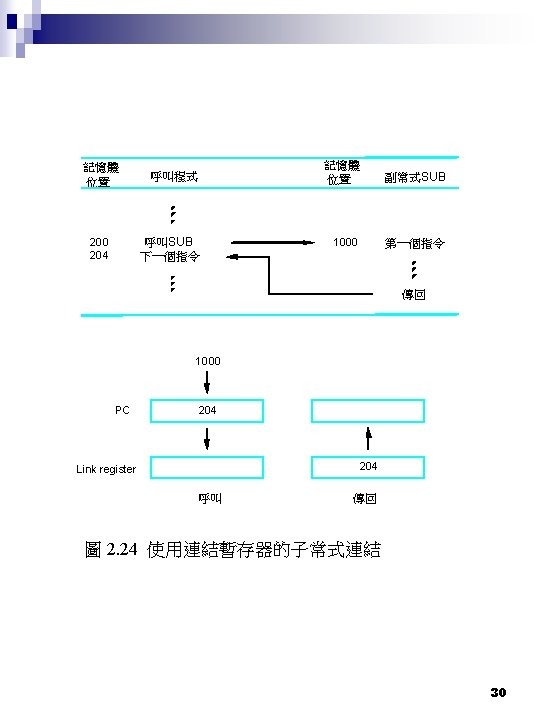

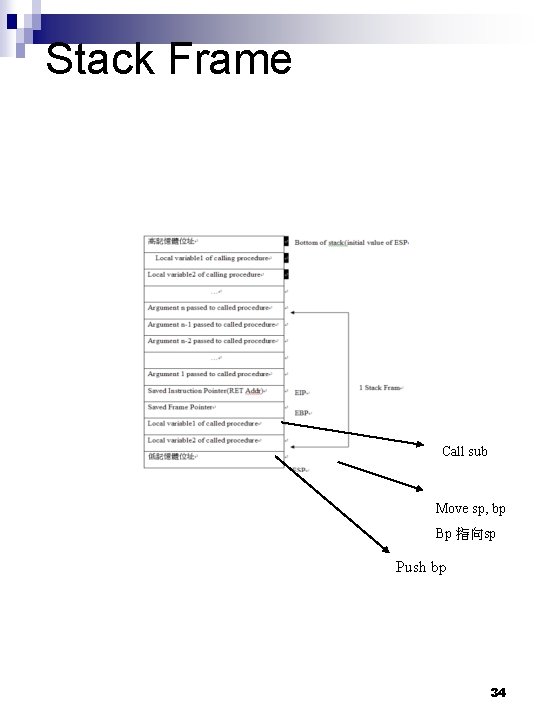

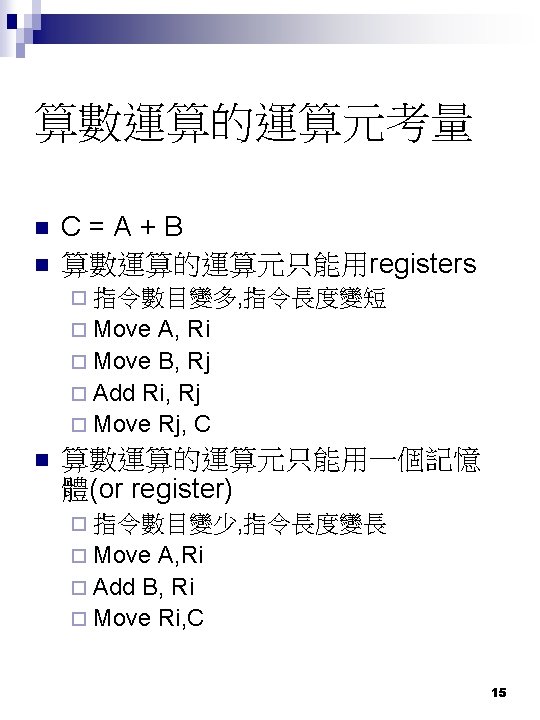

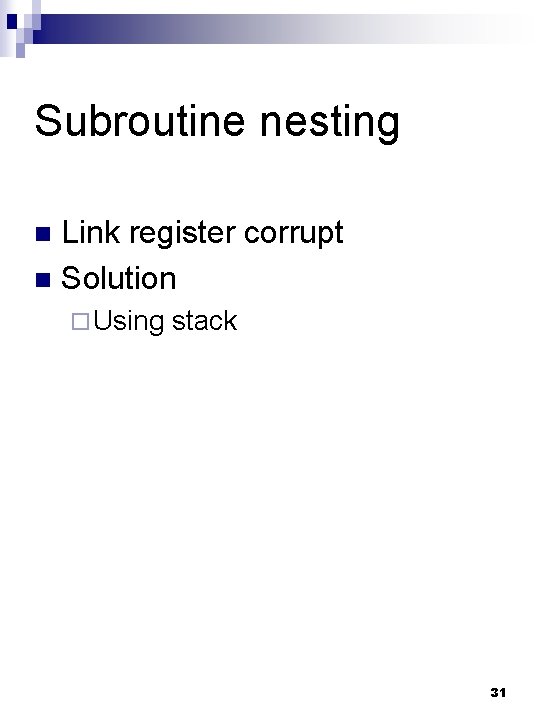

Procedure prologue epilogue n & prologue Move fp, -(sp) (將sp – 4後, 再將fp copy到 stack, 將舊fp(calling proc)存起來) ¨ Move sp, fp (fp sp)建立新的frame pointer ¨ OR ¨ Push bp (將舊bp(calling proc)存起來) ¨ Move sp, bp (bp sp), 建立新的frame pointer ¨ n Epilogue Move fp, sp (sp fp) ¨ Move fp, (sp)+ ¨ RET ¨ Or ¨ Move bp, sp (sp bp) ¨ Pop bp ¨ RET ¨ 35

![saved R 1 堆疊指標 saved R 0 localvar 3 Move SP FP New FP saved [R 1] 堆疊指標 saved [R 0] localvar 3 Move SP, FP New FP](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-36.jpg)

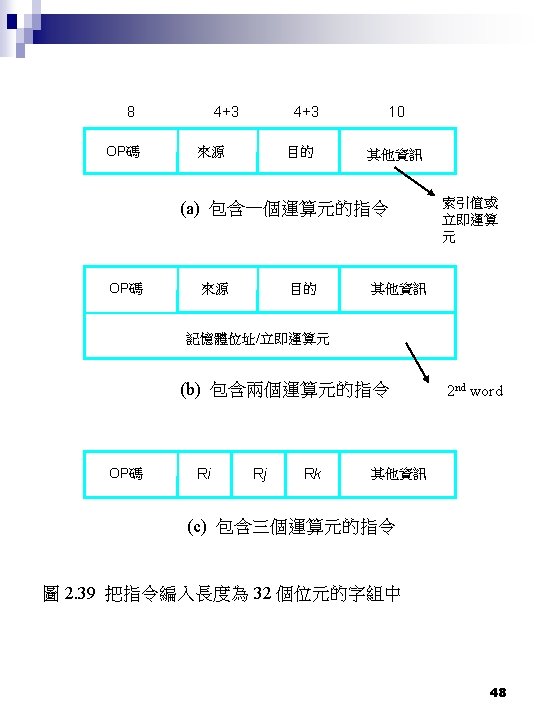

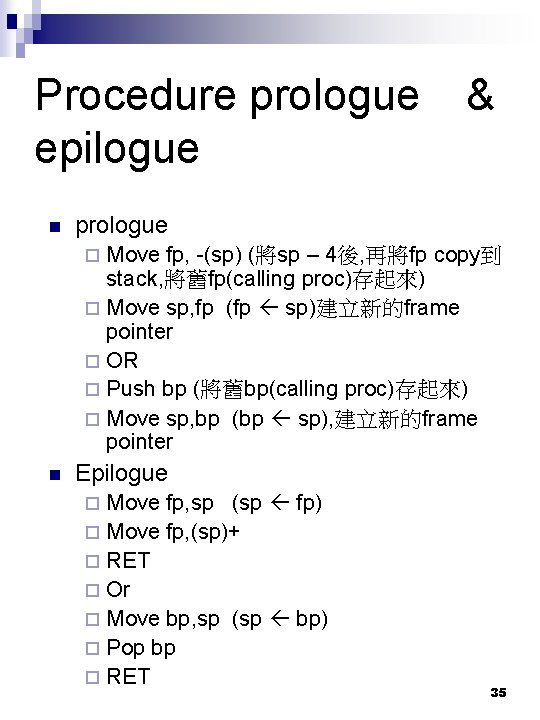

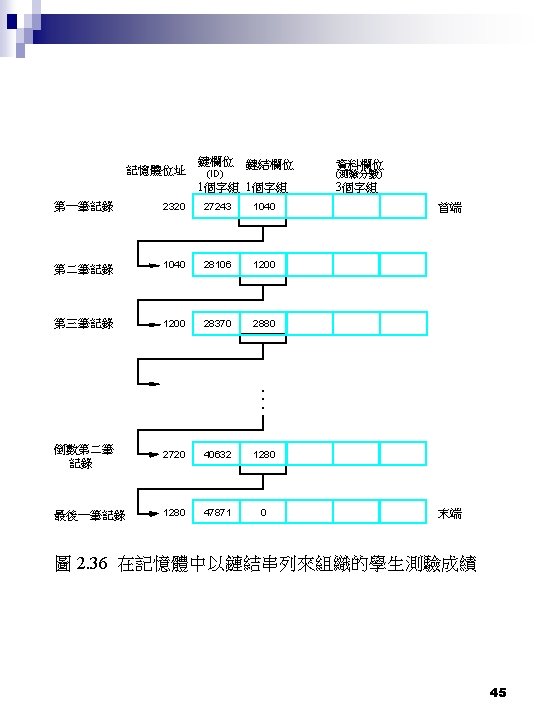

saved [R 1] 堆疊指標 saved [R 0] localvar 3 Move SP, FP New FP 窗格指標 Move FP, -(SP) localvar 2 localvar 1 saved [FP] Return address 被呼叫副常式 的堆疊窗格 Call 指令 param 1 param 2 param 3 呼叫者參數 param 4 舊的TOS 圖 2. 27 副常式的堆疊窗格範例 36

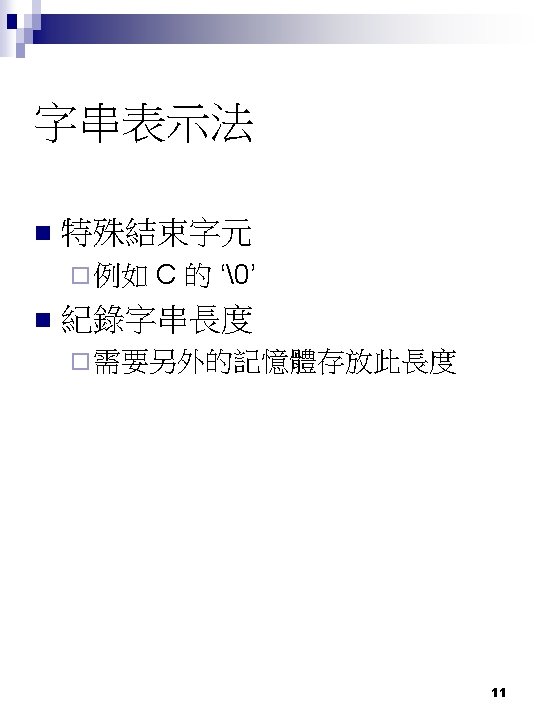

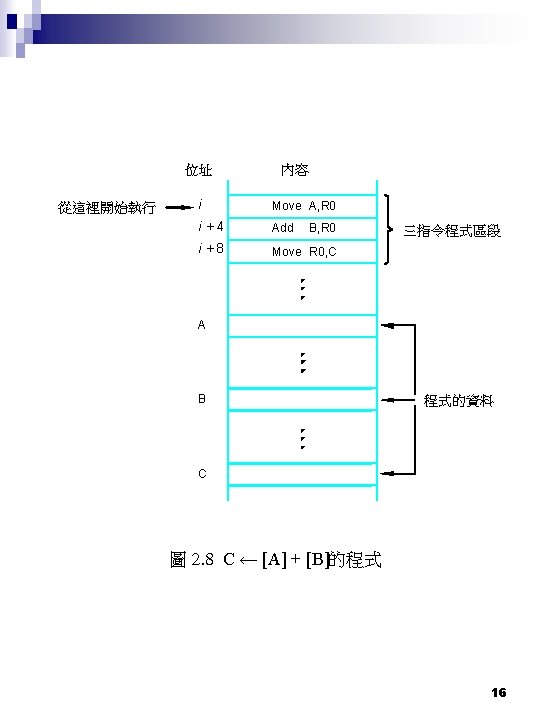

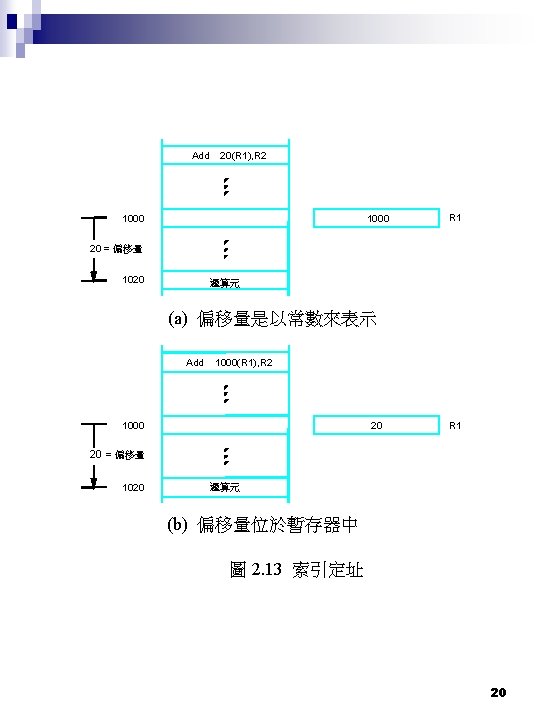

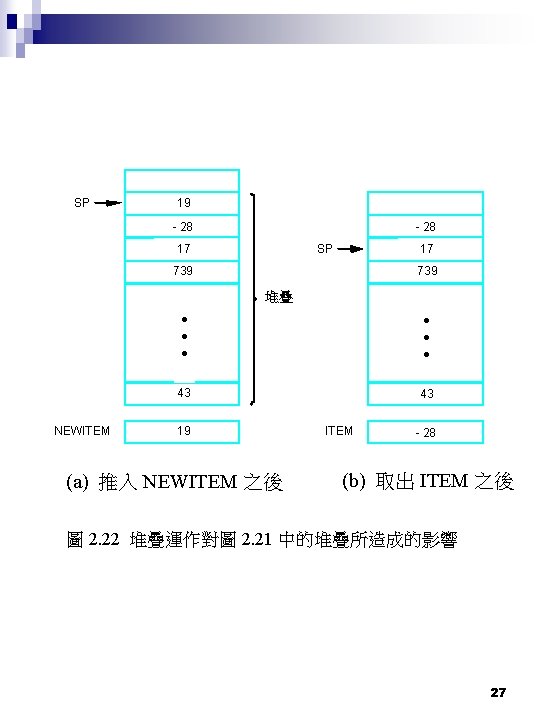

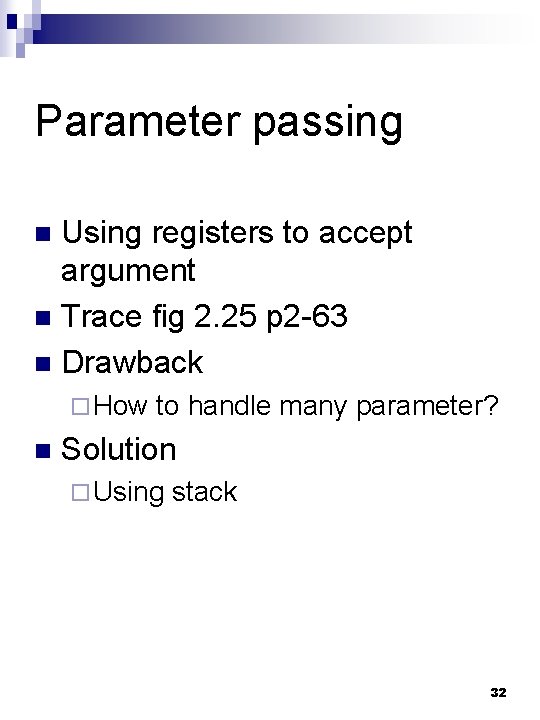

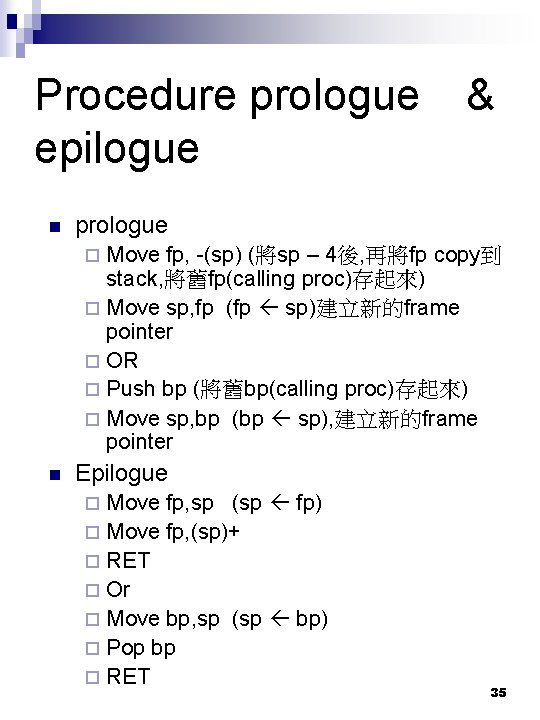

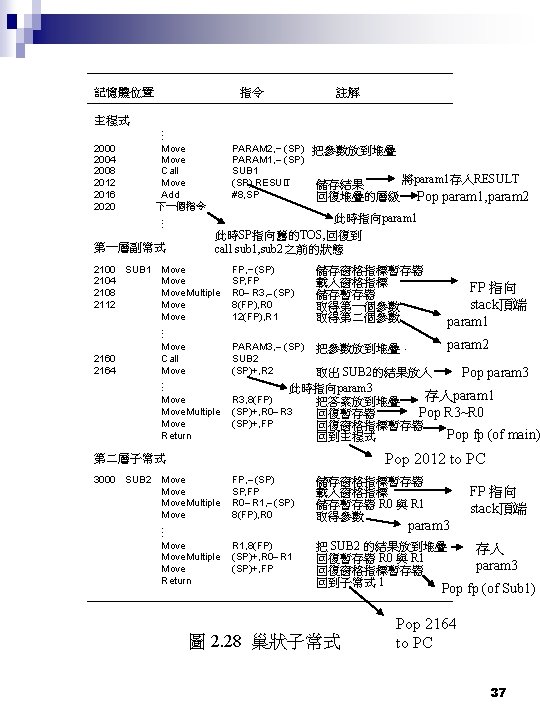

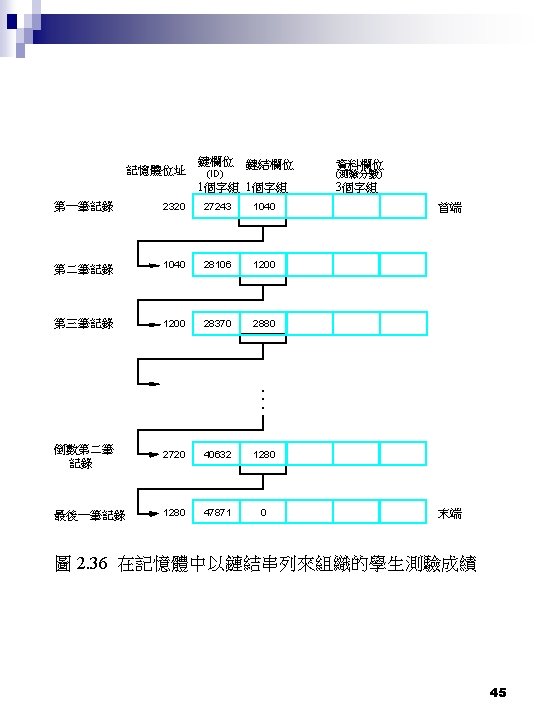

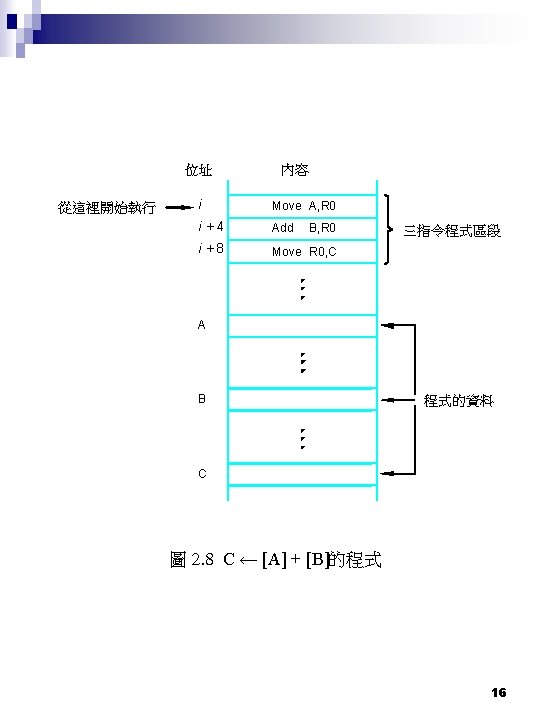

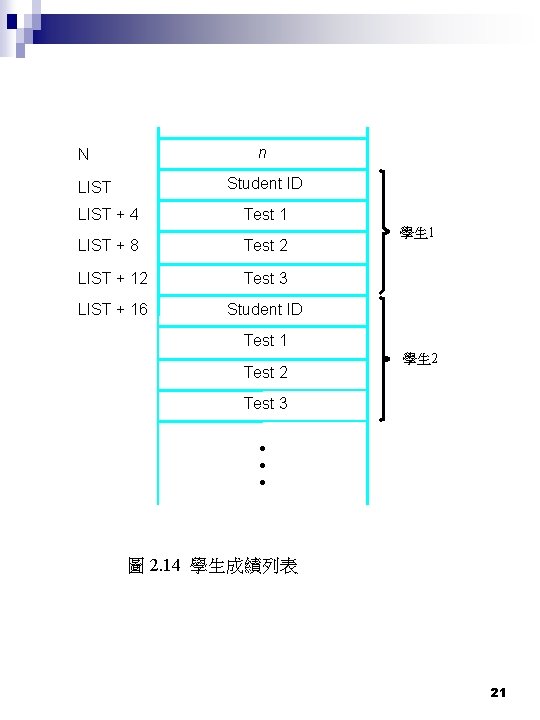

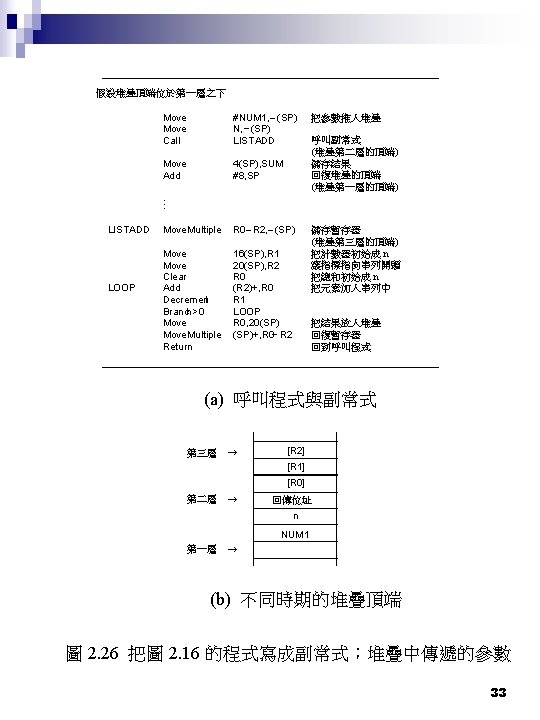

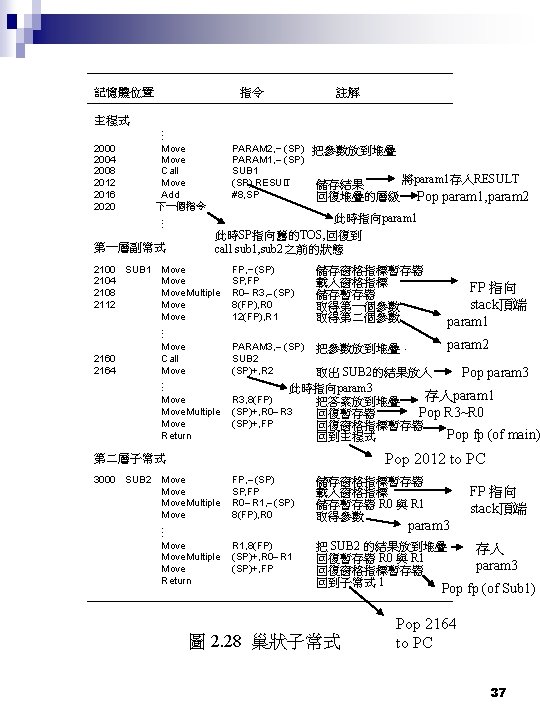

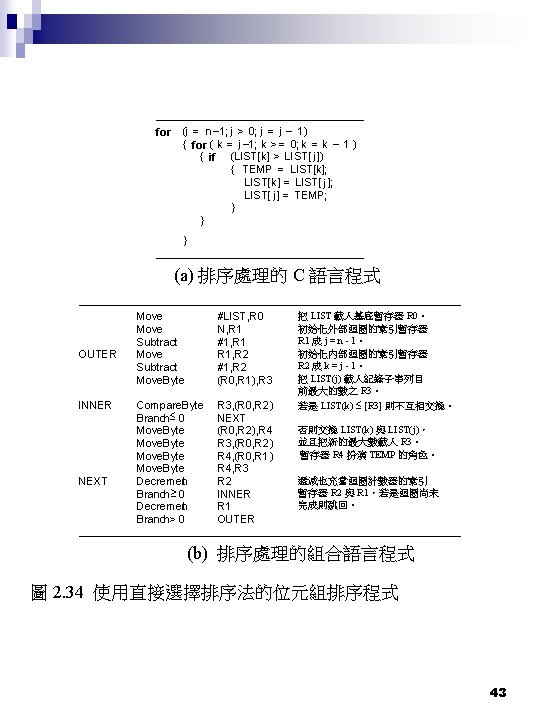

記憶體位置 主程式 2000 2004 2008 2012 2016 2020 指令. . . Move Call Move Add 下一個指令. . . 第一層副常式 2100 SUB 1 2104 2108 2112 2160 2164 PARAM 2, – (SP) PARAM 1, – (SP) SUB 1 (SP), RESULT #8, SP 註解 把參數放到堆疊 將param 1存入RESULT 儲存結果 回復堆疊的層級 Pop param 1, param 2 此時指向param 1 此時SP指向舊的TOS, 回復到 call sub 1, sub 2之前的狀態 Move. Multiple Move. . . FP, – (SP) SP, FP R 0– R 3, – (SP) 8(FP), R 0 12(FP), R 1 儲存窗格指標暫存器 載入窗格指標 儲存暫存器 取得第一個參數 取得第二個參數 FP 指向 stack頂端 param 1 Move Call Move. . . PARAM 3, – (SP) SUB 2 (SP)+, R 2 把參數放到堆疊. param 2 Move. Multiple Move Return 取出 SUB 2的結果放入 Pop param 3 此時指向param 3 存入param 1 R 3, 8(FP) 把答案放到堆疊 (SP)+, R 0– R 3 回復暫存器 Pop R 3~R 0 (SP)+, FP 回復窗格指標暫存器 Pop fp (of main) 回到主程式 Pop 2012 to PC 第二層子常式 3000 SUB 2 Move. Multiple Move. . . FP, – (SP) SP, FP R 0– R 1, – (SP) 8(FP), R 0 v 儲存窗格指標暫存器 載入窗格指標 儲存暫存器 R 0 與 R 1 取得參數 Move. Multiple Move Return R 1, 8(FP) (SP)+, R 0– R 1 (SP)+, FP 把 SUB 2 的結果放到堆疊 回復暫存器 R 0 與 R 1 回復窗格指標暫存器 回到子常式 1 FP 指向 stack頂端 param 3 圖 2. 28 巢狀子常式 存入 param 3 Pop fp (of Sub 1) Pop 2164 to PC 37

![低記憶體位址 R 1 from SUB 1 R 0 from SUB 1 FP from SUB 低記憶體位址 [R 1] from SUB 1 [R 0] from SUB 1 [FP] from SUB](https://slidetodoc.com/presentation_image_h/7f2f372e1eb5cbdc4e7559d88590ed81/image-38.jpg)

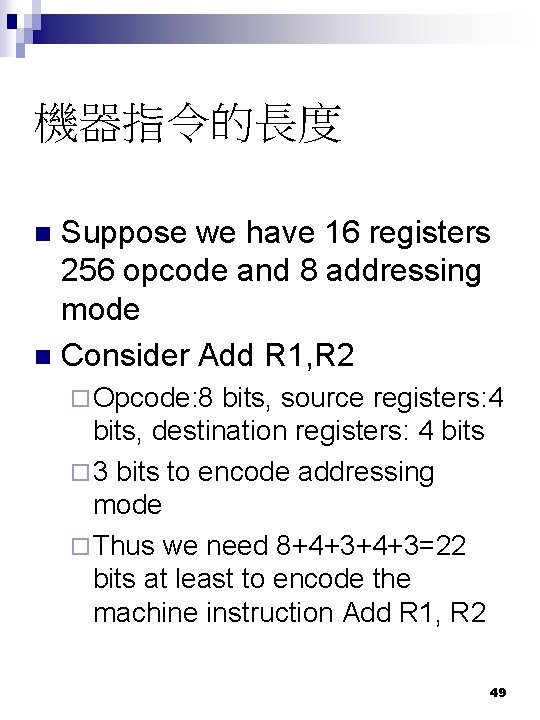

低記憶體位址 [R 1] from SUB 1 [R 0] from SUB 1 [FP] from SUB 1 FP 第二個副常式 的堆疊窗格 2164 param 3 [R 3] from Main [R 2] from Main [R 1] from Main [R 0] from Main FP [FP] from Main 第一個副常式 的堆疊窗格 2012 param 1 param 2 高記憶體位址 舊的TOS 圖 2. 29 圖 2. 28 的堆疊窗格 38

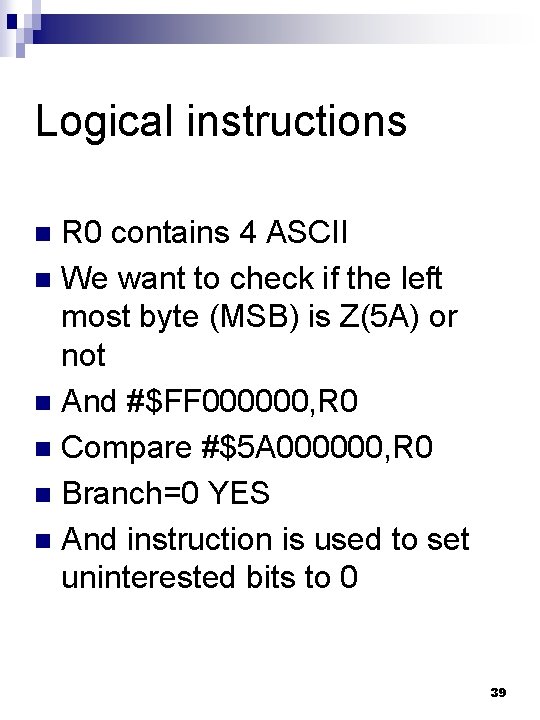

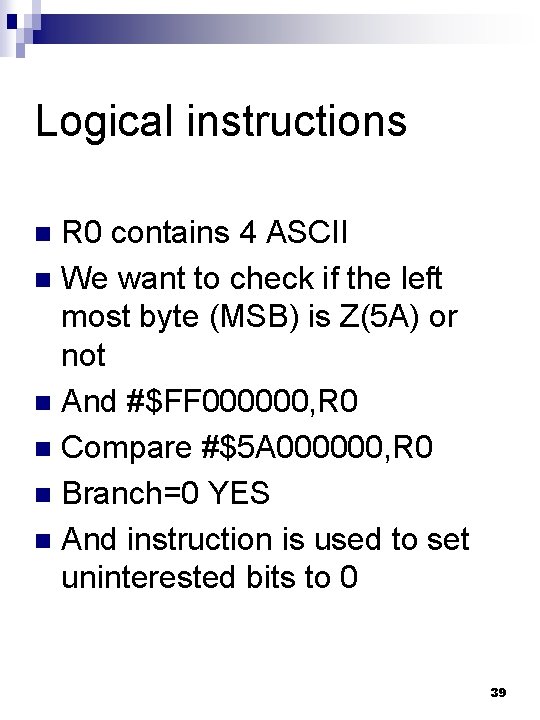

Logical instructions R 0 contains 4 ASCII n We want to check if the left most byte (MSB) is Z(5 A) or not n And #$FF 000000, R 0 n Compare #$5 A 000000, R 0 n Branch=0 YES n And instruction is used to set uninterested bits to 0 n 39

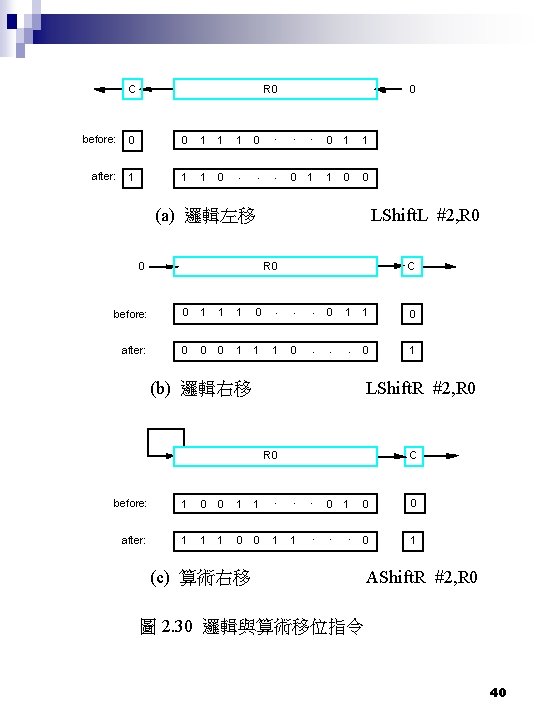

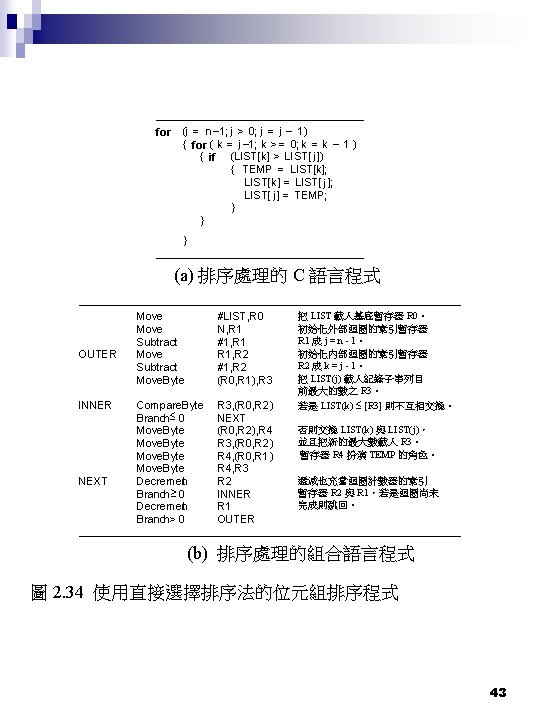

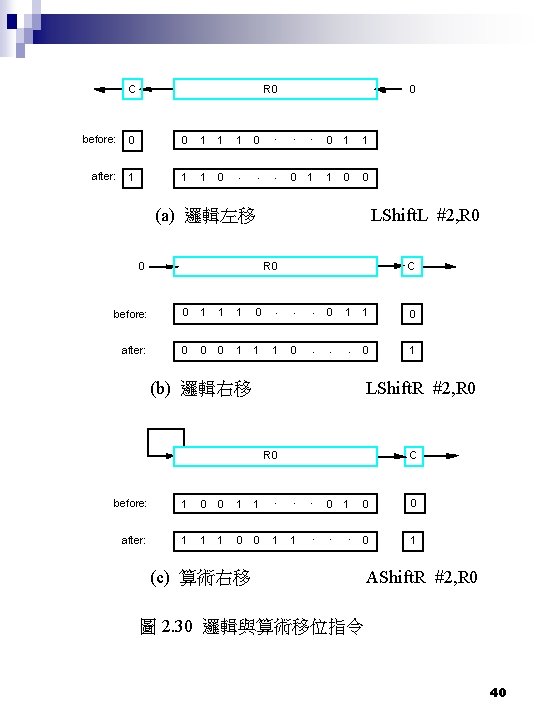

C R 0 . . . before: 0 0 1 1 1 after: 1 1 1 0 . . . 0 0 0 1 1 1 0 0 (a) 邏輯左移 LShift. L #2, R 0 0 R 0 C before: 0 1 1 1 0 . . . after: 0 0 0 1 1 1 0 0 1 1 0 . . . 0 1 (b) 邏輯右移 LShift. R #2, R 0 C before: 1 0 0 1 1 . . . after: 1 1 1 0 0 . . . 0 1 0 (c) 算術右移 AShift. R #2, R 0 圖 2. 30 邏輯與算術移位指令 40

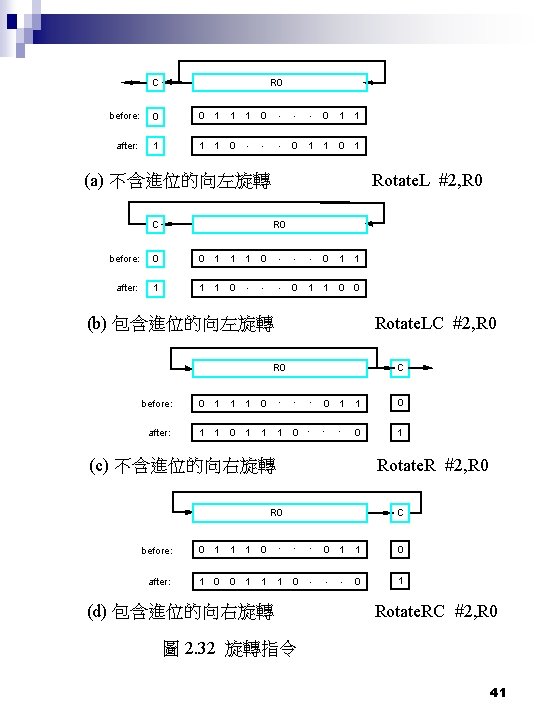

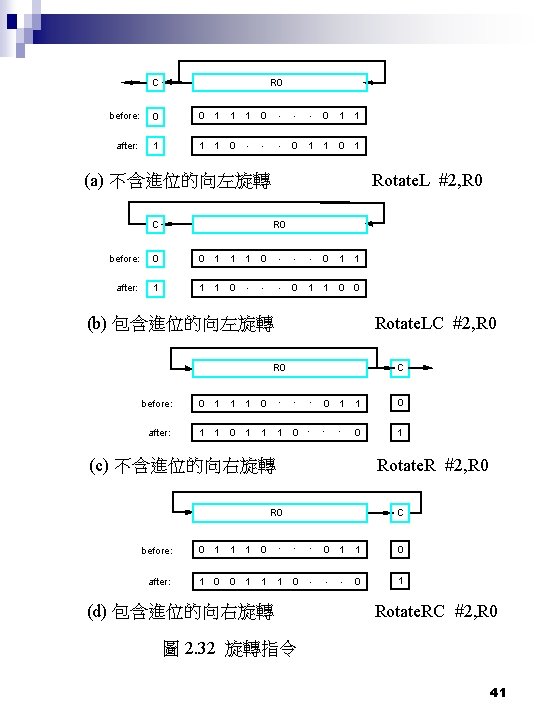

C R 0 before: 0 0 1 1 1 after: 1 1 1 0 . . . 0 0 1 1 0 1 (a) 不含進位的向左旋轉 C Rotate. L #2, R 0 before: 0 0 1 1 1 after: 1 1 1 0 . . . 0 0 1 1 0 0 (b) 包含進位的向左旋轉 Rotate. LC #2, R 0 C . . . before: 0 1 1 1 0 after: 1 1 0 1 1 1 0 0 1 . . . 1 0 0 1 (c) 不含進位的向右旋轉 Rotate. R #2, R 0 C . . . before: 0 1 1 1 0 after: 1 0 0 1 1 1 0 (d) 包含進位的向右旋轉 0 1 1 0 . . . 0 1 Rotate. RC #2, R 0 圖 2. 32 旋轉指令 41

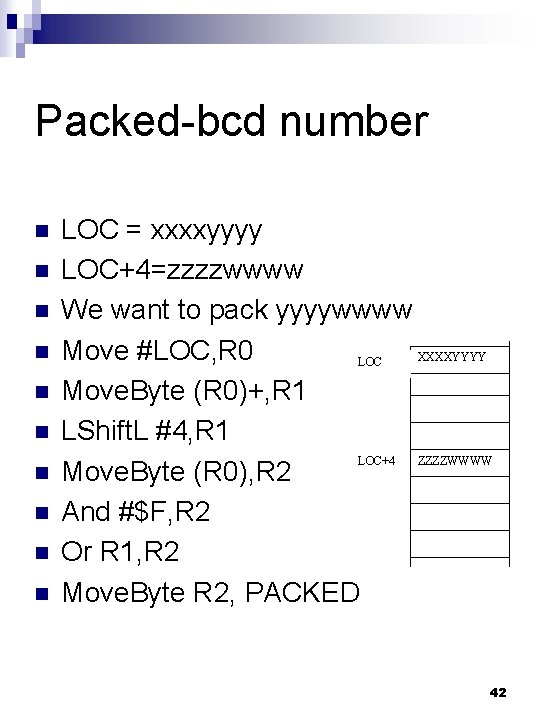

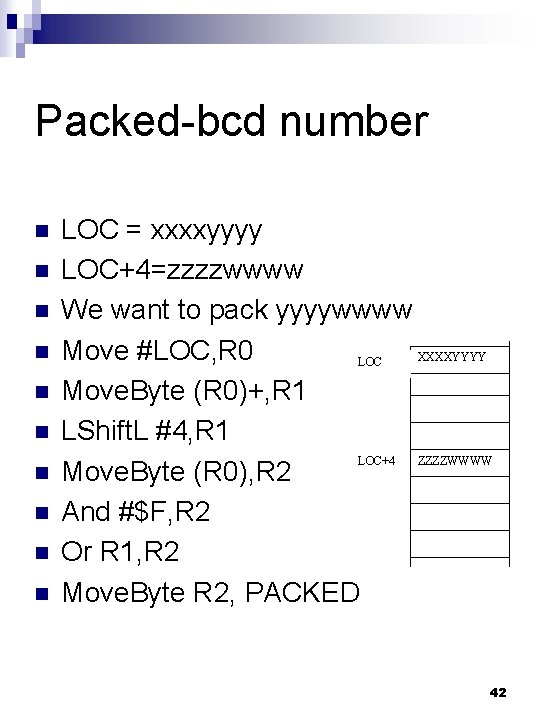

Packed-bcd number n n n n n LOC = xxxxyyyy LOC+4=zzzzwwww We want to pack yyyywwww Move #LOC, R 0 XXXXYYYY LOC Move. Byte (R 0)+, R 1 LShift. L #4, R 1 LOC+4 ZZZZWWWW Move. Byte (R 0), R 2 And #$F, R 2 Or R 1, R 2 Move. Byte R 2, PACKED 42

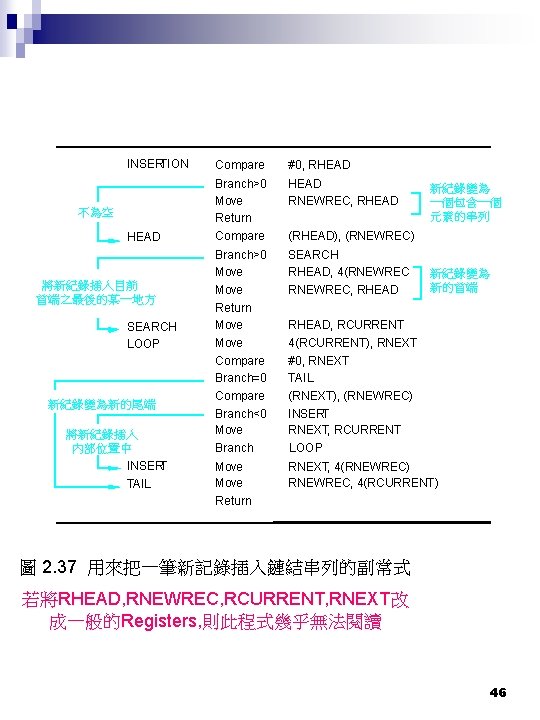

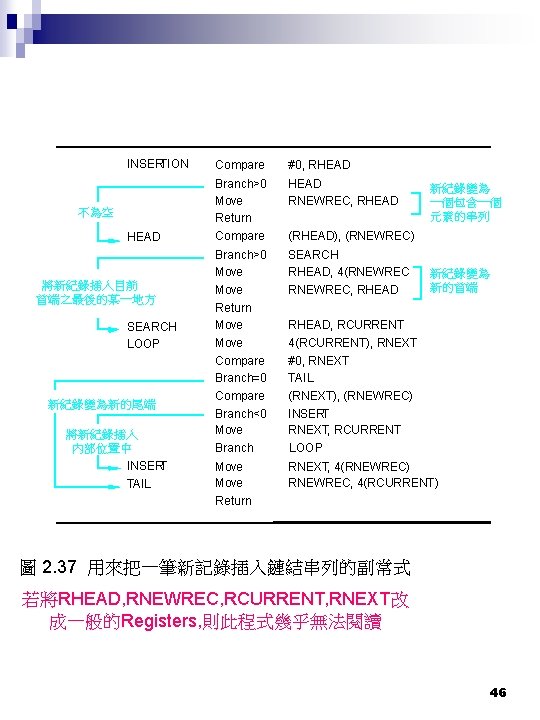

INSERTION Compare #0, RHEAD RNEWREC, RHEAD Branch>0 Move Return Compare Branch>0 Move Return Move Compare Branch=0 Compare Branch<0 Move Branch SEARCH RHEAD, 4(RNEWREC) RNEWREC, RHEAD Move Return RNEXT, 4(RNEWREC) RNEWREC, 4(RCURRENT) 不為空 將新紀錄插入目前 首端之最後的某一地方 SEARCH LOOP 新紀錄變為新的尾端 將新紀錄插入 內部位置中 INSERT TAIL 新紀錄變為 一個包含一個 元素的串列 (RHEAD), (RNEWREC) 新紀錄變為 新的首端 RHEAD, RCURRENT 4(RCURRENT), RNEXT #0, RNEXT TAIL (RNEXT), (RNEWREC) INSERT RNEXT, RCURRENT LOOP 圖 2. 37 用來把一筆新記錄插入鏈結串列的副常式 若將RHEAD, RNEWREC, RCURRENT, RNEXT改 成一般的Registers, 則此程式幾乎無法閱讀 46

刪除一筆紀錄 n Trace fig 2. 38 p 2 -88 47

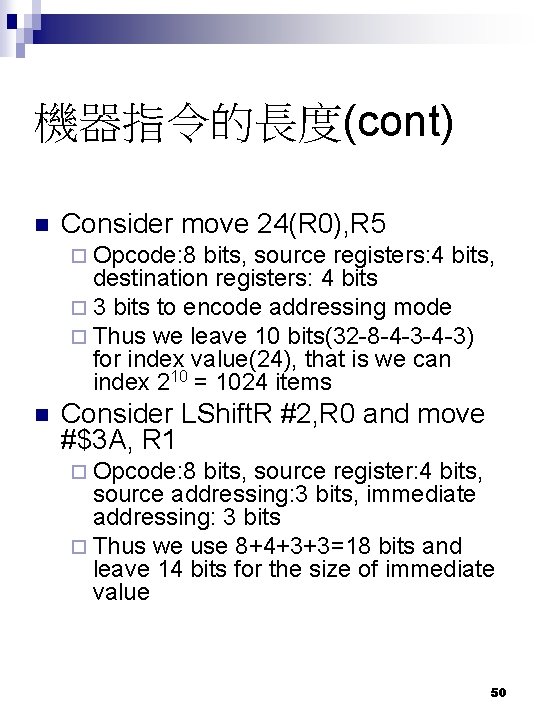

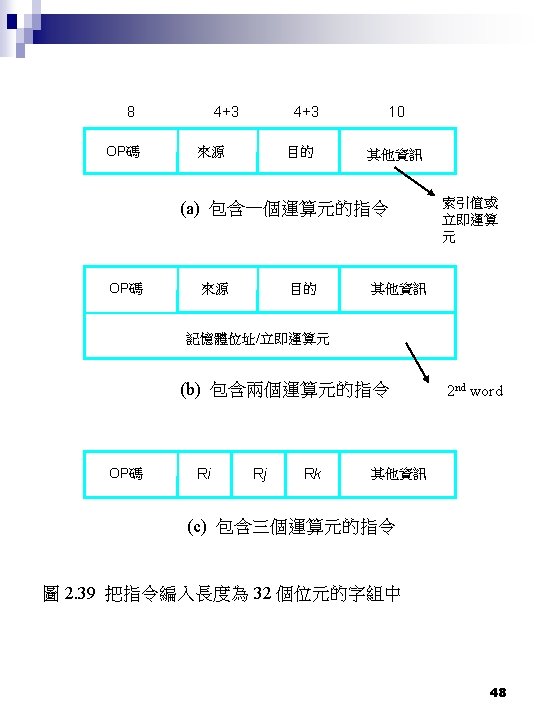

機器指令的長度 Suppose we have 16 registers 256 opcode and 8 addressing mode n Consider Add R 1, R 2 n ¨ Opcode: 8 bits, source registers: 4 bits, destination registers: 4 bits ¨ 3 bits to encode addressing mode ¨ Thus we need 8+4+3=22 bits at least to encode the machine instruction Add R 1, R 2 49

機器指令的長度(cont) n Consider move 24(R 0), R 5 ¨ Opcode: 8 bits, source registers: 4 bits, destination registers: 4 bits ¨ 3 bits to encode addressing mode ¨ Thus we leave 10 bits(32 -8 -4 -3) for index value(24), that is we can index 210 = 1024 items n Consider LShift. R #2, R 0 and move #$3 A, R 1 ¨ Opcode: 8 bits, source register: 4 bits, source addressing: 3 bits, immediate addressing: 3 bits ¨ Thus we use 8+4+3+3=18 bits and leave 14 bits for the size of immediate value 50

機器指令的長度(cont) n Consider Branch>0 LOOP ¨ ¨ n Opcode: 8 bits We have 24 bits for branch offset, consider positive and negative offset then we have 223 offset Consider Move R 2, LOC Opcode: 8 bits, source registers: 4 bits, source addressing: 3 bits, absolute addressing(LOC) 3 bits ¨ We use 8+4+3+3=18 bits and leave 14 bits for representing the address of LOC (cannot address 32 bits memory space) ¨ Solution: use 2 nd word to represent the whole address then we can encode And #$FF 000000, R 2 where FF 000000 is in the 2 nd word ¨ 51

機器指令的長度(cont) If we allow memory to memory operation(rarely seen in modern processor) then we need more longer instruction n Consider move LOC 1, LOC 2 n ¨ We need 2 nd for LOC 1, and 3 rd for LOC 2 52

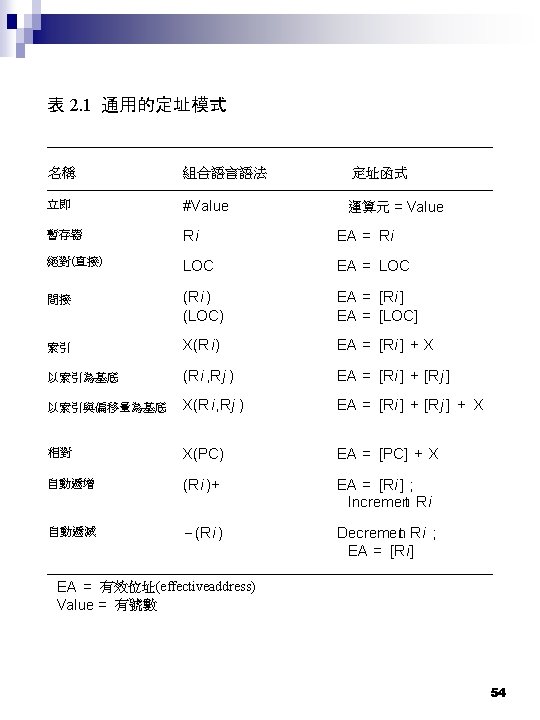

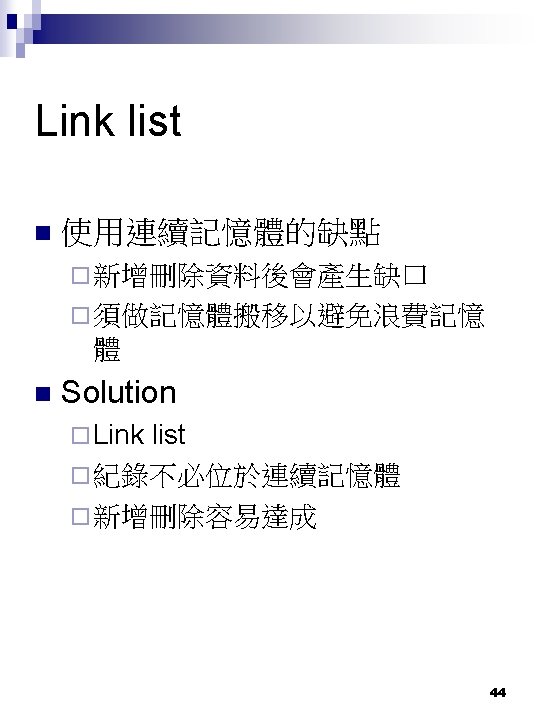

CISC vs. RISC n n CISC ¨ 允許machine instruction的長度不一, 例如Intel machine instructions的長度可以有1 byte, 2 bytes, 3 bytes, 4 bytes ¨ 使用多個字組可以實作較複雜, 較接近高階程式 語言作業方式的指令 ¨ 包含較多且較複雜的指令但完成一件事所需指 令數較少 RISC ¨ 20% of the instructions in a computer did 80% of the work (by John Cocke of IBM Research ) ¨ 所有指令長度固定(例如32 bits) ¨ 所有的ALU計算只能作用在register-register(不 能有register-memory) ¨ Memory reference只能用Load (for read), Store (for write)指令 ¨ 包含較少且較簡單的指令但完成一件事所需指 令數較多 53