SI u C 2 deo 2013 Nenad Jovii

- Slides: 33

SI u. C 2. deo 2013 Nenad Jovičić

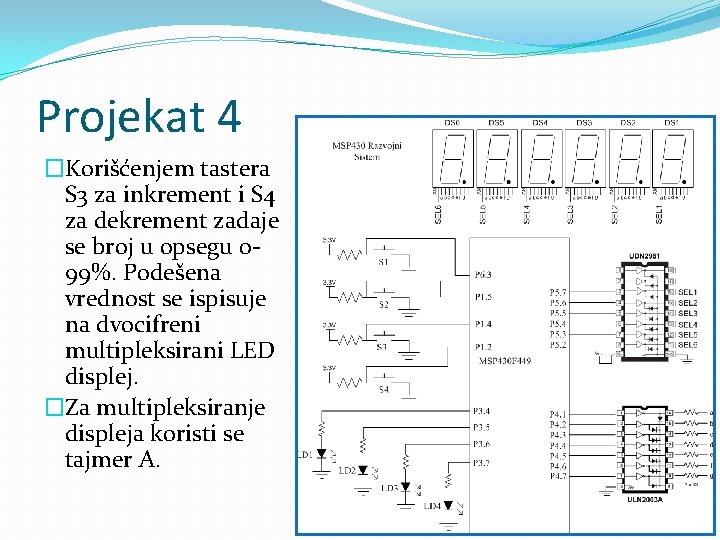

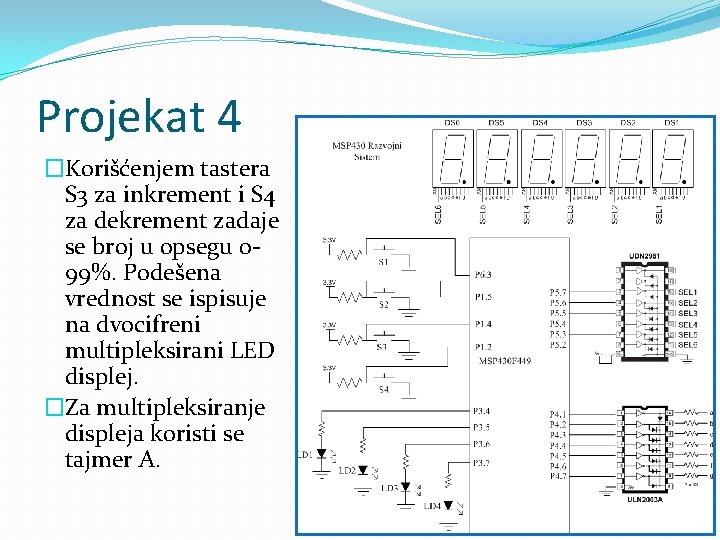

Projekat 4 �Korišćenjem tastera S 3 za inkrement i S 4 za dekrement zadaje se broj u opsegu 099%. Podešena vrednost se ispisuje na dvocifreni multipleksirani LED displej. �Za multipleksiranje displeja koristi se tajmer A.

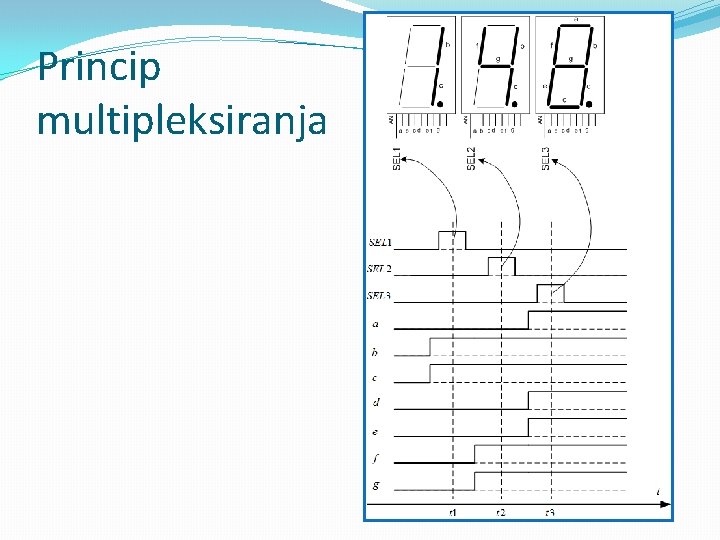

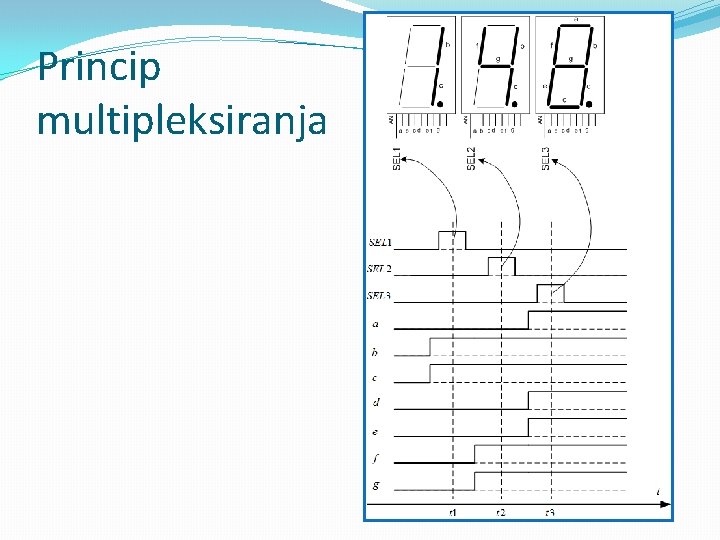

Princip multipleksiranja

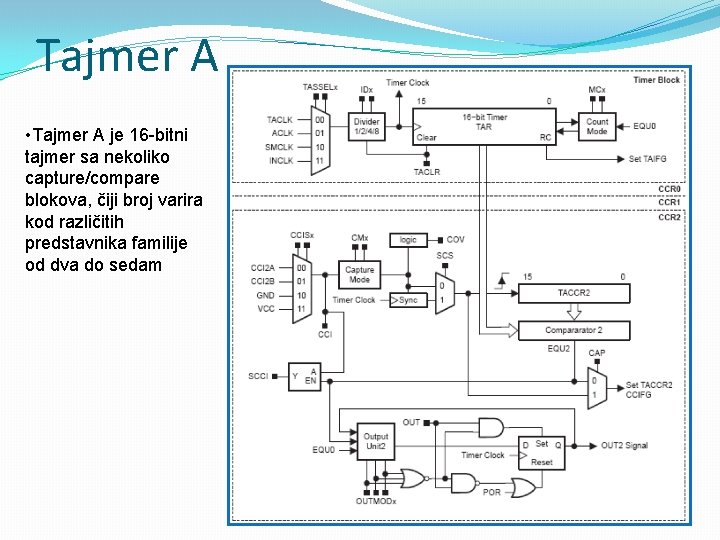

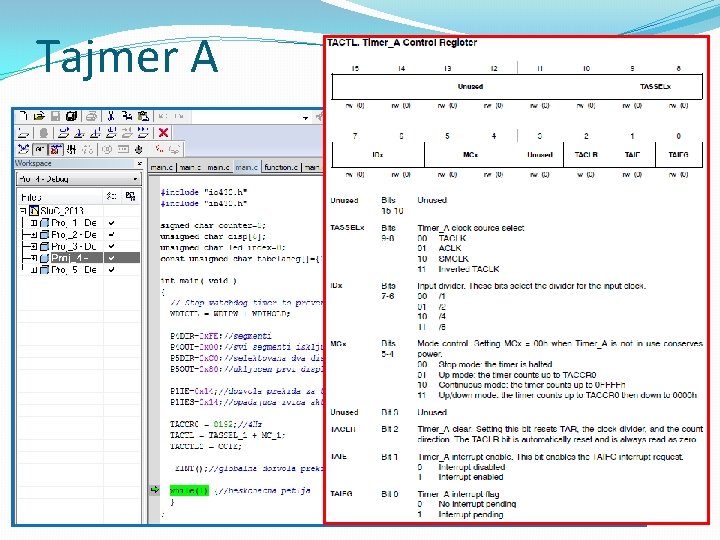

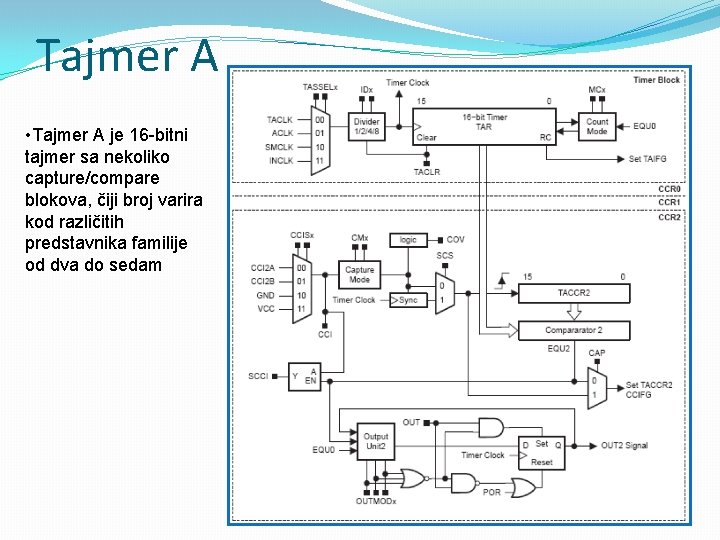

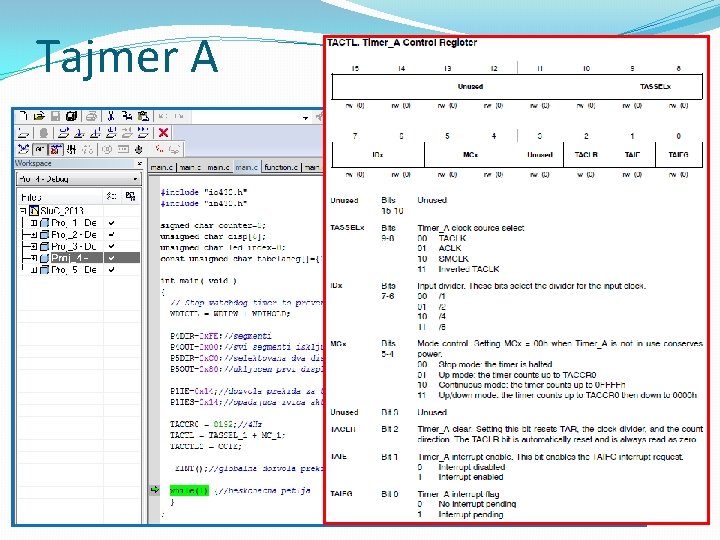

Tajmer A • Tajmer A je 16 -bitni tajmer sa nekoliko capture/compare blokova, čiji broj varira kod različitih predstavnika familije od dva do sedam

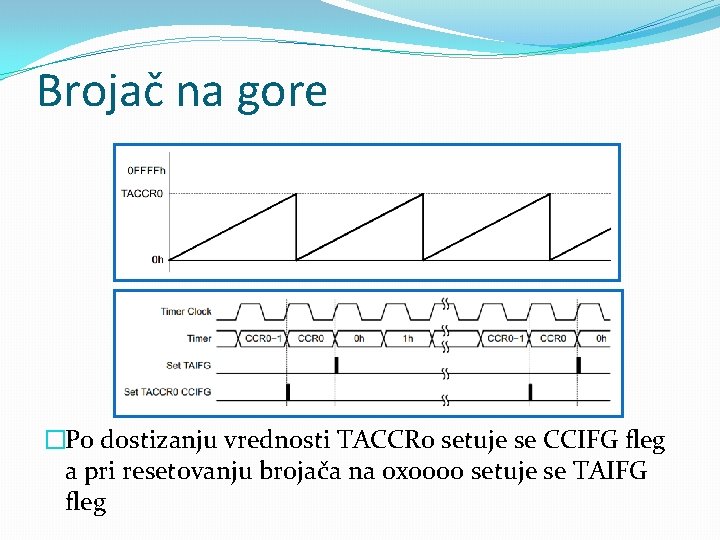

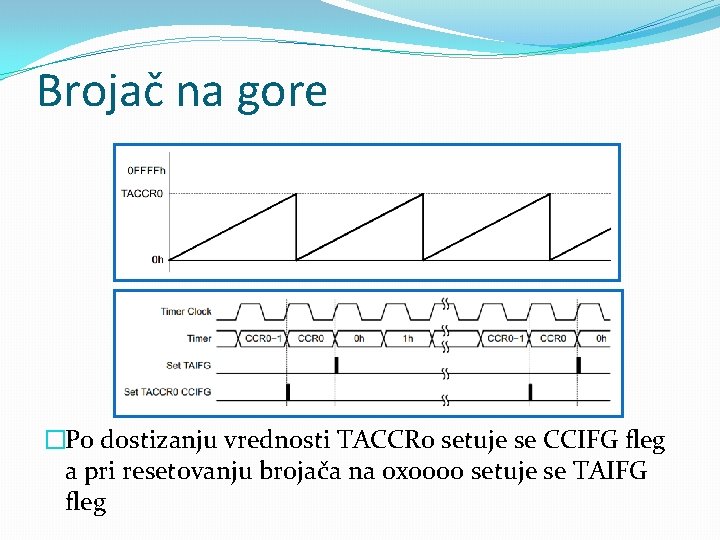

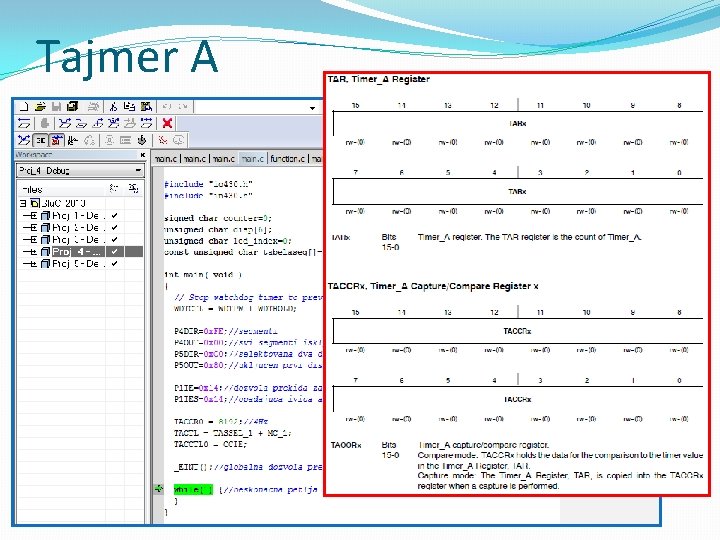

Brojač na gore �Po dostizanju vrednosti TACCR 0 setuje se CCIFG fleg a pri resetovanju brojača na 0 x 0000 setuje se TAIFG fleg

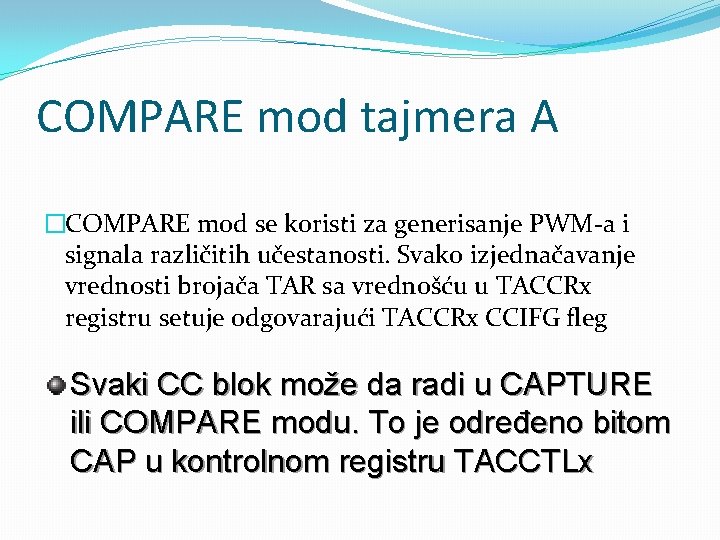

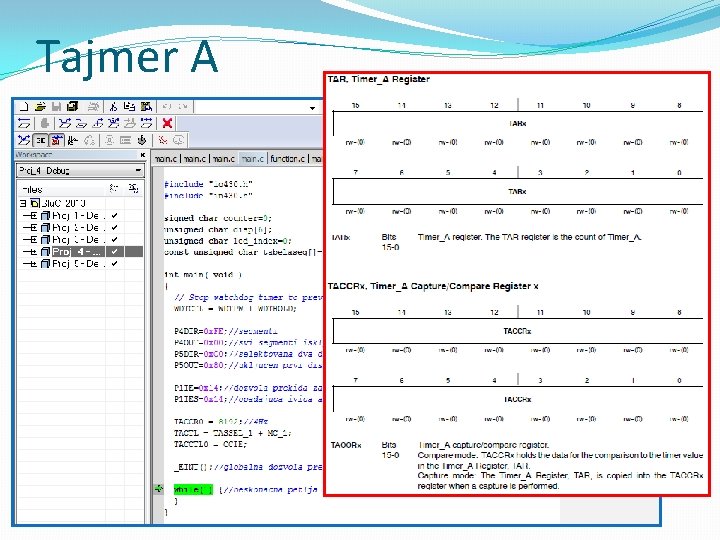

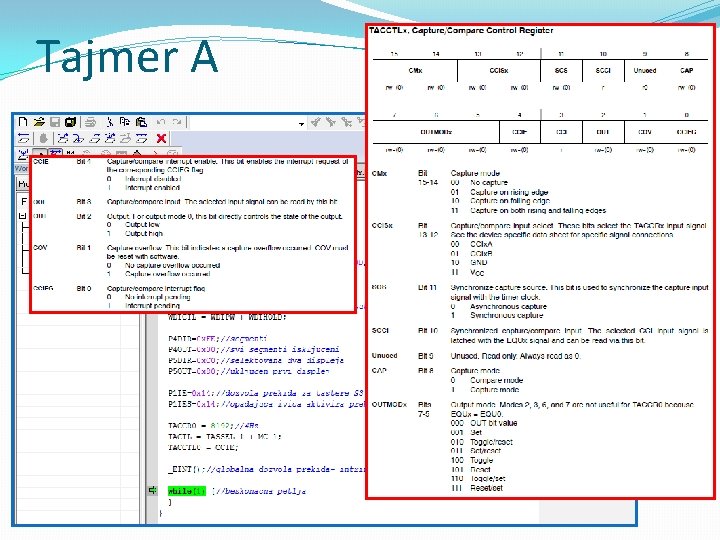

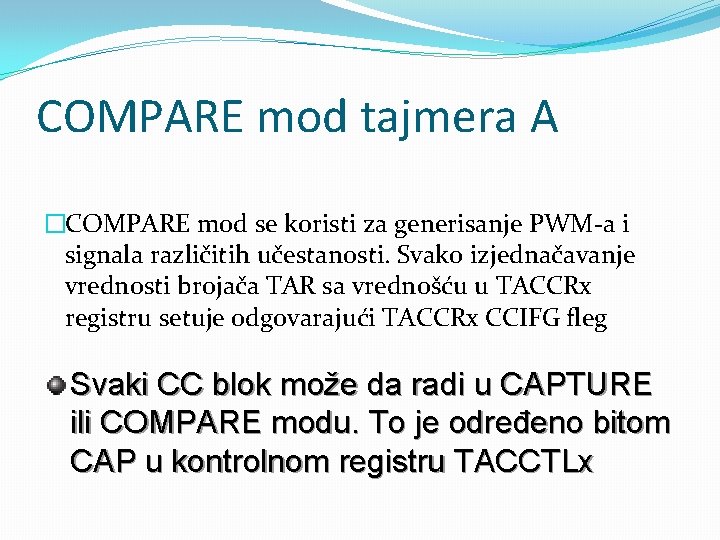

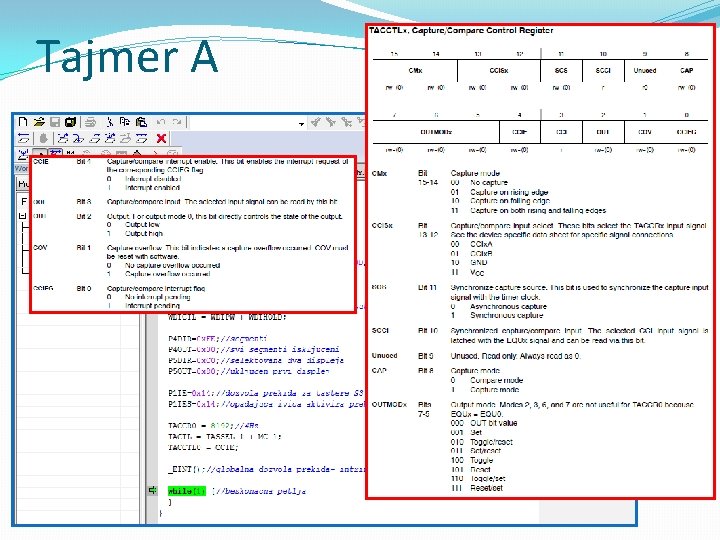

COMPARE mod tajmera A �COMPARE mod se koristi za generisanje PWM-a i signala različitih učestanosti. Svako izjednačavanje vrednosti brojača TAR sa vrednošću u TACCRx registru setuje odgovarajući TACCRx CCIFG fleg Svaki CC blok može da radi u CAPTURE ili COMPARE modu. To je određeno bitom CAP u kontrolnom registru TACCTLx

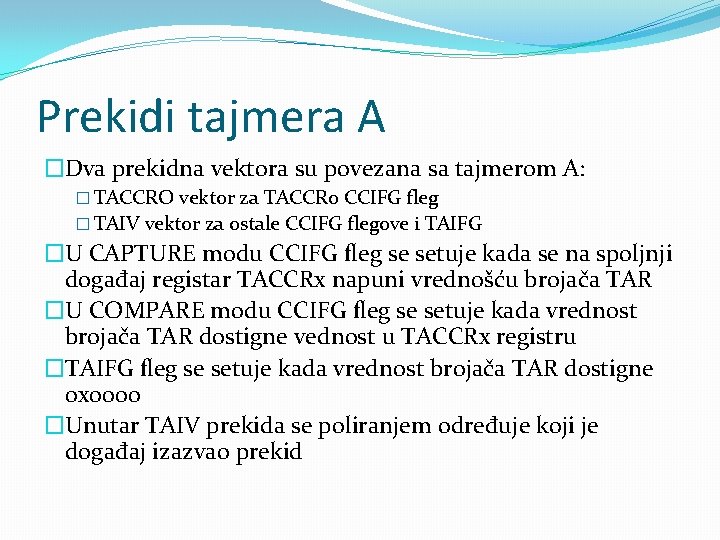

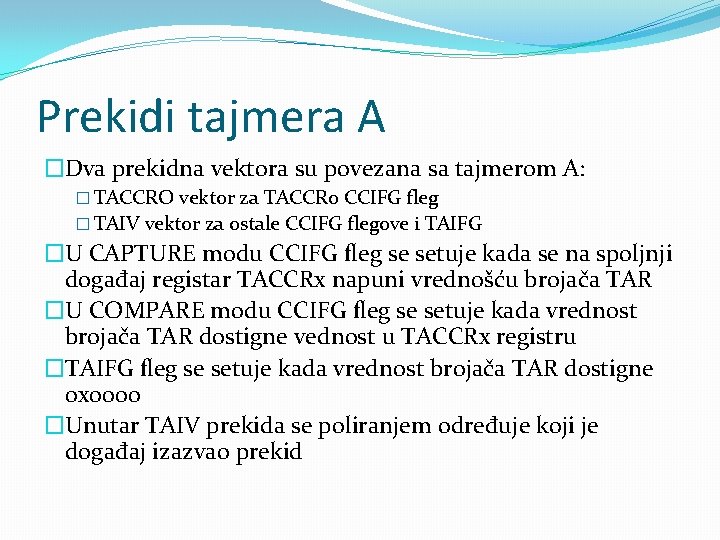

Prekidi tajmera A �Dva prekidna vektora su povezana sa tajmerom A: � TACCRO vektor za TACCR 0 CCIFG fleg � TAIV vektor za ostale CCIFG flegove i TAIFG �U CAPTURE modu CCIFG fleg se setuje kada se na spoljnji događaj registar TACCRx napuni vrednošću brojača TAR �U COMPARE modu CCIFG fleg se setuje kada vrednost brojača TAR dostigne vednost u TACCRx registru �TAIFG fleg se setuje kada vrednost brojača TAR dostigne 0 x 0000 �Unutar TAIV prekida se poliranjem određuje koji je događaj izazvao prekid

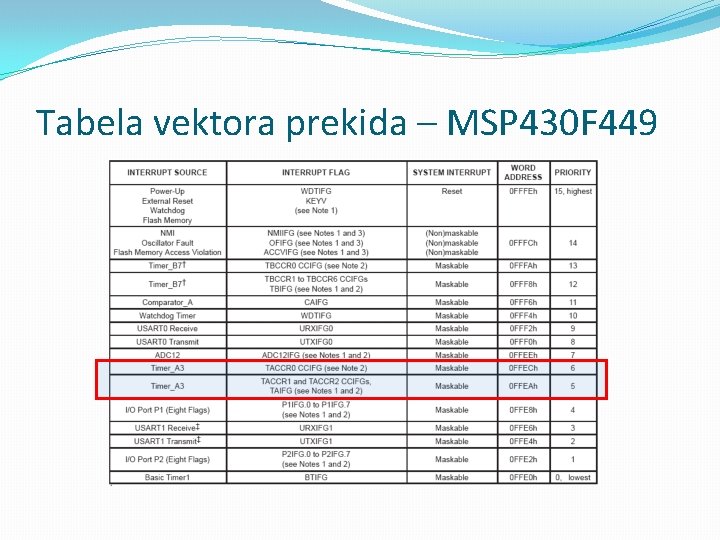

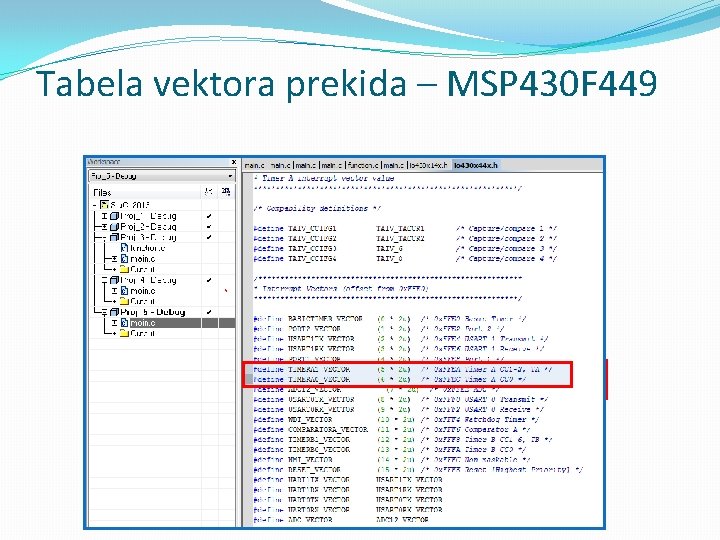

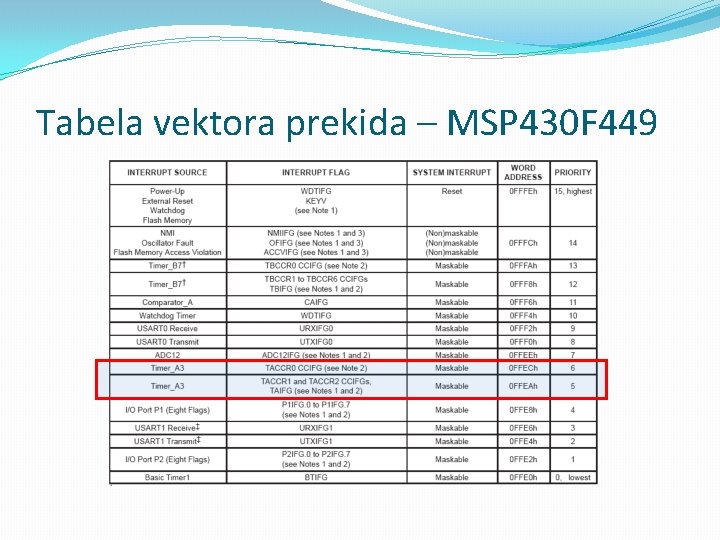

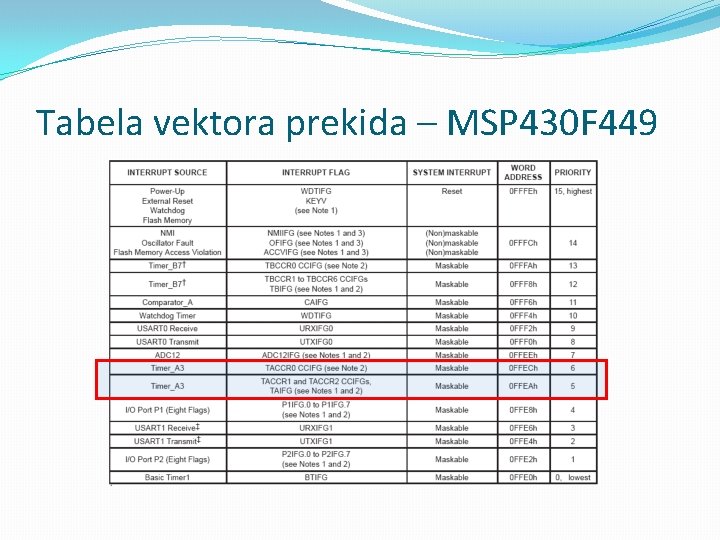

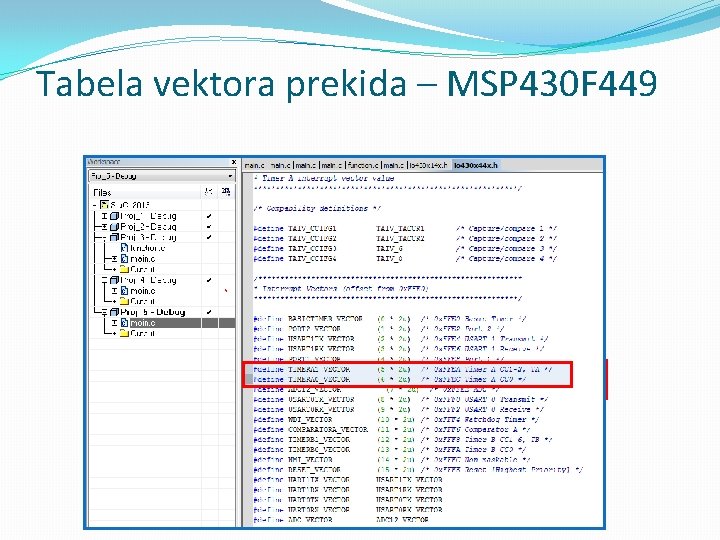

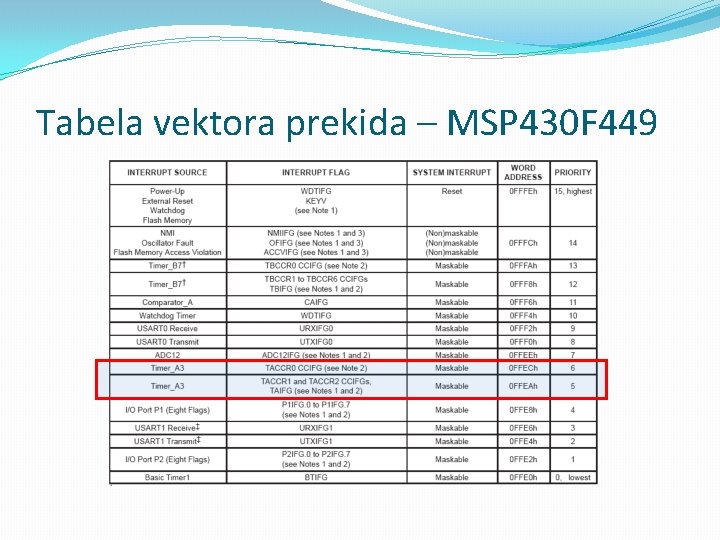

Tabela vektora prekida – MSP 430 F 449

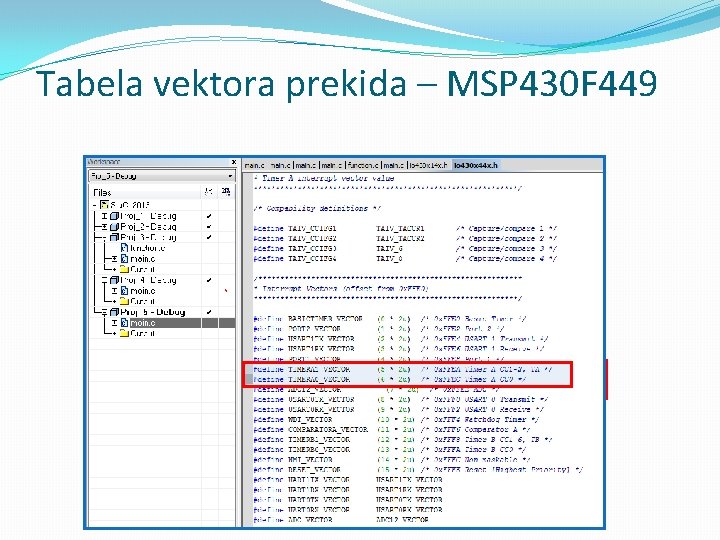

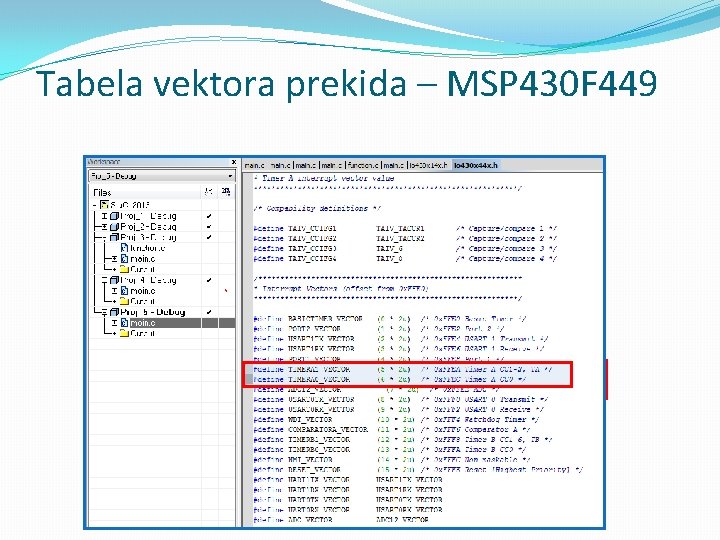

Tabela vektora prekida – MSP 430 F 449

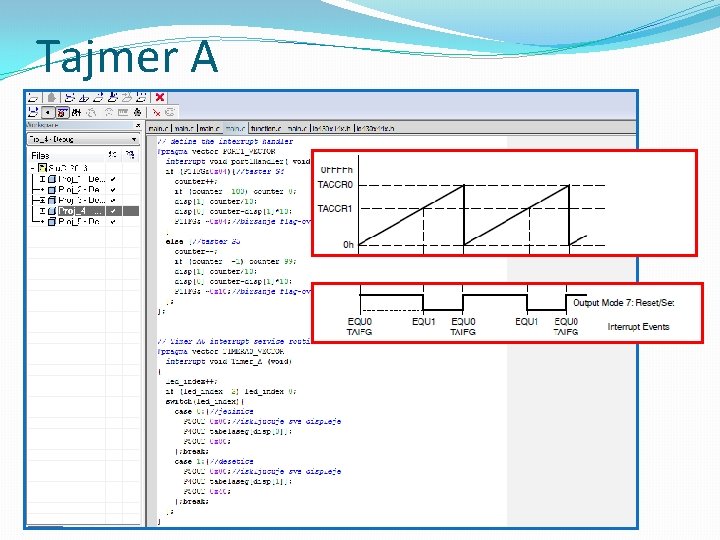

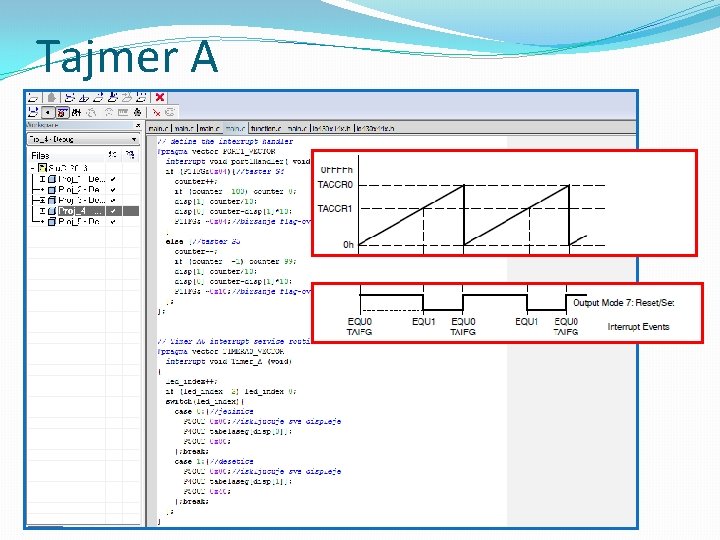

Tajmer A

Tajmer A

Tajmer A

Tajmer A

Zadatak 4 �Promeniti učestanost multipleksiranja tako da iznosi 100 Hz. �Hint: brojač se taktuje sa 32, 768 k. Hz, pa odatle sledi moduo =. . . �Modifikovati projekat 4 tako da se multipleksiraju 3 displeja, i da se podešava trocifreni broj.

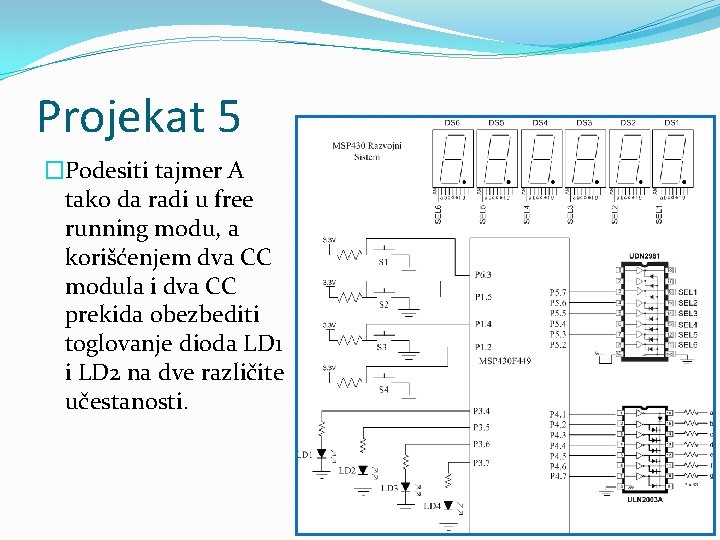

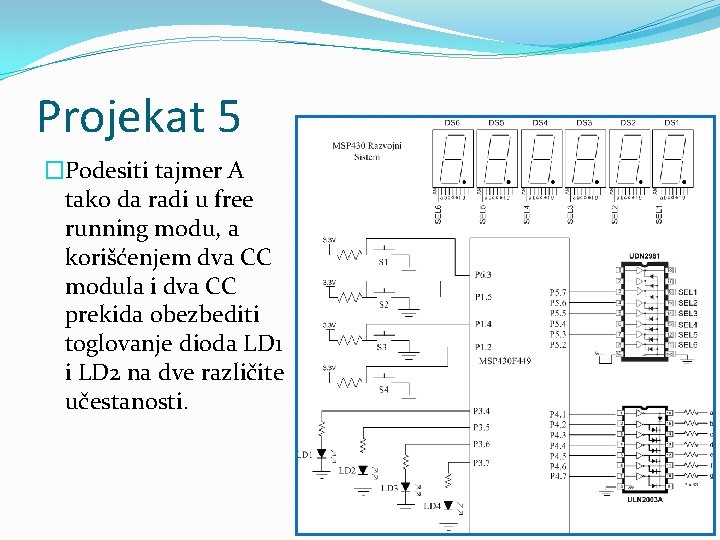

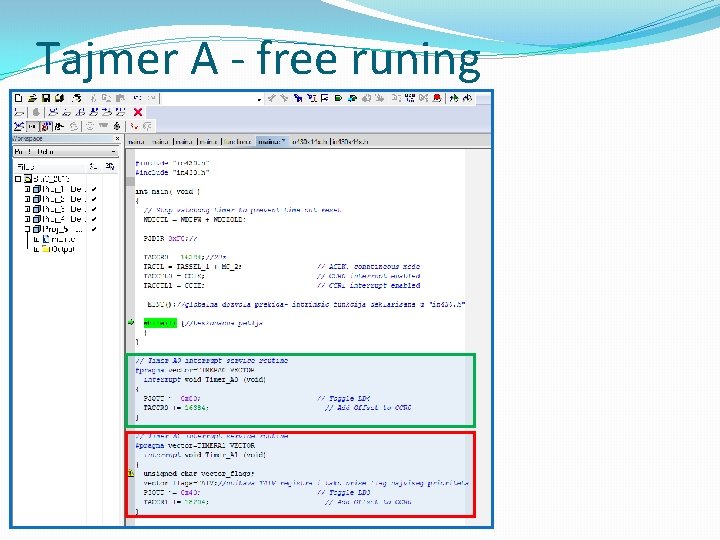

Projekat 5 �Podesiti tajmer A tako da radi u free running modu, a korišćenjem dva CC modula i dva CC prekida obezbediti toglovanje dioda LD 1 i LD 2 na dve različite učestanosti.

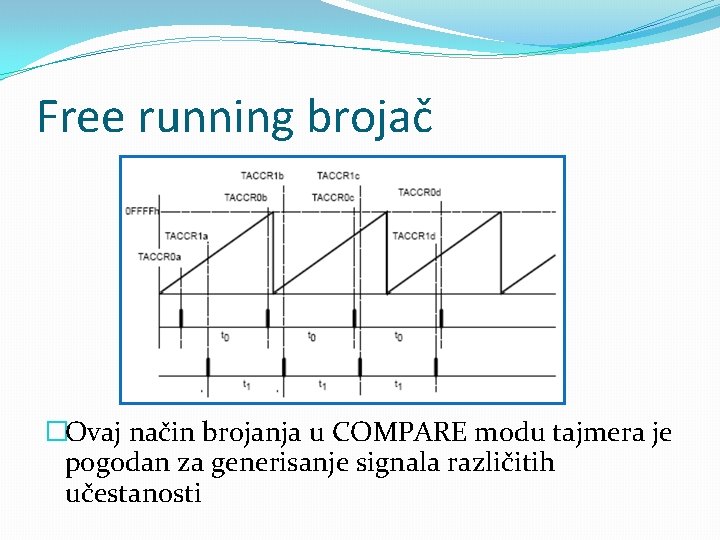

Ostali modovi rada brojača TAR

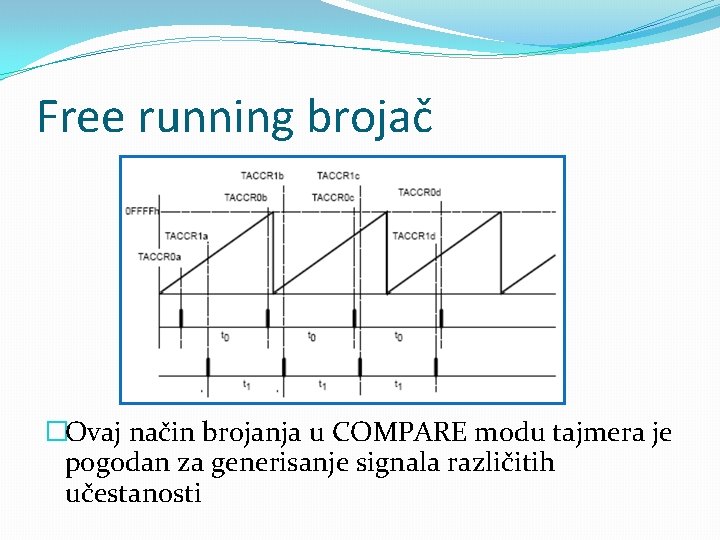

Free running brojač �Ovaj način brojanja u COMPARE modu tajmera je pogodan za generisanje signala različitih učestanosti

Tabela vektora prekida – MSP 430 F 449

Tabela vektora prekida – MSP 430 F 449

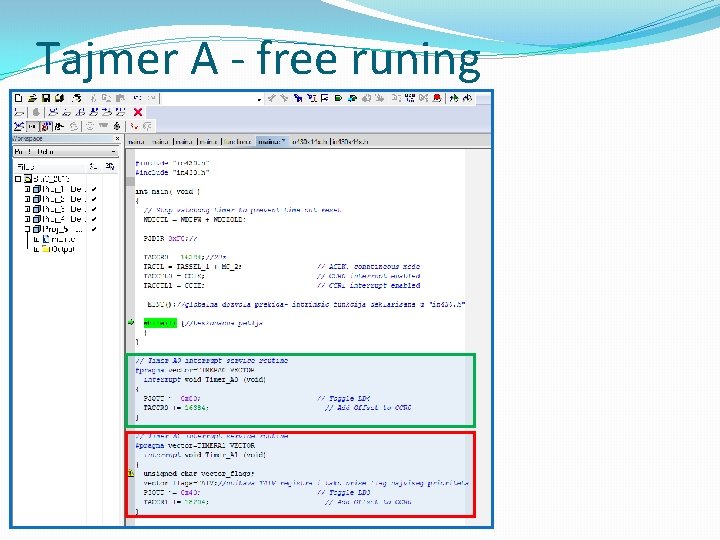

Tajmer A - free runing

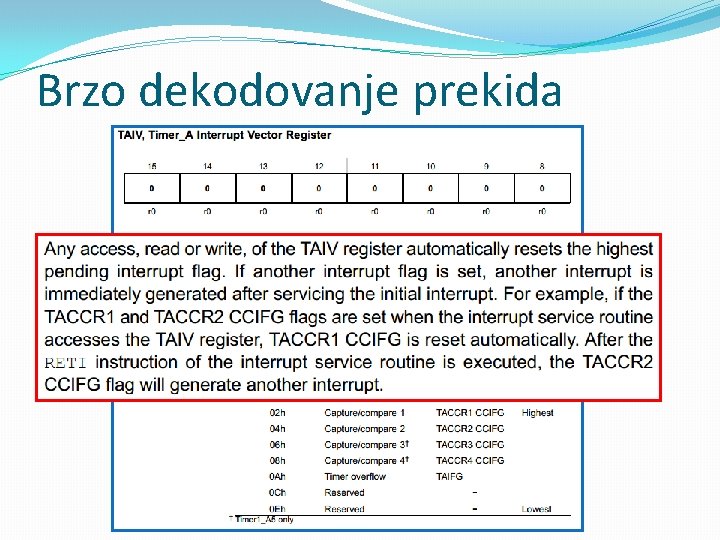

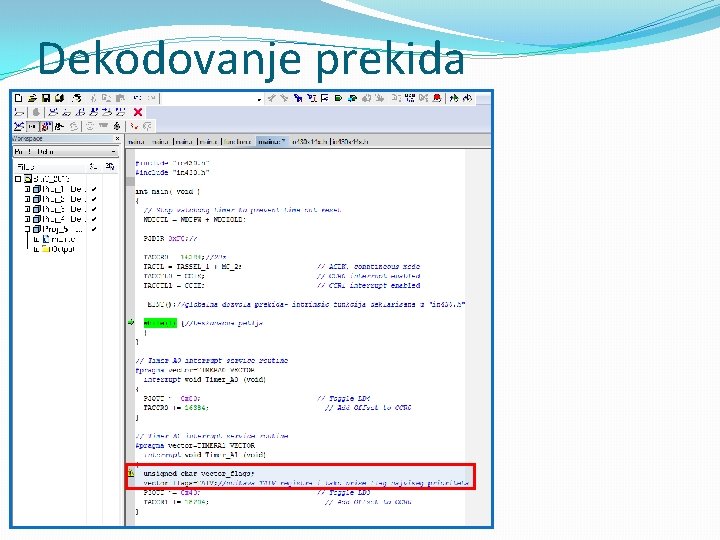

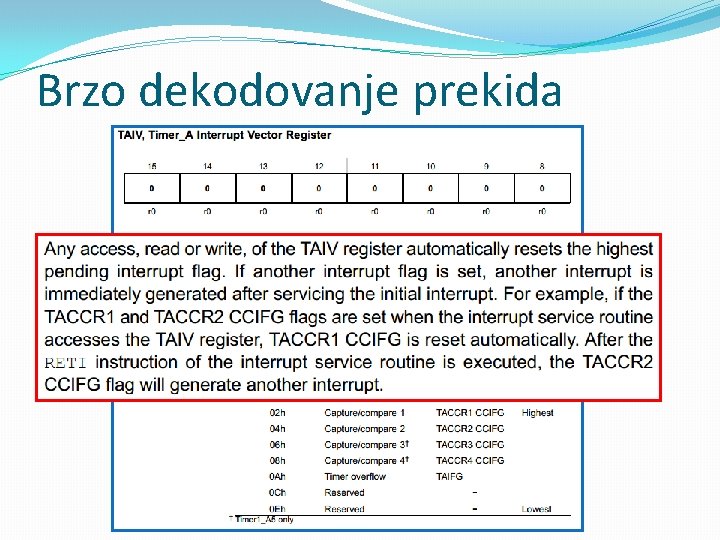

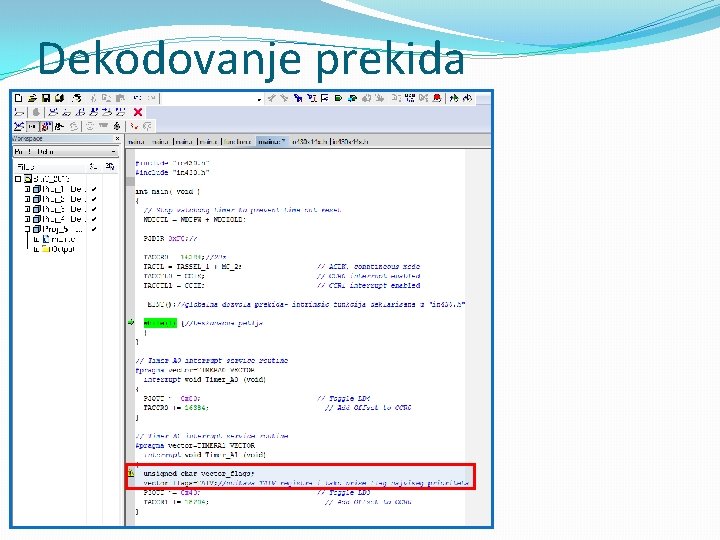

Brzo dekodovanje prekida

Dekodovanje prekida

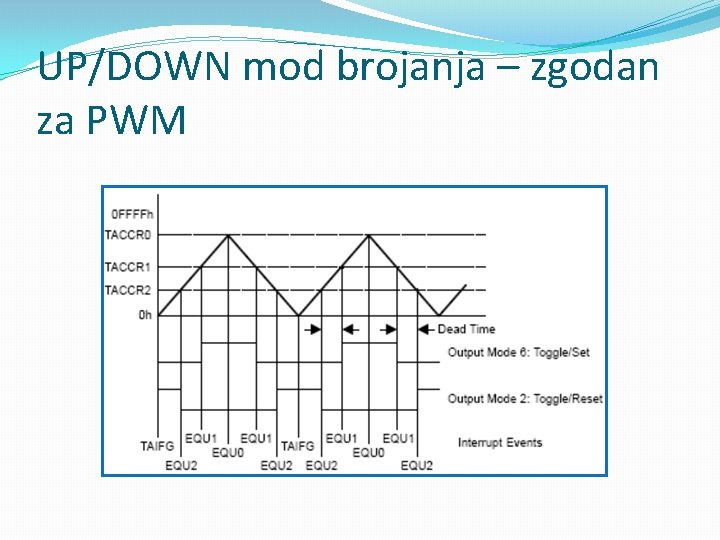

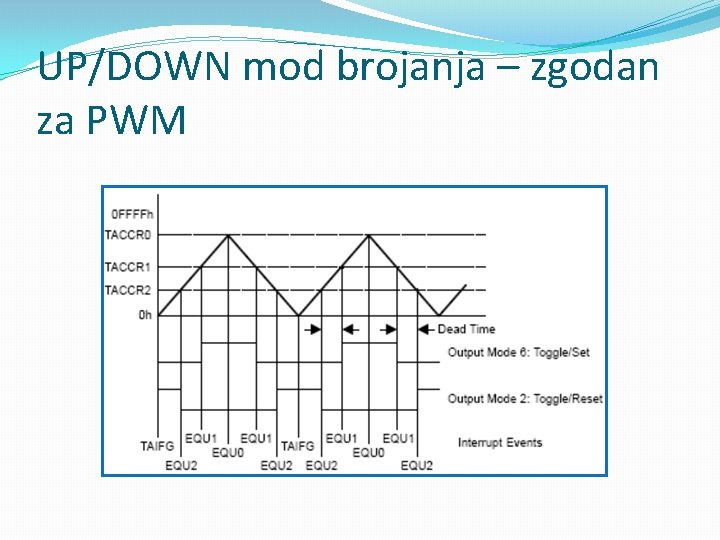

UP/DOWN mod brojanja – zgodan za PWM

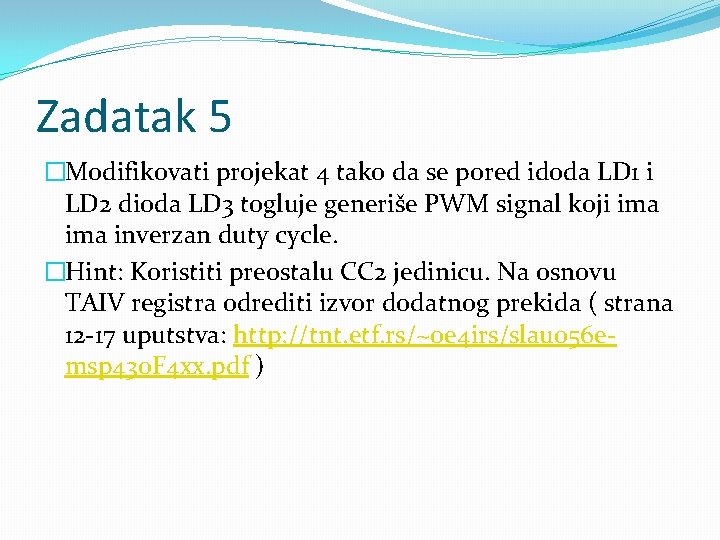

Zadatak 5 �Modifikovati projekat 4 tako da se pored idoda LD 1 i LD 2 dioda LD 3 togluje generiše PWM signal koji ima inverzan duty cycle. �Hint: Koristiti preostalu CC 2 jedinicu. Na osnovu TAIV registra odrediti izvor dodatnog prekida ( strana 12 -17 uputstva: http: //tnt. etf. rs/~oe 4 irs/slau 056 emsp 430 F 4 xx. pdf )

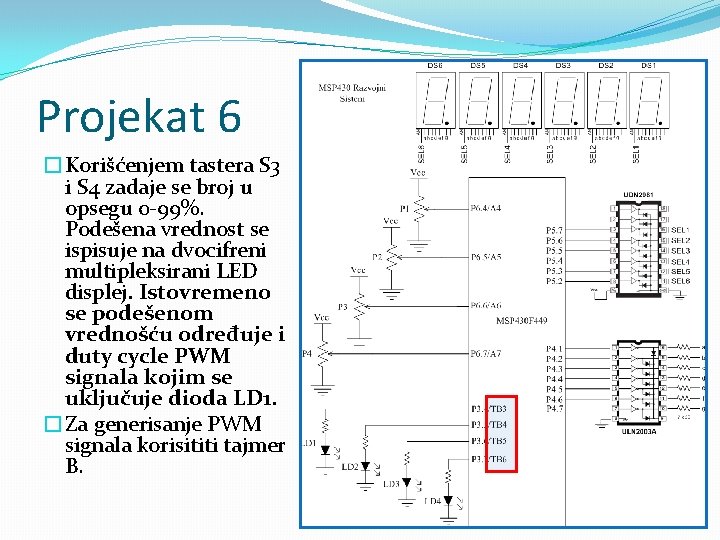

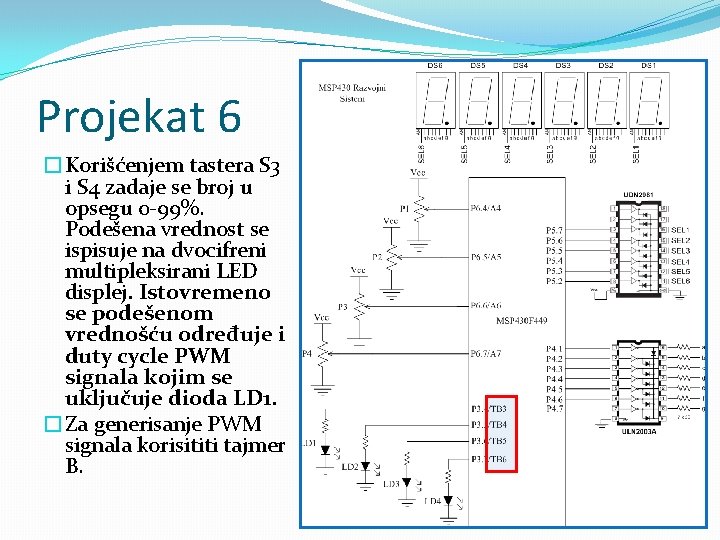

Projekat 6 �Korišćenjem tastera S 3 i S 4 zadaje se broj u opsegu 0 -99%. Podešena vrednost se ispisuje na dvocifreni multipleksirani LED displej. Istovremeno se podešenom vrednošću određuje i duty cycle PWM signala kojim se uključuje dioda LD 1. �Za generisanje PWM signala korisititi tajmer B.

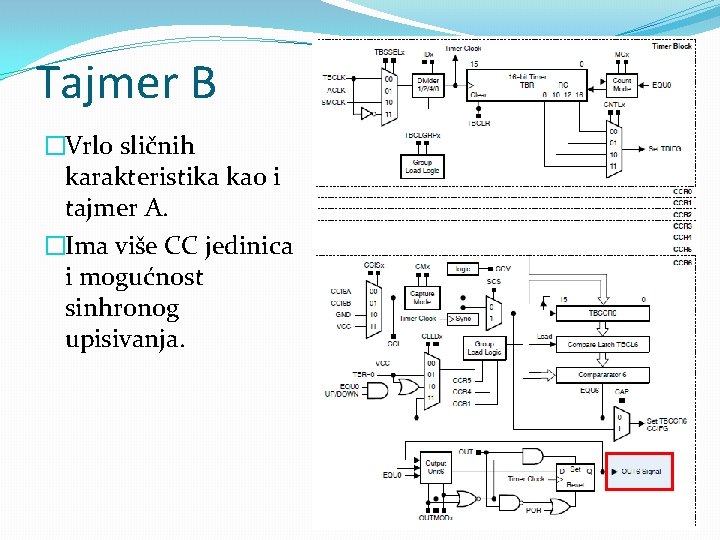

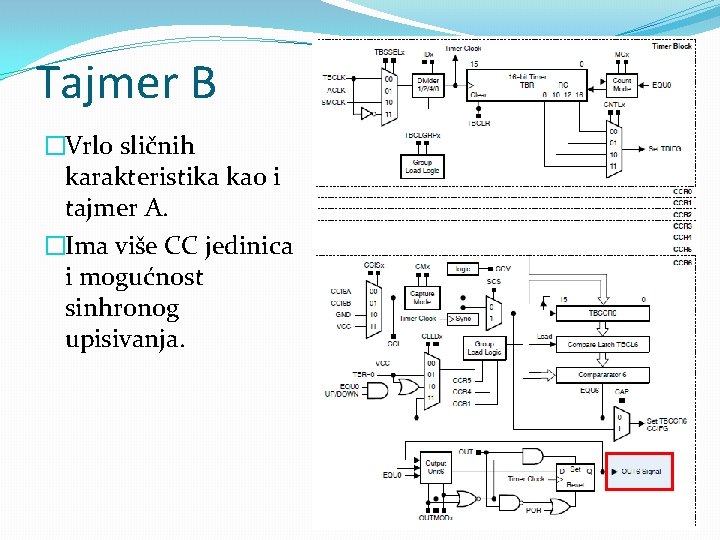

Tajmer B �Vrlo sličnih karakteristika kao i tajmer A. �Ima više CC jedinica i mogućnost sinhronog upisivanja.

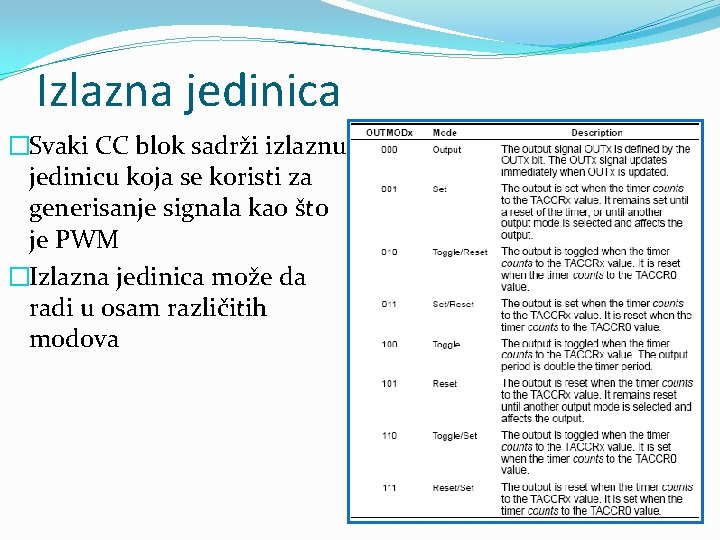

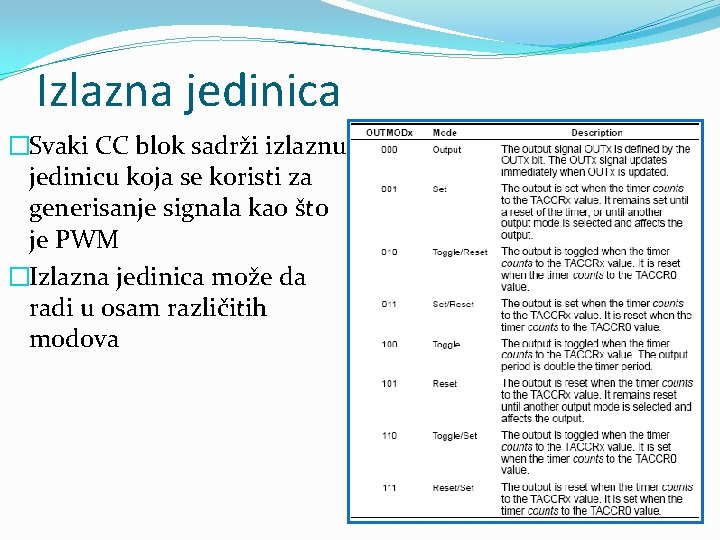

Izlazna jedinica �Svaki CC blok sadrži izlaznu jedinicu koja se koristi za generisanje signala kao što je PWM �Izlazna jedinica može da radi u osam različitih modova

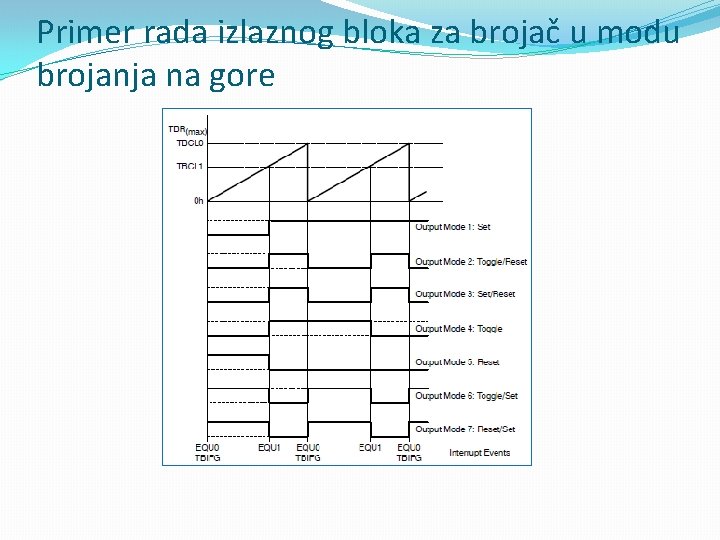

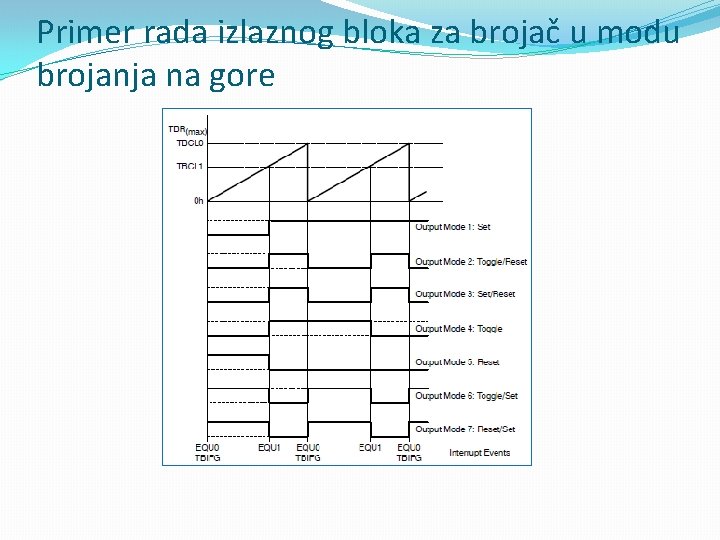

Primer rada izlaznog bloka za brojač u modu brojanja na gore

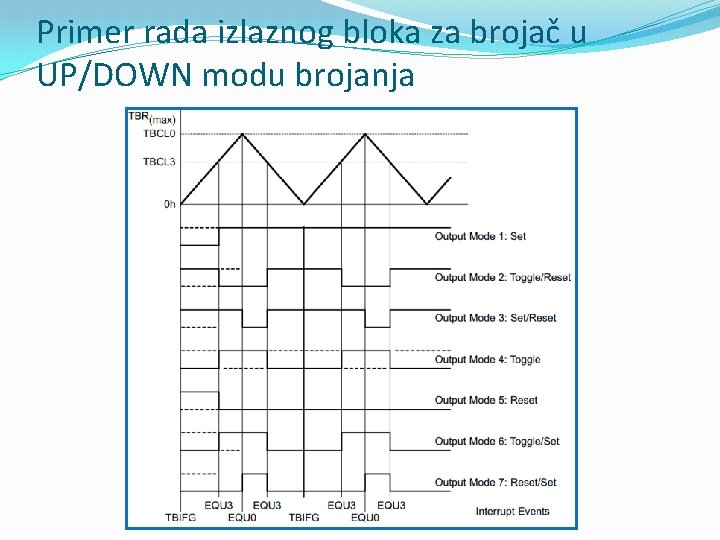

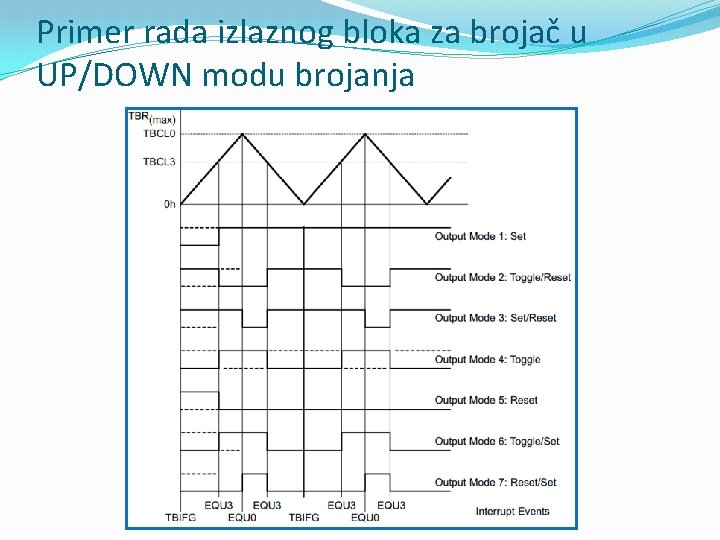

Primer rada izlaznog bloka za brojač u UP/DOWN modu brojanja

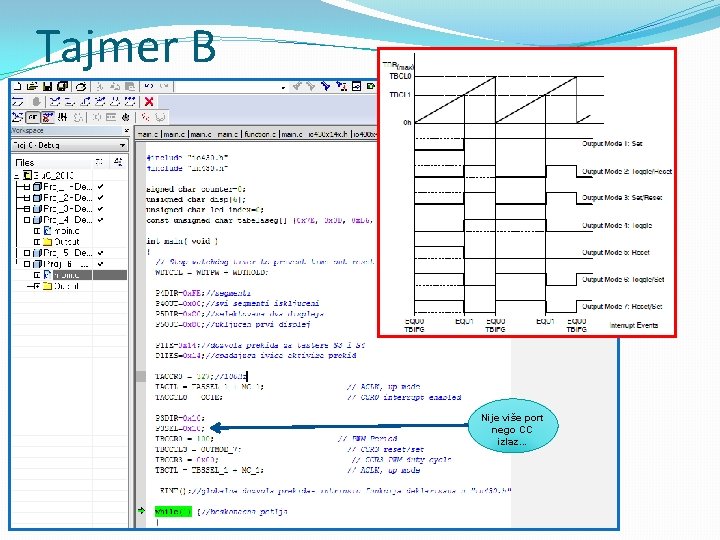

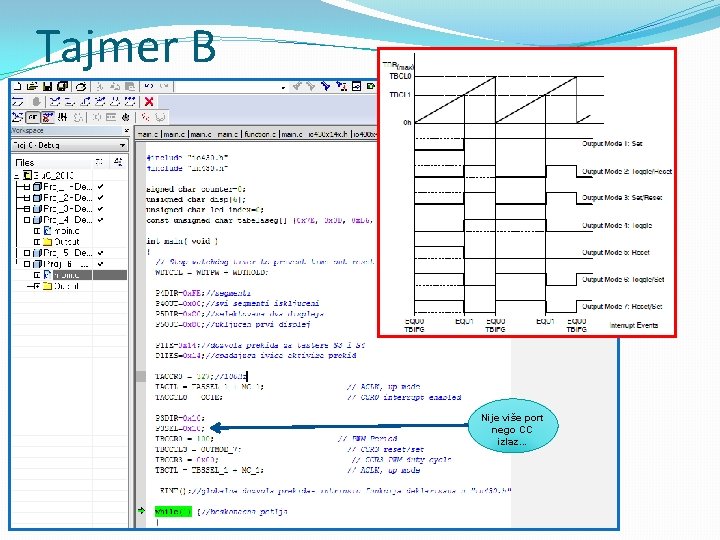

Tajmer B Nije više port nego CC izlaz. . .

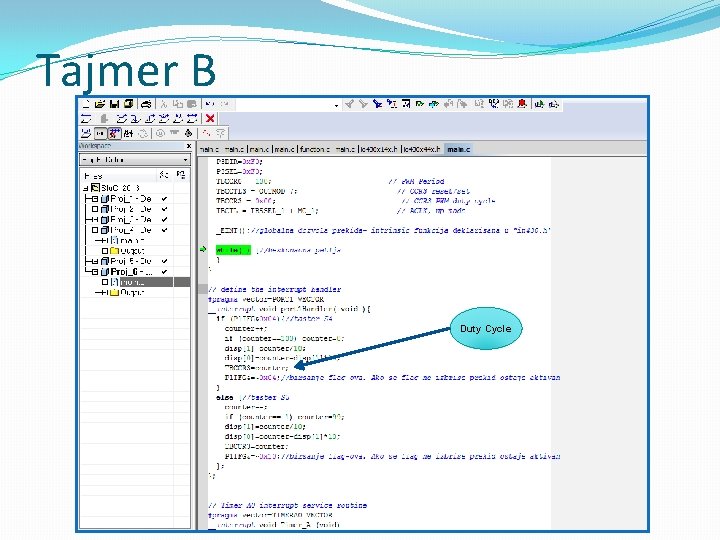

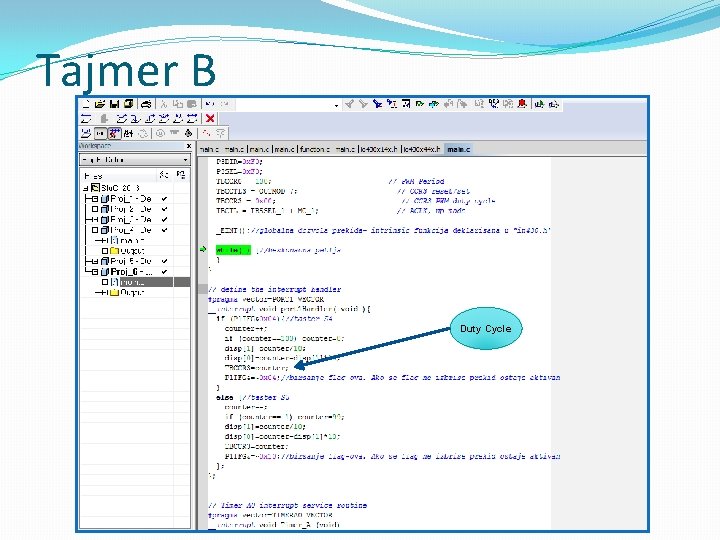

Tajmer B Duty Cycle

Zadatak 6 �Modifikovati projekat 4 tako da se na diodi LD 2 generiše PWM signal koji ima inverzan duty cycle od onog na diodi LD 1 (PWM 2=1 -PWM 1).

Domaći zadatak �Modifikovati projekat 4 tako da se na diodi LD 1 dobije PWM signal modulisan sinusoidom. �Sinusoida je mapirana u 32 tačke, i nalazi se u opsegu od 0 -99, tj. f=50+50*sin(2*pi*t/Ts). �Sa tasterima S 3 i S 4 se podešava perioda sinusoide Ts u opsegu od 0 -99 “nečega”. �Hint: Tajmer A koristiti za sukcesivno uzimanje odbiraka iz tabele u kojoj je mapirana sinusoida. Broj 0 -99 koji se podešava tasterima neka određuje periodu prekida tajmera A. . .