Shift Register Objectives Upon completion of this chapter

Shift Register

Objectives Upon completion of this chapter, you will be able to : J Explain the different classifications of registers : K Parallel In K Serial In / J / Parallel Out Serial Out / Serial Out Parallel Out Construct register using K RS flip-flop K D flip-flop J Determine the number of flip-flops required for an N-bit shift register

Introduction Shift Register is a Digital circuit that accepts binary data from some input source and then shifts these data through a chain of flip-flops one bit at a time.

The various types of registers can be classified according to the manner in which data can be entered into the register for storage and the manner in which data are outputted from the register. The various classifications are listed below KParallel In / Parallel Out KSerial In / Serial Out KParallel In / Serial Out KSerial In / Parallel Out ( 74174, 74 LS 174 ) ( 7431 B ) ( 74165, 74 LS 165 ) ( 74164, 74 LS 164 ) Each of these types is available in IC form so that a logic designer can usually find exactly what is required for a given application.

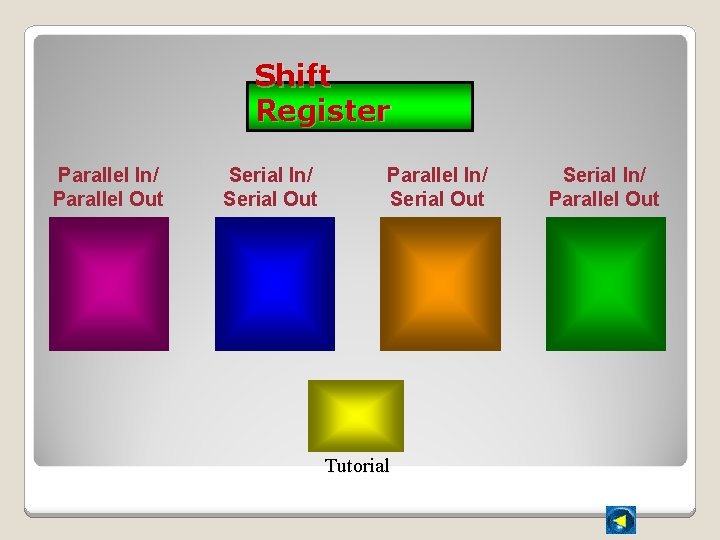

Shift Register Parallel In/ Parallel Out Serial In/ Serial Out Parallel In/ Serial Out Tutorial Serial In/ Parallel Out

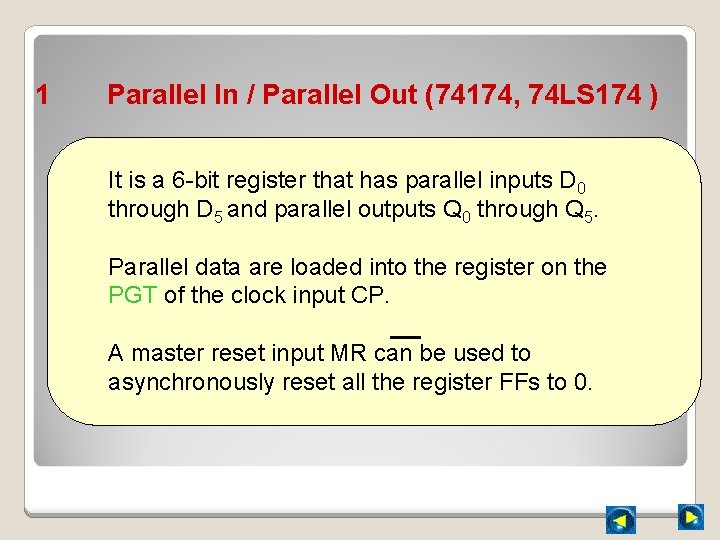

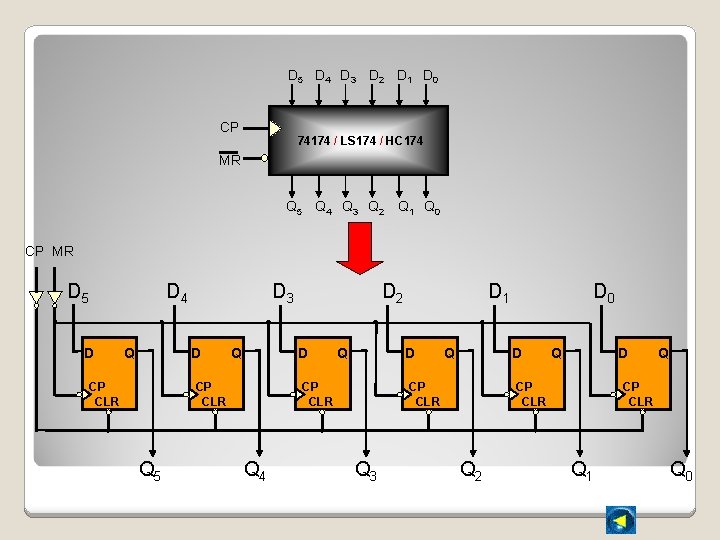

1 Parallel In / Parallel Out (74174, 74 LS 174 ) It is a 6 -bit register that has parallel inputs D 0 through D 5 and parallel outputs Q 0 through Q 5. Parallel data are loaded into the register on the PGT of the clock input CP. A master reset input MR can be used to asynchronously reset all the register FFs to 0.

D 5 D 4 D 3 D 2 D 1 D 0 CP 74174 / LS 174 / HC 174 MR Q 5 Q 4 Q 3 Q 2 Q 1 Q 0 CP MR D 5 D 4 D D 3 D Q CP CLR Q 5 D 2 D Q CP CLR Q 4 D 1 D Q CP CLR Q 3 D 0 D Q CP CLR Q 2 Q CP CLR Q 1 Q 0

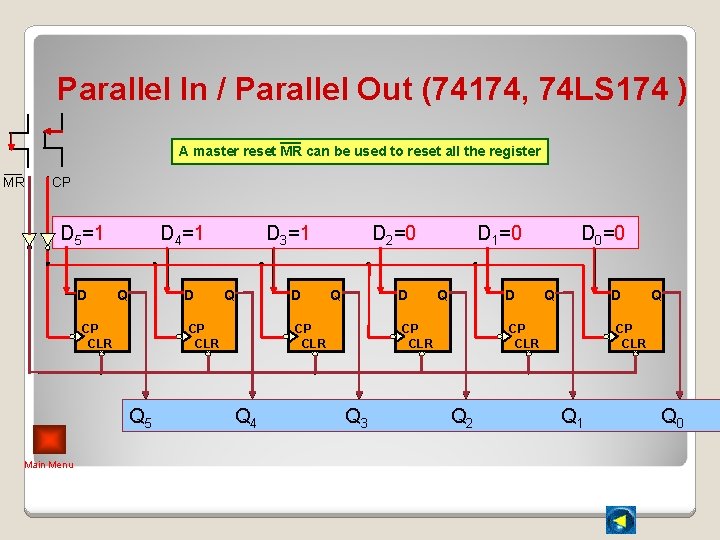

Parallel In / Parallel Out (74174, 74 LS 174 ) The data at the input will be shifted to the output only when the register gets the clock pulse, PGT. MR CP D 5=1 D D 4=1 D Q CP CLR D 3=1 D Q CP CLR Q 5 =1 D 22=0 D Q CP CLR Q 4=1 D D 11=0 D Q CP CLR Q 3=1 D 0=0 D Q CP CLR Q 2=0 Q CP CLR Q 1=0 Q 0=0

Parallel In / Parallel Out (74174, 74 LS 174 ) A master reset MR can be used to reset all the register MR CP D 5=1 D D 4=1 D Q CP CLR Q Q 55 =1 Main Menu D 3=1 D 22=0 D Q CP CLR Q Q 44=1 D D 11=0 D Q CP CLR Q Q 33=1 D 0=0 D Q CP CLR Q Q 22=0 Q CP CLR Q Q 11=0 Q Q 00=0

The End MAIN MENU

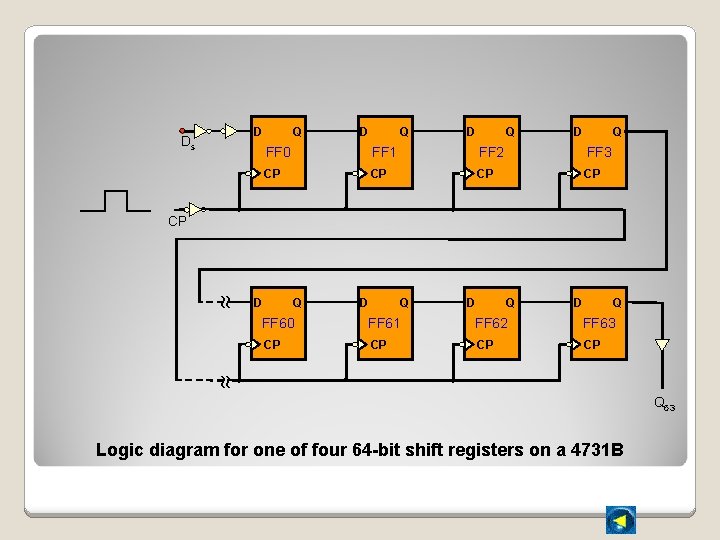

2 Serial In / Serial Out (7431 B) It is a CMOS quad 64 -bit shift register. It contains four identical 64 -bit shift registers on one chip. It has a serial input, DS, a clock input CP that responds to NGTs, and a serial output from the last FF, Q 63 is the only output that is externally accessible. This output goes through a buffer circuit ( triangle symbol with no inversion bubble). A buffer does not change the signal’s logic level; it is used to provide a greater output-current capability than normal.

Q D Ds Q D Q D FF 0 FF 1 FF 2 FF 3 CP CP Q D Q D FF 60 FF 61 FF 62 FF 63 CP CP CP Q 63 Logic diagram for one of four 64 -bit shift registers on a 4731 B

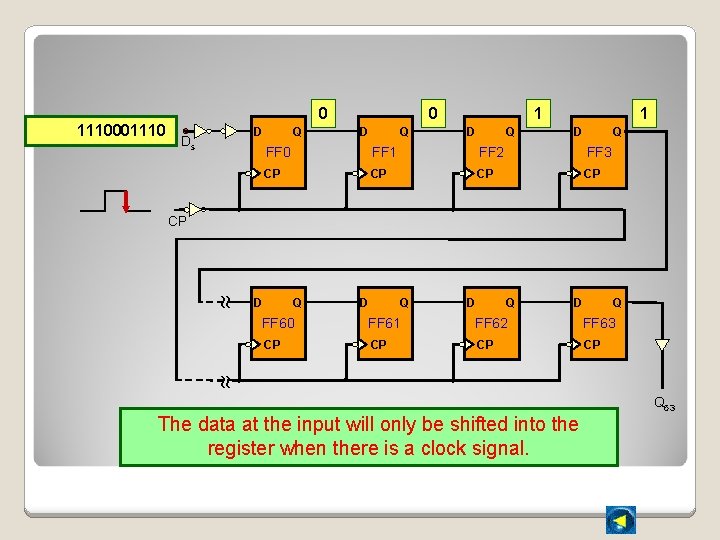

1110001110001 1110001110001110 1 0 Q D Ds 1 0 Q D 1 Q D FF 0 FF 1 FF 2 FF 3 CP CP Q D Q D FF 60 FF 61 FF 62 FF 63 CP CP CP Q 63 The data at the input will only be shifted into the register when there is a clock signal.

The End MAIN MENU

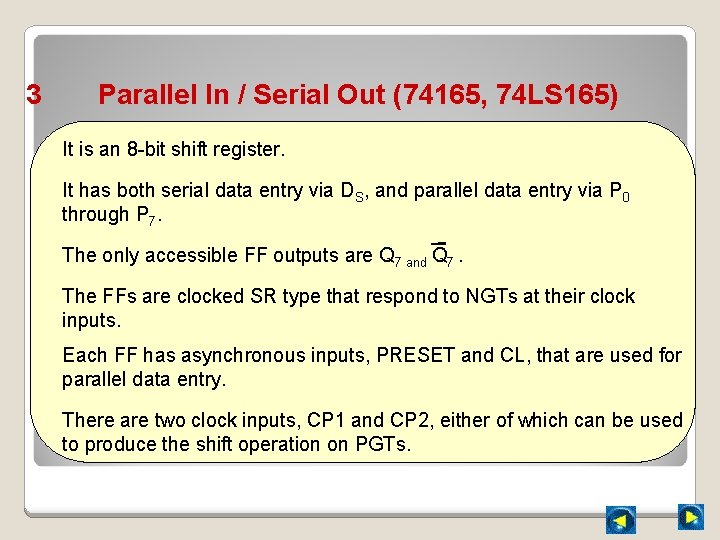

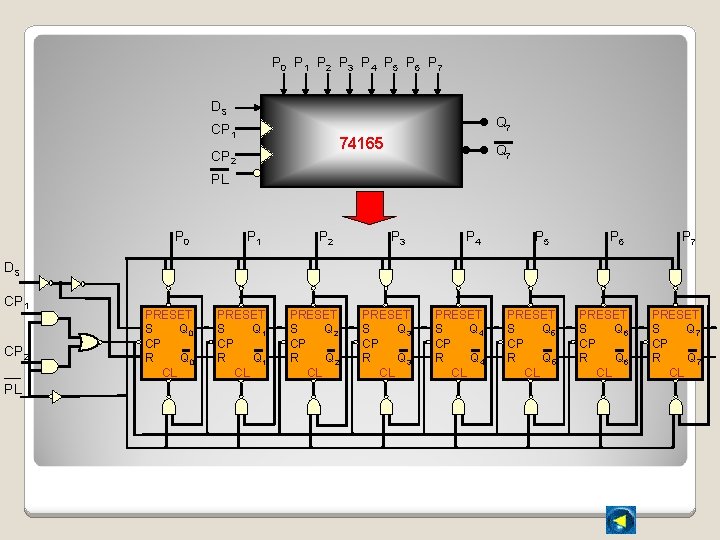

3 Parallel In / Serial Out (74165, 74 LS 165) It is an 8 -bit shift register. It has both serial data entry via DS, and parallel data entry via P 0 through P 7. The only accessible FF outputs are Q 7 and Q 7. The FFs are clocked SR type that respond to NGTs at their clock inputs. Each FF has asynchronous inputs, PRESET and CL, that are used for parallel data entry. There are two clock inputs, CP 1 and CP 2, either of which can be used to produce the shift operation on PGTs.

P 0 P 1 P 2 P 3 P 4 P 5 P 6 P 7 DS Q 7 CP 1 74165 CP 2 Q 7 PL P 0 P 1 P 2 P 3 P 4 P 5 P 6 P 7 DS CP 1 CP 2 PL PRESET S Q 0 CP R Q 0 CL PRESET S Q 1 CP R Q 1 CL PRESET S Q 2 CP R Q 2 CL PRESET S Q 3 CP R Q 3 CL PRESET S Q 4 CP R Q 4 CL PRESET S Q 5 CP R Q 5 CL PRESET S Q 6 CP R Q 6 CL PRESET S Q 7 CP R Q 7 CL

The End MAIN MENU

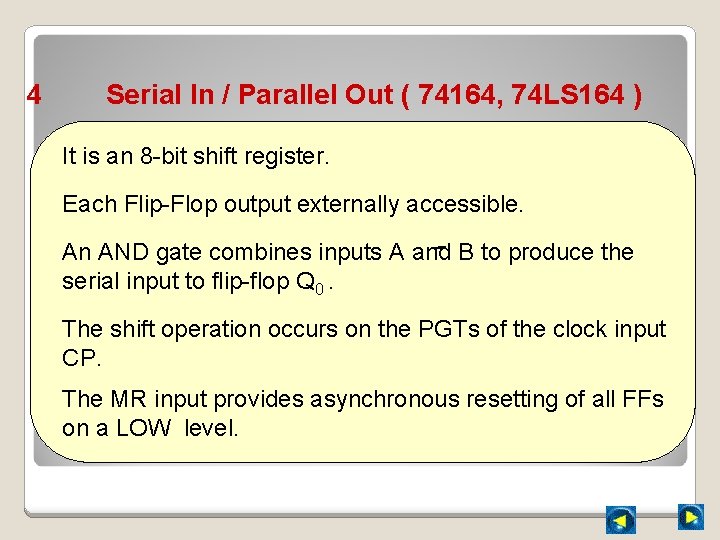

4 Serial In / Parallel Out ( 74164, 74 LS 164 ) It is an 8 -bit shift register. Each Flip-Flop output externally accessible. An AND gate combines inputs A and B to produce the serial input to flip-flop Q 0. The shift operation occurs on the PGTs of the clock input CP. The MR input provides asynchronous resetting of all FFs on a LOW level.

A 74164 / 74 LS 164 B CP MR A B D Q CP CD CP MR D Q CP CD Q 0 Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 Q 7 D Q CP CD D Q CP CD

The End MAIN MENU

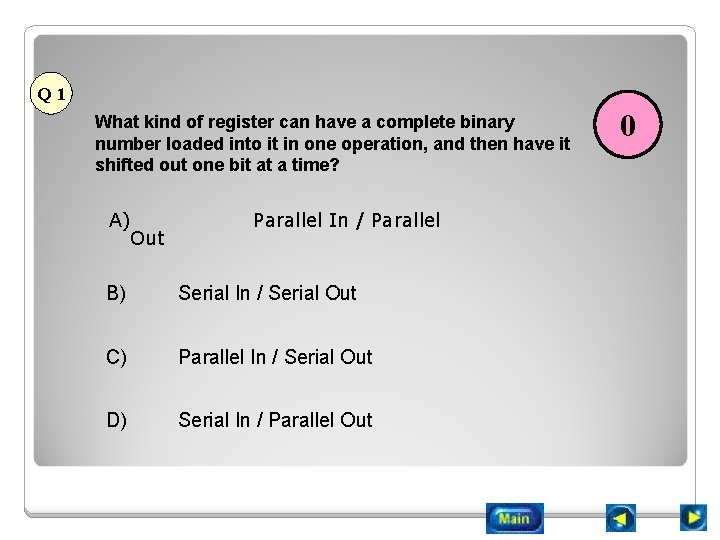

Q 1 What kind of register can have a complete binary number loaded into it in one operation, and then have it shifted out one bit at a time? A) Out Parallel In / Parallel B) Serial In / Serial Out C) Parallel In / Serial Out D) Serial In / Parallel Out 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 9876543210

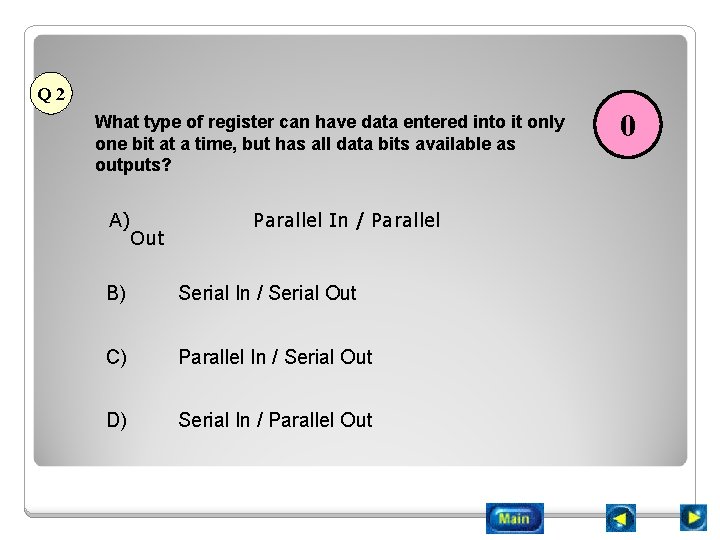

Q 2 What type of register can have data entered into it only one bit at a time, but has all data bits available as outputs? A) Out Parallel In / Parallel B) Serial In / Serial Out C) Parallel In / Serial Out D) Serial In / Parallel Out 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 9876543210

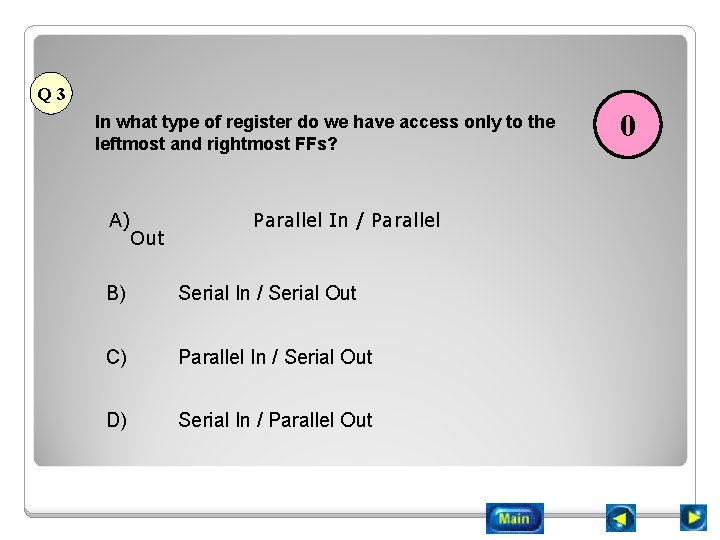

Q 3 In what type of register do we have access only to the leftmost and rightmost FFs? A) Out Parallel In / Parallel B) Serial In / Serial Out C) Parallel In / Serial Out D) Serial In / Parallel Out 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 9876543210

The End MAIN MENU

- Slides: 24