Sharif University of Technology Department of Computer Engineering

![Vectors l Syntax: l l wire/reg [msb_index : lsb_index] data_id; Example wire a; wire Vectors l Syntax: l l wire/reg [msb_index : lsb_index] data_id; Example wire a; wire](https://slidetodoc.com/presentation_image/2805ae5cfcc10751049786e1b8ec5eb2/image-8.jpg)

![Arrays vs. Vectors module test; reg [0: 9] x; reg [0: 9] y; module Arrays vs. Vectors module test; reg [0: 9] x; reg [0: 9] y; module](https://slidetodoc.com/presentation_image/2805ae5cfcc10751049786e1b8ec5eb2/image-9.jpg)

- Slides: 10

Sharif University of Technology Department of Computer Engineering Verilog® HDL -Review -Vectors and Arrays Alireza Ejlali

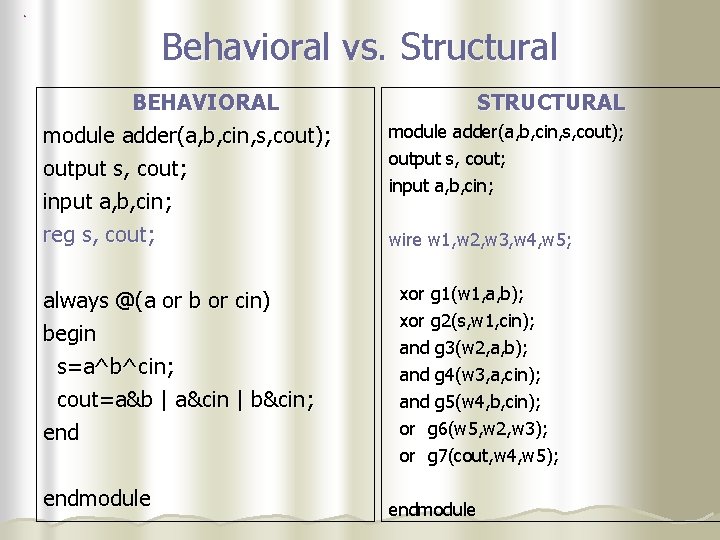

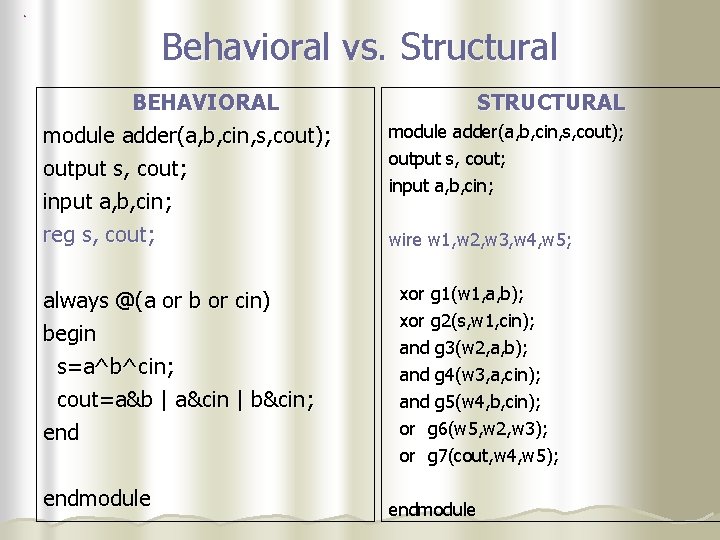

Review l Design Methodologies l Structural and Behavioral Models l Test Bench l 4 -Value Logic l wire and reg

Behavioral vs. Structural BEHAVIORAL module adder(a, b, cin, s, cout); output s, cout; input a, b, cin; reg s, cout; always @(a or b or cin) begin s=a^b^cin; cout=a&b | a&cin | b&cin; endmodule STRUCTURAL module adder(a, b, cin, s, cout); output s, cout; input a, b, cin; wire w 1, w 2, w 3, w 4, w 5; xor g 1(w 1, a, b); xor g 2(s, w 1, cin); and g 3(w 2, a, b); and g 4(w 3, a, cin); and g 5(w 4, b, cin); or g 6(w 5, w 2, w 3); or g 7(cout, w 4, w 5); endmodule

Test Bench module adder)a, b, cin, s, cout; ( output s, cout; input a, b, cin; reg s, cout; always @(a or b or cin( begin s=a^b^cin; cout=a&b | a&cin | b&cin; endmodule testbench; reg aa, bb, ccin; wire ss, ccout; adder add 1(aa, bb, ccin, ss, ccout); initial begin aa=1'b 0; bb=1'b 1; ccin=1'b 0; #2 aa=1'b 1; bb=1'b 1; ccin=1'b 1; #2 aa=1'b 0; bb=1'b 0; ccin=1'b 0; #2 aa=1'b 1; bb=1'b 1; ccin=1'b 0; #2 $stop; end initial $monitor($time, “ aa=%b, bb=%b, ccin=%b, ss=%b, ccout=%b", aa, bb, ccin, ss, ccout); endmodule

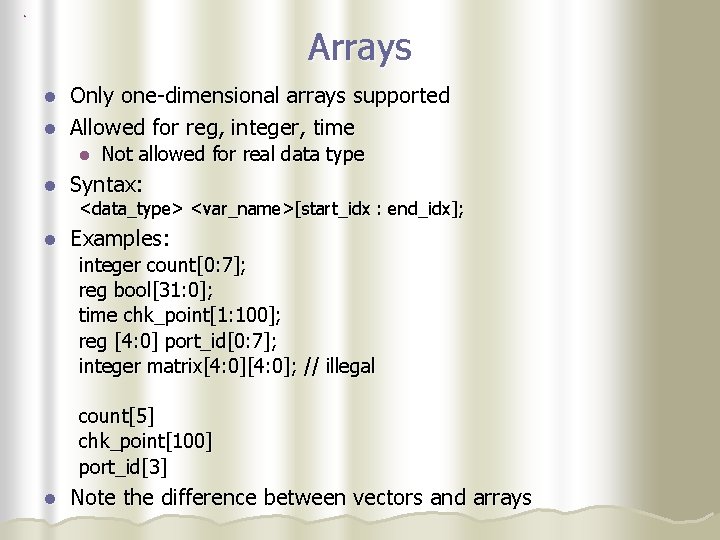

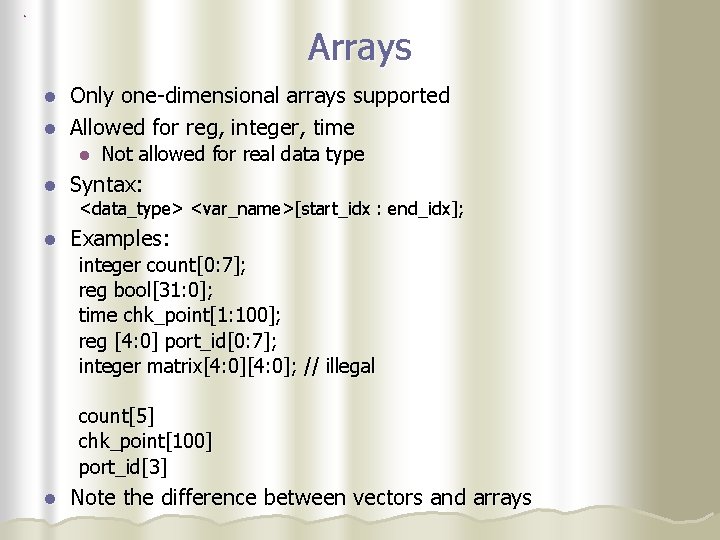

wire (net) vs. reg l Concept wire: Used to represent connections between HW elements l reg: data storage elements (like programming variables) l l Verilog l value l l l wire: might have multiple drivers (signal strength) reg: retains value until next assignment usage l l wire: output ports in instantiations (reg -> illegal) reg: LHS of assignments in behavioral bodies (wire -> illegal)

Example of wires and regs module example; reg i 1, i 2, i 3, i 4; wire o; and g 1(o, i 1, i 2); or g 2(o, i 3, i 4); initial begin i 1=0; i 2=0; i 3=0; i 4=0; #4 i 1=1; i 3=1; #4 i 2=1; i 4=1; #4 i 1=0; i 3=1; #4 i 2=0; i 4=1; endmodule

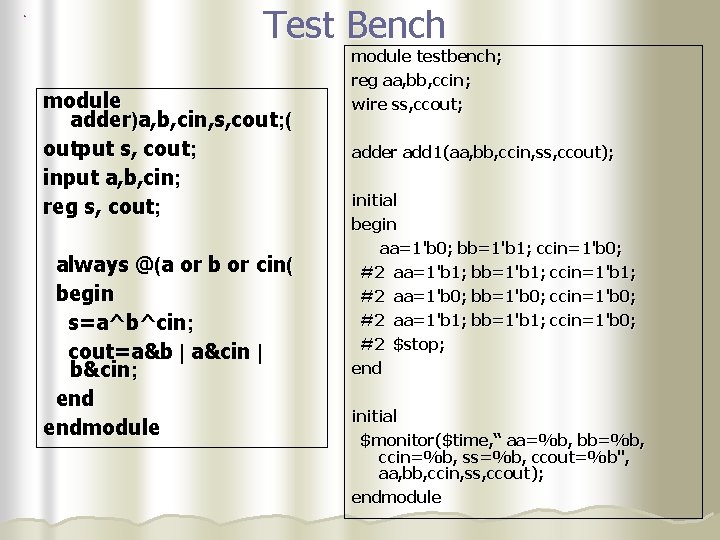

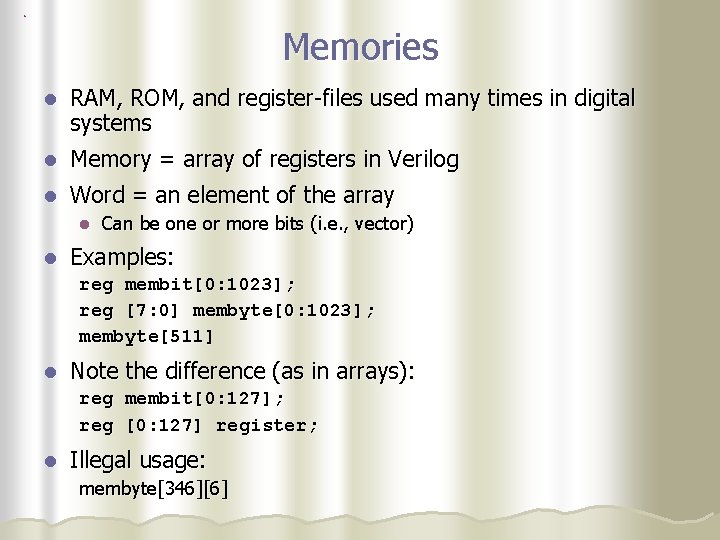

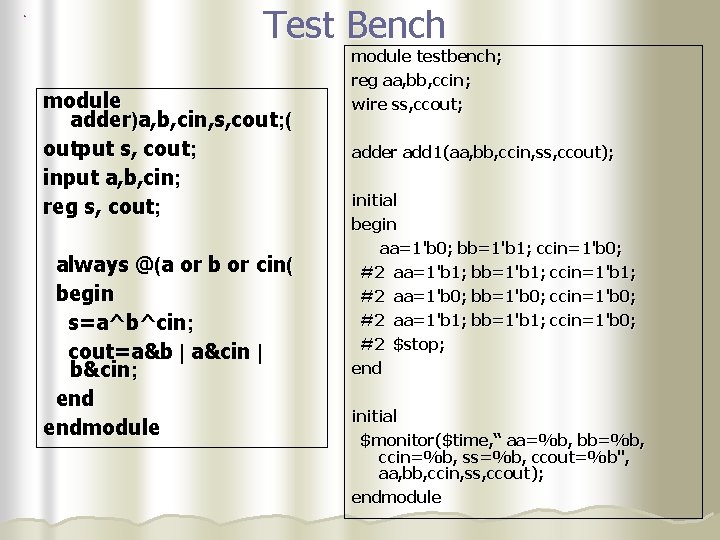

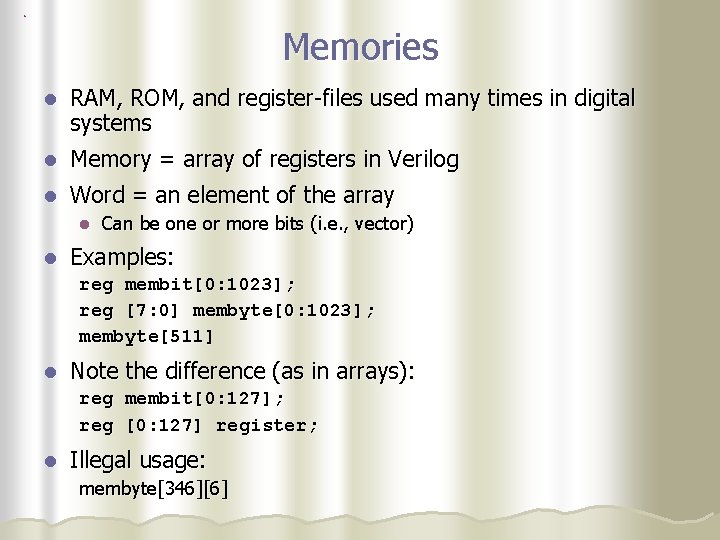

Arrays Only one-dimensional arrays supported l Allowed for reg, integer, time l l l Not allowed for real data type Syntax: <data_type> <var_name>[start_idx : end_idx]; l Examples: integer count[0: 7]; reg bool[31: 0]; time chk_point[1: 100]; reg [4: 0] port_id[0: 7]; integer matrix[4: 0]; // illegal count[5] chk_point[100] port_id[3] l Note the difference between vectors and arrays

![Vectors l Syntax l l wirereg msbindex lsbindex dataid Example wire a wire Vectors l Syntax: l l wire/reg [msb_index : lsb_index] data_id; Example wire a; wire](https://slidetodoc.com/presentation_image/2805ae5cfcc10751049786e1b8ec5eb2/image-8.jpg)

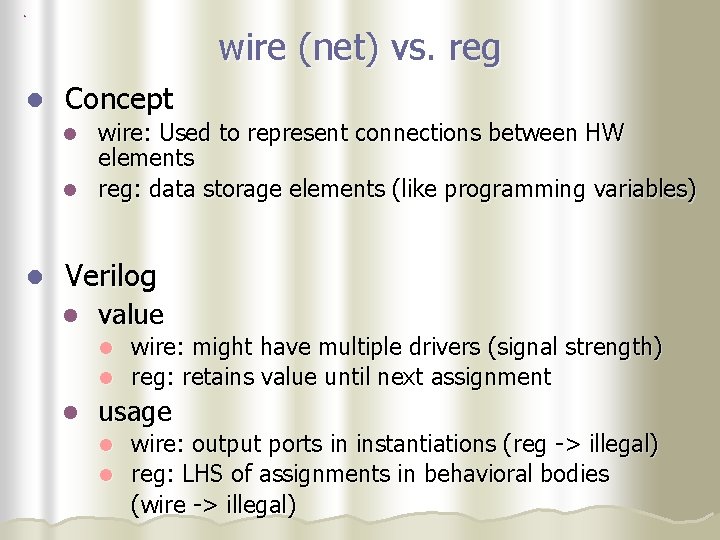

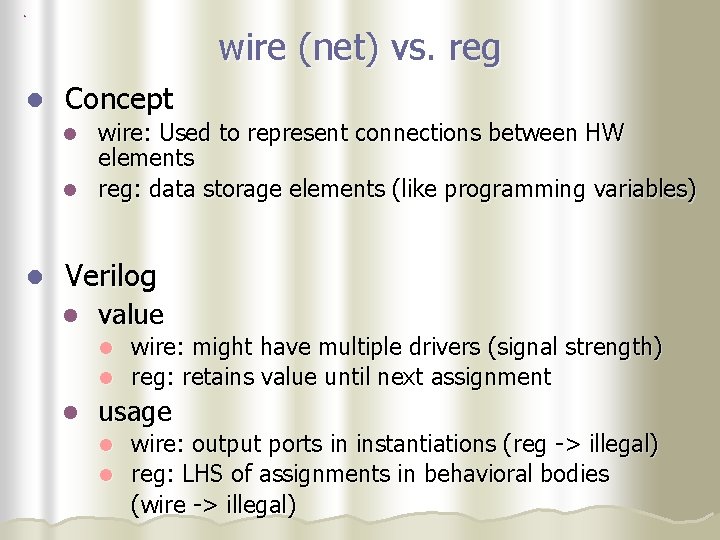

Vectors l Syntax: l l wire/reg [msb_index : lsb_index] data_id; Example wire a; wire [7: 0] bus; wire [31: 0] bus. A, bus. B, bus. C; reg clock; reg [0: 40] virtual_addr; l Access to parts of a vector Bus[2: 0]

![Arrays vs Vectors module test reg 0 9 x reg 0 9 y module Arrays vs. Vectors module test; reg [0: 9] x; reg [0: 9] y; module](https://slidetodoc.com/presentation_image/2805ae5cfcc10751049786e1b8ec5eb2/image-9.jpg)

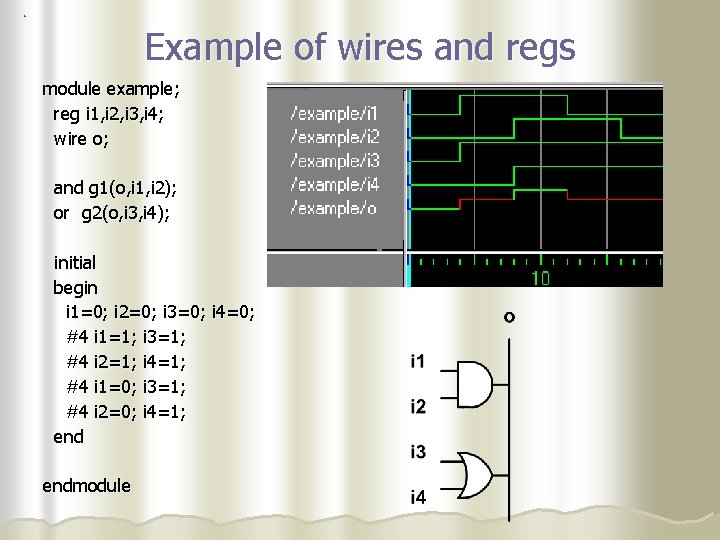

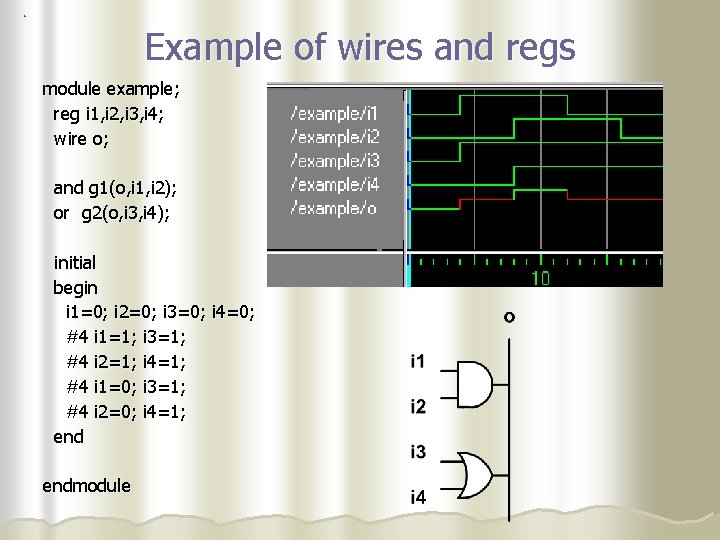

Arrays vs. Vectors module test; reg [0: 9] x; reg [0: 9] y; module test; integer x[0: 9]; integer y[0: 9]; initial begin x[6]=1'b 1; x[7]=1'b 0; initial begin y[6: 7]=x[6: 7]; //it is OK end y[6: 7]=x[6: 7]; //illegal endmodule x[7]=13; x[6]=10; endmodule

Memories l RAM, ROM, and register-files used many times in digital systems l Memory = array of registers in Verilog l Word = an element of the array l l Can be one or more bits (i. e. , vector) Examples: reg membit[0: 1023]; reg [7: 0] membyte[0: 1023]; membyte[511] l Note the difference (as in arrays): reg membit[0: 127]; reg [0: 127] register; l Illegal usage: membyte[346][6]