Shared Memory Consistency Models A Tutorial By Sarita

Shared Memory Consistency Models: A Tutorial By Sarita V Adve and Kourosh Gharachorloo Presenter: Meenaktchi Venkatachalam

Overview • • Memory consistency model Sequential Consistency (SC) model Relaxed Model Programmer centric Relaxed model

Memory Consistent Model • Memory consistency model of shared memory multiprocessor provides a formal specification of how the memory system will appear to the programmer, eliminating the gap between the behavior expected by the programmer and the actual behavior of the program. • Memory model affects: Programmability (easy-of-programming) -- Performance (optimization) -- Portability (moving software across different systems)

Sequential Memory model • It is simple and implicit • Definition: [A multiprocessor system is sequentially consistent if] the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program. • All operations executed in some sequential order • Memory operations of each process in program order

Implementing Sequential Consistency • Architecture without caches • Architecture with caches

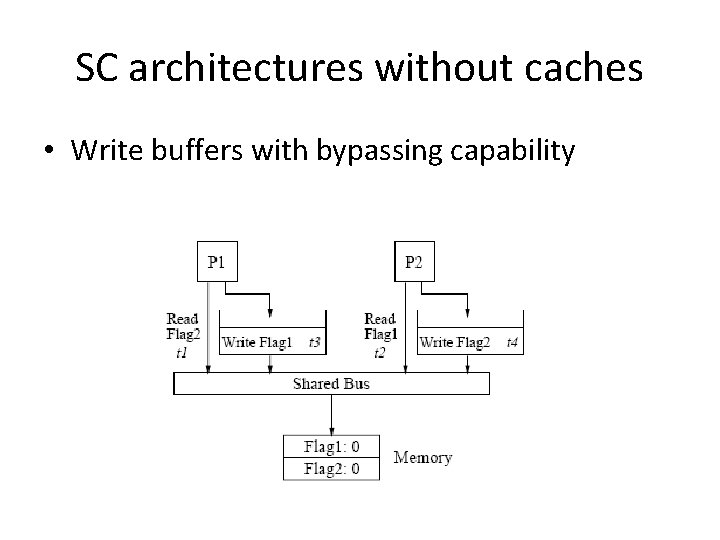

SC architectures without caches • Write buffers with bypassing capability

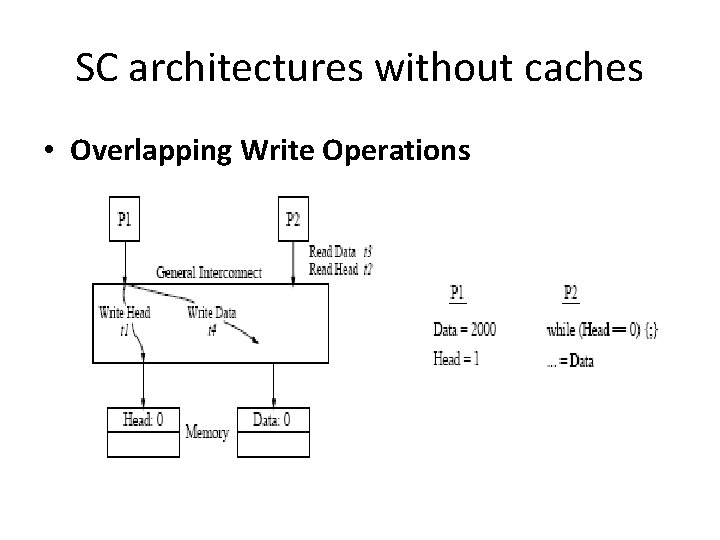

SC architectures without caches • Overlapping Write Operations

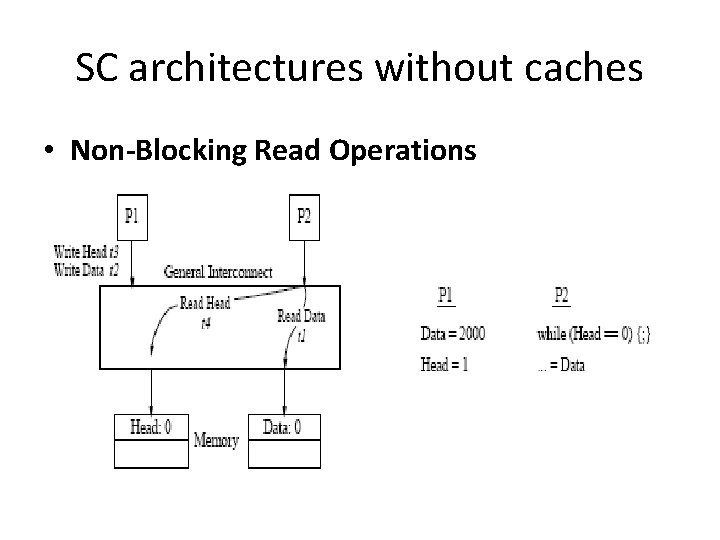

SC architectures without caches • Non-Blocking Read Operations

SC architectures with caches • Cache coherence models – Basic set of conditions commonly associated with a cache coherence protocol are: • • a write is eventually made visible to all processors, and writes to the same location appear to be seen in the same order by all processors (also referred to as serialization of writes to the same location) – The 2 nd condition requires writes to all locations and this can violate the sequential consistency – This can be done by invalidating the copy and then propagating the new value to all the memory locations

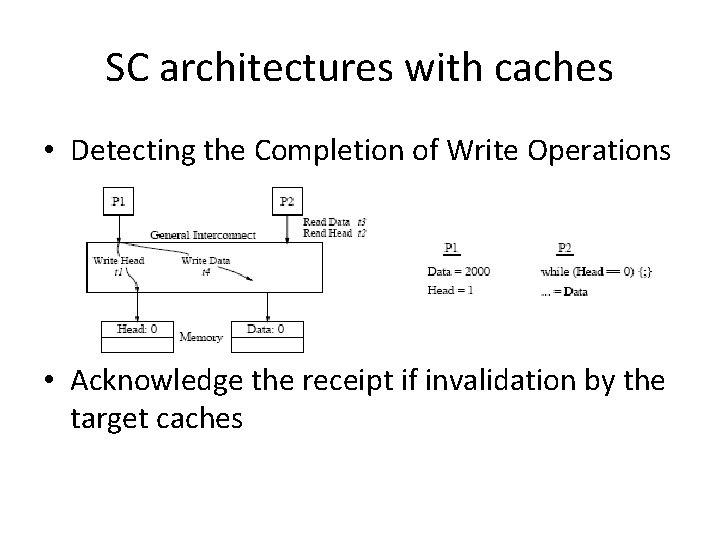

SC architectures with caches • Detecting the Completion of Write Operations • Acknowledge the receipt if invalidation by the target caches

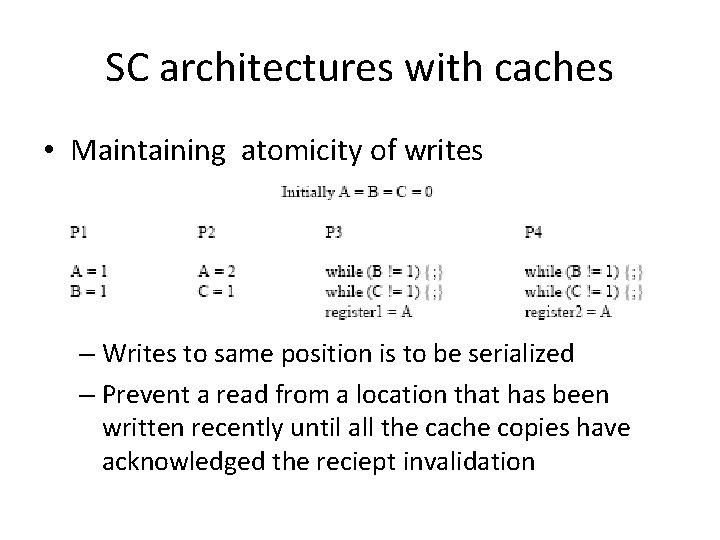

SC architectures with caches • Maintaining atomicity of writes – Writes to same position is to be serialized – Prevent a read from a location that has been written recently until all the cache copies have acknowledged the reciept invalidation

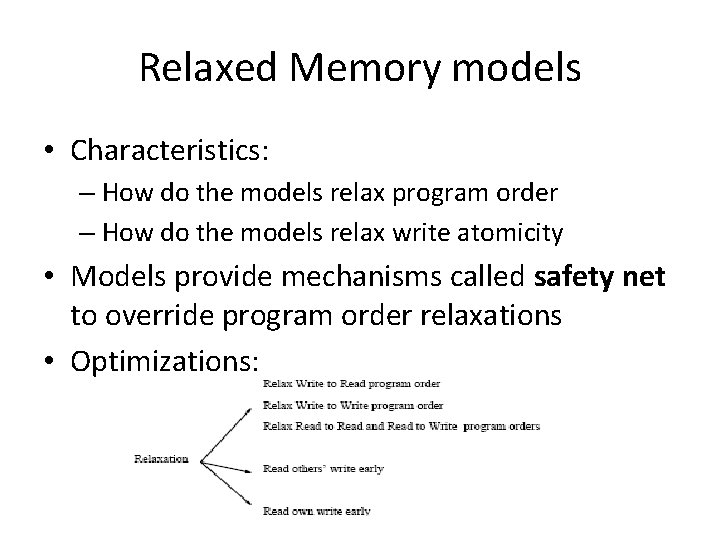

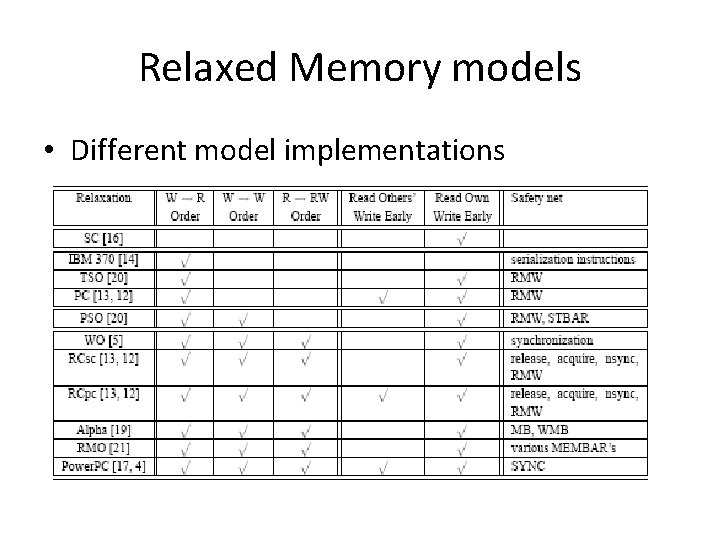

Relaxed Memory models • Characteristics: – How do the models relax program order – How do the models relax write atomicity • Models provide mechanisms called safety net to override program order relaxations • Optimizations:

Relaxed Memory models • Different model implementations

Programmer centric Relaxed model • So far we saw the system centric optimizations • Instead of exposing performance-enhancing optimizations directly to the programmer as is done by a system centric specification, a programmer-centric specification requires the programmer to provide certain information about the program • To provide program centric specification, define: – Notion of correctness and – Information required from the programmer

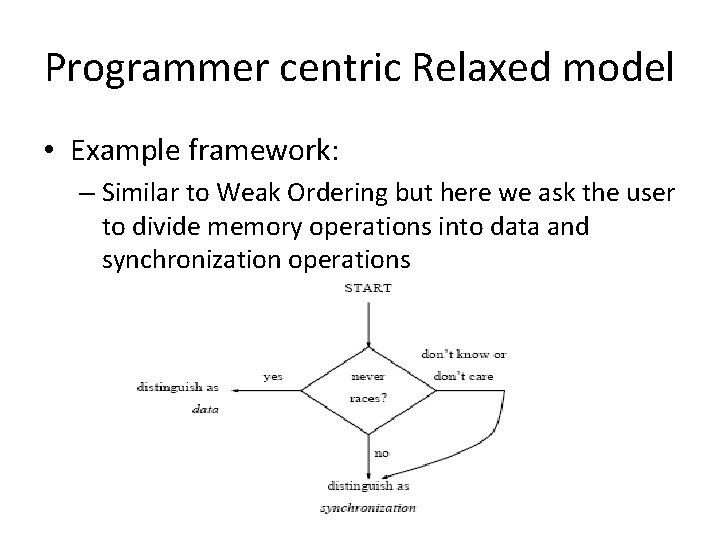

Programmer centric Relaxed model • Example framework: – Similar to Weak Ordering but here we ask the user to divide memory operations into data and synchronization operations

- Slides: 15