Session 5 Government Funded Standards Dr Edward Baranoski

Session 5 Government Funded Standards Dr. Edward Baranoski MIT Lincoln Laboratory This work is sponsored by the High Performance Computing Modernization Office under Air Force Contract F 19628 -00 -C 0002. Opinions, interpretations, conclusions, and recommendations are those of the author and are not necessarily endorsed by the Department of Defense. MIT Lincoln Laboratory 999999 -1 XYZ 9/25/2021

Outline • Introduction • Key Efforts • Summary 999999 -2 XYZ 9/25/2021 • Do. D Need • Standards Goals MIT Lincoln Laboratory

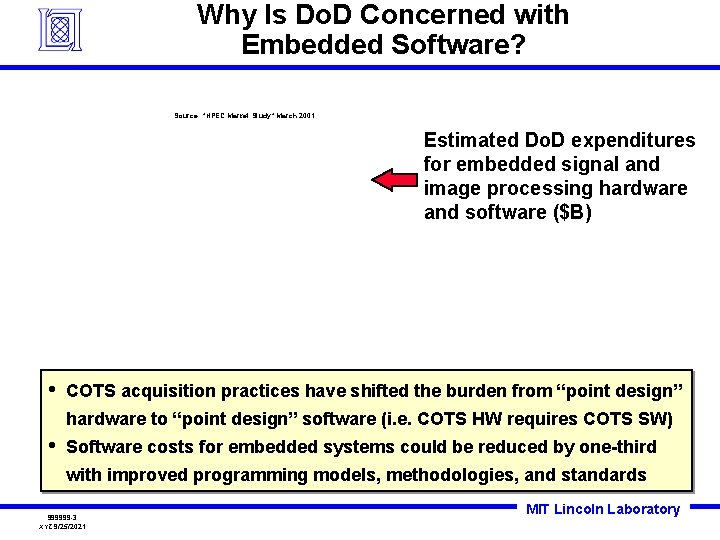

Why Is Do. D Concerned with Embedded Software? Source: “HPEC Market Study” March 2001 Estimated Do. D expenditures for embedded signal and image processing hardware and software ($B) • COTS acquisition practices have shifted the burden from “point design” hardware to “point design” software (i. e. COTS HW requires COTS SW) • Software costs for embedded systems could be reduced by one-third with improved programming models, methodologies, and standards 999999 -3 XYZ 9/25/2021 MIT Lincoln Laboratory

Evolution of Software Support Towards “Write Once, Run Anywhere/Anysize” Do. D software development COTS development Application Vendor SW 1990 Application Middleware 999999 -4 XYZ 9/25/2021 Middleware Application Middleware Embedded SW Standards Vendor Software 2000 Application Middleware • Application software has traditionally been tied to the hardware • Many acquisition programs are developing stove-piped middleware “standards” • Open software standards can provide portability, performance, and productivity benefits • Support “Write Once, Run Anywhere/Anysize” 2005 Application Middleware MIT Lincoln Laboratory

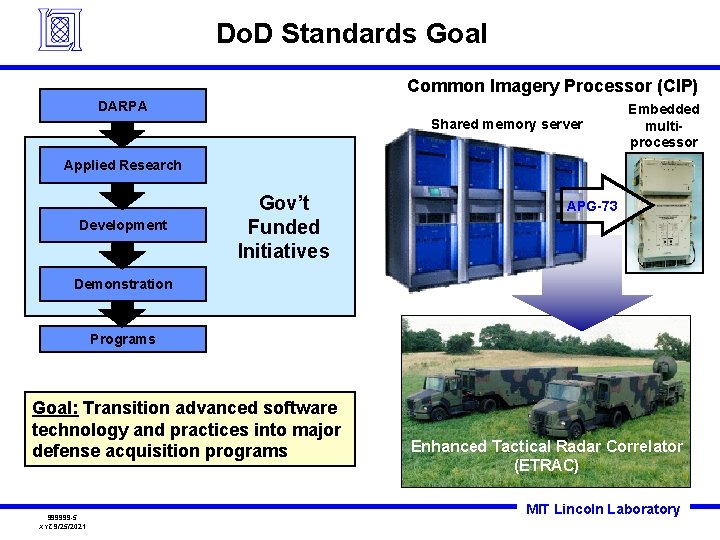

Do. D Standards Goal Common Imagery Processor (CIP) DARPA Shared memory server Embedded multiprocessor Applied Research Development Gov’t Funded Initiatives APG-73 Demonstration Programs Goal: Transition advanced software technology and practices into major defense acquisition programs 999999 -5 XYZ 9/25/2021 Enhanced Tactical Radar Correlator (ETRAC) MIT Lincoln Laboratory

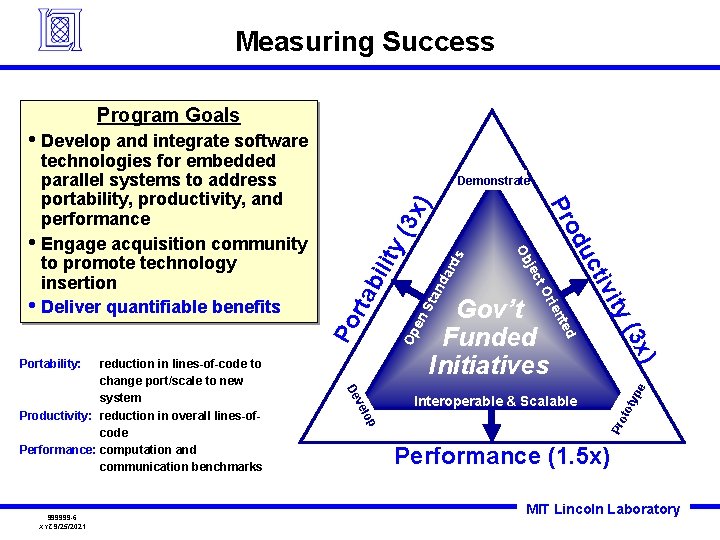

Measuring Success Program Goals • Develop and integrate software ) s ard nd Sta en ) typ e Op (3 x d nte ity oto Interoperable & Scalable Pr ab tiv Gov’t Funded Initiatives rie Po rt uc ilit y (3 x od Pr t. O lop ve 999999 -6 XYZ 9/25/2021 jec Portability: De reduction in lines-of-code to change port/scale to new system Productivity: reduction in overall lines-ofcode Performance: computation and communication benchmarks Demonstrate Ob technologies for embedded parallel systems to address portability, productivity, and performance • Engage acquisition community to promote technology insertion • Deliver quantifiable benefits Performance (1. 5 x) MIT Lincoln Laboratory

Outline • Introduction • Key Efforts • Summary 999999 -7 XYZ 9/25/2021 • • VSIPL++ DRI SCA MIT Lincoln Laboratory

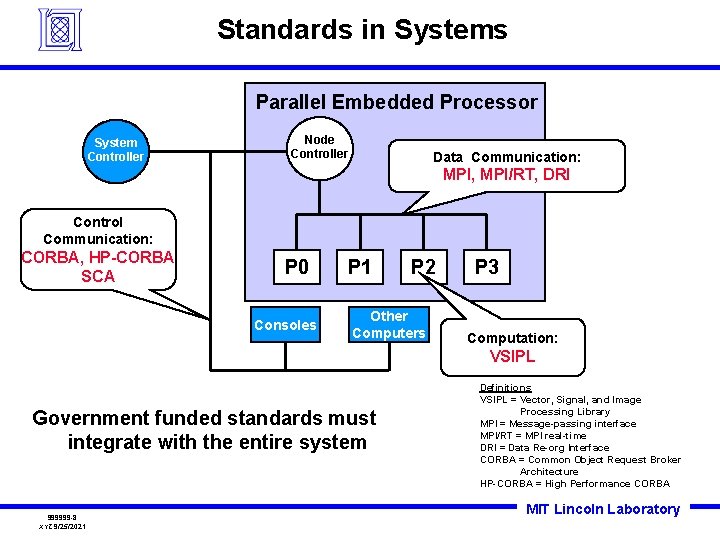

Standards in Systems Parallel Embedded Processor System Controller Node Controller Data Communication: MPI, MPI/RT, DRI Control Communication: CORBA, HP-CORBA SCA P 0 Consoles P 1 P 2 Other Computers P 3 Computation: VSIPL Government funded standards must integrate with the entire system 999999 -8 XYZ 9/25/2021 Definitions VSIPL = Vector, Signal, and Image Processing Library MPI = Message-passing interface MPI/RT = MPI real-time DRI = Data Re-org Interface CORBA = Common Object Request Broker Architecture HP-CORBA = High Performance CORBA MIT Lincoln Laboratory

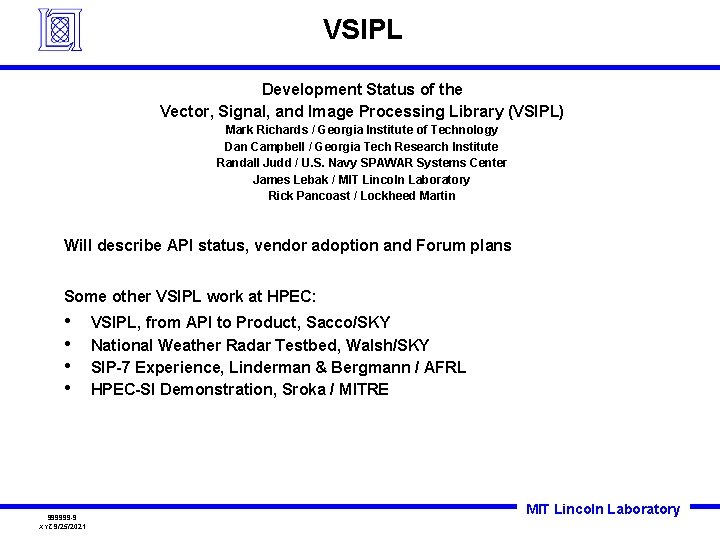

VSIPL Development Status of the Vector, Signal, and Image Processing Library (VSIPL) Mark Richards / Georgia Institute of Technology Dan Campbell / Georgia Tech Research Institute Randall Judd / U. S. Navy SPAWAR Systems Center James Lebak / MIT Lincoln Laboratory Rick Pancoast / Lockheed Martin Will describe API status, vendor adoption and Forum plans Some other VSIPL work at HPEC: • • 999999 -9 XYZ 9/25/2021 VSIPL, from API to Product, Sacco/SKY National Weather Radar Testbed, Walsh/SKY SIP-7 Experience, Linderman & Bergmann / AFRL HPEC-SI Demonstration, Sroka / MITRE MIT Lincoln Laboratory

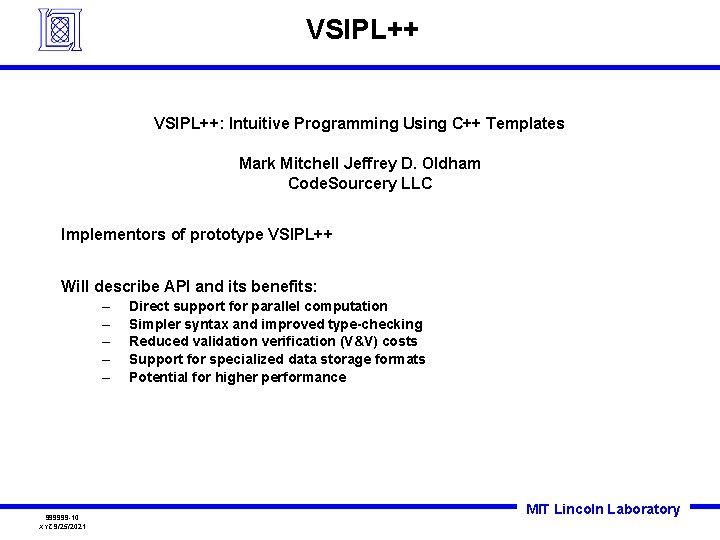

VSIPL++: Intuitive Programming Using C++ Templates Mark Mitchell Jeffrey D. Oldham Code. Sourcery LLC Implementors of prototype VSIPL++ Will describe API and its benefits: – – – 999999 -10 XYZ 9/25/2021 Direct support for parallel computation Simpler syntax and improved type-checking Reduced validation verification (V&V) costs Support for specialized data storage formats Potential for higher performance MIT Lincoln Laboratory

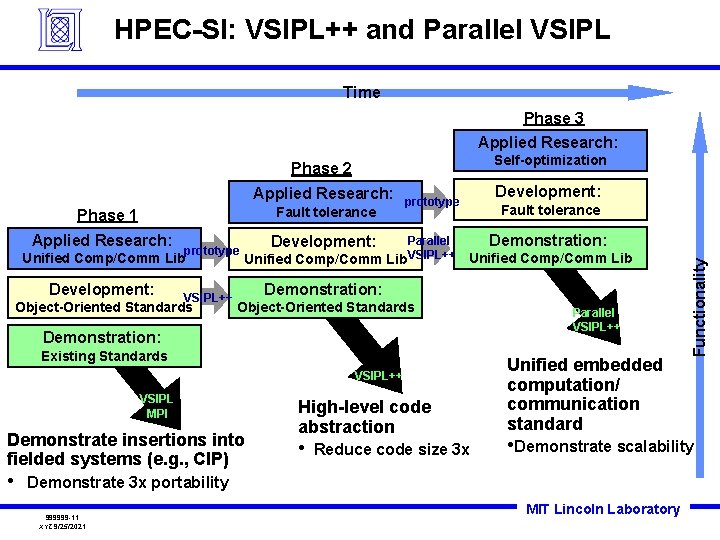

HPEC-SI: VSIPL++ and Parallel VSIPL Time Phase 3 Applied Research: Self-optimization Phase 2 Fault tolerance Phase 1 Applied Research: prototype Unified Comp/Comm Lib Development: VSIPL++ Object-Oriented Standards Development: prototype Fault tolerance Demonstration: Development: Parallel Unified Comp/Comm Lib. VSIPL++ Unified Comp/Comm Lib Demonstration: Object-Oriented Standards Demonstration: Existing Standards VSIPL++ VSIPL MPI Demonstrate insertions into fielded systems (e. g. , CIP) • High-level code abstraction • Reduce code size 3 x Parallel VSIPL++ Unified embedded computation/ communication standard • Demonstrate scalability Demonstrate 3 x portability 999999 -11 XYZ 9/25/2021 Functionality Applied Research: MIT Lincoln Laboratory

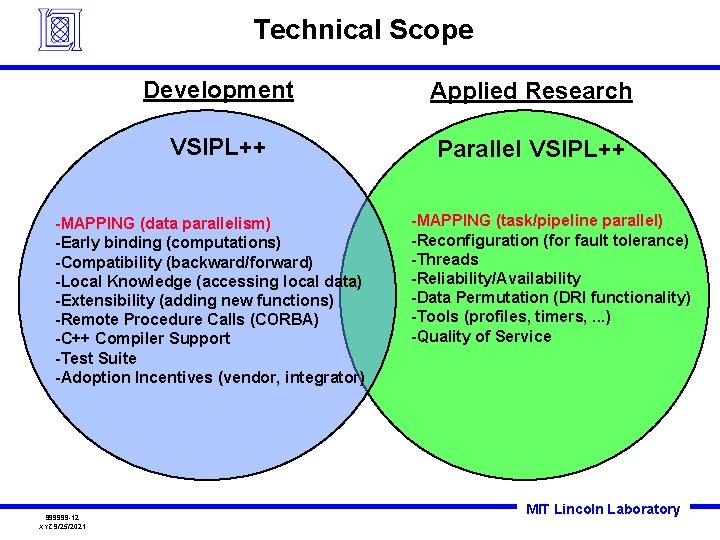

Technical Scope Development Applied Research VSIPL++ Parallel VSIPL++ -MAPPING (data parallelism) -Early binding (computations) -Compatibility (backward/forward) -Local Knowledge (accessing local data) -Extensibility (adding new functions) -Remote Procedure Calls (CORBA) -C++ Compiler Support -Test Suite -Adoption Incentives (vendor, integrator) 999999 -12 XYZ 9/25/2021 -MAPPING (task/pipeline parallel) -Reconfiguration (for fault tolerance) -Threads -Reliability/Availability -Data Permutation (DRI functionality) -Tools (profiles, timers, . . . ) -Quality of Service MIT Lincoln Laboratory

DRI Data Reorganization Interface (DRI) Kenneth Cain, Jr. / Mercury Computer Systems Anthony Skjellum / MPI Software Technology Focus • Higher level abstraction for collective communication (i. e. “corner turn”) Will describe API status, vendor adoption and Forum plans 999999 -13 XYZ 9/25/2021 MIT Lincoln Laboratory

SCA Software Communications Architecture (SCA) Compliant Software Defined Radios S. Murat Bicer / Mercury Computer Systems Jeffrey Smith / Mercury Computer Systems Technical goal: • Open architecture radios across multiple domains Will describe: • Advantages and difficulties of implementing a SCA-compliant software defined radio • An implementation to define a Minimum SCA OMG Specification 999999 -14 XYZ 9/25/2021 MIT Lincoln Laboratory

Summary • Government funded standards play a key role in transitioning Do. D developed technology into Do. D systems • Four efforts are critical for the future success of Do. D embedded computing systems 999999 -15 XYZ 9/25/2021 – VSIPL++ and Parallel VSIPL – DRI – SCA MIT Lincoln Laboratory

- Slides: 15