Sequential Multiplication Lecture L 6 4 Multiplication 13

- Slides: 37

Sequential Multiplication Lecture L 6. 4

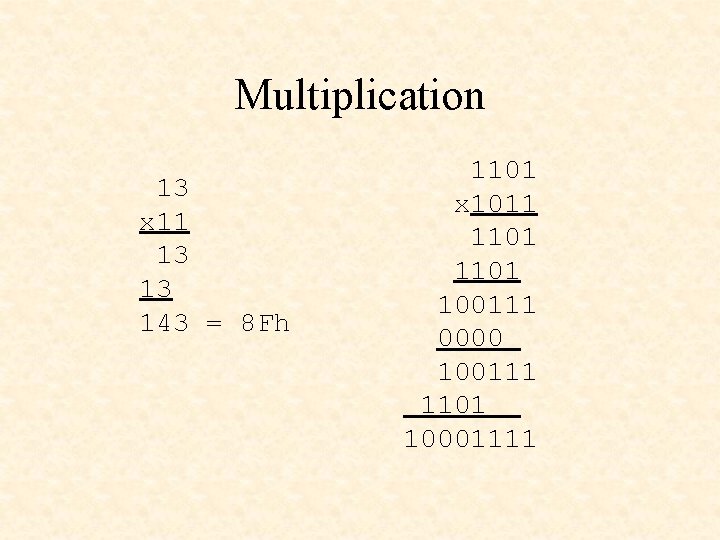

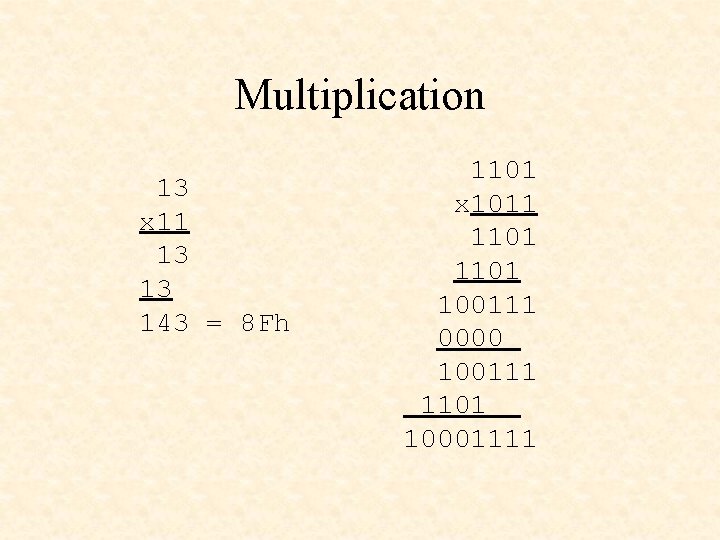

Multiplication 13 x 11 13 13 143 = 8 Fh 1101 x 1011 1101 100111 0000 100111 1101 10001111

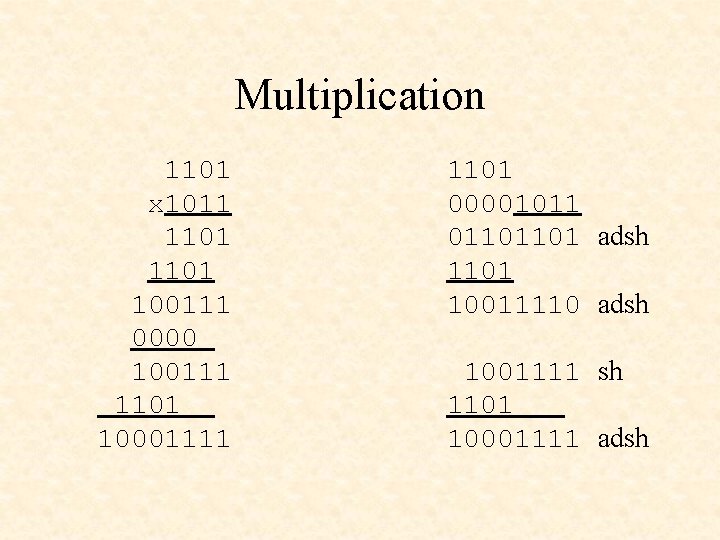

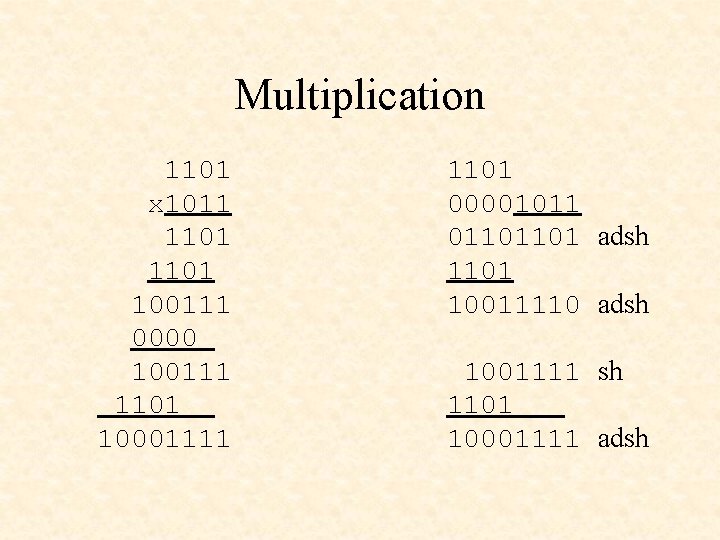

Multiplication 1101 x 1011 1101 100111 0000 100111 1101 10001111 1101 00001011 01101101 adsh 1101 10011110 adsh 1001111 sh 1101 10001111 adsh

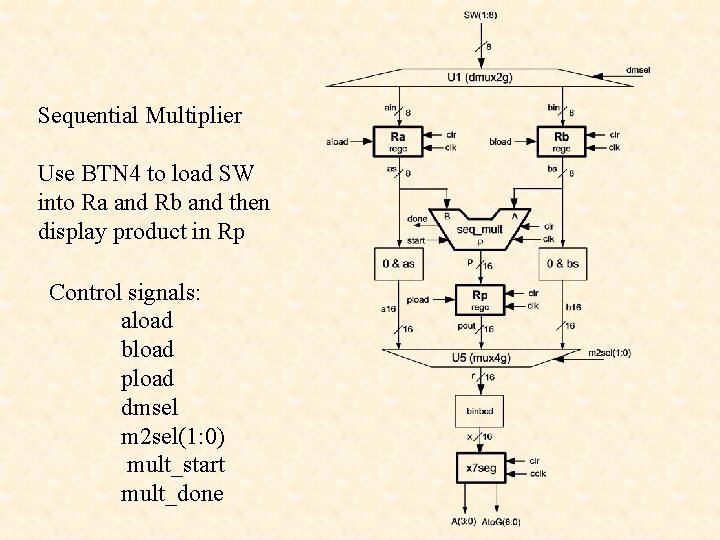

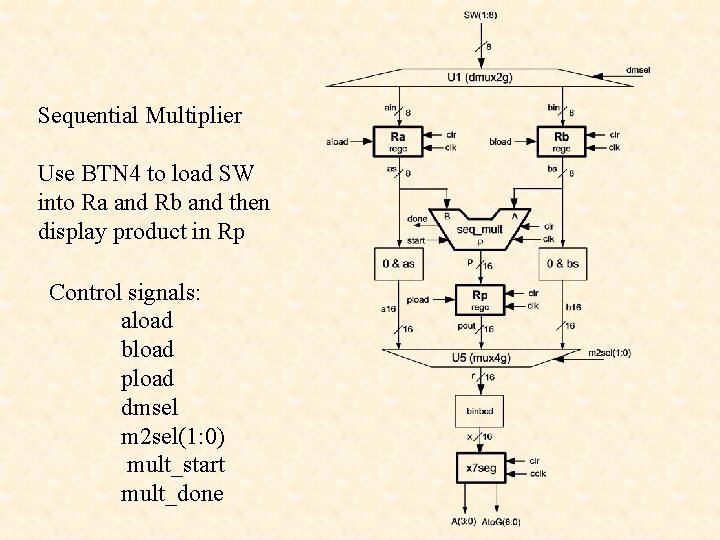

Sequential Multiplier Use BTN 4 to load SW into Ra and Rb and then display product in Rp Control signals: aload bload pload dmsel m 2 sel(1: 0) mult_start mult_done

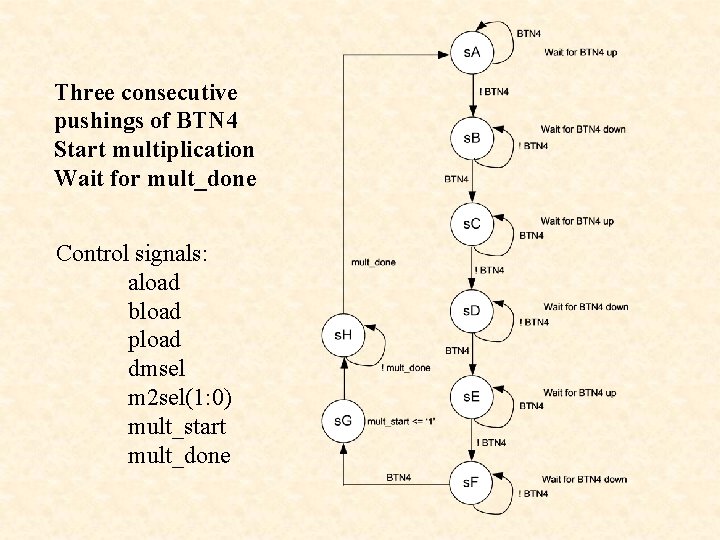

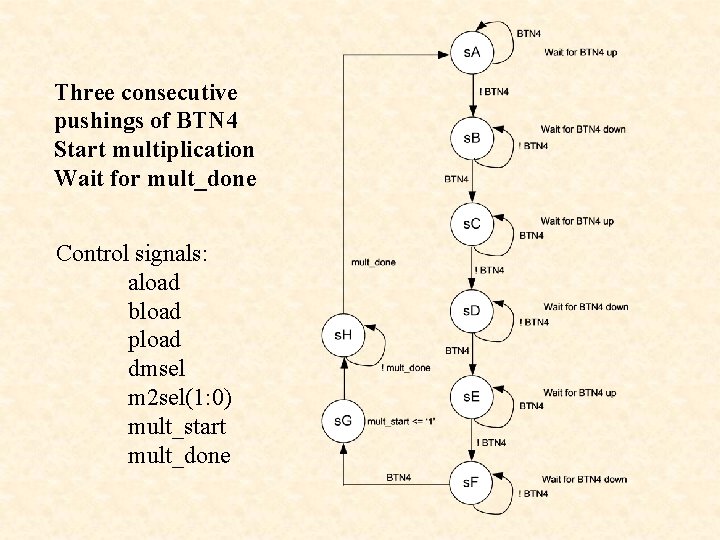

Three consecutive pushings of BTN 4 Start multiplication Wait for mult_done Control signals: aload bload pload dmsel m 2 sel(1: 0) mult_start mult_done

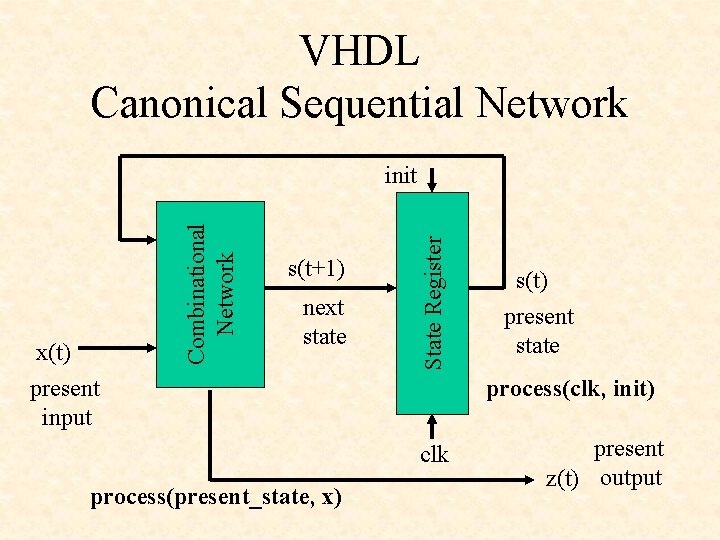

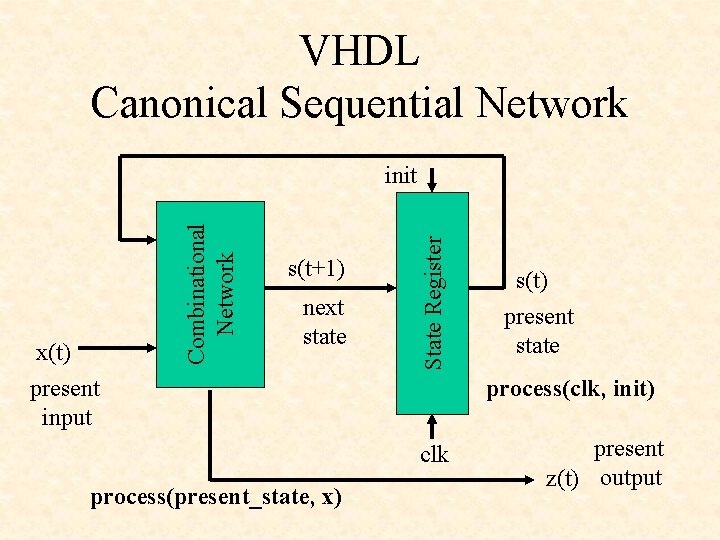

VHDL Canonical Sequential Network s(t+1) next state State Register x(t) present input Combinational Network init process(clk, init) clk process(present_state, x) s(t) present state present z(t) output

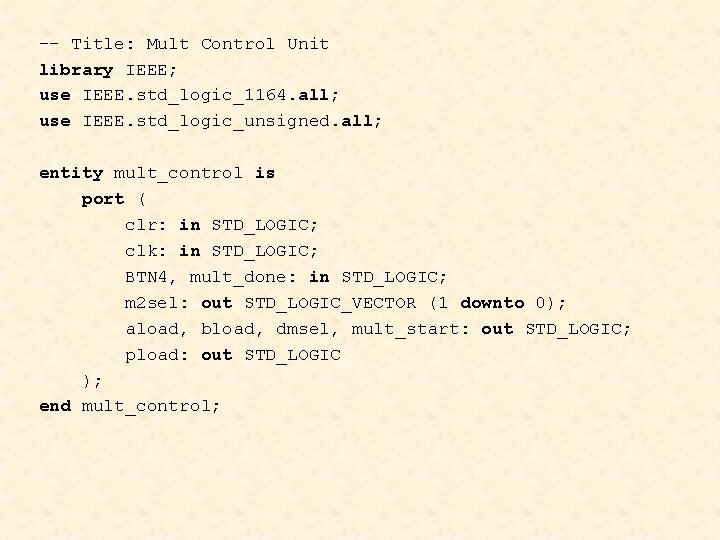

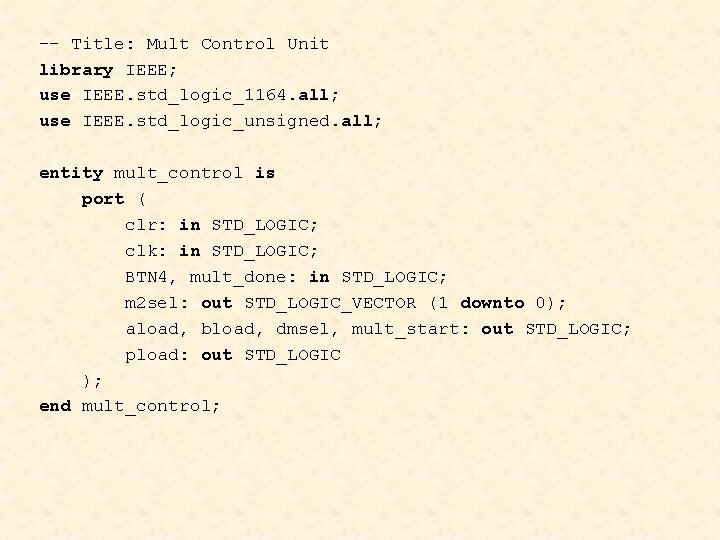

-- Title: Mult Control Unit library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity mult_control is port ( clr: in STD_LOGIC; clk: in STD_LOGIC; BTN 4, mult_done: in STD_LOGIC; m 2 sel: out STD_LOGIC_VECTOR (1 downto 0); aload, bload, dmsel, mult_start: out STD_LOGIC; pload: out STD_LOGIC ); end mult_control;

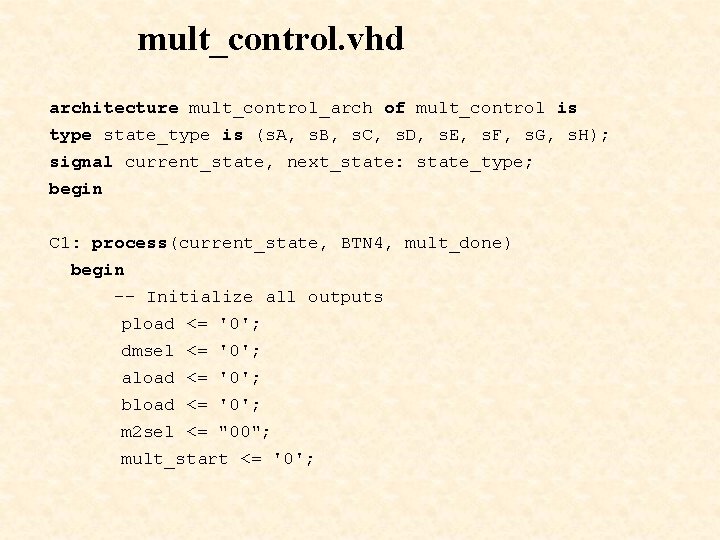

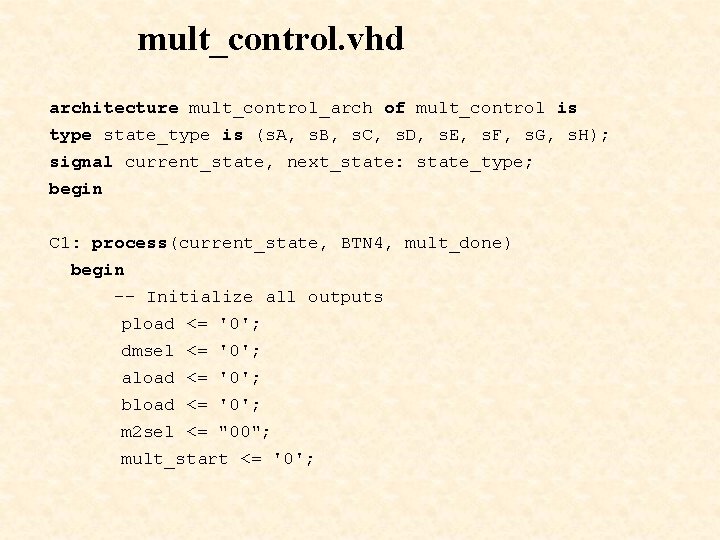

mult_control. vhd architecture mult_control_arch of mult_control is type state_type is (s. A, s. B, s. C, s. D, s. E, s. F, s. G, s. H); signal current_state, next_state: state_type; begin C 1: process(current_state, BTN 4, mult_done) begin -- Initialize all outputs pload <= '0'; dmsel <= '0'; aload <= '0'; bload <= '0'; m 2 sel <= "00"; mult_start <= '0';

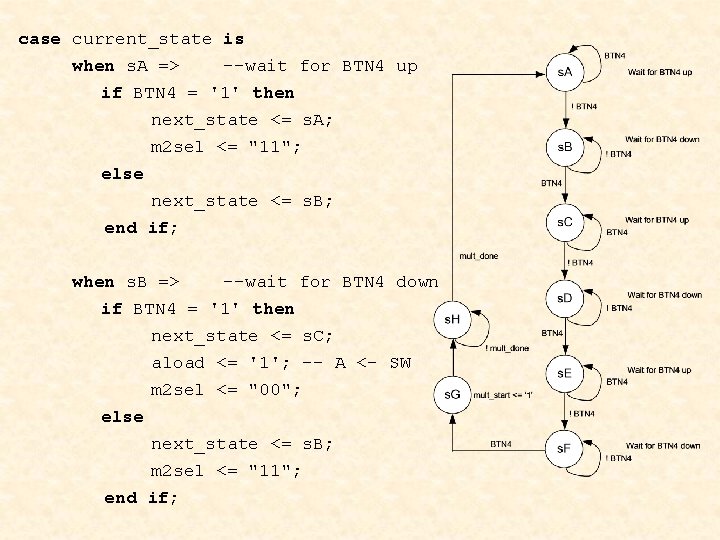

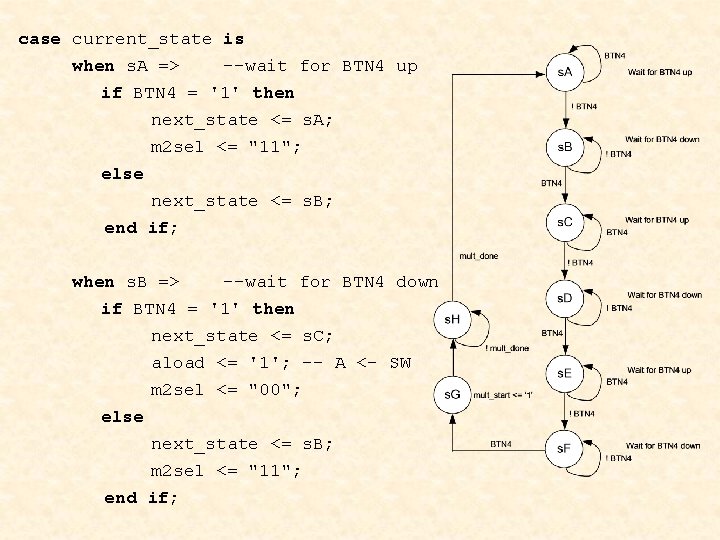

case current_state is when s. A => --wait for BTN 4 up if BTN 4 = '1' then next_state <= s. A; m 2 sel <= "11"; else next_state <= s. B; end if; when s. B => --wait for BTN 4 down if BTN 4 = '1' then next_state <= s. C; aload <= '1'; -- A <- SW m 2 sel <= "00"; else next_state <= s. B; m 2 sel <= "11"; end if;

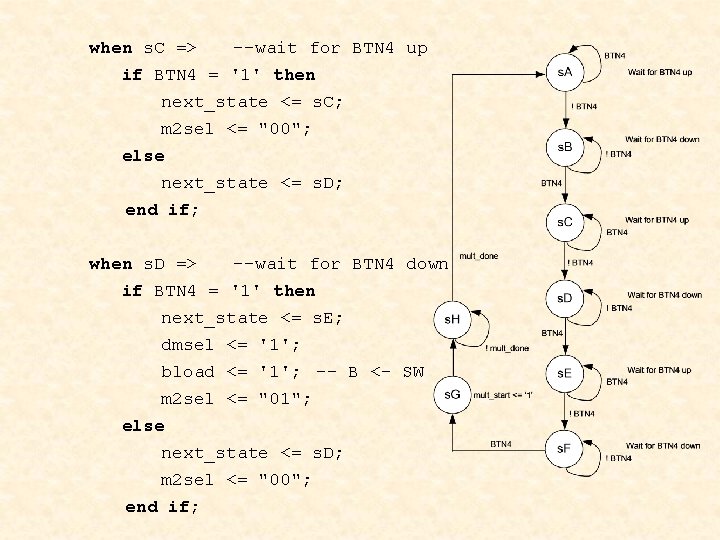

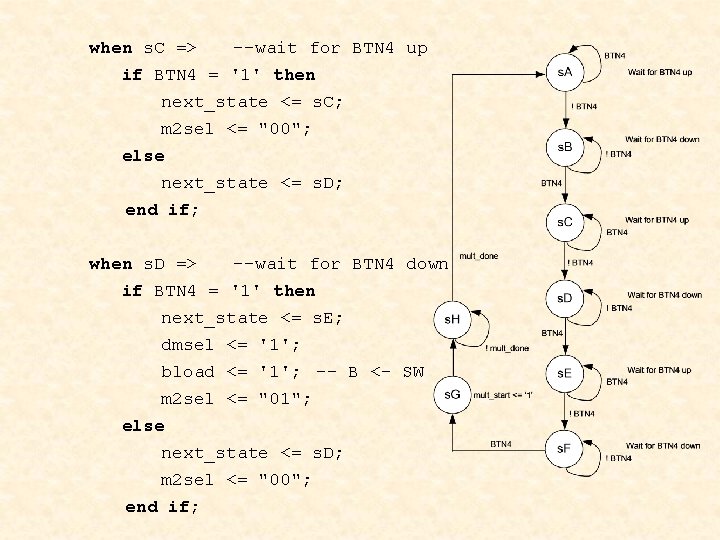

when s. C => --wait for BTN 4 up if BTN 4 = '1' then next_state <= s. C; m 2 sel <= "00"; else next_state <= s. D; end if; when s. D => --wait for BTN 4 down if BTN 4 = '1' then next_state <= s. E; dmsel <= '1'; bload <= '1'; -- B <- SW m 2 sel <= "01"; else next_state <= s. D; m 2 sel <= "00"; end if;

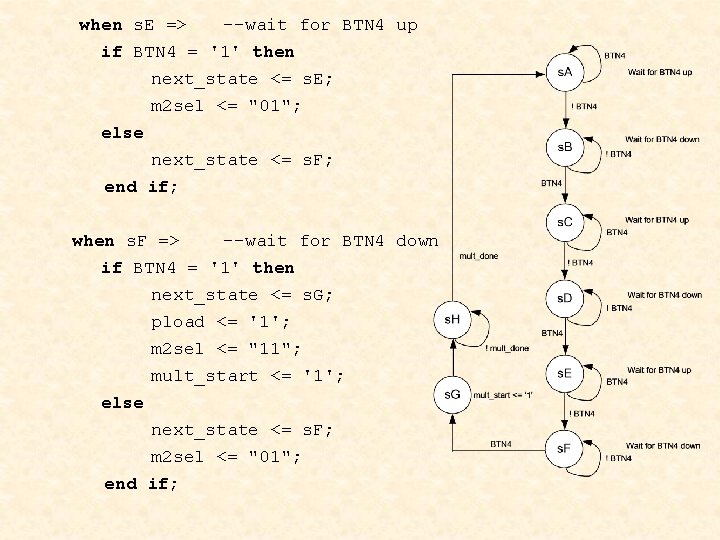

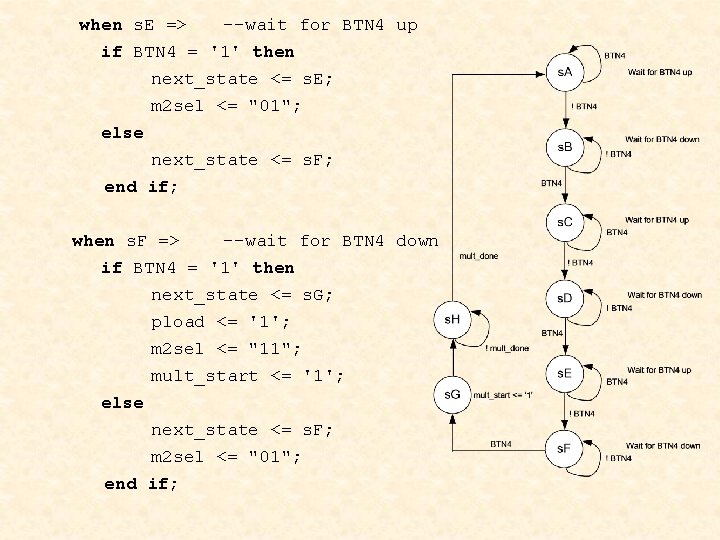

when s. E => --wait for BTN 4 up if BTN 4 = '1' then next_state <= s. E; m 2 sel <= "01"; else next_state <= s. F; end if; when s. F => --wait for BTN 4 down if BTN 4 = '1' then next_state <= s. G; pload <= '1'; m 2 sel <= "11"; mult_start <= '1'; else next_state <= s. F; m 2 sel <= "01"; end if;

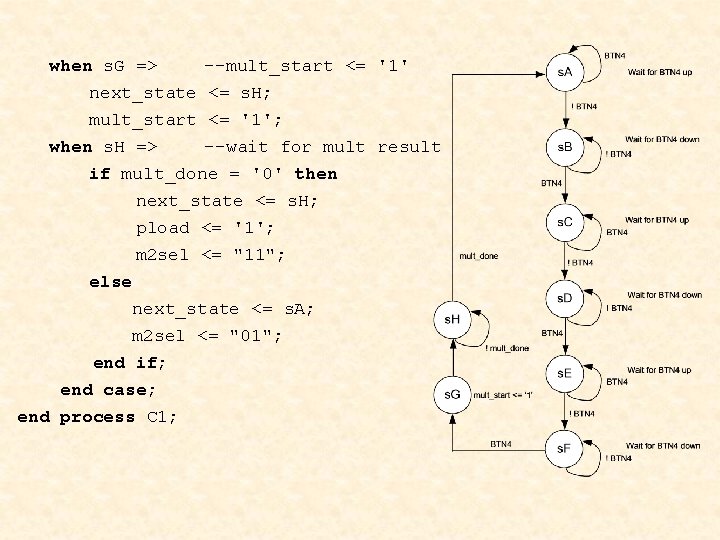

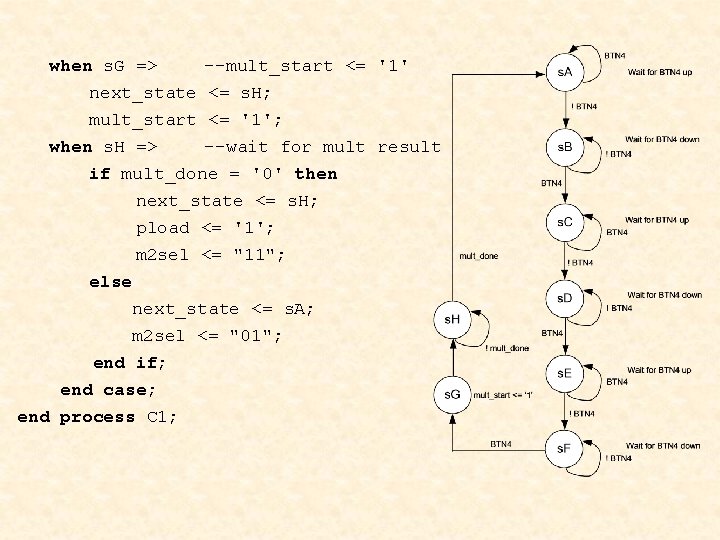

when s. G => --mult_start <= '1' next_state <= s. H; mult_start <= '1'; when s. H => --wait for mult result if mult_done = '0' then next_state <= s. H; pload <= '1'; m 2 sel <= "11"; else next_state <= s. A; m 2 sel <= "01"; end if; end case; end process C 1;

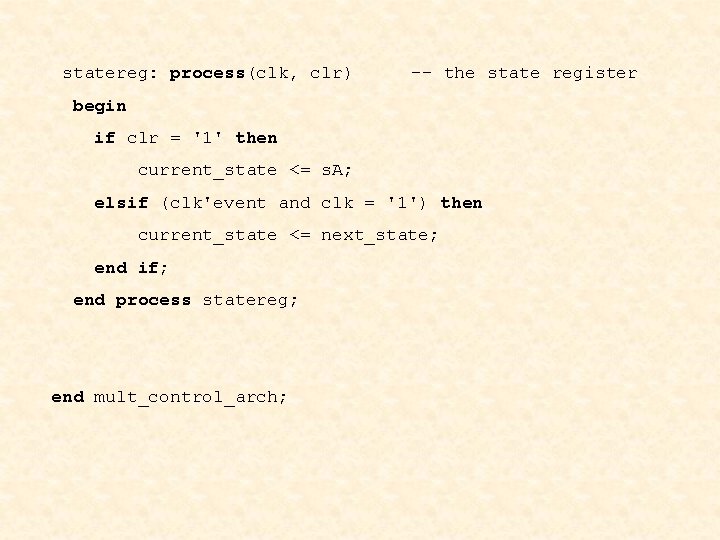

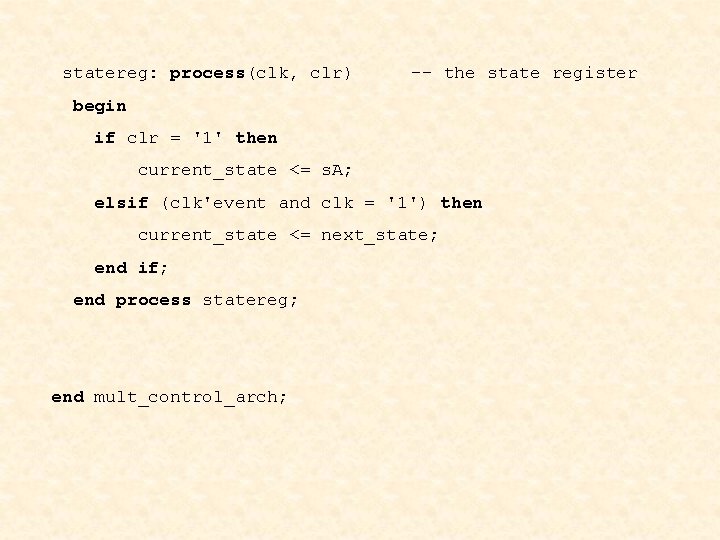

statereg: process(clk, clr) -- the state register begin if clr = '1' then current_state <= s. A; elsif (clk'event and clk = '1') then current_state <= next_state; end if; end process statereg; end mult_control_arch;

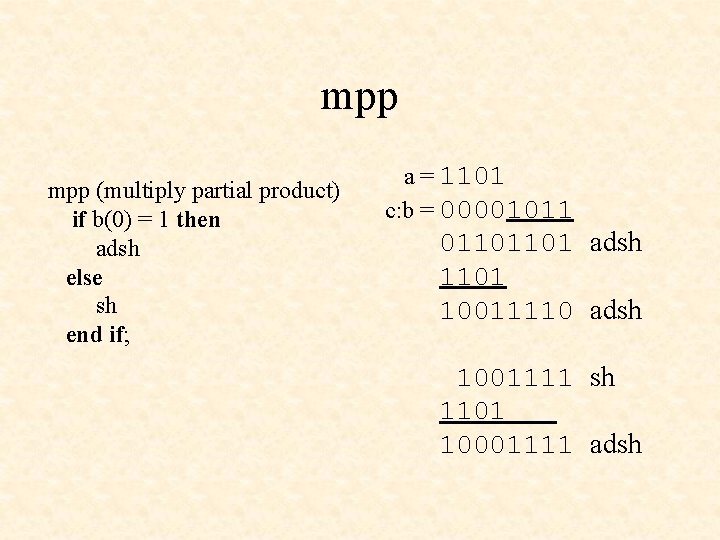

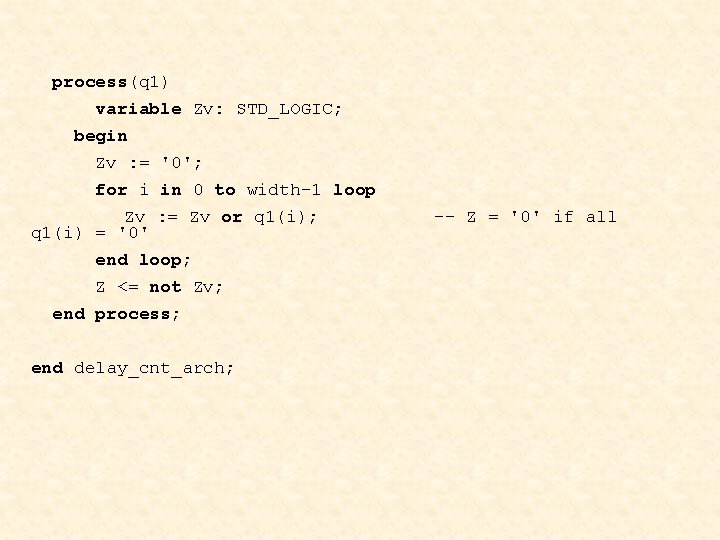

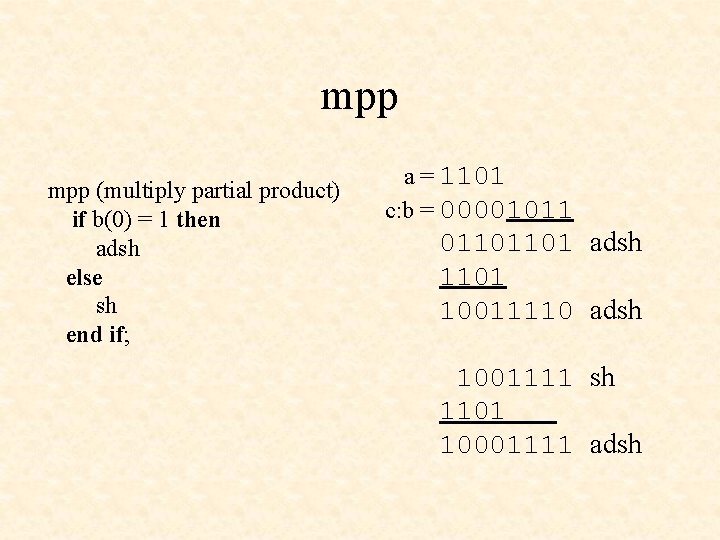

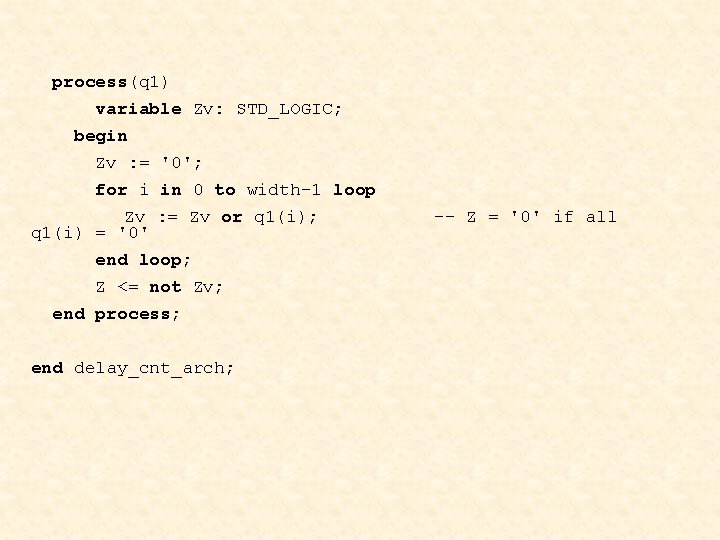

mpp (multiply partial product) if b(0) = 1 then adsh else sh end if; a = 1101 c: b = 00001011 01101101 adsh 1101 10011110 adsh 1001111 sh 1101 10001111 adsh

seq_mult Datapath

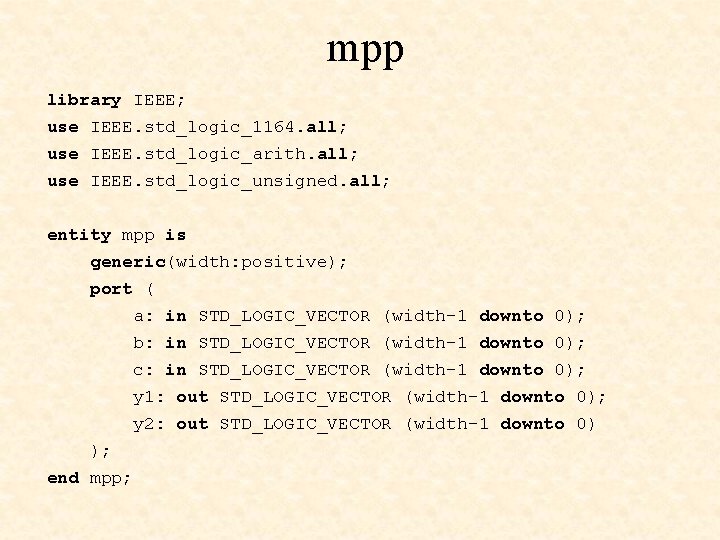

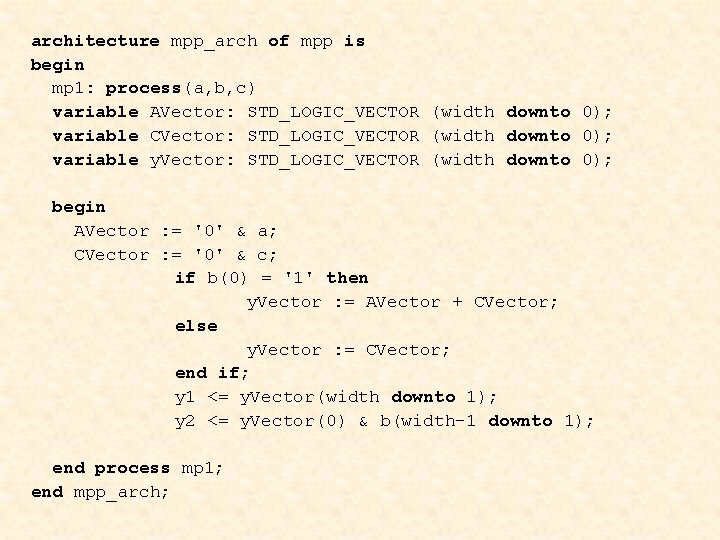

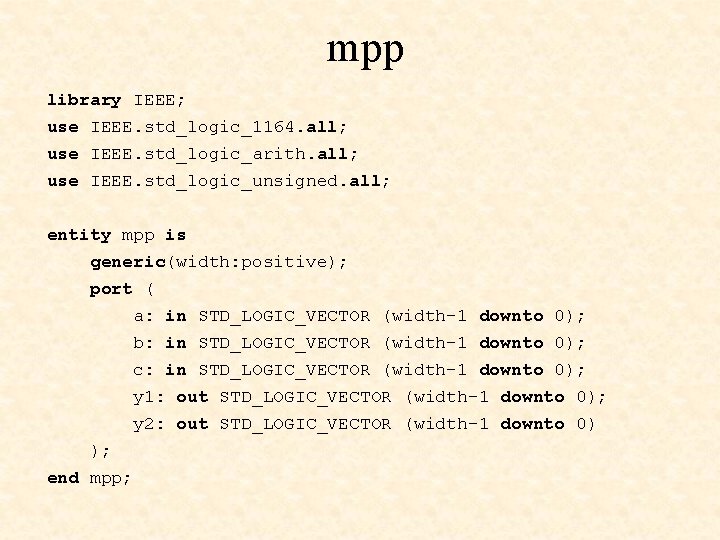

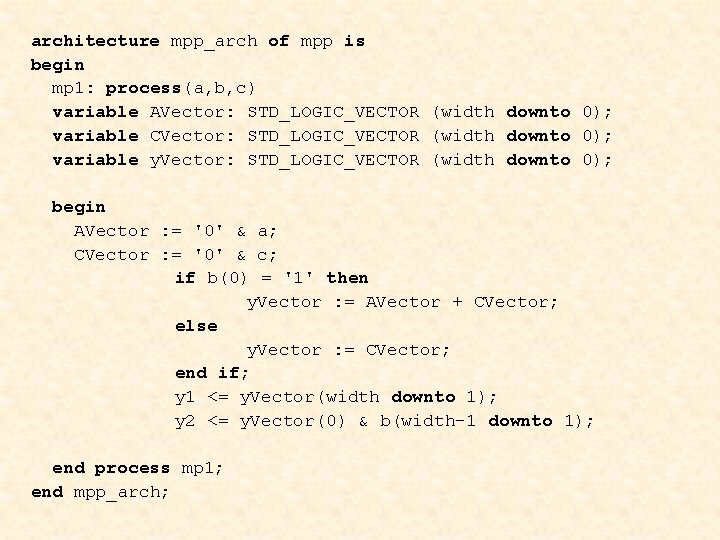

mpp library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; use IEEE. std_logic_unsigned. all; entity mpp is generic(width: positive); port ( a: in STD_LOGIC_VECTOR (width-1 downto 0); b: in STD_LOGIC_VECTOR (width-1 downto 0); c: in STD_LOGIC_VECTOR (width-1 downto 0); y 1: out STD_LOGIC_VECTOR (width-1 downto 0); y 2: out STD_LOGIC_VECTOR (width-1 downto 0) ); end mpp;

architecture mpp_arch of mpp is begin mp 1: process(a, b, c) variable AVector: STD_LOGIC_VECTOR (width downto 0); variable CVector: STD_LOGIC_VECTOR (width downto 0); variable y. Vector: STD_LOGIC_VECTOR (width downto 0); begin AVector : = '0' & a; CVector : = '0' & c; if b(0) = '1' then y. Vector : = AVector + CVector; else y. Vector : = CVector; end if; y 1 <= y. Vector(width downto 1); y 2 <= y. Vector(0) & b(width-1 downto 1); end process mp 1; end mpp_arch;

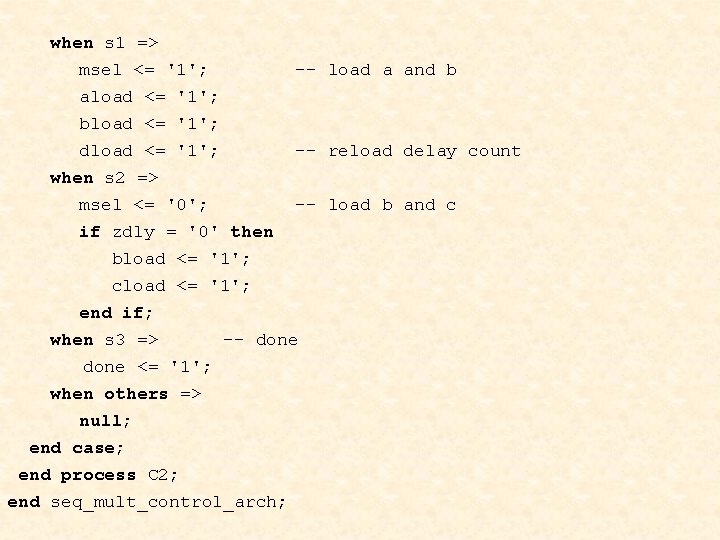

seq_mult Control

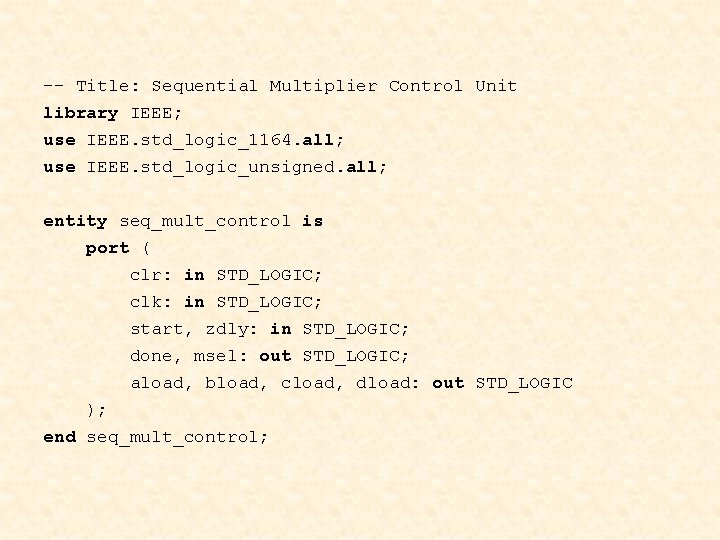

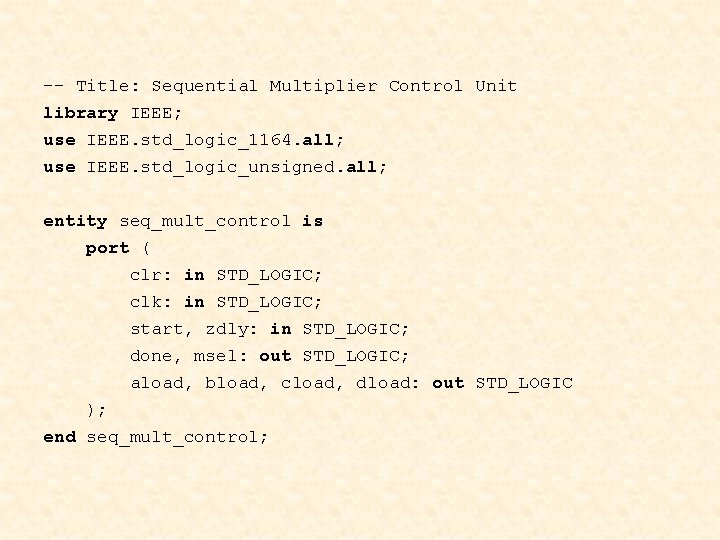

-- Title: Sequential Multiplier Control Unit library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity seq_mult_control is port ( clr: in STD_LOGIC; clk: in STD_LOGIC; start, zdly: in STD_LOGIC; done, msel: out STD_LOGIC; aload, bload, cload, dload: out STD_LOGIC ); end seq_mult_control;

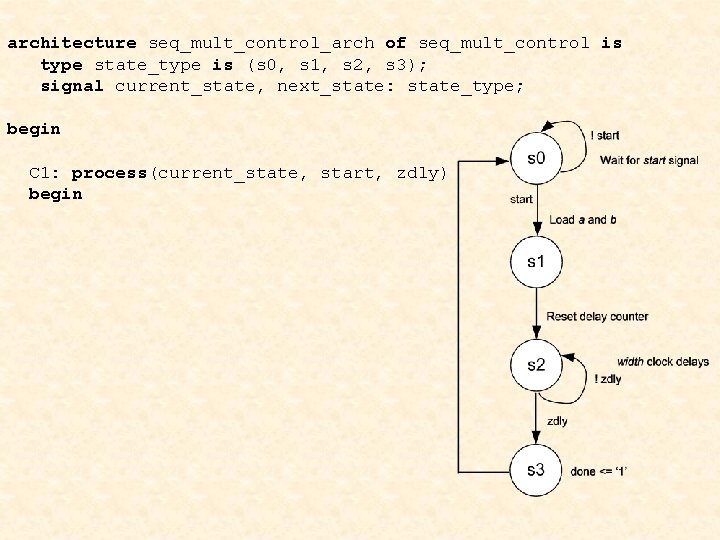

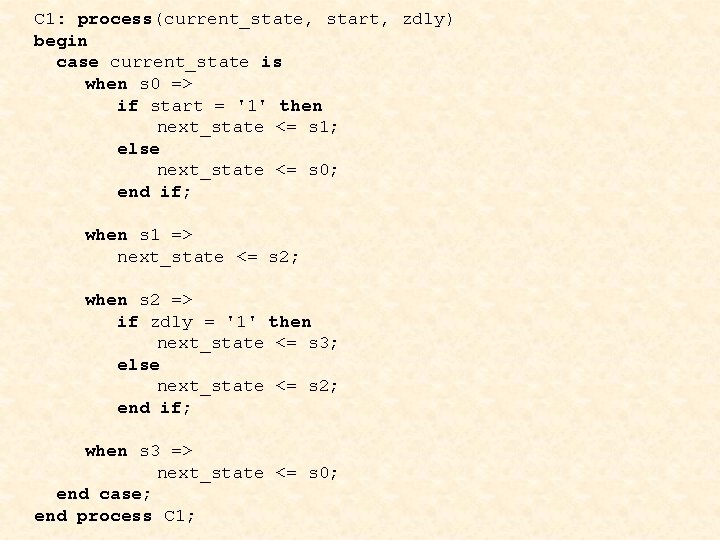

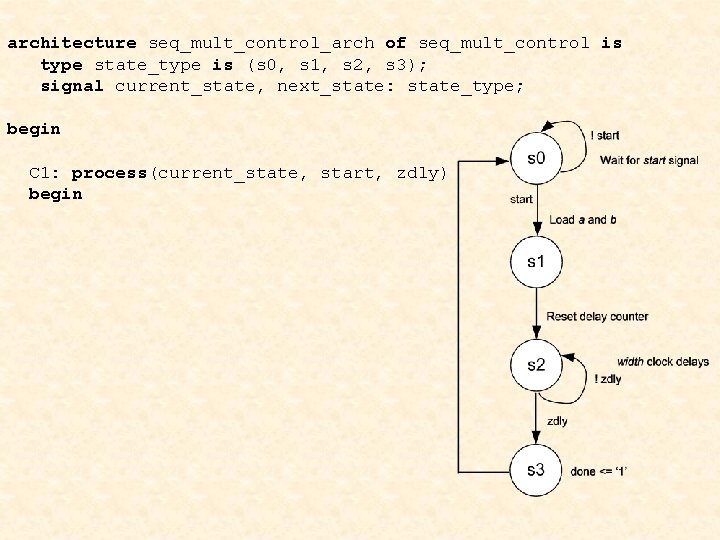

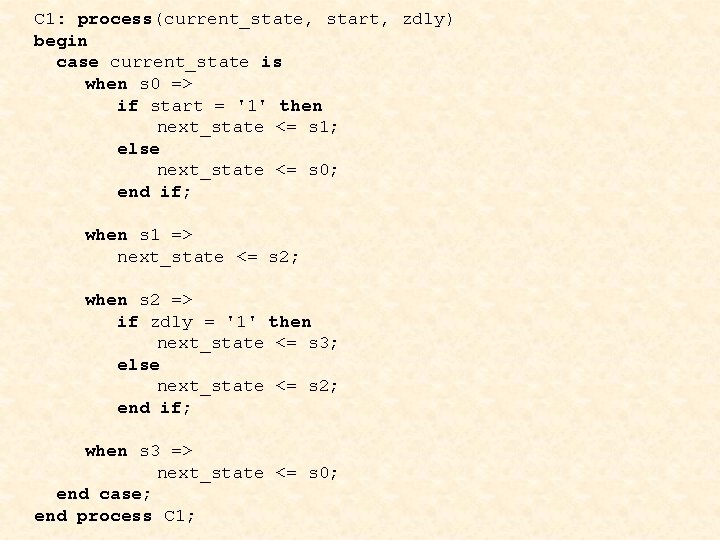

architecture seq_mult_control_arch of seq_mult_control is type state_type is (s 0, s 1, s 2, s 3); signal current_state, next_state: state_type; begin C 1: process(current_state, start, zdly) begin

C 1: process(current_state, start, zdly) begin case current_state is when s 0 => if start = '1' then next_state <= s 1; else next_state <= s 0; end if; when s 1 => next_state <= s 2; when s 2 => if zdly = '1' then next_state <= s 3; else next_state <= s 2; end if; when s 3 => next_state <= s 0; end case; end process C 1;

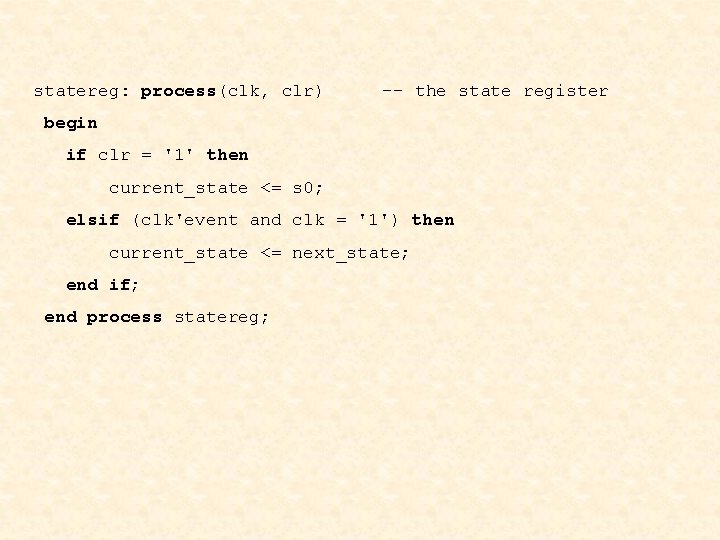

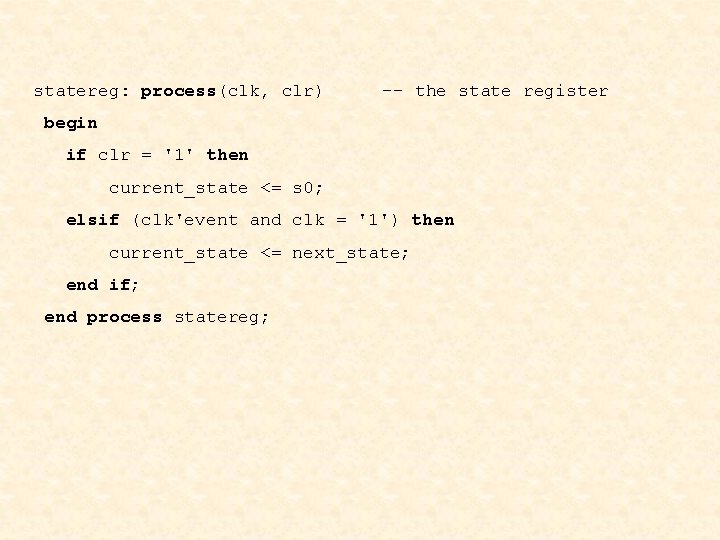

statereg: process(clk, clr) -- the state register begin if clr = '1' then current_state <= s 0; elsif (clk'event and clk = '1') then current_state <= next_state; end if; end process statereg;

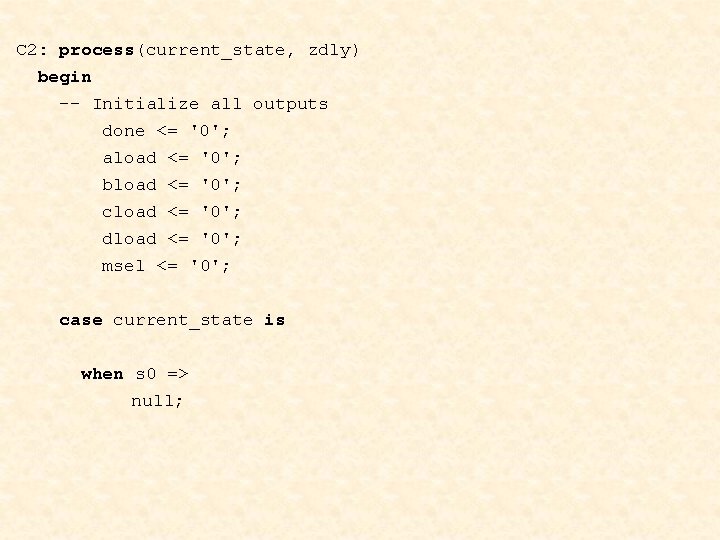

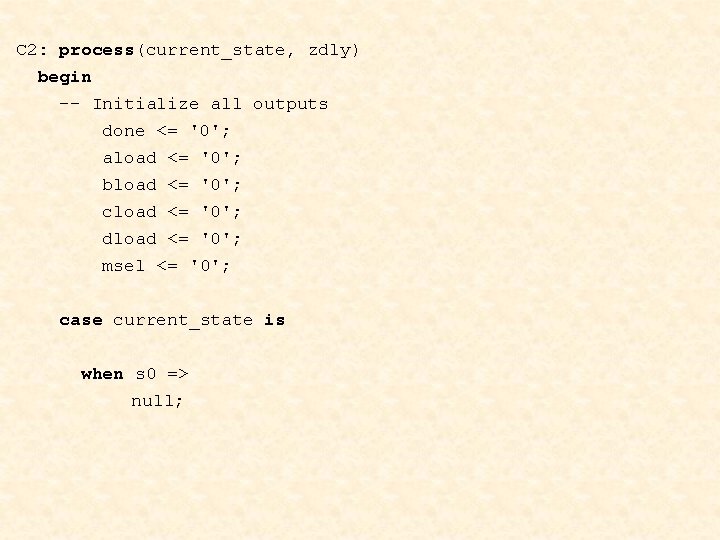

C 2: process(current_state, zdly) begin -- Initialize all outputs done <= '0'; aload <= '0'; bload <= '0'; cload <= '0'; dload <= '0'; msel <= '0'; case current_state is when s 0 => null;

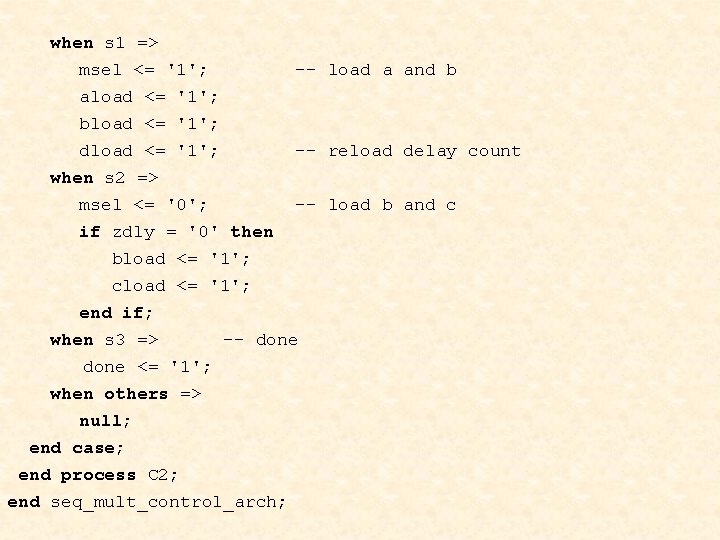

when s 1 => msel <= '1'; aload <= '1'; bload <= '1'; dload <= '1'; when s 2 => msel <= '0'; -- load a and b -- reload delay count -- load b and c if zdly = '0' then bload <= '1'; cload <= '1'; end if; when s 3 => -- done <= '1'; when others => null; end case; end process C 2; end seq_mult_control_arch;

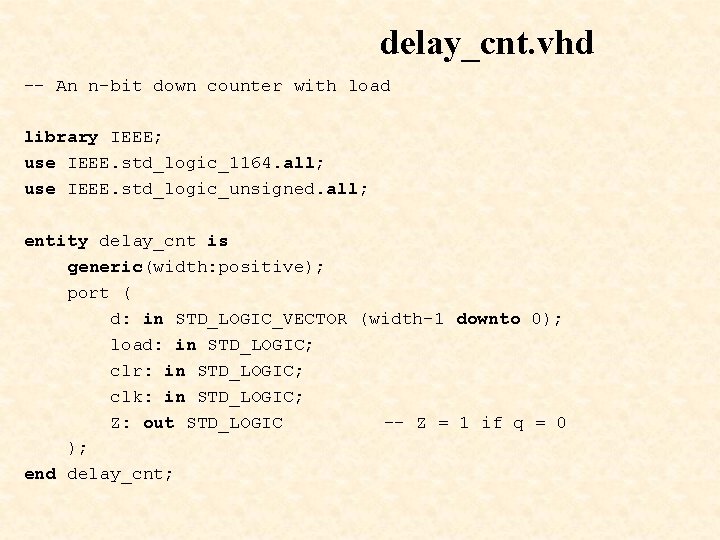

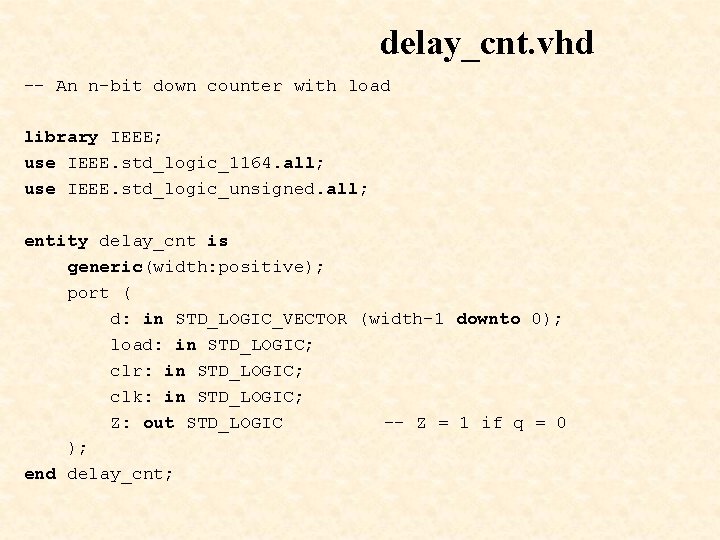

delay_cnt. vhd -- An n-bit down counter with load library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity delay_cnt is generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; clr: in STD_LOGIC; clk: in STD_LOGIC; Z: out STD_LOGIC -- Z = 1 if q = 0 ); end delay_cnt;

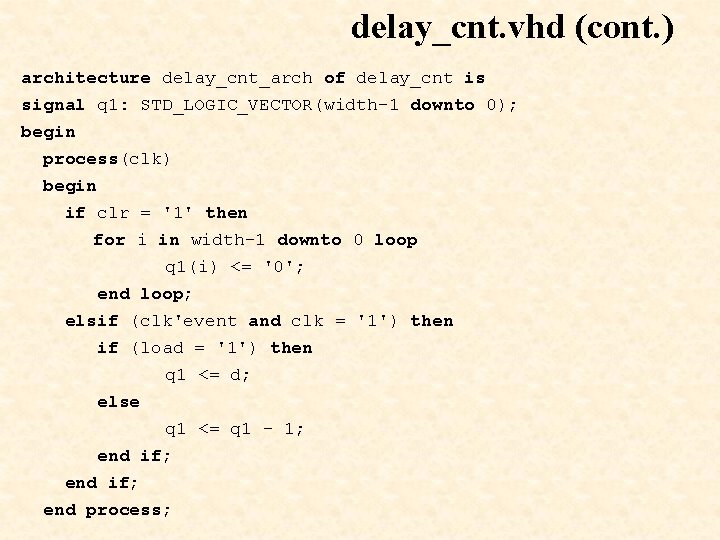

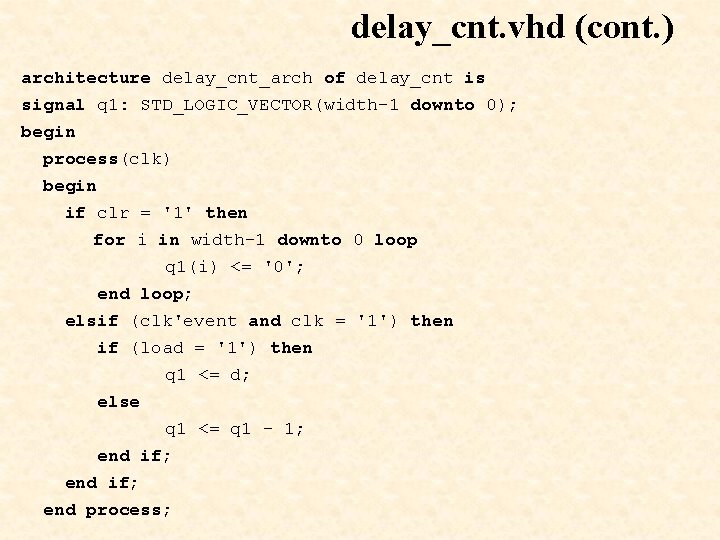

delay_cnt. vhd (cont. ) architecture delay_cnt_arch of delay_cnt is signal q 1: STD_LOGIC_VECTOR(width-1 downto 0); begin process(clk) begin if clr = '1' then for i in width-1 downto 0 loop q 1(i) <= '0'; end loop; elsif (clk'event and clk = '1') then if (load = '1') then q 1 <= d; else q 1 <= q 1 - 1; end if; end process;

process(q 1) variable Zv: STD_LOGIC; begin Zv : = '0'; for i in 0 to width-1 loop Zv : = Zv or q 1(i); q 1(i) = '0' end loop; Z <= not Zv; end process; end delay_cnt_arch; -- Z = '0' if all

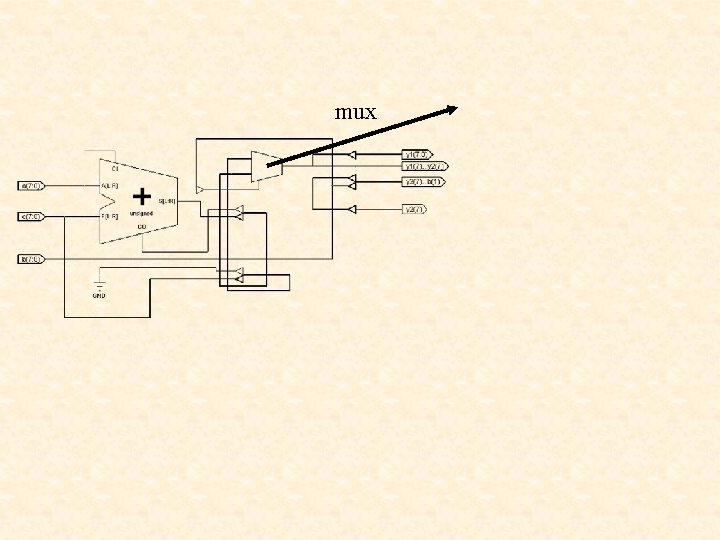

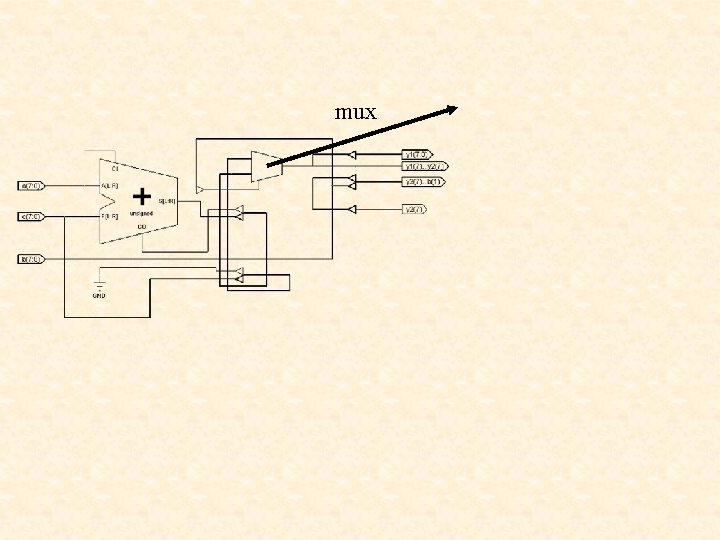

mpp seq_mult_ control a_reg delay_cnt b_reg mux 2 g c_reg

mpp

mux

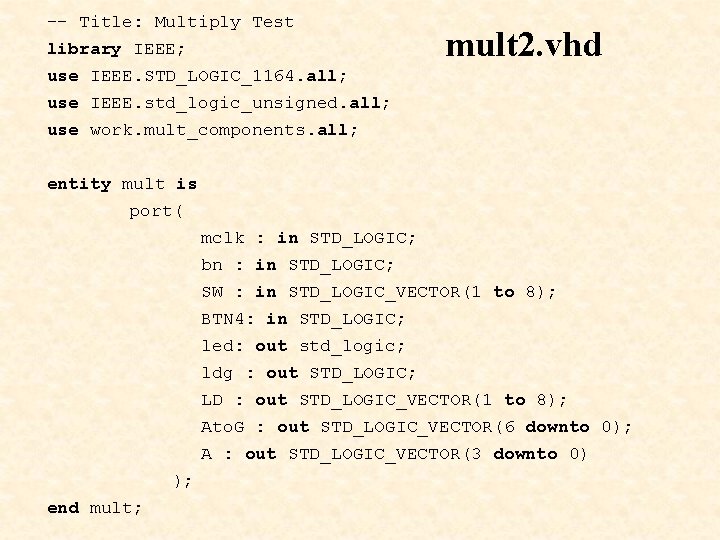

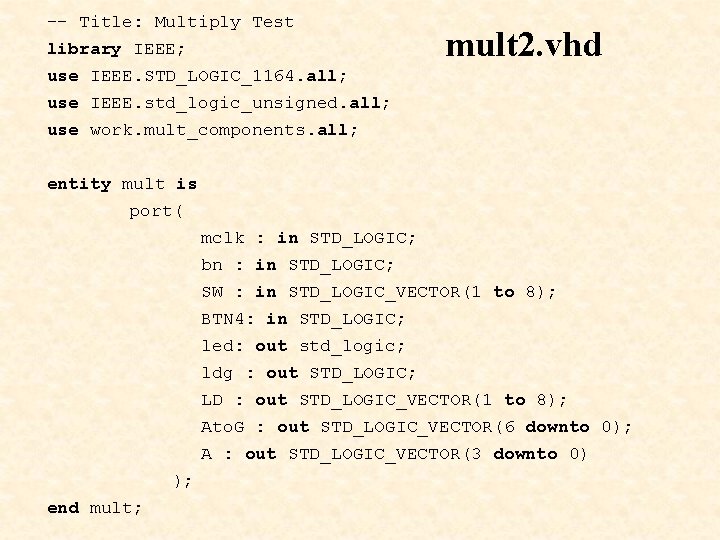

-- Title: Multiply Test library IEEE; mult 2. vhd use IEEE. STD_LOGIC_1164. all; use IEEE. std_logic_unsigned. all; use work. mult_components. all; entity mult is port( mclk : in STD_LOGIC; bn : in STD_LOGIC; SW : in STD_LOGIC_VECTOR(1 to 8); BTN 4: in STD_LOGIC; led: out std_logic; ldg : out STD_LOGIC; LD : out STD_LOGIC_VECTOR(1 to 8); Ato. G : out STD_LOGIC_VECTOR(6 downto 0); A : out STD_LOGIC_VECTOR(3 downto 0) ); end mult;

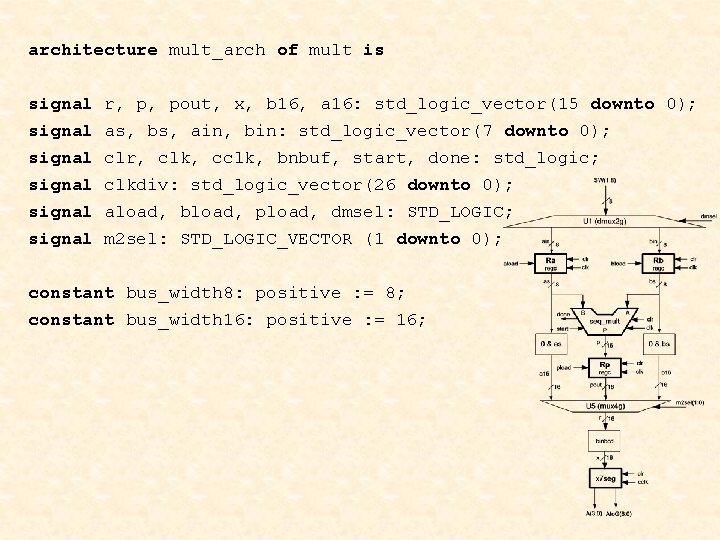

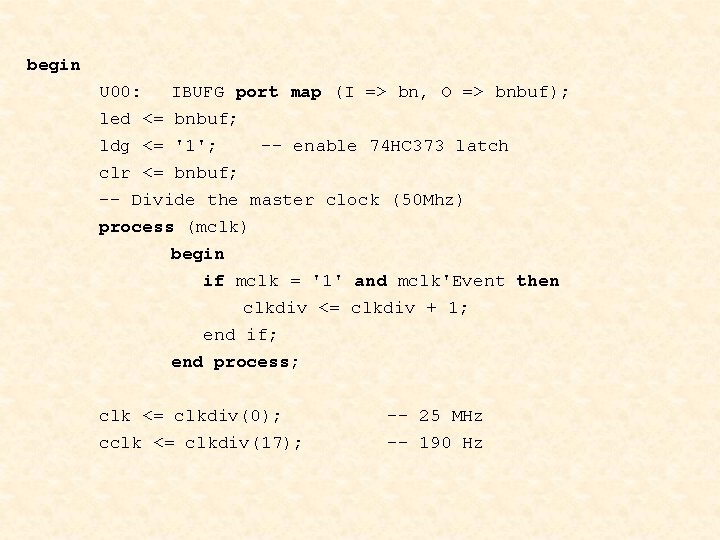

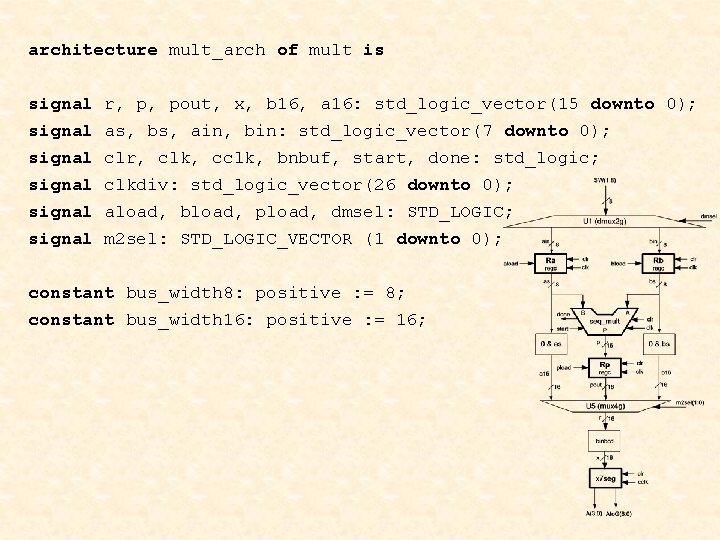

architecture mult_arch of mult is signal r, p, pout, x, b 16, a 16: std_logic_vector(15 downto 0); as, bs, ain, bin: std_logic_vector(7 downto 0); clr, clk, cclk, bnbuf, start, done: std_logic; clkdiv: std_logic_vector(26 downto 0); signal aload, bload, pload, dmsel: STD_LOGIC; signal m 2 sel: STD_LOGIC_VECTOR (1 downto 0); constant bus_width 8: positive : = 8; constant bus_width 16: positive : = 16;

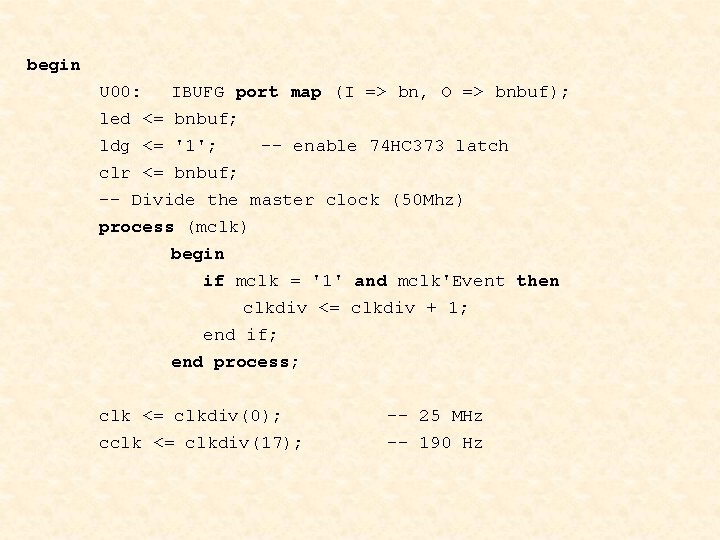

begin U 00: IBUFG port map (I => bn, O => bnbuf); led <= bnbuf; ldg <= '1'; -- enable 74 HC 373 latch clr <= bnbuf; -- Divide the master clock (50 Mhz) process (mclk) begin if mclk = '1' and mclk'Event then clkdiv <= clkdiv + 1; end if; end process; clk <= clkdiv(0); cclk <= clkdiv(17); -- 25 MHz -- 190 Hz

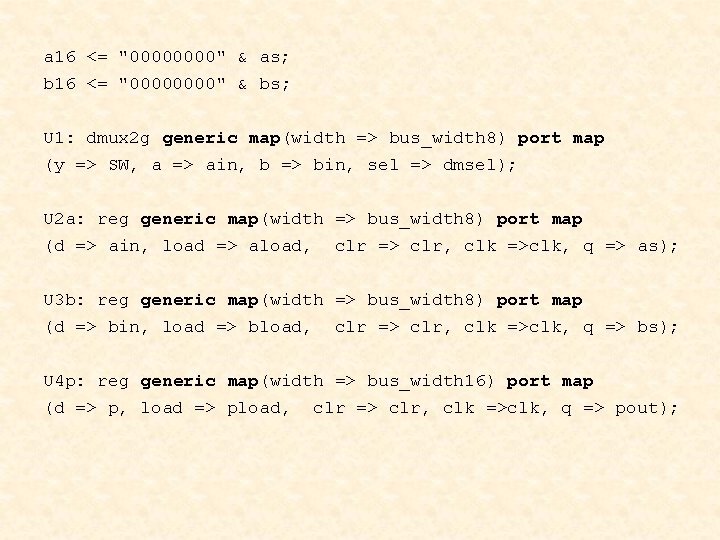

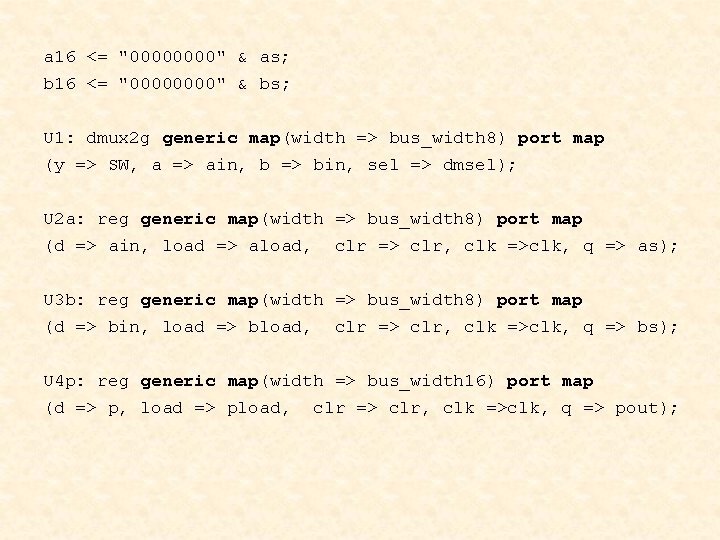

a 16 <= "0000" & as; b 16 <= "0000" & bs; U 1: dmux 2 g generic map(width => bus_width 8) port map (y => SW, a => ain, b => bin, sel => dmsel); U 2 a: reg generic map(width => bus_width 8) port map (d => ain, load => aload, clr => clr, clk =>clk, q => as); U 3 b: reg generic map(width => bus_width 8) port map (d => bin, load => bload, clr => clr, clk =>clk, q => bs); U 4 p: reg generic map(width => bus_width 16) port map (d => p, load => pload, clr => clr, clk =>clk, q => pout);

U 5: mux 4 g generic map(width => bus_width 16) port map (a => a 16, b => b 16, c => pout, d => pout, sel => m 2 sel, y => r); U 6: binbcd port map (B => r, P => x); U 7: x 7 seg port map (x => x, cclk => cclk, clr => clr, Ato. G => Ato. G, A => A);

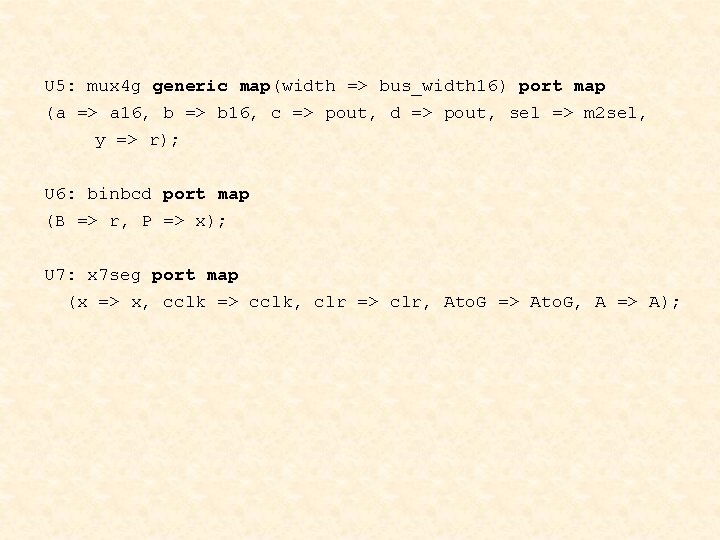

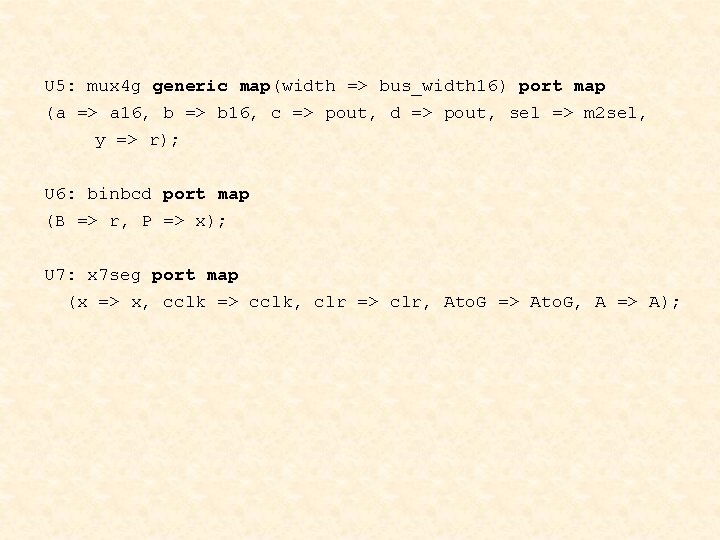

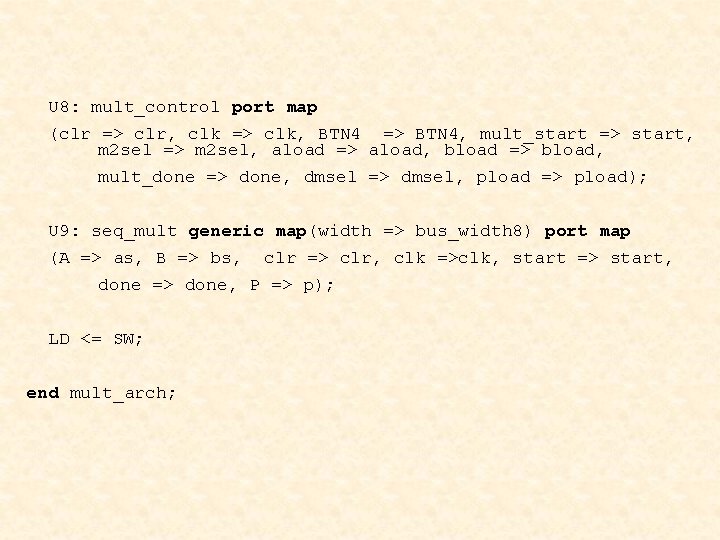

U 8: mult_control port map (clr => clr, clk => clk, BTN 4 => BTN 4, mult_start => start, m 2 sel => m 2 sel, aload => aload, bload => bload, mult_done => done, dmsel => dmsel, pload => pload); U 9: seq_mult generic map(width => bus_width 8) port map (A => as, B => bs, clr => clr, clk =>clk, start => start, done => done, P => p); LD <= SW; end mult_arch;

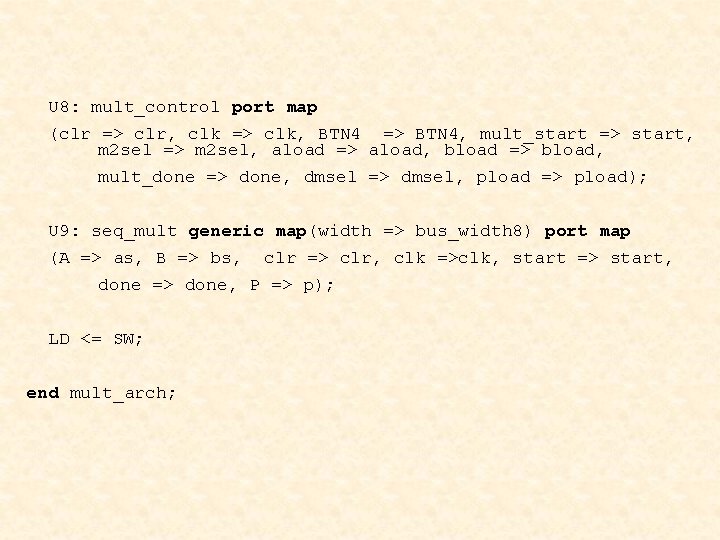

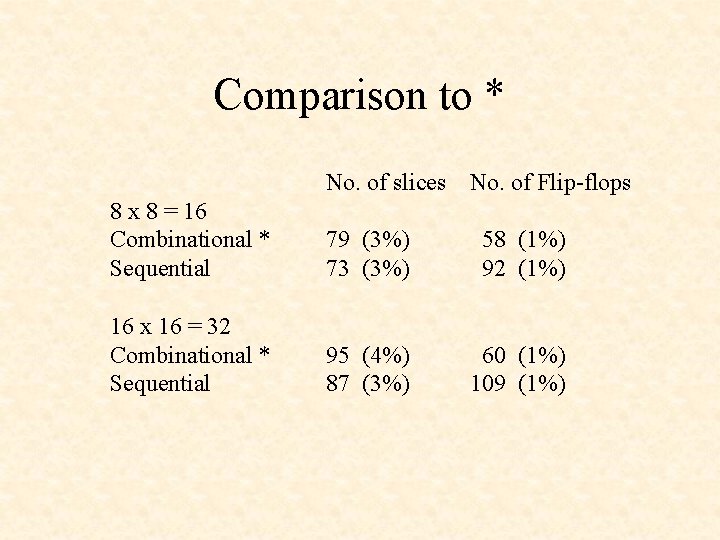

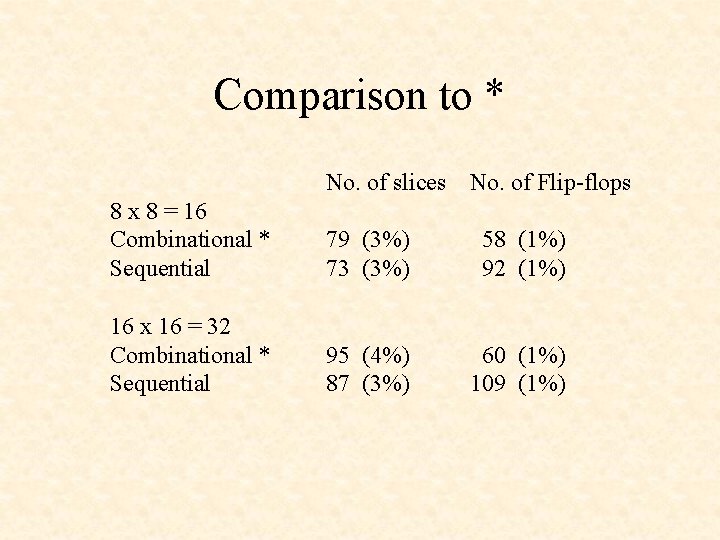

Comparison to * No. of slices No. of Flip-flops 8 x 8 = 16 Combinational * Sequential 79 (3%) 73 (3%) 58 (1%) 92 (1%) 16 x 16 = 32 Combinational * Sequential 95 (4%) 87 (3%) 60 (1%) 109 (1%)